본 발명의 일 측면에 있어서, 장치는 적어도 하나의 반도체 소자를 포함하는 반도체 기판 및 상기 반도체 기판 상에 배치된 금속층을 포함할 수 있다. 상기 장치는 개구를 정의하는 비도전층을 포함할 수 있고, 상기 비도전층은 상기 금속층 내의 리세스 상부에 배치되는 돌출부를 정의하는 단면부를 구비할 수 있으며, 상기 장치는 상기 금속층 및 상기 비도전층에 의해 정의되는 상기 돌출부 사이에 배치되는 일부분을 구비하는 솔더 범프를 포함할 수 있다.

배경 기술

반도체 소자의 웨이퍼-레벨 칩 스케일 패키지(wafer-level chip scale package, WLCSP)에서 솔더 범프들의 커플링(예를 들면, 조인트(joint))의 신뢰성은 WLCSP 어셈블리(assembly)의 제조 과정에서 중요한 이슈가 된다. 솔더 범프들 및 그 나머지의 웨이퍼-레벨 칩 스케일 패키지 사이의 신뢰성 없는 커플링은 신뢰성 테스트(reliability testing) 또는 컴퓨팅 애플리케이션(computing application) 내에서의 WLCSP의 사용 과정에서 고장(failure, 기계적 고장, 전자적 고장)을 유발할 수 있다. 예를 들면, WLCSP 내에서 알려진 어떤 솔더 범프 구성들(configurations)은 신뢰성 테스트 과정 또는 WLCSP의 솔더 범프의 사용 과정에서 바람직하지 않은 속도로 크랙(crack)이 발생하는 경향이 있다. 예를 들면, 보드-레벨 낙하 테스트(board-level drop test)와 같은 신뢰성 테스트는 솔더 범프가 본드 패드(bond pad)로부터 들어 올려질 수 있고 그리고 솔더 범프의 모서리들에서, 인캡슐레이션층(encapsulation layer)(폴리이미드(polyimide)층)의 개구(opening) 및 솔더 범프가 결합된 부분 아래의 본드 패드 사이의 접합부(junction)에서 바람직하지 않은 방법으로 솔더 범프의 크랙을 유발할 수 있다. 따라서 현재 기술의 약점을 해결하고 다른 새롭고 독창적인 특성들을 제공하는 방법들 및 장치가 필요하다.

발명의 내용

발명을 실시하기 위한 구체적인 내용

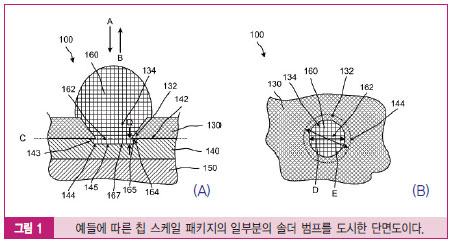

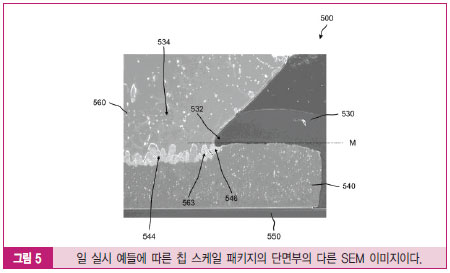

그림 1 (A)는 일 실시 예들에 따른 칩 스케일 패키지(CSP, 100)의 일부분의 솔더 범프(160)를 도시한 단면도이다. 그림 1에 도시된 칩 스케일 패키지(100)의 상기 일부분은 웨이퍼-레벨 칩 스케일 패키지(WLCSP)일 수 있다. 솔더 범프(160)는 비도전층(130)(인캡슐레이션층으로 지칭될 수 있는) 또는 언더 범프 메탈(under bump metallization, UBM)층(140)에 커플링되어 있다(접촉하거나 본딩되어 있다). UBM층(140, 도전층(conductive layer)으로 지칭될 수 있는)은 반도체 기판(150) 상에 배치된다. 반도체 기판(150)은 다양한 반도체 소자들 또는 트랜지스터들과 같은 피쳐들(features)(MOSFET들(metal-oxide-semiconductor field effect transistors), 수직형 MOSFET들(vertical MOSFETs), 수평형 MOSFET들(lateral MOSFETs), 바이폴라 정션 트랜지스터들(bipolar junction transistors, BJTs), 다이오드들(diodes), 레지스터들(resistors), 인덕터들(inductors), 비아들(vias), 금속층들 또는 등등)을 포함할 수 있다.

여기 설명된 여러 실시 예들에서, 상부(top) 및 바닥(bottom)의 용어들은 도면들의 상부 및 바닥에 대응되며(오른쪽 면이 위로 위치할 때), 피쳐들(칩 스케일 패키지(100)의 일부분의 피쳐들)을 언급하는 데 사용된다. 많은 상기 피쳐들이 칩 스케일 패키지(100)의 일부분 내에서 비춰지기(mirrored) 때문에, 단순화를 위하여 참조부호들은 칩 스케일 패키지(100)의 일부분의 한쪽 면에만 일반적으로 도시한다. 또한, 도면들에 나타난 일부 피쳐들은 여기에 정확한 스케일로 그려지지 않을 수 있다.

일 실시 예들에 있어서, UBM층(140)은, 예를 들어 구리(Cu), 금(Au), 알루미늄(Al), 니켈(Ni), 티타늄(Ti), 바나듐(V), 백금(Pt), 또는 등등과 같은 다양한 타입들의 금속(또는 이들의 조합들)일 수 있거나, 또는 이들을 포함할 수 있다. 일 실시 예들에 있어서, UBM층(140)은 폴리실리콘 물질과 같은 비금속 도전성 물질(nonmetallic conductive material)을 포함할 수 있다. 일 실시 예들에 있어서, UBM층(140)은 예를 들어 반도체 퇴적 공정 기술들(예를 들면, 화학 기상 증착(chemical vapor deposition, CVD) 기술들, 서브-대기압 CVD(sub-atmospheric CVD) 기술들)을 사용하여 퇴적된 층일 수 있다. 일 실시 예들에 있어서, UBM층(140)은 마이크로미터의 일부분(fraction of a micrometer)(예를 들어, 0.2 ㎛, 0.5 ㎛) 및 수 마이크로미터(예를 들면, 1 ㎛, 3 ㎛, 10 ㎛) 사이의 두께를 가질 수 있다. 일 실시 예들에 있어서, UBM층(140)은 솔더 범프(160)의 적어도 일부분이 커플링될 수 있는 본드 패드들(예를 들면, 본드 패드 영역들)을 정의할 수 있다. 일 실시 예들에 있어서, UBM층(140)은 각각 하나 이상의 다른 타입들의 도전성 물질들을 포함할 수 있는 하나 이상의 층들을 포함할 수 있다.

일 실시 예들에 있어서, 비도전층(130)은 예를 들어 폴리이미드, 폴리벤조비스옥사졸(polybenzobisoxazole, PBO), 벤조시클로부텐(benzocyclobutene, BCB), 실리콘 이산화물(silicon dioxide), 실리콘 질화물(silicon nitride) 또는 등등일 수 있거나, 이들을 포함할 수 있다. 일 실시 예들에 있어서, 비도전층(130)은 예를 들어 반도체 퇴적 공정 기술들을 사용하여 퇴적된 층일 수 있고, 또는 포토-디파인드(photo-defined) 층일 수 있다. 일 실시 예들에 있어서, 비도전층(130)은 마이크로미터의 일부분(예를 들어, 0.2 ㎛, 0.5 ㎛) 및 수 마이크로미터(예를 들면, 1 ㎛, 3 ㎛, 10 ㎛, 15 ㎛, 20 ㎛) 사이의 두께를 가질 수 있다.

그림 1 (A)에 도시된 바와 같이, 솔더 범프(160)는 비도전층(130) 내의 개구(134)를 통해 UBM층(140)에 커플링될 수 있다. 특히, 솔더 범프(160)는 UBM층(140)에 의해 정의되는 리세스(144)(또한, 포켓(pocket)으로 지칭될 수 있는) 내에 배치된 바닥부(162)를 구비할 수 있다. 일 실시 예들에 있어서, 솔더 범프(160)는 은(Ag), 주석(Sn), 구리(Cu), 니켈(Ni) 또는 등등을 포함하는 다양한 물질들(또는 이들의 조합들)(예를 들면, SAC, SNC, SACX 및 다른 주석계 합금들)을 사용하여 형성될 수 있다. 일 실시 예들에 있어서, 솔더 범프(160)는 비도전층(130)의 적어도 어떤 부분들(예를 들면, 상부들, 중앙 부분들)과 커플링되지 않을 수 있다(예를 들면, 접촉하지 않을 수 있다).

그림 1 (A)에 도시된 바와 같이, 리세스(144)는 경사벽(sloped wall, 143)(예를 들면, 측벽) 및 편평한(flat)(예를 들면, 실질적으로 편평한) 바닥면(145)에 의해 정의될 수 있다. 일 실시 예들에 있어서, 리세스(144)는 등방성식각 공정(isotropic etching process)(예를 들면, 습식 식각 공정(wet etch process)) 또는 이방성 식각공정(anisotropic etching process)(예를 들면, 반응성 이온 식각(reactive ion etching, RIE) 공정)과 같은 식각 공정을 사용하여 UBM층(140) 내에 형성될 수 있다. 일 실시 예들에 있어서, 리세스(144)를 제조하는 데 사용되는 상기 식각 공정은 역시 과식각(over-etch) 공정으로 지칭될 수 있는데, 이는 상기 식각이 비도전층(130)의 적어도 일부분 아래의 물질을 제거하기 때문이다.

일 실시 예들에 있어서, 리세스(144)는 그림 1 (A)에 도시된 것과는 다른 프로파일(예를 들면, 단면 프로파일)을 구비할 수 있다. 예를 들어, 일 실시 예들에 있어서, 리세스(144)의 상기 벽(143)은 그림 1 (A)에 도시된 것과는 다른 경사(slope)를 가질 수 있다. 일 실시 예들에 있어서, 리세스(144)의 벽(143)은 실질적으로 수직할 수 있다. 일 실시 예들에 있어서, 리세스(144)의 바닥은 커브질 수 있고(아래로 볼록(concave up), 위로 볼록(concave down)), 편평할 수 있고, 경사진 부분들을 가질 수 있거나, 기타 등등일 수 있다.

그림 1 (A)에 도시된 바와 같이, 비도전층(130)에 의해 정의된 돌출부(132)는 비도전층(130) 및 UBM층(140) 사이의 계면(142)을 따라 얼라인된다. 계면(142)은 C 면을 따라 얼라인된다. 일 실시 예들에 있어서, 비도전층(130)의 돌출부(132)는 오버행(overhang)으로 지칭될 수 있다. 돌출부(132)는 상기 돌출부 아래의 UBM층(140) 부분들이 상기 돌출부의 아래로부터 식각되어 제거(예를 들면, 등방성 식각 공정을 사용하여 식각)됨에 따라 형성될 수 있다. 상기 돌출부의 형성과 관련된 더욱 상세한 사항은 하기에, 예를 들어 그림 2 (A)와 관련하여 설명한다.

이러한 실시 예들에 있어서, 돌출부(132) 및 리세스(144)는 집합적으로 캐비티(164)(또는 크레비스(crevice))를 정의한다. 특히, 리세스(144)의 벽(143) 및 돌출부(132)의 바닥면이 집합적으로 캐비티(164)의 적어도 일부분을 정의한다. 리세스(144) 내의 솔더 범프(160)의 바닥부(162) 일부분은 캐비티(164) 내에 배치된다. 바닥부(162)의 상기 일부분은 돌출부(132)의 바닥면과 커플링된(또는 접촉하는) 상면을 구비한다. 일 실시 예들에 있어서, 솔더 범프(160)의 바닥부(162)의 상기 일부분은 솔더 범프(160)의 리플로우 공정 동안에 캐비티(164) 내에 배치될 수 있다. 상기 리플로우 공정은 솔더 범프(160)의 적어도 일부분이 용융(melt)될 때까지 솔더 범프(160)를 가열(heating)하는 단계를 포함할 수 있다. 상기 캐비티(164) 내의 상기 솔더 범프의 형성과 관련된 더욱 상세한 사항은 하기에, 예를 들어 그림 2 (A) 내지와 관련하여 설명한다.

비도전층(130)의 돌출부(132)는 칩 스케일 패키지(100)의 상기 일부분 내에 솔더 범프(160)를 재빨리 홀드(hold)하도록 구성된 유지 부재(retention member)로 작용할 수 있다. 일 실시 예들에 있어서, 비도전층(130)의 돌출부(132)는 솔더 범프(160)의 신뢰성 테스트 과정에서, 또는 예를 들어 칩 스케일 패키지(100)의 상기 일부분이 컴퓨팅 애플리케이션에서 사용될 때의 신뢰성을 위한 유지 부재로 작용할 수 있다. 예를 들면, 돌출부(132)는 보드-레벨 낙하 테스트(board-level drop test, BLDT) 과정에서 솔더 범프(160)의 크랙킹(솔더 범프(160) 내에서)을 방지하거나 또는 칩 스케일 패키지(100)의 상기 일부분(UBM층(140) 또는 비도전층(130))으로부터 디커플링(decoupled)되는 것을 방지할 수 있다. 보드-레벨 낙하 테스트 과정에서, 아래 방향으로의(A 방향을 따라) 힘들이 솔더 범프(160)에 대항하여(against) 인가될 수 있고(대상체를 사용하여), 이는 위 방향으로의(B 방향을 따라) 리바운드 힘들(rebound forces)(예를 들면, 스프링백 힘들(spring-back forces))을 유발하거나 일으킬 수 있다. 이러한 리바운드 힘들은 솔더 범프(160) 또는 그 일부분이 크랙되거나 또는 금속층(140)으로부터 들어올려지는 것을(B 방향을 따라) 유발할 수 있다. 돌출부(132)는 솔더 범프(160)를 안전하게 유지할 수 있고, 솔더 범프(160)가 크랙되거나 또는 위 방향으로의(B 방향을 따른) 힘들에 대응하여 들어 올려지는 것을 방지할 수 있다. 여기 설명된 기술들을 사용하여 많은 가능한 고장 메커니즘들이 방지될 수 있거나, 실질적으로 방지될 수 있으므로, 이러한 예시적인 메커니즘은 예시들을 한정하는 것으로 여겨져서는 안 된다.

돌출부(132)의 형성을 유발할 수 있는 리세스(144)의 형성이 없다면, UBM층(140)은 리세스(144) 내에 배치되고 C 면 아래에 배치된 바닥면(145)을 구비하지 않을 것이다. 대신에, 리세스되지 않은(non-recessed) UBM층 내에, 솔더 범프의 바닥 에지(edge)가 상기 UBM층 및 비도전층 사이의 접합부에서 끝날 것이고, 돌출부는 존재하지 않을 것이다. 이러한 리세스되지 않은 구성들에서, 신뢰성 테스트 동안에, 상기 솔더 범프는 아래 방향으로의 힘들 및 후속적인 위 방향으로의 힘들에 대응하여 상기 접합부에서 시작되어 크랙될 수 있다. 여기 설명된 기술들을 사용하여 많은 가능한 고장 메커니즘들이 방지될 수 있거나, 실질적으로 방지될 수 있으므로, 이러한 예시적인 메커니즘은 예시들을 한정하는 것으로 여겨져서는 안 된다.

리세스되지 않은 구성 내에서 설명된 접합부(교차부(intersection))는 그림 1 (A)에 도시된 구성으로부터 제외된다. 대신에, 리세스(144)의 바닥면(145)을 따른 솔더 범프(160)의 바닥면(167)이 리세스(144)와 동일한 물질로 형성된 리세스(144)의 벽(143)에서 끝난다(terminate). 솔더 범프(160)의 바닥부(162)의 상기 일부분은 비도전층(130) 및 금속층(140) 사이의 접합부(교차부)에서 끝나는 캐비티(164)의 상부 모서리 내의 일 지점(point)을 구비한다. 그러나 이러한 접합부(교차부)는 돌출부(132) 아래에 위치한다. 따라서 아래 방향으로의(A 방향을 따른) 힘들 또는 위 방향으로의(B 방향을 따른) 힘들에 대응한 상기 접합부의 크랙킹은 방지될 수 있다(또는 실질적으로 방지될 수 있다). 그렇지 않다면, 리세스되지 않은 구성 내에서 솔더 범프(160) 내로 분산되거나(distributed) 인도되어(directed) 솔더 범프(160) 내의 크랙킹을 유발하였을 힘들(예를 들면, 힘 벡터들(force vectors))은, 대신에 비도전층(130)의 돌출부(132)에 대항하여 인가되어 그림 1 (A)에 도시된 칩 스케일 패키지(100) 구성의 상기 일부분의 솔더 범프(160) 내에서 크랙킹을 방지할 수 있다. 다시 말하면, 돌출부(132)는 솔더 범프(160) 내로(또는 대항한) 힘들의 인가를 바꿈으로써 신뢰성 테스트 과정에서 고장들을 방지 또는 실질적으로 방지하도록 구성될 수 있다. 다르게 말하면, 어떤 힘들은 비도전층(130)의 돌출부(132)에 대항하여 인가될 것이고, 솔더 범프(160) 내부 대신에 비도전층(130) 또는 UBM층(140) 내부의 다른 곳으로 분산될 것이다. 여기 설명된 기술들을 사용하여 많은 가능한 고장 메커니즘들이 방지될 수 있거나, 실질적으로 방지될 수 있으므로, 이러한 예시적인 메커니즘은 예시들을 한정하는 것으로 여겨져서는 안 된다.

리세스(144)의 형성으로, 솔더 범프(160)의 바닥부(162)가 커플링될 수 있는 표면적(surface area)은 또한 리세스(144)의 형성 없이 솔더 범프(160)가 커플링될 수 있는 표면적보다 크다. 또한, 힘들(신뢰성 테스트 동안에 인가되는 힘)이 인가될 수 있는 표면적은, 리세스(144)가 형성된 경우에 리세스되지 않은 칩 스케일 패키지 구성의 표면적과 비교할 때 더 크다. 특히, 솔더 범프(160) 층은 리세스(144)의 벽(143), 리세스(144)의 바닥면(145), 돌출부(132)의 바닥면, 또는 비도전층(130) 내에서 개구(134)를 정의하는 벽에 커플링될 수 있다.

그림 1 (B)는 그림 1 (A)에 도시된 칩 스케일 패키지(100)의 일부분의 상부 단면을 나타낸 도면이다. 칩 스케일 패키지(100)의 일부분의 상면도는 그림 1 (A)에 도시된 C 면 바로 위에서 잘라진 칩 스케일 패키지(100)를 나타낸다. 돌출부(132)의 바닥면(상기 C 면 바로 위의)이 그림 1 (B)에 도시된다. 리세스(144)의 벽(143)의 에지(상기 C 면 바로 아래)는 점선으로서 그림 1 (B)에 도시된다. 이러한 실시예에서, 비도전층(130)의 개구(134) 및 리세스(144)의 벽(143)의 에지는 원형(circular shape)을 갖도록 도시된다. 일 실시 예들에 있어서, 비도전층(130)의 개구(134) 또는 리세스(144)의 벽(143)의 상기 에지는 육각형, 정사각형, 커브진 형상, 타원형, 직사각형, 또는 등등과 같은 다양한 형상(또는 단면 프로파일)을 가질 수 있다. 일 실시 예들에 있어서, 비도전층(130)의 개구(134) 및 리세스(144)의 벽(143)의 상기 에지는 다양한 형상들(또는 단면 프로파일들)을 가질 수 있다.

그림 1 (B)에 도시된 바와 같이, 돌출부(132)는 리세스(144) 상부로 연장된다. 그림 1B에 도시된 바와 같이, 리세스(144)는 개구(134)의 폭(D)보다 큰 폭(E)을 갖는다. 일 실시 예들에 있어서, 리세스(144)의 폭(E)은 리세스(144)의 최대 폭일 수 있고, 개구(134)의 폭(D)은 개구(134)의 최소 폭일 수 있다. 일 실시 예들에 있어서, 폭(D) 또는 폭(E)은 50 ㎛ 및 500 ㎛ 사이일 수 있다(예를 들면, 100 ㎛, 175 ㎛, 220 ㎛, 400 ㎛). 일 실시 예들에 있어서, 폭(D) 또는 폭(E)은 50 ㎛보다 작을 수 있거나 또는 500 ㎛보다 클 수 있다.

일 실시 예들에 있어서, 폭(D) 및 폭(E)의 차이는 대략 수 마이크로미터(예를 들면, 1 ㎛, 10 ㎛) 및 수 밀리미터(예를 들어, 0.3 mm, 0.4 mm, 1 mm, 2 mm) 사이일 수 있다. 일 실시 예들에 있어서, 폭(D) 및 폭(E)의 차이는 수 마이크로미터보다 작을 수 있거나, 수 밀리미터보다 클 수 있다. 일 실시 예들에 있어서, 폭(D) 및 폭(E)의 차이는 대략 그림 1 (A)에 도시된 깊이(Q)와 동일할 수 있다. 일 실시 예들에 있어서, 폭(D) 및 폭(E)의 차이는 깊이(Q)보다 클 수 있거나, 깊이(Q)보다 작을 수 있다.

일 실시 예들에 있어서, 폭(D) 또는 폭(E)은 대략 솔더 범프(160)(그림 1 (A)에 도시된)의 직경의 대략 50% 및 150% 사이일 수 있다. 예를 들면, 폭(D) 또는 폭(E)은 솔더 범프(160)의 직경의 대략 65%일 수 있다. 일 실시 예들에 있어서, 폭(D) 또는 폭(E)은 솔더 범프(160)의 직경의 대략 80%일 수 있다. 다른 예시로서, 폭(D) 또는 폭(E)은 솔더 범프(160)의 직경의 대략 105%일 수 있다.

그림 1 (A)를 다시 참조하면, 일 실시 예들에 있어서, 리세스(144)의 벽(143)은 그림 1 (A)에 도시된 것보다 큰 경사를 가질 수 있거나, 경사지지 않을 수 있다. 일 실시 예들에 있어서, 리세스(144)의 벽(143)은 그림 1 (A)에 도시된 것과 같이 개구(134)로부터 멀어지기보다는(바닥으로부터 상부까지) 개구(134)를 향하여 안쪽으로(바닥으로부터 상부까지) 경사질 수 있다. 일 실시 예들에 있어서, UBM층(140)의 리세스(144)의 바닥면(145)은 편평하지 않을 수 있다. 일 실시 예들에 있어서, 리세스(144)의 바닥면(145)은 개구(134)의 폭(예를 들면, 최소 폭)보다 큰 폭(예를 들면, 최대 폭)을 가질 수 있다.

그림 1 (A)에 도시된 바와 같이, 돌출부(132)는 삼각형(또는 뾰족한(pointed)) 단면 형상을 가진다. 일 실시 예들에 있어서, 돌출부(132)는 삼각형 단면 형상과는 다른 형상을 가질 수 있다. 다시 말하면, 개구(134)를 정의하는 벽들은 그림 1 (A)에 도시된 것과는 다른 프로파일을 가질 수 있다. 예를 들면, 비도전층(130) 내의 개구(134)를 정의하는 벽들은 수직할 수 있다(또는 실질적으로 수직할 수 있다). 이러한 실시 예들에서, 돌출부(132)의 단면 형상은 실질적으로 정사각형, 직사각형, 커브진 형상 또는 등등일 수 있다. 일 실시 예들에 있어서, 돌출부(132)는 개구(134)의 프로파일의 적어도 일부분을 정의할 수 있다. 일 실시 예들에 있어서, 비도전층(130) 내의 개구(134)를 정의하는 벽들은 그림 1 (A)에 도시된 것과 같이 개구(134)로부터 멀어지기보다는(바닥으로부터 상부까지) 개구(134)의 바닥부로부터 개구(134)의 상부까지 안쪽으로 경사질 수 있다(바닥 폭보다 작은 상부 폭을 가질 수 있다). 일 실시 예들에 있어서, 개구(134)를 정의하는 상기 벽들은 커브질 수 있고, 또는 등등일 수 있다.

일 실시 예들에 있어서, 캐비티(164)의 적어도 일부분, 및 그 내부에 배치된 솔더 범프(160)의 바닥부(162)의 상기 일부분이 각각 삼각형 단면 형상을 가질 수 있다. 일 실시 예들에 있어서, 캐비티(164) 또는 그 내부에 배치된 솔더 범프(160)의 바닥부(162)의 상기 일부분이 삼각형(또는 뾰족한) 단면 형상과 다른 형상을 가질 수 있다. 예를 들면, 캐비티(164) 또는 그 내부에 배치된 솔더 범프(160)의 바닥부(162)의 상기 일부분이 직사각형 또는 정사각형 단면 프로파일(만약 벽(143)이 경사지지 않는다면)을 가질 수 있다.