솔더 페이스트 침착물은 일반적으로 PCB와 집적 회로 패키지 사이에 도포된다. 솔더 페이스트 침착물은 집적 회로 패키지와 PCB 사이에 고체 접합(solid bond)을 형성하도록 처리되어, 전자 시스템 또는 전자 조립체를 형성할 수 있다. 처리는 일반적으로 냉각, 가열 또는 리플로우 프로세스를 수반할 수 있다. 접합 및 냉각 프로세스 동안, 솔더 페이스트의 플럭스 컴포넌트에서 가스를 제거(out-gassing)하는 것으로 인해 가스가 트랩(trapped) 될 수 있다. 임의의 특정 이론에 구애됨이 없이, 트랩된 가스 제거는 솔더 조인트에 하나 이상의 보이드 영역을 형성할 수 있다. PCB와 집적 회로 패키지 사이에 솔더 페이스트를 샌드위치하면 또한 솔더 조인트에 보이드 영역을 초래할 수 있다. 보이드는 종종 허용될 수 있으나 바람직하지 않다.

명세서

배경 기술

집적 회로 패키지는 일반적으로 고성능 전자 조립체를 제조할 때 인쇄 회로 보드와 같은 기판에 솔더링된다. 솔더 조인트에서 보이드는 조립체를 처리하는 동안 발생할 수 있다. 과도한 보이드는 전력 소비를 증가시키고, 동작 온도를 증가시키며, 전기적 성능을 감소시키고, 집적 회로 패키지에 전체적으로 고장을 야기하여 예상 수명에 이르게 할 수 있다.

발명의 내용

하나 이상의 측면에 따르면, 솔더 조인트에서 보이드의 형성을 감소시키는 방법은 솔더 페이스트 침착물(solder paste deposit)을 기판에 도포하는 단계, 솔더 프리폼(solder preform)을 상기 솔더 페이스트 침착물에 위치(placing)시키는 단계, 디바이스를 상기 솔더 프리폼 및 상기 솔더 페이스트 침착물 위에 배치(disposing)하는 단계 및 상기 솔더 페이스트 침착물 및 상기 솔더 프리폼을 처리하여 상기 디바이스 및 상기 기판 사이에 상기 솔더 조인트를 형성하는 단계를 포함할 수 있다.

일부 측면에서, 상기 기판은 인쇄 회로 보드이고 상기 디바이스는 집적 회로 패키지이다. 처리 단계는 상기 솔더 페이스트 침착물 및 상기 솔더 프리폼을 약 140℃ 내지 약 275℃의 범위의 온도로 가열하는 단계를 포함할 수 있다. 본 방법은 제2 솔더 프리폼을 상기 솔더 페이스트 침착물에 위치시키는 단계를 더 포함할 수 있다. 솔더 페이스트 침착물은 솔더 프리폼의 두께 이상의 두께로 도포될 수 있다. 상기 솔더 페이스트 침착물을 상기 기판에 도포하는 단계는 상기 솔더 페이스트를 상기 기판 위에 패턴으로 인쇄하는 단계를 포함한다. 상기 솔더 프리폼의 직경은 약 1㎜ 내지 약 15㎜일 수 있다. 상기 솔더 프리폼의 두께는 약 0.025㎜ 내지 약 0.2㎜일 수 있다. 솔더 프리폼은 적어도 약 99.9중량%의 순수 금속 또는 순수 금속 합금을 포함할 수 있다. 순수 금속 또는 순수 금속 합금은 주석, 은, 안티몬, 구리, 납, 니켈, 인듐, 팔라듐, 갈륨, 카드뮴 및 비스무스 중 적어도 하나를 포함할 수 있다. 일부 측면에서, 솔더 프리폼은 실질적으로 플럭스(flux)가 없다. 적어도 특정 측면에서, 솔더 조인트는 약 40면적% 미만의 보이드 공간을 특징으로 할 수 있다. 솔더 프리폼은 리플로우(reflow) 후에 솔더 조인트의 약 25% 내지 약 95체적(volume)%에 기여할 수 있다.

하나 이상의 측면에 따르면, 조립체는 인쇄 회로 보드, 상기 인쇄 회로 보드에 접합된 디바이스 및 상기 인쇄 회로 보드와 상기 디바이스 사이에 솔더 조인트를 포함할 수 있다. 솔더 조인트의 약 25% 내지 약 95체적%는 리플로우 후에 솔더 프리폼을 포함한다. 일부 측면에서, 상기 솔더 조인트는 주석, 은, 안티몬, 구리, 납, 니켈, 인듐, 팔라듐, 갈륨, 카드뮴 및 비스무스 중 적어도 하나를 포함한다. 솔더 조인트는 약 40면적% 미만의 보이드 공간을 특징으로 한다.

하나 이상의 측면에 따르면, 디바이스를 인쇄 회로 보드에 조립하는 키트는 솔더 페이스트 및 약 1㎜ 내지 약 15㎜의 직경과 약 0.025㎜ 내지 0.2㎜의 두께를 구비하는 적어도 하나의 솔더 프리폼을 포함할 수 있고, 상기 적어도 하나의 솔더 프리폼은 적어도 약 99.9중량%의 순수 금속 또는 순수 금속 합금을 포함할 수 있다. 일부 측면에서, 상기 적어도 하나의 솔더 프리폼은 테이프 앤 릴 패키징(tape and reel packaging) 위에 배치된다. 다른 측면에서, 상기 적어도 하나의 솔더 프리폼은 픽 앤 플레이스 처리(pick and place treatment)를 위한 트레이(tray) 위에 배치된다. 더 다른 측면에서, 상기 적어도 하나의 솔더 프리폼은 자동화된 및 기계 준비된 패키징(automated and/or machine-ready packaging)으로 패키징된다.

하나 이상의 측면에 따르면, 솔더 조인트에서 보이드를 감소시키는 방법은 솔더 프리폼을 제공하는 단계 및 솔더 조인트를 형성하는 리플로우 전에 상기 솔더 프리폼을 인쇄 회로 보드 위 솔더 페이스트 침착물에 도포하는 명령을 제공하는 단계를 포함할 수 있다. 일부 측면에서, 상기 방법은 솔더 페이스트를 제공하는 단계를 더 포함할 수 있다.

하나 이상의 측면에 따르면, 인쇄 회로 보드와 집적 회로 패키지 사이에 솔더 조인트는 약 40면적% 미만의 보이드 공간을 특징으로 할 수 있고, 솔더 조인트의 약 25% 내지 약 95체적%는 리플로우 후에 솔더 프리폼을 포함할 수 있다. 이들 예시적인 측면 및 실시예의 더 다른 측면, 실시예, 및 장점은 아래에 상세히 설명된다. 더욱이, 전술된 정보 및 이하 상세한 설명은 여러 측면 및 실시예의 단지 예시적인 예들이고, 청구된 측면 및 실시예의 특성과 특징을 이해하기 위한 개요 또는 구조를 제공하려고 의도된 것으로 이해된다. 첨부 도면은 여러 측면 및 실시예를 예시하고 이를 더 잘 이해하기 위해 포함된 것이며, 본 명세서의 일부를 형성한다. 도면은, 본 명세서의 나머지 부분과 함께, 설명 및 청구된 측면 및 실시예의 원리와 동작을 설명하는 기능을 한다.

발명을 실시하기 위한 구체적인 내용

하나 이상의 실시예에 따르면, 솔더 조인트에서 보이드는 솔더 조인트의 강도를 유지하면서 감소될 수 있다. 보이드 감소는 전자 조립체에서 집적 회로 패키지의 무결성과 수명을 개선시킬 수 있다. 유리하게는, 솔더 조인트에서 보이드를 감소시키면 열 발산을 개선시키고 집적 회로 패키지의 전력 소비를 감소시킬 수 있다. 개선된 전기적 성능은 인식될 수 있다. 집적 회로 패키지의 신뢰성은 또한 개선될 수 있다. 또한 조립 동작 동안 배치(disposal) 또는 재작업(rework)을 요구하는 집적 회로 패키지의 수를 감소시키는 것에 의해 비용 절감이 인식될 수 있다.

하나 이상의 실시예에 따르면, 전자 조립체를 제조하는 기존의 시스템 및 방법은 솔더 조인트에서 보이드를 감소시키도록 용이하게 개조될 수 있다. 하나 이상의 실시예에 따르면, 솔더 프리폼은 솔더 조인트에서 보이드를 감소시키는데 사용될 수 있다. 일부 비제한적인 실시예에서, 솔더 조인트는 약 50면적% 미만의 보이드 공간을 특징으로 할 수 있다. 적어도 일부 비제한적인 실시예에서, 솔더 조인트는 약 35% 미만의 보이드 공간을 특징으로 할 수 있다.

하나 이상의 실시예에 따르면, 제1 요소는 제2 요소와의 사이에 조인트를 사이에 형성하도록 제2 요소와 접합될 수 있다. 일부 실시예에서, 제1 요소는 집적 회로 패키지일 수 있고 제2 요소는 인쇄 회로 보드(PCB)와 같은 기판일 수 있다. 다른 기판이 구현될 수 있다. 특정 실시예에서, 전자 조립체는 일반적으로 PCB에 접합된 적어도 하나의 집적 회로 패키지를 포함할 수 있다. 일부 전자 조립체는 PCB에 접합된 복수의 집적 회로를 포함할 수 있다. 집적 회로 패키지는, LGA(Land Grid Array), DFN(Duel Flat No lead), QFP(Quad Flat Package), QFN(Quad Flat No lead), LQFP(Low-Profile Quad Flat Package) 및 MLF(Micro Lead Frame)와 같은 임의의 전자 디바이스 또는 패키지일 수 있으나 이들로 제한되지 않는다. 적어도 하나의 대안적인 실시예에서, 제1 및 제2 요소는 대신 조립될 집적 회로 패키지 또는 다른 컴포넌트의 제1 및 제2 요소일 수 있다. 보이드를 감소시키는 것과 관련된 다른 제1 및 제2 요소가 여러 실시예에 따라 구현될 수 있다.

하나 이상의 실시예에 따르면, 제1 요소는 접착제, 수지 또는 솔더와 같은 여러 물질을 사용하여 제2 요소에 접합될 수 있다. 솔더 페이스트는 일반적으로 집적 회로 패키지를 PCB와 같은 기판에 접합하는데 사용된다. 솔더 페이스트는 일반적으로 금속 또는 금속 합금을 포함할 수 있다. 솔더 페이스트는 또한 일반적으로 플럭스로 알려진 하나 이상의 솔더링제(soldering agent)를 포함할 수 있다. 플럭스는 하나 이상의 화학적 클리닝제(chemical cleaning agent) 및 습윤제(wetting agent)를 포함할 수 있다. 클리닝제로서, 플럭스는 접합될 금속면으로부터 산화종(oxidation species)을 제거하는 것에 의해 솔더링을 제공할 수 있다. 습윤제로서, 플럭스는 가공부품(work piece)에 솔더를 흐르게 하여, 비드(bead)의 형성을 방지하고 가공부품의 표면을 효과적으로 습윤화할 수 있다.

솔더 페이스트 침착물은 일반적으로 PCB와 집적 회로 패키지 사이에 도포된다. 솔더 페이스트 침착물은 집적 회로 패키지와 PCB 사이에 고체 접합(solid bond)을 형성하도록 처리되어, 전자 시스템 또는 전자 조립체를 형성할 수 있다. 처리는 일반적으로 냉각, 가열 또는 리플로우 프로세스를 수반할 수 있다. 접합 및 냉각 프로세스 동안, 솔더 페이스트의 플럭스 컴포넌트에서 가스를 제거(out-gassing)하는 것으로 인해 가스가 트랩(trapped) 될 수 있다. 임의의 특정 이론에 구애됨이 없이, 트랩된 가스 제거는 솔더 조인트에 하나 이상의 보이드 영역을 형성할 수 있다. PCB와 집적 회로 패키지 사이에 솔더 페이스트를 샌드위치하면 또한 솔더 조인트에 보이드 영역을 초래할 수 있다. 보이드는 종종 허용될 수 있으나 바람직하지 않다.

집적 회로 패키지는 일반적으로 동작 동안 열을 생성한다. 집적 회로 패키지가 열을 효과적으로 발산할 수 없으면, 이 패키지는 성능이 저하되거나 또는 열 손상을 받을 수 있다. 많은 집적 회로 패키지는 하부면과 연관된 것과 같은 열을 발산하는 열 경로를 사용한다. 열 경로는 종종 써멀 패드를 포함할 수 있다. 써멀 패드는 PCB에 솔더링되어, 집적 회로 패키지로부터 PCB의 접지면으로 열을 전달하는 메커니즘을 제공할 수 있다. 집적 회로 패키지를 PCB에 접합하면 집적 회로 패키지로부터 PCB로 플로우 경로를 따라 열을 전달할 수 있다. 접착 수지 및 솔더는 일반적으로 우수한 열 전도도를 구비하고, 집적 회로 패키지로부터 PCB로 열을 전달하는 기능을 한다. 추가적으로, 솔더는 집적 회로 패키지를 전기적으로 접지하는 것을 도와주는 우수한 전기 전도도를 구비한다. 임의의 특정 이론에 구애됨이 없이, 보이드 형성은 집적 회로 패키지와 PCB 사이에 조인트의 열 전도도 및 전기 전도도 중 적어도 하나를 손상시킬 수 있다. 집적 회로는 또한 불량한 전기적 접지 무결성의 결과 고주파수 신호의 전기적 성능이 감소될 수 있다.

산업적인 조립체 라인 장비 및 방법은 다수의 전자 조립체를 효과적으로 생산하는 기계화된 프로세스를 제공한다. 솔더 조인트에서 일정 보이드율은 허용될 수 있으나, 실장된 집적 회로 패키지와 PCB 사이에 솔더 조인트에서 과도한 보이드가 존재하면, 많은 조립체들이 하나 이상의 동작 사양, 또는 IPC(Association Connecting Electronics Industries) 또는 다른 관련 표준 설정 기구(standards-setting organization)에서 설정된 것과 같은 산업 표준을 충족하지 못할 수 있다. 과도한 보이드로 인한 이러한 실패는 재작업, 컴포넌트 스크랩 율(scrap rate) 및 PCB 스크랩 율로 인해 다수의 제조 비용을 증가시킬 수 있다. 상대적으로 긴 수명을 가지는 것으로 예상되는 하이 엔드 컴포넌트와 관련된 특정 경우에, 보이드 형성을 감소시키는 것과 관련된 하나 이상의 실시예는 상대적으로 낮은 비용을 보장하여 이러한 컴포넌트들이 예상된 수명 동안 동작할 수 있게 한다. 컴포넌트의 예상된 수명이 상대적으로 짧을 수 있는 다른 실시예에서, 보이드 감소는 그럼에도 불구하고 집적 회로 패키지의 연관된 전력 발산을 저하시키는 것에 의해 이익을 제공할 수 있다. 집적 회로 패키지가 모바일 폰과 같이 배터리에 의해 전력 공급받는 경우, 전력 발산이 낮으면 배터리 수명이 길어진다. 따라서 보이드가 감소하면 구체적으로 배터리로 전력 공급되는 집적 회로 기술 또는 일반적으로 전력 소비를 보존하려는 노력과 관련하여 유리한 응용에 사용될 수 있다. 그리하여 하나 이상의 실시예에 따라 보이드를 감소시키는 반복 가능한 체계적인 접근법은 다수의 레벨의 제조 프로세스에서 전체 효율을 개선시킬 수 있다.

하나 이상의 실시예에 따르면, 솔더 조인트에서 형성된 보이드 공간을 감소시키는 시스템 및 방법은 하나 이상의 솔더 프리폼의 사용을 수반할 수 있다. 일부 실시예에서, 솔더 페이스트 및 하나 이상의 솔더 프리폼의 조합이 사용될 수 있다. 적어도 하나의 실시예에서, 용융된 솔더 조인트에서 플럭스의 양이 감소될 수 있다. 일부 실시예에서, 적어도 하나의 프리폼은 리플로우 전에 솔더 조인트에서 솔더 페이스트의 적어도 일 부분을 대체하여 존재하는 플럭스의 양을 감소시키는데 사용될 수 있다. 일부 실시예에서, 솔더 페이스트를 감소시키고 프리폼을 추가하여 보이드를 체계적으로 감소시킬 수 있다. 솔더 조인트의 무결성과 강도가 유지될 수 있다. 일부 실시예에서, 리플로우 전에 솔더 조인트에 존재하는 솔더 페이스트와 프리폼의 상대적인 양은 보이드 형성을 원하는 대로 감소시키면서 솔더 조인트의 무결성을 보장하도록 선택될 수 있다.

하나 이상의 실시예에 따르면, 최종 솔더 조인트는 감소된 보이드 공간을 구비할 수 있다. 나아가, 하나 이상의 실시예에 따라 시스템 및 방법은 새로운 캐피탈 장비(new capital equipment)의 구매를 요구함이 없이 산업적인 규모로 적용될 수 있다. 대신, 기존의 제조 시스템 및 방법은 하나 이상의 실시예에 따라 개조될 수 있다. 예를 들어, 프리폼은 테이프 앤 릴 패키징 또는 픽 앤 플레이스 트레이 위에 위치되어, 프리폼이 표준 자동화된 프로세스에 용이하게 병합될 수 있게 한다. 하나 이상의 프리폼과 관련하여 솔더 페이스트를 사용하면 앵커링(anchoring)을 용이하게 할 수 있다. 본 명세서에 상술된 바와 같이 솔더 페이스트와 관련하여 하나 이상의 프리폼을 사용하면 프리폼을 고정(fixture)하거나 앵커링할 수 있어, 프리폼 및 집적 회로 패키지를 조립체 라인을 따라 진행하는 동안 제 위치에 유지할 수 있다.

본 명세서에 개시된 특정 측면 및 예들은 솔더 조인트에서 보이드 공간을 감소시키거나 또는 보이드 공간을 감소시키는 것을 용이하게 하는 방법, 조립체 및 키트를 제공한다. 하나 이상의 실시예는 보이드를 감소시키는 시스템 및 방법에 관한 것이다. 일부 특정 실시예는 솔더 페이스트 및 솔더 프리폼을 솔더 조인트를 형성하도록 구현하는 보이드 형성을 감소시키는 시스템 및 방법에 관한 것이다. 적어도 특정 실시예는 솔더 페이스트 및 솔더 프리폼을 조합으로 사용하여 솔더 조인트에 보이드 형성을 감소시키는 방법에 관한 것이다. 일부 비제한적인 실시예는 솔더 조인트에 의해 PCB에 접합된 집적 회로 패키지를 포함하는 조립체에 관한 것이다. 처리 또는 리플로우 전에 솔더 조인트는 솔더 페이스트 및 적어도 하나의 솔더 프리폼을 포함할 수 있다. 다른 비제한적인 실시예는 집적 회로 패키지를 PCB에 조립하는 키트에 관한 것이다. 이 키트는 솔더 페이스트 및 적어도 하나의 솔더 프리폼을 포함할 수 있다. 솔더 조인트에서 보이드를 감소시키는 것은 솔더 프리폼를 제공하고 이 솔더 조인트를 형성하는 처리 또는 리플로우 전에 솔더 프리폼을 인쇄 회로 보드 위 솔더 페이스트 침착물에 도포하는 명령을 제공하는 것에 의해 제공될 수 있다.

하나 이상의 실시예에 따르면, 솔더 조인트에서 보이드 형성을 감소시키는 방법은 솔더 페이스트 침착물을 기판에 도포하는 것을 수반할 수 있다. 기판은 예를 들어, PCB일 수 있다. 임의의 솔더 페이스트는 의도된 응용에 따라 사용될 수 있다. 전술된 바와 같이 솔더 페이스트는 일반적으로 하나 이상의 금속 또는 금속 합금 및 하나 이상의 플럭스제(flux agent)를 포함할 수 있다. 일부 실시예에서, 솔더 페이스트는 주석, 은, 안티몬, 구리, 납, 니켈, 인듐, 팔라듐, 갈륨, 카드뮴 및 비스무스 중 적어도 하나를 포함할 수 있다. 일부 비제한적인 실시예에서, 솔더 페이스트 물질은 일반적으로 솔더 페이스트에 배치되는 프리폼 물질과 동일할 수 있으나, 이것이 엄격히 필요한 것은 아니다. 일부 비제한적인 실시예에서, Cookson Electronics社로부터 상업적으로 이용가능한 임의의 솔더 페이스트가 사용될 수 있다. 본 명세서에 상술된 솔더 페이스트 및 프리폼에 사용될 수 있는 합금의 비제한적인 예로는 Sn/Ag/Cu; Sn/Ag/Cu/Ni; Sn/Ag/Cu/Ni/Bi; Sn/Ag; Sn/Ag/Cu/Bi; Sn/Bi; Sn/Bi/Ag; Sn/Bi/Ag/Ni; Sn/Bi/Ag/Cu; Sn/Pb; Sn/In; 및 Sn/Pb/Ag를 포함할 수 있다.

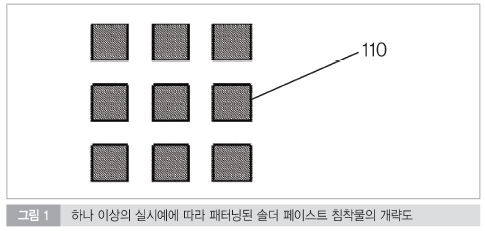

하나 이상의 실시예에 따르면, 솔더 페이스트는 인쇄 방법과 같은 여러 알려진 기술로 기판에 도포될 수 있다. 일부 실시예에서, 솔더 페이스트는 단일 침착물로 도포될 수 있다. 기판 위 침착물의 치수 및 체적은 기판에 접합될 집적 회로 패키지의 사이즈 또는 의도된 최종 솔더 조인트의 사이즈에 대응할 수 있다. 일부 비제한적인 실시예에서, 솔더 페이스트 침착물의 체적은 처리 후 최종 솔더 조인트의 체적의 약 2배일 수 있다. 다른 실시예에서, 솔더 페이스트는 단일 침착물에 도포되는 것이 아니라 임의의 원하는 패턴으로 도포될 수 있다. 스텐실(stencil) 또는 다른 기술을 사용하여 원하는 패턴을 생성할 수 있다. 예를 들어, 솔더 페이스트(110)는 그림 1에 도시된 바와 같이 격자 패턴(lattice pattern) 또는 창문 패턴(window pattern)으로 도포될 수 있다. 일부 비제한적인 실시예에서, 솔더 페이스트는 일반적으로 PCB와 같은 기판에 매립된 전도성 컨택(contact)의 패턴과 매칭하는 패턴으로 배치될 수 있다. 임의의 특정 이론에 구애됨이 없이, 솔더 페이스트의 패터닝은 사용되는 솔더 페이스트의 전체 체적을 감소시킬 수 있고, 처리 동안 솔더 페이스트에 존재하는 휘발성 플럭스에서 가스를 제거하는(out-gassing) 경로를 제공하여 보이드 형성의 감소에 기여할 수 있다. 솔더 페이스트는 임의의 원하는 두께로 도포될 수 있다. 적어도 일부 실시예에서, 솔더 페이스트 침착물의 두께는 일반적으로 솔더 페이스트 침착물에 위치될 프리폼의 두께 이상일 수 있다. 일부 비제한적인 실시예에서, 하나 이상의 프리폼이 삽입될 수 있어, 도포된 솔더 페이스트 패턴에 의해 보이드로 남아있는 체적에 기여할 수 있다. 스텐실의 두께는 원하는 솔더 높이에 따라 달라질 수 있고, 컴포넌트 피치(pitch), 애스펙트 비율(aspect ratio) 및 다른 인자에 의해 영향을 받을 수 있다. 일부 실시예에서, 솔더 페이스트를 큰 써멀 패드(large thermal pad)의 코너에 인쇄하고 하나 이상의 프리폼을 이 써멀 패드의 중심 쪽으로 삽입하는 것이 바람직할 수 있다. 베이스 층(base layer)이 또한 프리폼 아래에 도포될 수 있다.

하나 이상의 실시예에 따르면, 하나 이상의 솔더 프리폼은 기판 위 솔더 페이스트 침착물에 위치될 수 있다. 솔더 프리폼은 의도된 응용에 따라 하나 이상의 금속 또는 금속 합금을 포함할 수 있다. 솔더 프리폼은 일반적으로 예를 들어, 솔더 페이스트가 아니라 프리폼 고체(preformed solid)일 수 있다. 프리폼에 사용될 수 있는 금속의 일부 예로는 주석, 은, 안티몬, 구리, 납, 니켈, 인듐, 팔라듐, 갈륨, 카드뮴 및 비스무스를 포함하나 이들로 제한되지 않는다. 솔더 프리폼은 의도된 응용에 따라 임의의 사이즈 및 형상일 수 있다. 일부 실시예에서, 프리폼은 일반적으로 디스크 형상일 수 있다. 프리폼은 임의의 원하는 두께를 구비할 수 있다. 일부 실시예에서, 프리폼은 프리폼이 위치되는 솔더 페이스트의 침착물보다 일반적으로 더 얇을 수 있다. 프리폼은 기판에 접합되는 컴포넌트 또는 디바이스 아래에 끼워 맞춰질 만큼 충분히 얇을 수 있다. 일부 비제한적인 실시예에서, 프리폼의 두께는 약 0.025밀리미터 내지 0.2밀리미터일 수 있다. 마찬가지로, 프리폼은 임의의 원하는 직경일 수 있다. 일부 실시예에서, 접합되는 집적 회로 패키지의 치수 또는 사용되는 기판의 특성은 프리폼의 사이즈에 영향을 미칠 수 있다. 일부 비제한적인 실시예에서, 디스크 형상의 프리폼은 약 1㎜ 내지 15㎜ 직경을 구비할 수 있다. 일부 실시예에서, 구현되는 프리폼은 Cookson Electronics社로부터 상업적으로 이용 가능한 임의의 Alpha(등록상표) Exactalloy(등록상표) 솔더 프리폼일 수 있다.

하나 이상의 실시예에 따르면, 솔더 프리폼은 실질적으로 플럭스가 없을 수 있다. 일부 비제한적인 실시예에서, 솔더 프리폼은 적어도 99%의 순수 금속 또는 순수 금속 합금일 수 있다. 일부 실시예에서, 솔더 프리폼은 약 99.9%의 순수 금속 또는 순수 금속 합금일 수 있다. 적어도 일부 실시예에서, 솔더 프리폼은 약 99.99%의 순수 금속 또는 순수 금속 합금일 수 있다. 하나 이상의 실시예에 따르면, 특정 플럭스가 아니라, 솔더 프리폼은 처리 또는 리플로우를 지원하는 주변 솔더 페이스트에 존재하는 플럭스에 의존할 수 있다. 따라서 솔더 조인트의 무결성 및 강도는 보이드를 감소시키면서 유지될 수 있다. 일부 특정 비제한적인 실시예에서, 실질적으로 플럭스-없는 프리폼이 솔더 페이스트 플럭스 코팅과 복합화(complexed)될 수 있다. 프리폼은 플럭스 고체로 코팅될 수 있다. 임의의 특정 이론에 구애됨이 없이, 이러한 코팅은 프리폼의 완전한 리플로우를 보장하고, 또한 후-처리 기판에 집적 회로 패키지의 강력한 저보이드 연결을 제공할 수 있다. 따라서 솔더 프리폼 및 솔더 페이스트의 조합의 사용에 대한 대안으로, 보이드 감소는 또한 일부 비제한적인 실시예에서 플럭스로 프리폼을 코팅하는 것에 의해 달성될 수 있다. 일반적으로, 프리폼 위에 플럭스 코팅의 양을 최소화하여 보이드를 감소시키는 것이 바람직할 수 있다. 프리폼이 페이스트에 사용되는 솔더 파우더(powder)보다 훨씬 더 작은 표면적을 구비하므로, 훨씬 더 적은 플럭스가 유효 솔더링에 요구될 수 있다. 솔더 페이스트가 프리폼과 관련하여 사용되지 못할 수 있는 비제한적인 예에서, 프리폼은 대신 예를 들어, 집적 회로 패키지로부터 PCB로 연장되는 리드(lead)에 의해 고정되거나, 앵커링되거나 또는 제 위치에 유지될 수 있다. 일부 실시예에서, 집적 회로 패키지의 리드는 솔더 페이스트에 위치될 수 있고, 플럭스 코팅된 프리폼은 처리 전에 집적 회로 패키지의 써멀 패드와 컨택하여 위치될 수 있다. 하나 이상의 실시예에 따르면, 프리폼은 플럭스 코팅될 수 있다. 플럭스 코팅된, 테이프 앤 릴 프리폼은 일반적으로 하나 이상의 실시예에 따라 구현될 수 있다.

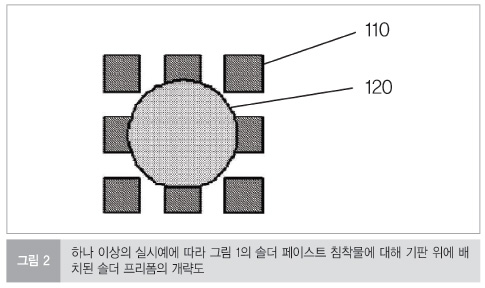

선형(직선 램프)

일부 비제한적인 실시예에서, 단일 프리폼은 솔더 페이스트 침착물의 중심에 위치될 수 있다. 다른 실시예에서, 단일 솔더 프리폼은 일반적으로 오프셋(offset)될 수 있다. 일부 실시예에서, 2개 이상의 프리폼은 단일 솔더 페이스트 침착물에서 사용될 수 있다. 다른 실시예에서, 솔더 프리폼은 솔더 페이스트 패턴의 각 컴포넌트에 위치될 수 있다. 솔더 페이스트 침착물에 대해 솔더 프리폼의 개수와 위치는 일반적으로 솔더 페이스트 침착물의 패터닝 및 조립체에 접합되는 집적 회로 패키지의 사이즈와 같은 안자에 따라 달라질 수 있다. 그림 2는 솔더 페이스트에 위치된 프리폼(120)을 갖는 ‘창문’ 패턴으로 도포된 솔더 페이스트(110)를 도시한다. 임의의 특정 이론에 구애됨이 없이, 솔더 페이스트는 처리 동안 시프트(shifting)를 피하기 위해 프리폼(들)을 제 위치에 유지하거나 고정하는 기능을 할 수 있다. 일부 실시예에서, 집적 회로 패키지와 연관된 리드 또는 레그(leg)는 집적 회로 패키지가 PCB에 앵커링될 수 있도록 조립체를 정렬하는 것을 도와줄 수 있다.

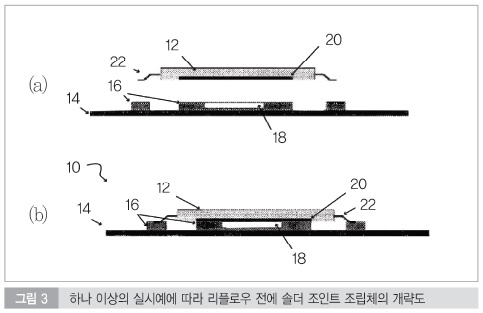

하나 이상의 실시예에 따르면, 집적 회로 패키지와 같은 컴포넌트 또는 디바이스는 침착된 솔더 페이스트 및 프리폼 위에 배치될 수 있다. 일부 실시예에서, 디바이스는 리플로우 전에 솔더 페이스트 및 프리폼의 조합 위에 배치될 수 있다. 리플로우 전에, 솔더 조인트 컴포넌트는 그리하여 접합되는 컴포넌트와 기판 사이에 샌드위치될 수 있다. 그림 3은 하나 이상의 실시예에 따라 리플로우 전의 조립체의 측면도를 도시한다. 그림 3의 (a)는 솔더 페이스트 및 솔더 프리폼의 조합 위에 디바이스를 배치하기 전에 여러 컴포넌트의 위치를 도시한다. 그림 3의 (b)는 처리 단계 전에 그림 3의 (a)의 컴포넌트의 위치를 도시한다. 일반적으로 그림 3의 (b)에 일반적으로 (10)으로 지시된 조립체는 인쇄 회로 보드(14)를 포함한다. 솔더 페이스트(16)의 침착물은 인쇄 회로 보드(14)에 도포된다. 솔더 페이스트(16)에는 솔더 프리폼(18)이 배치된다. 집적 회로 패키지(12)는 솔더 페이스트(16) 및 솔더 프리폼(18)에 도포된다. 집적 회로 패키지(12)의 써멀 패드(20)는 적어도 솔더 페이스트(16)와 컨택한다. 솔더 페이스트(16)는 또한 집적 회로 패키지(12)와 연관될 수 있는 리드 와이어(22)와 컨택한다. 프리폼(18)은 패키지(12) 아래에 끼워 맞춰질 만큼 충분히 얇을 수 있다. 후술되는 바와 같이 처리 후에, 솔더 페이스트(16) 및 솔더 프리폼(18)은 집적 회로 패키지(12)를 인쇄 회로 보드(14)에 접합하는 솔더 조인트를 형성할 수 있다. 일부 바람직한 실시예에서, 솔더 조인트의 약 25% 내지 약 95체적%는 리플로우 후에 솔더 프리폼을 포함할 수 있다.

하나 이상의 실시예에 따르면, 조립체는 집적 회로 패키지와 PCB와 같은 기판 사이에 솔더 조인트를 형성하도록 처리될 수 있다. 처리는 일반적으로 가열 및 냉각을 수반할 수 있다. 솔더 프리폼은 가열되어 용융되어 솔더 페이스트와 복합화된 후에, 냉각되어 기판과 집적 회로 패키지 사이에 고체 솔더 조인트를 형성할 수 있다.

처리 단계는 일부 비제한적인 실시예에서 솔더 페이스트 침착물 및 솔더 프리폼을 약 140℃ 내지 약 275℃의 범위의 온도로 가열하는 단계를 포함 수 있다. 솔더는 냉각되고 응고되어 고체 접합(solid bond)을 형성할 수 있다.

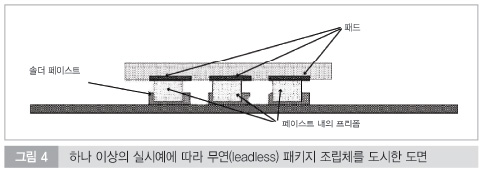

하나 이상의 비제한적인 실시예에 따르면, 프리폼 두께는 솔더 페이스트와 디바이스 사이에 상호작용을 나타낼 수 있다. 일부 실시예에서, 컴포넌트 써멀 패드는 프리폼이 프리폼의 두께에 따라 붕괴될(collapse) 때까지 플럭스와 컨택하지 않을 수 있다. 이것은 솔더 페이스트의 플럭스가 써멀 패드를 환원(deoxidize)시킬 기회가 적도록 컨택 시간을 감소시킬 수 있다. 리드를 갖는 컴포넌트를 수반하는 일부 실시예에서, 상대적으로 얇은 프리폼은 솔더 페이스트와 관련하여 사용될 수 있고, 컴포넌트 리드는 인쇄된 페이스트와 여전히 컨택할 수 있어, 리플로우 전에 리드-솔더 페이스트 컨택 및 써멀 패드-솔더 페이스트 컨택으로 컴포넌트를 PCB에 앵커링할 수 있다. 이러한 실시예에서, 솔더 페이스트보다 더 두꺼운 프리폼을 사용하는 것은 컴포넌트의 리드들이 솔더 페이스트와 컨택하지 않아서 문제시될 수 있고, 처리 후에는 솔더 페이스트와 패드 및 리드가 정렬되지 않을 수 있다. 그러나 바닥면에만 다수의 패드를 포함하는 LGA와 같은 그림 4에 도시된 무연 패키지를 수반하는 일부 실시예에서는, 솔더 페이스트 침착물보다 더 두꺼운 프리폼을 사용하여 리플로우 후에 감소된 보이드와 적절한 컴포넌트-PCB 정렬을 여전히 달성할 수 있다. 이것은 상대적으로 대략적인 고정으로 달성될 수 있다. 컴포넌트 패드의 배향이 고정부로 보드 패드에 대해 유지된다면, 처리 동안, 프리폼은 용융된 솔더로 붕괴될 수 있고, 컴포넌트는 보드 패드로 낮아질 수 있다. 컴포넌트 패드 위 솔더의 모세관 동작 및 습윤 동작으로 인해 컴포넌트가 자체 배향되는 경향이 있는 자가 정렬이 일정 양 발생한다. 표면 실장 패드만을 고려하면, 고정부는 상대적으로 저가이지만, 후처리에 허용 가능한 컴포넌트 위치를 달성하기에 적합하다.

하나 이상의 실시예에 따르면, 조립체는 인쇄 회로 보드, 이 인쇄 회로 보드에 접합된 컴포넌트 또는 디바이스 및 이 인쇄 회로 보드 및 디바이스를 접합시키는 솔더 조인트를 포함할 수 있다. 하나 이상의 실시예에 따르면 솔더 조인트의 약 25% 내지 약 95체적%는 리플로우 또는 처리 후에 솔더 프리폼으로 구성될 수 있다. 보이드 공간의 감소의 측정은 처리 전에 솔더 조인트에 솔더 페이스트의 적어도 일부를 대체하도록 솔더 프리폼을 사용하여 검출될 수 있다. 일부 비제한적인 실시예에서, 솔더 프리폼은 리플로우 후에 솔더 조인트의 10체적%만큼 적게 구성할 수 있다. 일부 실시예에서, 솔더 프리폼은 리플로우 전에 솔더 조인트의 약 25% 내지 약 95체적%를 구성할 수 있다. 다른 실시예에서, 솔더 프리폼은 리플로우 후에 솔더 조인트의 약 25% 내지 약 80체적%에 기여할 수 있다. 더 다른 실시예에서, 솔더 프리폼은 리플로우 후에 솔더 조인트의 약 50% 내지 약 80체적%를 구성할 수 있다. 일부 비제한적인 실시예에서, 하나 이상의 실시예에 따라 형성된 솔더 조인트는 약 50면적% 미만의 최종 보이드 공간을 특징으로 할 수 있다. 더 다른 실시예에서, 솔더 조인트는 약 40면적% 미만의 최종 보이드 공간을 특징으로 할 수 있다. 일부 실시예에서, 솔더 조인트는 약 35면적% 미만의 최종 보이드 공간을 특징으로 할 수 있다. 일부 비제한적인 실시예에서, 솔더 조인트는 약 30면적% 미만의 최종 보이드 공간을 구비할 수 있다. 적어도 일부 실시예에서, 솔더 조인트는 약 20면적% 미만의 최종 보이드 공간을 구비할 수 있다. 특정 비제한적인 실시예에서, 솔더 조인트는 약 10면적% 미만의 최종 보이드 공간을 구비할 수 있다. 보이드 공간은 솔더 조인트의 x-선 사진에 의하여 또는 다른 이미징 기술에 의하여 측정될 수 있다. 일부 실시예에서, 보이드인 솔더 조인트의 총 면적의 비율은 일반적으로 솔더 조인트의 보이드 공간 면적 퍼센트를 나타낼 수 있다.

하나 이상의 실시예에 따르면, 솔더 조인트에 포함되기 전에, 프리폼은 상이한 형태의 패키징으로 배치되어 인쇄 회로 보드와 같은 기판 위에 프리폼의 자동화된 위치(placement)를 용이하게 한다. 예를 들어, 프리폼은 테이프 앤 릴 패키징 또는 픽 앤 플레이스 트레이 위에 위치될 수 있다.

상기 측면은 집적 회로 패키지가 PCB에 접합된 응용으로 제한되지 않는다. 전술된 바와 같이, 여러 제1 및 제2요소는 본 명세서에 상술된 기술로 접합될 수 있다. 예를 들어, 일부 비제한적인 실시예에서 프리폼과 솔더 페이스트의 조합은 단일 집적 회로 패키지의 컴포넌트를 접합하는데 사용될 수 있다. 집적 회로 패키지 내 솔더링된 조인트는 바람직하게는 낮은 보이드 및 집적 회로 패키지를 기판에 접합하는 후속 처리 동안 리플로우에 저항할 수 있는 능력을 특징으로 할 수 있다. 이 후속 가열 프로세스에 저항하는 것은 예를 들어, 적절한 솔더 페이스트 및 솔더 프리폼 합금을 선택하여 집적 회로 패키지 내에 솔더 조인트의 납 함량을 증가시키는 것에 의해 달성될 수 있다.

하나 이상의 실시예에 따르면, 디바이스를 인쇄 회로 보드에 조립하는 키트가 제공될 수 있다. 키트는 솔더 페이스트 및 적어도 하나의 솔더 프리폼을 포함할 수 있다. 일부 비제한적인 실시예에서, 프리폼은 약 1㎜ 내지 약 15㎜의 직경 및 약 0.025㎜ 내지 0.2㎜의 두께를 구비할 수 있다. 특정 비제한적인 실시예에서, 솔더 프리폼은 적어도 약 99.9중량%의 순수 금속 또는 순수 금속 합금일 수 있고, 나머지 0.1%는 불순물 및 트레이스 요소로 구성될 수 있다. 적어도 하나의 실시예에서, 솔더 프리폼은 적어도 약 99.99중량%의 순수 금속 또는 순수 금속 합금일 수 있고, 나머지 0.01%는 불순물 및 트레이스 요소로 구성될 수 있다. 높은 순도의 금속 또는 금속 합금은 불순물이 예를 들어, 습윤 교란에 의하여 조인트 형성과 간섭하는 것으로 인해 보이드 성능을 개선시킬 수 있다. 키트는 또한 솔더 조인트를 형성하는 리플로우 전에 솔더 프리폼을 인쇄 회로 보드 위 솔더 페이스트 침착물에 도포하는 명령을 포함할 수 있다.

하나 이상의 다른 실시예에 따르면, 솔더 조인트에서 보이드를 감소시키는 방법은 솔더 프리폼을 제공하는 단계 및 이 솔더 조인트를 형성하는 리플로우 전에 솔더 프리폼을 인쇄 회로 보드 위 솔더 페이스트 침착물에 도포하는 명령을 제공하는 단계를 포함할 수 있다.

실시예 1

30㎟ 써멀 패드를 구비하는 컴포넌트 및 보드로부터 0.05-0.10㎜ 스탠드오프(standoff) 및 2㎜ 또는 4㎜ 프리폼에 실험이 수행되었다. 일반적인 두께, 약 0.062 인치의 FR4 유리 에폭시 인쇄 회로 보드가 사용되었다. 보드 마무리(finish)는 유기면 보호제(organic surface protectant: OSP)이었다. 사용된 솔더 페이스트는 SAC305 유형 4 파우더였다. 디스크 형상의 프리폼은 0.1㎜ 두께를 가지는 치수 4㎜ 직경 및 0.1㎜ 두께를 가지는 2㎜ 직경을 구비하는 SAC305 합금이었다. 사용되는 리플로우 프로파일은 산업에서 사용된 것을 나타내는 직선 램프(straight ramp)(온도 대 시간) 및 침지 프로파일(soak profile)이었다. 인쇄된 페이스트 패턴은 프리폼 없는 100% 커버리지(대조군)와, 패드 면적의 20% 미만으로 50%의 커버리지를 구비하는 인쇄된 솔더 페이스트의 여러 창유리 패턴을 포함하였다. 50% 커버리지에 대응하여, 솔더 조인트 체적의 45%를 초래한 작은 프로폼이 사용되었다. 20% 미만의 커버리지에 대응하여, 솔더 조인트의 상당히 더 높은 퍼센트(80% 초과)를 초래한 더 큰 프리폼이 사용되었다.

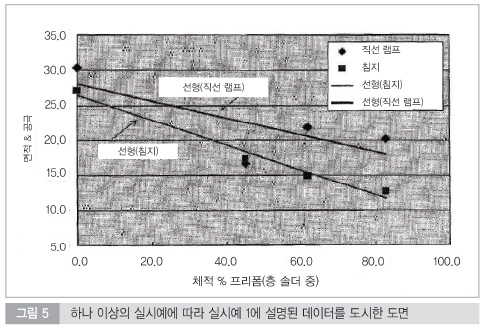

그림 5는 보이드 형성을 감소시키기 위해 솔더 페이스트로 프리폼의 조합 사용을 수반하는 실험 결과를 나타낸다. y-축은 솔더 조인트의 총 면적에 대한 보이드 형성의 면적 퍼센트를 나타낸다. x-축은 처리 후 총 솔더 조인트에서 솔더 프리폼의 체적 퍼센트를 나타낸다. 트렌드 라인은 프리폼의 상대적인 체적의 증가와 솔더 조인트의 보이드 면적 퍼센트의 감소 사이의 관계를 나타낸다. 보이드는 프리폼 체적이 솔더 조인트의 총 체적의 퍼센트에 따라 증가될 때 감소한다. 프리폼의 존재 또는 부재는 보이드에 가장 중요한 인자였다.

실시예 2

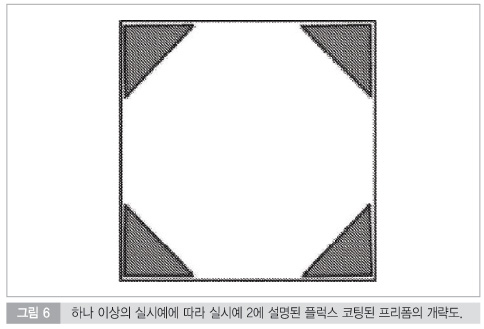

하나 이상의 실시예에 따라 보이드 감소 프리폼은 그림 6에 도시된 바와 같이 형성되었다. 암 영역(dark area)은 인쇄된 솔더 페이스트를 나타내는 반면, 명 영역(white area)은 플럭스 코팅된 솔더 프리폼을 나타낸다. 이들 플럭스 코팅된 프리폼은 테스트 동안 반복가능한 결과를 제공하였다.

이제 일부 예시적인 실시예를 설명하였으나, 이 기술 분야에 통상의 지식을 가진 자라면 전술된 내용은 단지 예시적인 것이어서 발명을 제한하는 것이 아니어서 단지 예로서 제시된 것이라는 것을 이해할 수 있을 것이다. 수많은 변형과 다른 실시예들이 이 기술 분야에 통상의 지식을 가진 자의 범위 내에 있고 본 발명의 범위 내에 있는 것으로 고려된다. 특히, 본 명세서에 제시된 많은 예는 방법 동작 또는 시스템 요소의 특정 조합을 수반하는 것이지만, 이들 동작 및 이들 요소는 조합된 다른 방식으로 조합되어 동일한 목적을 달성할 수 있다는 것을 이해될 수 있을 것이다.