칩 배열이 제공되며, 이는 몰드 컴파운드(mold compound) 및 몰드 컴파운드 내에 적어도 부분적으로 내장된 마이크로 전자기계 시스템 소자를 포함할 수 있다. 칩 배열을 제조하는 방법이 제공되며, 이는 마이크로 전자기계 시스템 소자를 캐리어 위에 배치하는 단계와, 마이크로 전자기계 시스템 소자를 몰드 컴파운드에 적어도 부분적으로 내장하는 단계를 포함할 수 있다.

배경 기술

칩(또는 다이)은 다른 전자 어셈블리들에 배치 및 통합되기 전에 패키징될 수 있다. 칩의 패키징은 어떤 재료로 칩을 캡슐화하거나 내장하는 것을 포함할 수 있고, 예를 들어, 전기적 콘택트들(electrical contacts)에 의해 캡슐화된(encapsulated) 또는 내장된(embedded) 칩에 인터페이스를 제공하는 것을 더 포함할 수 있다. 칩 패키지는 주위의 대기 및 오염으로부터 내장된 칩을 보호하고, 기계적인 지지물을 내장된 칩에 제공하며, 내장된 칩 내의 열을 분산하고, 내장된 칩에 대한 기계적인 손상을 줄여줄 수 있으며, 물론 칩 패키지의 다른 이용도 가능하다.

칩 패키지의 더 나은 성능과 특징부들에 대한 요구가 증가함에 따라서 센서, 발진기, 표면 음향 파(surface acoustic wave; SAW) 구조, 벌크 음향 파(bulk acoustic wave; BAW) 구조 및 다른 마이크로 전자기계 시스템(microelectromechanical systems; MEMS) 구조를 포함하는 칩들이 패키징될 수 있다. 그러한 칩들은 MEMS 소자라고도 불릴 수 있다. MEMS 소자들을 포함하는 칩 패키지는 큰 두께 및 큰 측면 크기(패키지 풋프린트(package footprint))를 가질 수 있다. 그러한 칩 패키지는, 더 작은 두께 및 더 작은 패키지 풋프린트를 추구하는 경향을 보여주는 미래 기술 노드들(future technology nodes)에는 바람직하지 않을 수 있다. MEMS 소자를 패키징하는 새로운 방법이 필요할 수 있다.

발명의 내용

발명을 실시하기 위한 구체적인 내용

마이크로 전자기계 시스템(MEMS) 소자(센서, 가속도계, 발진기, 표면 음향 파(SAW) 구조, 벌크 음향파(BAW) 구조 및 다른 MEMS 구조를 포함하는 칩)의 이용은 글로벌 반도체 사업에서 성장할 수 있다. 예를 들어, MEMS 소자는 이동 통신(이동 전화, GPS 모듈 등), 컴퓨팅(태블릿 컴퓨터), 및 다른 산업에 점점 더 많이 이용되고 있다.

MEMS 소자는 반도체 칩과 함께 이용될 수 있다. 반도체 칩은 로직 칩, 주문형 반도체(ASIC), 메모리 칩, 능동 소자(트랜지스터), 및 수동 소자(저항 및 커패시터 및 인덕터) 중 적어도 하나일 수 있거나 이를 포함할 수 있다. 반도체 칩(능동 소자, 로직 칩 및 ASIC)은, 예를 들어, MEMS 소자의 동작을 제어할 수 있다. 다른 예로서, MEMS 소자로부터의 데이터(예를 들어, 측정치)는 반도체 칩(메모리 칩 및 수동 소자)에 제공될 수 있다.

산업 동향이 소형 및 단일 집적 회로(IC) 패키지를 추구하고 있으므로, MEMS 소자는 IC 패키지로서 패키징될 수 있다. MEMS 소자를 포함하는 오늘날의 IC 패키지에 가장 널리 이용되는 패키지 기술은 와이어 본딩일 수 있다.

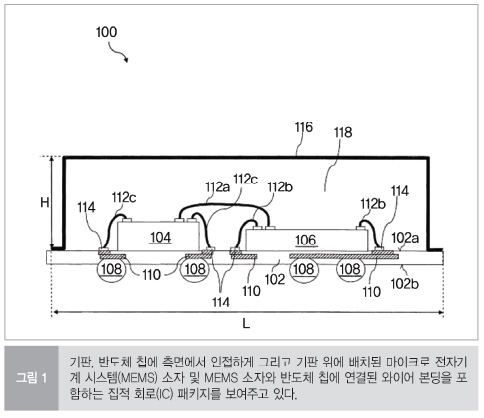

그림 1은 기판(102), 반도체 칩(106)에 측면에서 인접하게 그리고 기판(102) 위에 배치된 MEMS 소자(104) 및 MEMS 소자(104)와 반도체 칩(106)에 전기적으로 연결된 와이어 본딩(112a, 112b, 112c)을 포함하는 IC 패키지(100)를 보여주고 있다. 라미네이트(lamination) 또는 압착(pressing) 공정에 의해 형성될 수 있는 IC 패키지(100)의 기판(102)은 라미네이트 재료로 구성되거나 이를 포함할 수 있다. 다른 예로서, 기판(102)은 충전제(filler) 재료(예를 들어, 유리 섬유)를 포함하는 에폭시 폴리머를 포함할 수 있거나 이 에폭시 폴리머로 구성될 수 있다. 또 다른 예로서, 기판(102)은 FR4 및 BT(bis-maleimide triazine)로 구성되거나 이를 포함할 수 있다. 또 다른 예로서, 기판(102)은 유기 수지 및 세라믹 재료로 구성되거나 이를 포함할 수 있다.

기판(102)은 제1 면(102a)과 제1 면 반대쪽의 제2 면(102b)을 가질 수 있다. MEMS 소자(104) 및 반도체 칩(106)은 그림 1에 도시된 바와 같이, 기판(102)의 제1 면(102a)에 배치될 수 있다. IC 패키지(100)는 기판(102)의 제2 면(102b)에 배치된 적어도 하나의 전기 커넥터(108)(예를 들어, 적어도 하나의 솔더 볼)를 포함할 수 있다. MEMS 소자(104) 및 반도체 칩(106)은 와이어 본딩(112a, 112b, 112c) 및 재배선 층(redistribution layer; RDL)(110)에 의해서 적어도 하나의 전기 커넥터(108)에 전기적으로 연결될 수 있다. RDL(110)은 기판(102) 내에 부분적으로 또는 완전히 배치될 수 있고, MEMS 소자(104) 및 반도체 칩(106)으로부터 적어도 하나의 전기 커넥터(108)로의 전기적 연결을 재배선 및 재맵핑(remap)할 수 있다.

IC 패키지(100)는 와이어 본딩(112a)을 포함할 수 있고, 이는 MEMS 소자(104)와 반도체 칩(106)을 서로 전기적으로 연결할 수 있다. 와이어 본딩(112a)은 예를 들어, MEMS 소자(104) 및 MEMS 소자(104)가 전기 신호를 반도체 칩(106)에 제공하는 수단의 동작을 제어하기 위해 반도체 칩(106)이 MEMS 소자(104)에 전기 신호를 제공하는 수단일 수 있다.

IC 패키지(100)는 와이어 본딩(112c)을 포함할 수 있고, 이는 MEMS 소자(104)를, 예를 들어, 기판(102)의 제1면(102a)에 배치된 적어도 하나의 전기 전도 패드(114)를 통해, RDL(110)에 전기적으로 연결할 수 있다. 와이어 본딩(112a, 112b, 112c), 적어도 하나의 전기 전도 패드(114), RDL(110), 및 적어도 하나의 전기 커넥터(108)는 MEMS 소자(104) 및 반도체 칩(106)에 인터페이스를 제공할 수 있다. 즉, 신호들은 적어도 하나의 전기 커넥터(108), RDL(110), 적어도 하나의 전기 전도 패드(114) 및 와이어 본딩(112a, 112b, 112c)을 통해서 MEMS 소자(104) 및 반도체 칩(106)과 교환될 수 있다.

IC 패키지(100)는 캐비티(118) 내의 MEMS 소자(104)와 반도체 칩(106)을 밀봉 및 차폐할 수 있는 캡(116)을 포함할 수 있다. 즉, MEMS 소자(104) 및 반도체 칩(106)은 캡(116) 내에 하우징될 수 있고, 적어도 MEMS 소자(104) 및 반도체 칩(106) 및 와이어 본딩(112a, 112b, 112c) 위에 배치된 마진(margin)(예를 들어, 갭, 공기 갭)을 가질 수 있다.

와이어 본딩 패키징 기술이 IC 패키지(100)에 널리 이용될 수 있지만, 와이어 본딩(112a, 112b, 112c)의 각 와이어 본드를 형성하는데 요구되는 시간은 느릴 수 있다. 이는, 예를 들어, 와이어 본딩(112a, 112b, 112c)의 각 와이어 본드를 위해 점대점 연결(point-to-point connection)을 형성할 필요가 있을 수 있기 때문이다. 결국, 이는 IC 패키지(100)를 제조하는데 소요되는 시간을 증가시킬 수 있다. 더욱이, 와이어 본딩(112a) 및 와이어 본딩(112b) 및 와이어 본딩(112c)에 의해 제공된 상호연결(interconnect)의 길이는 길 수 있다. 와이어 본딩(112a, 112b, 112c)의 증가한 길이는 와이어 본딩(112a, 112b, 112c)의 전기 성능은 물론이고 IC 패키지(100)의 전기 성능을 떨어뜨릴 수 있다. IC 패키지(100)의 떨어진 전기 성능은, MEMS 소자(104) 및 반도체 칩(106)이 신뢰할 수 있는 전기 성능을 갖는 인터페이스에 의해서 접촉되도록 요구할 수 있는 미래의 기술 노드에는 적합하지 않을 수 있다. 심지어, MEMS 소자(104), 반도체 칩(106) 및 와이어 본딩(112a, 112b, 112c)은 기판(102) 상의 영역을 차지할 수 있다. 이는 IC 패키지(100)의 측면 크기 L(예를 들어, 풋프린트)를 증가시킬 수 있다. 풋프린트 L의 증가는 IC 패키지(100)가 복수의 반도체 칩(106) 및 복수의 MEMS 소자(104)를 포함할 수 있는 예에서 좀 더 확연할 수 있다. 예를 들어, IC 패키지(100)는 서로 옆에 그리고 기판(102) 위에 배치되는 가속도계로서 구성된 MEMS 소자(104), 자이로스코프로서 구성된 다른 MEMS 소자(104) 및 적어도 하나의 반도체 칩(106)(로직 칩, ASIC, 수동 소자)를 포함할 수 있는 관성 측정 장치(inertial measurement unit; IMU)일 수 있거나 이를 포함할 수 있다. 더욱이, IC 패키지(100)의 높이 H는, 예를 들어, 와이어 본딩(112a, 112b, 112c)의 원호(예를 들어, 루프, 예를 들어, 와이어 루프) 및 IC 패키지(100)의 캡(116) 내에 하우징될 수 있는 MEMS 소자(104) 및 반도체 칩(106) 및 와이어 본딩(112a, 112b, 112c) 위에 제공될 수 있는 마진 때문에 증가할 수 있다. 결과적으로, IC 패키지(100)가 점유한 풋프린트 L 및 IC 패키지(100)의 두께(높이 H)는 좀 더 작은 두께 및 좀 더 작은 패키지 풋프린트를 추구하는 미래 기술 노드에는 적합하지 않을 수 있다.

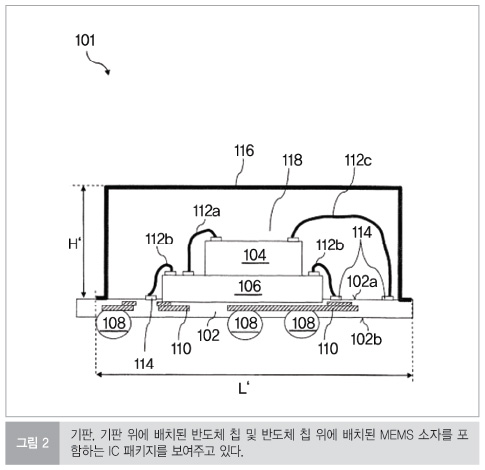

그림 2에 도시된 IC 패키지(101)에서, MEMS 소자(104)는 반도체 칩(106) 위에 배치된다. 그러한 예에서, IC 패키지(101)의 풋프린트 L’은 그림 1에 도시된 IC 패키지(100)에 비해서 감소할 수 있다. 그러나 와이어 본딩(112a, 112b, 112c)은 여전히 기판(102) 상의 영역을 점유할 수 있고 및 원호를 여전히 포함할 수 있다. 더욱이, 마진도 여전히 반도체 칩(106) 및 와이어 본딩(112a, 112b, 112c) 위에 배치된 MEMS 소자(104) 위에 제공될 수 있다. 결과적으로, 반도체 칩(106) 위에 MEMS(104)를 배치하면 IC 패키지(101)의 풋프린트가 줄어들지만, IC 패키지(101)의 높이 및 두께가 증가할 수 있다. 더구나, 반도체 칩(106) 위에 MEMS 소자(104)를 배치하면 다른 반도체 칩(106)을 스택할 수 없게 될 수 있다. 따라서 이러한 IC 패키지(101)는 복수의 반도체 칩(106)을 포함할 수 있는 IC 패키지 및 더 작은 두께를 필요로 할 수 있는 IC 패키지에는 적합하지 않을 수 있다.

IC 패키지(100 및 101)에 이용된 와이어 본딩(112a, 112b, 112c) 대신에, 플립 칩 패키징이 이용될 수 있다. 그러한 예에서, 기판(102)은 가장 엄격한 설계 규칙에 따라서 선택될 수 있다. 통상, 가장 엄격한 설계 규칙은 반도체 칩(106)에 적용될 수 있고, 이는 고가인 기판(102)의 이용을 야기할 수 있다. 그러한 예에서, MEMS 소자(104)는 고가인 기판(102) 상의 영역을 점유할 수 있고 그렇지 않으면 이 영역은 추가 회로를 위해 이용될 수 있거나 IC 패키지의 풋프린트를 축소하기 위해서 제거될 수 있다. MEMS 소자(104)가 플립 칩 패키징 내의 반도체 칩(106) 위에 배치될 수 있을지라도, 플립 칩 패키징을 포함하는 IC 패키지의 높이 및 두께는 클 수 있다.

IC 패키지(100 및 101) 내에 이용된 와이어 본딩(112a, 112b, 112c) 대신에, MEMS 소자(104)는 MEMS 소자(104)의 적어도 일부를 통해서 연장할 수 있는 스루-실리콘-비아들(through-silicon-vias; TSVs)을 포함할 수 있다. 그러나 TSV의 형성은 높은 제조 비용을 초래할 수 있다. 더욱이, TSV의 생산량이 낮아질 수 있다.

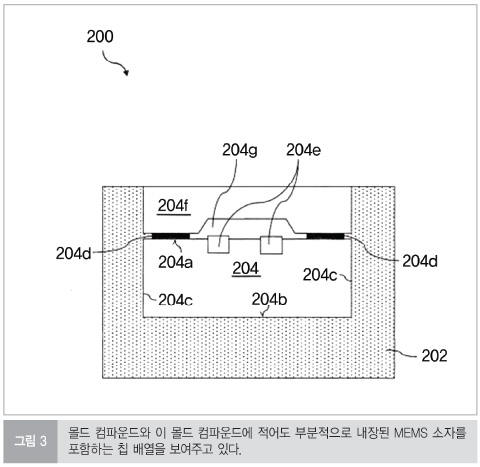

앞에 언급한 고려사항들에 비추어볼 때 다음의 필요성을 확인할 수 있다. 더 작은 측면 크기(작은 풋프린트)를 가질 수 있는 패키지형 MEMS 소자를 포함하는 칩 배열을 제공할 필요가 있을 수 있다. 작은 높이 및 두께를 가질 수 있는 패키지형 MEMS 소자를 포함하는 칩 배열을 제공할 필요가 있을 수 있다. 신뢰 가능한 전기 성능을 가진 상호연결에 의해 접촉될 수 있는 패키지형 MEMS 소자를 포함하는 칩 배열을 제공할 필요가 있을 수 있다. 단기간 동안에 제조될 수 있는 패키지형 MEMS 소자를 포함하는 칩 배열을 제공할 필요가 있을 수 있다. 그러한 칩 배열은, 예를 들어, 그림 3에 도시된 칩 배열(200)에 의해서 제공될 수 있다.

그림 3은 몰드 컴파운드(202)와 몰드 컴파운드(202) 내에 적어도 부분적으로 내장된 MEMS 소자(204)를 포함하는 칩 배열(200)을 보여주고 있다. MEMS 소자(204)는 제1 면(204a)과 제1 면(204a) 반대쪽의 제2 면(204b)을 포함할 수 있다. MEMS 소자(204)는 적어도 하나의 측벽(204c)을 더 가질 수 있다. MEMS 소자(204)는 MEMS 소자(204)의 제1 면(204a)에 배치될 수 있는 적어도 하나의 전기 전도 콘택트(204d)를 포함할 수 있다. MEMS 소자(204)의 적어도 하나의 전기 전도 콘택트(204d)는 패드(본딩 및 콘택트 패드)일 수 있거나 이를 포함할 수 있다. MEMS 소자(204)의 적어도 하나의 전기 전도 콘택트(204d)는 MEMS 소자(204)에 인터페이스를 제공할 수 있다. 즉, 신호들은 적어도 하나의 전기 전도 콘택트(204d)를 통해서 MEMS 소자(204)와 교환될 수 있다.

MEMS 소자(204)는 MEMS 소자(204)의 제1 면(204a)에 배치될 수 있는 적어도 하나의 MEMS 구조(204e)를 포함할 수 있다. 단지 2개의 MEMS 구조(204e)가 일례로 도시되어 있지만, MEMS 구조(204e)의 수는 1일 수 있거나 2보다 클 수 있으며, 예를 들어, 3, 4, 5, 등일 수 있다. 적어도 하나의 MEMS 구조(204e)가 배치될 수 있는 MEMS소자(204)의 제1 면(204a)은 MEMS 소자(204)의 활성 면(active side)으로 칭해질 수 있다. 적어도 하나의 MEMS 구조(204e)는 센서, 가속도계, 발진기, 표면 음향 파(SAW) 구조 및 벌크 음향 파(BAW) 구조 중에서 적어도 하나일 수 있거나 이를 포함할 수 있지만, 다른 MEMS 구조들도 가능하다. MEMS 소자(204)는 캡(204f)을 포함할 수 있다. 캡(204f)은, 예를 들어, 캐비티(204g) 내에 적어도 하나의 MEMS 구조(204e)를 캡슐화하도록 구성될 수 있다. 캡(204f)은, 예를 들어, 캐비티(204g) 내에 적어도 하나의 MEMS 구조(204e)를 밀봉 및 차폐할 수 있다. 캡(204f)은 예를 들어, 수분, 먼지 및 기계적 손상으로부터 적어도 하나의 MEMS 구조(204e)를 밀봉 및 차폐할 수 있다. 캡(204f)은 캡(204f)의 주변에 배치된 시일(seal)로 적어도 하나의 MEMS 구조(204e)를 밀봉할 수 있다. 그림 3에 도시된 예에서, 적어도 하나의 전기전도 콘택트(204d)는 캡(204f)이 적어도 하나의 MEMS 구조(204e)를 밀봉할 수 있는 수단일 수 있다. 다른 예에서, 적어도 하나의 전기 전도 콘택트(204d) 이외의 구조가 캡(204f)이 적어도 하나의 MEMS 구조(204e)를 밀봉할 수 있는 수단일 수 있다.

캡(204f)은 MEMS 소자(204)의 제1 면(204a)(활성 면)의 적어도 일부 위에 배치될 수 있다. 예를 들어, 그림 3에 도시된 칩 배열(200)에서, 캡(204f)은 MEMS 소자(204)의 제1 면(204a)의 측면 크기 위에 배치될 수 있다. 다른 예에서, 캡(204f)은 MEMS 소자(204)의 제1 면(204a)의 일부 위에 배치될 수 있고, MEMS 소자(204)의 제1 면(204a)의 다른 부분은 캡(204f)에서 자유로울 수 있다. 캡(204f)은 반도체 재료로 구성될 수 있거나 이를 포함할 수 있는 반도체 기판을 포함할 수 있다.

몰드 컴파운드(202)는 적어도 하나의 폴리머로 구성될 수 있거나 이를 포함할 수 있다. 몰드 컴파운드(202)는 플라스틱 재료로 구성될 수 있거나 이를 포함할 수 있다. 몰드 컴파운드(202)의 플라스틱 재료는 열경화성 몰딩 컴파운드로 구성될 수 있거나 이를 포함할 수 있다. 다른 예로서, 몰드 컴파운드(202)의 플라스틱 재료는 열가소성(고순도 플루오르폴리머(high purity fluoropolymer))로 구성될 수 있거나 이를 포함할 수 있다. 몰드 컴파운드(202)는 충전제 재료(실리카 충전제, 유리 충전제, 유리 직물, 고무, 폴리머 및 금속 입자 중에서 적어도 하나로 구성되거나 이를 포함)를 포함할 수 있다. 충전제 재료에 의해 점유된 몰드 컴파운드(202)의 전체 체적의 퍼센티지를 나타낼 수 있는 몰드 컴파운드(202)의 충전제 비율은, 약 80% 이상일 수 있고, 예를 들어, 약 80%로부터 약 90%까지의 범위 내에 있을 수 있다. 다른 예에서, 몰드 컴파운드(202)의 충전제 비율은 약 90% 이상일 수 있다.

그림 3에 도시된 칩 배열(200)은 예를 들어, 칩 패키지로 구성될 수 있다. 즉, MEMS 소자(204)는 몰드 컴파운드(202) 내에 패키징될 수 있다. 그림 3에 도시된 칩 배열(200)은, 예를 들어, 내장된 웨이퍼 레벨 볼 그리드 어레이(embedded wafer level ball grid array; eWLB) 패키지로서 구성될 수 있다. 즉, MEMS 소자(204)는 eWLB 공정 흐름을 이용하여 몰드 컴파운드(202) 내에 패키징될 수 있다. 몰드 컴파운드(202) 내에 적어도 부분적으로 내장될 수 있는 MEMS 소자(204)에는 인터페이스가 제공될 수 있고, 이 인터페이스를 통해서 신호들이 MEMS 소자(204)와 교환될 수 있다. 그러한 인터페이스를 포함하는 칩 배열은 그림 4에 도시되어 있다.

그림 4는 몰드 컴파운드(202), 몰드 컴파운드(202) 내에 적어도 부분적으로 내장된 MEMS 소자(204), 적어도 하나의 전기 커넥터(302), 및 MEMS 소자(204)를 적어도 하나의 전기 커넥터(302)에 전기적으로 결합하도록 구성된 상호연결 구조(304)를 포함하는 칩 배열(300)을 보여주고 있다.

몰드 컴파운드(202)는 제1 면(202a)과 제1 면(202a) 반대쪽의 제2 면(202b)을 가질 수 있다. 몰드 컴파운드(202)의 제1 면(202a)은, 예를 들어, 칩 배열(300)의 앞면일 수 있다. 몰드 컴파운드(202)의 제2 면(202b)은, 예를 들어, 칩 배열(300)의 후면일 수 있다. 그리 4에 도시된 칩 배열(300)에서, MEMS 소자(204)의 제1 면(204a)(활성 면)은 몰드 컴파운드(202)의 제1 면(202a)이 바라보는 방향과 동일한 방향으로 바라볼 수 있다. 다른 예에서, MEMS 소자(204)의 제1 면(204a)(활성 면)은 몰드 컴파운드(202)의 제1 면(202a)이 바라보는 방향과 반대 방향으로 바라볼 수 있다.

칩 배열(300)은 몰드 컴파운드(202)의 제1 면(202a)에 배치된 적어도 하나의 전기 커넥터(302)를 포함할 수 있다. 적어도 하나의 전기 커넥터(302)는 전기 전도 재료들의 그룹에서 선택된 적어도 하나의 전기 전도 재료로 구성될 수 있거나 이를 포함할 수 있다. 전기 전도 재료 그룹은 금속 또는 금속 합금으로 구성될 수 있다. 예를 들어, 적어도 하나의 전기 커넥터(302)는 솔더 재료(예를 들어, 주석, 은 및 구리의 합금)로 구성될 수 있다. 다른 예로서, 적어도 하나의 전기 커넥터(302)는 구리, 백금, 티타늄, 텅스텐, 니켈, 금, 알루미늄, 또는 전도 페이스트, 또는 열거된 금속 중 적어도 하나를 포함하는 스택이나 합금으로 구성될 수 있다.

칩 배열(300)은 상호연결 구조(304)를 포함할 수 있고, 이 상호연결 구조는 적어도 하나의 전기 커넥터(302)에 MEMS 소자(204)를 전기적으로 결합하도록 구성될 수 있다. 상호연결 구조(304)는, 예를 들어, MEMS 소자(204)(예로, MEMS 소자(204)의 제1 면(204a))로부터 적어도 하나의 전기 커넥터(302)(솔더 볼들의 BGA)로의 전기 연결을 재배선 및 재맵핑할 수 있다. 따라서 신호들(전기 신호, 전원 전위, 접지전위 등)이 적어도 하나의 전기 커넥터(302) 및 상호연결 구조(304)를 통해서 MEMS 소자(204)와 교환될 수 있다.

상호연결 구조(304)는 MEMS 소자(204)의 적어도 일부를 통해서 연장할 수 있는 적어도 하나의 스루-비아(through-via)(304a)를 포함할 수 있다. 예를 들어, 그림 4에 도시된 칩 배열(300)에서, 상호연결 구조(304)의 적어도 하나의 스루-비아(304a)는 MEMS 소자(204)의 캡(204f)의 적어도 일부를 통해서 연장할 수 있다. 다른 예에서, 상호연결 구조(304)의 적어도 하나의 스루-비아(304a)는 MEMS 소자(204)의 바디의 적어도 일부를 통해서 연장할 수 있다. 상호연결 구조(304)의 적어도 하나의 스루-비아(304a)는 그림 4에 도시된 바와 같이 MEMS 소자(204)의 적어도 하나의 전기 전도 콘택트(204d)에 전기적으로 결합될 수 있다.

그림 4에 도시된 칩 배열(300)에서, 몰드 컴파운드(202)는 적어도 하나의 측벽(204c) 및 제2 면(204b)으로부터 MEMS 소자(204)를 둘러쌀 수 있다. 다른 예(예를 들어, 몰드 컴파운드(202)가 모든 측면으로부터 MEMS 소자(204)의 캡(204f)을 덮을 수 있는 예)에서, 몰드 컴파운드(202)는 적어도 하나의 측벽(204c)(예를 들어, 모든 측벽(204c)), 제1 면(204a)(예를 들어, 활성 면), 및 제2 면(204b)으로부터 MEMS 소자(204)를 둘러쌀 수 있다. 그러한 예에서, 상호연결 구조(304)의 적어도 하나의 스루-비아(304a)는 몰드 컴파운드(202)의 적어도 일부를 통해서(예를 들어, 몰드 컴파운드(202)의 제1 면(202a)으로), 예를 들어, MEMS 소자(204)의 제1 면(204a)(예를 들어, 활성 면)으로부터 MEMS 소자(204)를 둘러싸는 몰드 컴파운드(202)의 일부를 통해서 연장할 수 있다.

그림 4에 도시된 칩 배열(300)은, 예를 들어, 칩 패키지로서 구성될 수 있다. 즉, MEMS 소자(204)는 몰드 컴파운드(202) 내에 패키징될 수 있고, MEMS 소자(204)로의 인터페이스를 갖출 수 있다. MEMS 소자(204)로의 인터페이스는 적어도 하나의 전기 커넥터(302)(예를 들어, 솔더 볼들의 BGA) 및 상호연결 구조(304)(예를 들어, 적어도 하나의 스루-비아(304a) 및 재배선 구조(304b))일 수 있거나 이를 포함할 수 있다. 그림 4에 도시된 칩 배열(300)은, 예를 들어, 내장된 웨이퍼 레벨 볼 그리드 어레이(eWLB) 패키지로 구성될 수 있다. 즉, MEMS 소자(204)는 몰드 컴파운드(202) 내에 내장될 수 있고, eWLB 공정 흐름에 의해서 적어도 하나의 전기 커넥터(302)( 및 상호연결 구조(304) 및 재배선 구조(304b))를 갖출 수 있다.

그림 4에 도시된 바와 같이, MEMS 소자(204)와 적어도 하나의 전기 커넥터(302) 간의 거리는 작을 수 있다. 따라서 MEMS 소자(204)를 적어도 하나의 전기 커넥터(302)에 전기적으로 결합하도록 구성된 상호연결 구조(304)의 길이는 짧을 수 있다. 결과적으로, 칩 배열(300)에 의해 제공된 효과는 MEMS 소자(204)에 대한 상호연결의 신뢰할 수 있는 전기 성능(낮은 저항 및 용량성 및 유도성)일 수 있다.

그림 4에 도시된 바와 같이, MEMS 소자(204)를 적어도 하나의 전기 커텍터(302)에 전기적으로 결합하도록 구성된 상호연결 구조(304)는 그림 1 및 그림 2에 도시된 와이어 본딩(112a, 112b, 112c)에 비해서 더 신뢰할 수 있는 전기 성능을 가질 수 있는 재배선 구조(304b)(RDL)를 포함할 수 있다. 결과적으로, 칩 배열(300)에 의해 제공되는 효과는 MEMS 소자(204)에 대한 상호연결의 신뢰 가능한 전기 성능일 수 있다.

그림 4에 도시된 바와 같이, MEMS 소자(204)를 적어도 하나의 전기 커넥터(302)에 전기적으로 결합하도록 구성된 상호연결 구조(304)는, 예를 들어, MEMS 소자(204)의 측면 크기 내에 한정될 수 있는 적어도 하나의 스루-비아(304a) 및 재배선 구조(304b)(RDL)를 포함할 수 있다. 칩 배열(300)에 의해 제공되는 효과는 작은 측면 크기를 갖는 칩 배열일 수 있다.

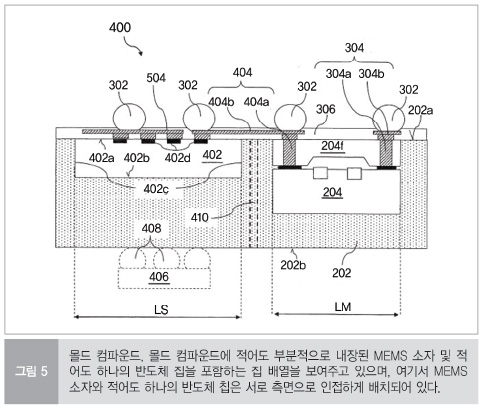

그림 5는 몰드 컴파운드(202), 몰드 컴파운드(202) 내에 적어도 부분적으로 내장된 MEMS 소자(204) 및 적어도 하나의 반도체 칩(402)을 포함하는 칩 배열(400)을 보여주고 있으며, 여기서 MEMS 소자(204) 및 적어도 하나의 반도체 칩(402)은 서로 측면에서 인접하게 배치되어 있다.

적어도 하나의 반도체 칩(402)의 제1 면(402a) 및 제2 면(402b)은 각각 적어도 하나의 반도체 칩(402)의 앞면 및 후면일 수 있거나 이를 포함할 수 있다. 다른 예로서, 적어도 하나의 반도체 칩(402)의 제1 면(402a)은 적어도 하나의 반도체 칩(402)의 활성면일 수 있거나 이를 포함할 수 있다. 또 다른 예로서, 적어도 하나의 반도체 칩(402)의 제1 면(402a) 및 제2면(402b)은 각각 적어도 하나의 반도체 칩(402)의 하부 표면 및 상부 표면일 수 있거나 이를 포함할 수 있다.

적어도 하나의 반도체 칩(402)은 적어도 하나의 반도체 칩(402)의 제1 면(402a)에 배치될 수 있는 적어도 하나의 전기 전도 콘택트(402d)를 포함할 수 있다. 적어도 하나의 반도체 칩(402)의 적어도 하나의 전기 전도 콘택트(402d)는 패드일 수 있거나 이를 포함할 수 있다. 적어도 하나의 반도체 칩(402)의 적어도 하나의 전기 전도 콘택트(402d)는 적어도 하나의 반도체 칩(402)에 인터페이스를 제공할 수 있다. 즉, 신호들이 적어도 하나의 전기 콘택트(402d)을 통해서 적어도 하나의 반도체 칩(402)과 교환될 수 있다.

적어도 하나의 반도체 칩(402)은 그림 4에 도시된 바와 같이 MEMS 소자(204)에 측면에서 인접하게 배치될 수 있다. 그림 5에 도시된 예에서, MEMS 소자(204)의 측면 크기 LM은 적어도 하나의 반도체 칩(402)의 측면 크기 LS이하일 수 있다. 다른 예에서, MEMS 소자(204)의 측면 크기 LM은 적어도 하나의 반도체 칩(402)의 측면 크기 LS보다 클 수 있다.

제2 상호연결 구조(404)는 MEMS 소자(204)의 적어도 일부를 통해서 연장할 수 있는 적어도 하나의 스루-비아(404a)를 포함할 수 있다. 예를 들어, 제2 상호연결 구조(404)의 적어도 하나의 스루-비아(404a)는 MEMS 소자(204)의 캡(204f)의 적어도 일부를 통해서 연장할 수 있다. 다른 예에서, 제2 상호연결 구조(404)의 적어도 하나의 스루-비아(404a)는 MEMS 소자(204)의 바디의 적어도 일부(즉, 캡(204f) 이외의 MEMS 소자(204)의 일부)를 통해서 연장할 수 있다. 제2 상호연결 구조(404)의 적어도 하나의 스루-비아(404a)는 MEMS 소자(204)의 적어도 하나의 전기 전도 콘택트(204d)에 전기적으로 결합할 수 있다.

그림 5에 도시된 칩 배열(400)에서, 몰드 컴파운드(202)는 적어도 하나의 측벽(204c)(예를 들어, 모든 측벽(204c)) 및 제2 면(204b)으로부터 MEMS 소자(204)를 둘러쌀 수 있다. 다른 예(예를 들어, 몰드 컴파운드(202)가 모든 측면으로부터 MEMS 소자(204)의 캡(204f)을 덮을 수 있는 예)에서, 몰드 컴파운드(202)는 적어도 하나의 측벽(204c)(예를 들어 모든 측벽(204c)), 제1 면(204a)활성 면), 및 제2 면(204b)으로부터 MEMS 소자(204)를 둘러쌀 수 있다. 그러한 예에서, 제2 상호연결 구조(404)의 적어도 하나의 스루-비아(404a)는 몰드 컴파운드(202)의 적어도 일부를 통해서, 예를 들어, MEMS 소자(204)의 제1 면(204a)(활성 면)으로부터 MEMS 소자(204)를 둘러싸는 몰드 컴파운드(202)의 일부를 통해서 연장할 수 있다.

그림 5에 도시된 바와 같이, 제2 상호연결 구조(404)는 몰드 컴파운드(202)의 제1 면(202a)에 배치된(예를 들어 상에 또는 위에 배치된) 재배선 구조(404b)를 포함할 수 있다. 재배선 구조(404b)는 재배선 층(RDL)일 수 있거나 이를 포함할 수 있다. 위에 기술된 바와 같이, 몰드 컴파운드(202)의 제1 면(202a)은, 예를 들어, 칩 배열(400)의 앞면일 수 있다. 따라서 몰드 컴파운드(202)의 제1 면(202a)에 배치된 제2 상호연결 구조(404)의 재배선 구조(404b)는 앞면 RDL일 수 있거나 이를 포함할 수 있다. 제2 상호연결 구조(404)의 재배선 구조(404b)(예를 들어, 앞면 RDL)는 절연 층(306) 내에 부분적으로 또는 완전히 배치될 수 있다. 제2 상호연결 구조(404)의 재배선 구조(404b)(예를 들어, RDL)는 싱글-레벨(예를 들어, 단일 층) RDL 또는 멀티-레벨(예를 들어, 다-층) RDL일 수 있거나 이를 포함할 수 있다.

그림 5에 도시된 바와 같이, 제2 상호연결 구조(404)(예를 들어, 제2 상호연결 구조(404)의 재배선 구조(404b))는 적어도 하나의 반도체 칩(402)의 적어도 하나의 전기 전도 접점(402d)에 전기적으로 결합될 수 있다. 그림 5에 도시된 칩 배열(400)에서, 몰드 컴파운드(202)는 적어도 하나의 측벽(402c)(예를 들어, 모든 측벽(402c)) 및 제2 면(402b)으로부터 적어도 하나의 반도체 칩(402)을 둘러쌀 수 있다. 다른 예(예를 들어, 몰드 컴파운드(202)가 모든 측면으로부터 적어도 하나의 반도체 칩(402)을 덮을 수 있는 예)에서, 몰드 컴파운드(202)는 적어도 하나의 측벽(402c)(예를 들어, 모든 측벽(402c)), 제1 면(402a), 및 제2 면(402b)으로부터 적어도 하나의 반도체 칩(402)을 둘러쌀 수 있다. 그러한 예에서, 제2 상호연결 구조(404)는 몰드 컴파운드(202)의 적어도 일부를 통해서, 예를 들어, 제1 면(402a)으로부터 적어도 하나의 반도체 칩(402)을 둘러싸는 몰드 컴파운드(202)의 일부를 통해서 적어도 하나의 반도체 칩(402)의 적어도 하나의 전기 전도 접점(402d)으로 연장될 수 있다.

칩 배열(400)은 적어도 하나의 반도체 칩(402)을 적어도 하나의 전기 커넥터(302)에 전기적으로 결합하도록 구성될 수 있는 제3 상호연결 구조(504)를 포함할 수 있다.

그림 5에 도시된 칩 배열(400)에서, MEMS 소자(204)는 적어도 하나의 전기 커넥터(302)에 그리고 적어도 하나의 반도체 칩(402)에 전기적으로 결합될 수 있다. 그러나 다른 예에서, MEMS 소자(204)는 적어도 하나의 전기 커넥터(302)에만 전기적으로 연결될 수 있다. 그러한 예에서, 제2 상호연결 구조(404)를 통한 MEMS 소자(204)와 적어도 하나의 반도체 칩(402) 간의 전기 연결은 없을 수 있다. 또 다른 예에서, MEMS 소자(204)는 적어도 하나의 반도체 칩(402)에만 전기적으로 결합될 수 있다. 그러한 예에서, 상호연결 구조(404)를 통한 MEMS 소자(204)와 적어도 하나의 전기 커넥터(302) 간의 전기 연결은 없을 수 있다. 대신에, MEMS 소자(204)와 적어도 하나의 전기 커넥터(302) 간의 전기 연결은 적어도 하나의 반도체 칩(402)을 통할 수 있고, 예를 들어, 제2 상호연결 구조(404)에 의해서 중재될 수 있다.

요약하면, MEMS 소자(204)는 적어도 하나의 전기 커넥터(302)에 또는 적어도 하나의 반도체 칩(402)에, 또는 양쪽에 전기적으로 결합될 수 있다.

그림 5에 도시된 칩 배열(400)은 몰드 컴파운드(202)의 제2 면(202b) 위에 배치될 수 있는 적어도 하나의 제2 반도체 칩(406)을 포함할 수 있다. 단지 하나의 제2 반도체 칩(406)이 일례로서 도시되어 있지만, 제2 반도체 칩(406)의 수는 1보다 클 수 있고, 예를 들어, 2, 3, 4, 5 등일 수 있다. 예를 들어, 칩 배열(400)은 예를 들어, 서로 측면에서 인접하게 배열될 수 있는 복수의 반도체 칩(406)을 포함할 수 있다.

그림 5에 도시된 바와 같이, MEMS 소자(204)(예를 들어, MEMS 소자(204)의 제1 면(204a))과 적어도 하나의 반도체 칩(402)(예를 들어, 적어도 하나의 반도체 칩(402)의 제1 면(402a)) 간의 거리는 작을 수 있다. 따라서 MEMS소자(204)를 적어도 하나의 반도체 칩(402)에 전기적으로 결합하도록 구성된 제2 상호연결 구조(404)의 길이는 짧을 수 있다. 결과적으로, 칩 배열(400)에 의해 제공되는 효과는 MEMS 소자(204)와 적어도 하나의 반도체 칩(402) 간의 상호연결의 신뢰할 수 있는 전기 성능일 수 있다.

그림 5에 도시된 바와 같이, MEMS 소자(204) 및 적어도 하나의 반도체 칩(402)은, 몰드 컴파운드(202)가 적당한 두께, MEMS 소자(204)의 두께 또는 적어도 하나의 반도체 칩(402)의 두께와 실질적으로 같을 수 있는 두께로 아래로 연삭 가공되는 경우에, 몰드 컴파운드(202)의 제1 면(202a) 및 제2 면(202b)으로부터 접촉될 수 있다. 결과적으로, 칩 배열(300)에 의해 제공되는 효과는 작은 측면 크기 및 작은 높이 및 두께를 갖는 칩 배열일 수 있다.

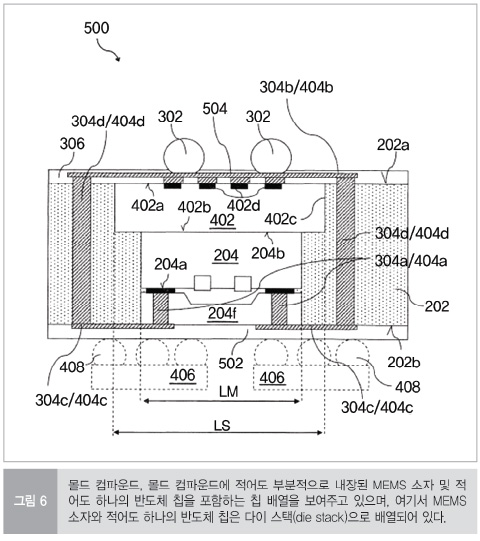

그림 6은 몰드 컴파운드(202), 몰드 컴파운드(202) 내에 적어도 부분적으로 내장된 적어도 MEMS 소자(204) 및 적어도 하나의 반도체 칩(402)을 포함하는 칩 배열(500)을 보여주고 있으며, 여기서 MEMS 소자(204)와 적어도 하나의 반도체 칩(402)은 다이 스택으로서 배열되어 있다. 그림 6에 도시된 바와 같이, MEMS 소자(204)와 적어도 하나의 반도체 칩(402)은 다이 스택으로서 배열될 수 있다. 즉, MEMS 소자(204)는 적어도 하나의 반도체 칩(402) 위에 배치될 수 있다. 그러한 예에서, 적어도 하나의 반도체 칩(402)은 MEMS 소자(204)를 덮는데(cap) 이용될 수 있다.

MEMS 소자(204)의 측면 크기 LM이 적어도 하나의 반도체 칩(402)의 측면 크기 LS보다 작을 수 있는 예에서, 복수의 MEMS 소자(204)는 서로 측면으로 인접하게 배열될 수 있고 적어도 하나의 반도체 칩(402) 위에 배치될 수 있다. 이 예에서, 적어도 하나의 반도체 칩(402)은, 복수의 MEMS 소자(204)의 기능을 제어하기 위해서 복수의 MEMS 소자(204)와 함께 이용될 수 있다.

그림 6에 도시된 칩 배열(500)은 몰드 컴파운드(202)의 제2 면(202b) 위에 배치될 수 있고 서로 측면으로 인접하게 배열될 수 있는 복수의 제2 반도체 칩(406)을 포함할 수 있다. 복수의 제2 반도체 칩(406)은 MEMS 소자(204), 적어도 하나의 전기 커넥터(302), 및 적어도 하나의 반도체 칩(402) 중 적어도 하나에, 예를 들어, 적어도 하나의 전기 전도성 상호연결(408)에 의해서 전기적으로 결합될 수 있다.

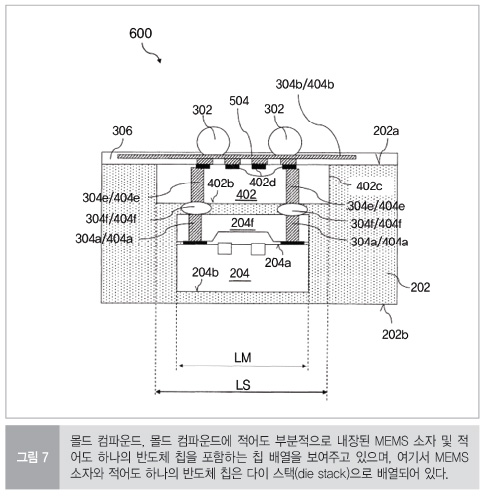

그림 7은 몰드 컴파운드(202), 몰드 컴파운드(202) 내에 적어도 부분적으로 내장된 MEMS 소자(204) 및 적어도 하나의 반도체 칩(402)을 포함하는 칩 배열(600)을 보여주고 있으며, 여기서 MEMS 소자(204)와 적어도 하나의 반도체 칩(402)은 다이 스택으로서 배열되어 있다. 그림 7에 도시된 MEMS 소자(204)의 제1 면(204a)(활성면)은 몰드 컴파운드(202)의 제1 면(202a)이 바라보는 방향과 동일한 방향으로 바라볼 수 있다. 그러한 예에서, MEMS 소자(204)를 적어도 하나의 전기 커넥터(302)에 전기적으로 결합하도록 구성된 상호연결 구조(304)는 적어도 하나의 반도체 칩(402)의 적어도 일부를 통해서 연장할 수 있는 적어도 하나의 스루-비아(304e)를 포함할 수 있다.

상호연결 구조(304)는 적어도 하나의 반도체 칩(402)과 MEMS 소자(204) 사이에 배치된 적어도 하나의 전도성 상호연결(304f)을 더 포함할 수 있다. 같은 식으로, 제2 상호연결 구조(404)는 적어도 하나의 반도체 칩(402)과 MEMS 소자(204) 사이에 배치된 적어도 하나의 전도성 상호연결(404f)을 더 포함할 수 있다. 적어도 하나의 전도성 상호연결(304f 및 404f)은 재배선 구조, 범프 구조, 필러 구조 및 금속화일 수 있거나 이를 포함할 수 있고, 적어도 하나의 반도체 칩(402)과 MEMS 소자(204) 사이에 다른 매개 구조들도 물론 가능할 수 있다.

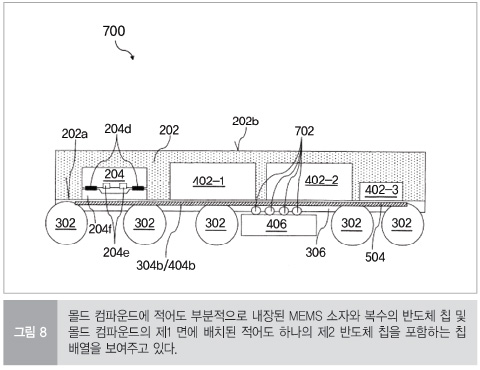

그림 8은 몰드 컴파운드(202) 내에 적어도 부분적으로 내장된 MEMS 소자(204) 와 복수의 반도체 칩(402-1, 402-2, 402-3), 및 몰드 컴파운드(202)의 제1 면(202a)에 배치된 적어도 하나의 제2 반도체 칩(406)을 포함하는 칩 배열(700)을 보여주고 있다. 그림 8에 도시된 바와 같이, 칩 배열(700)은 몰드 컴파운드(202) 내에 적어도 부분적으로 내장된 복수의 반도체 칩(402-1, 402-2, 402-3)을 포함할 수 있다. 적어도 하나의 제2 반도체 칩(406)은 몰드 컴파운드(202)의 제1면(202a)에 배치될 수 있고, 도터 다이(daughter die)로서 구성될 수 있다. 적어도 하나의 제2 반도체 칩(406)(도터 다이)는 복수의 반도체 칩(402-1, 402-2, 402-3) 중 한 반도체 칩의 활성 면을 바라볼 수 있는 활성 면을 가질 수 있다. 즉, 적어도 하나의 제2 반도체 칩(406)(도터 다이) 및 복수의 반도체 칩(402-1, 402-2, 402-3)은 대면(face-to-face) 구성으로 배열될 수 있다. 적어도 하나의 제2 반도체 칩(406)(도터 다이)은 MEMS 소자(204), 복수의 반도체 칩(402-1, 402-2, 402-3) 및 적어도 하나의 전기 커넥터(302) 중 적어도 하나에 전기적으로 결합될 수 있다. 다른 예에서, 적어도 하나의 다른 제2 반도체 칩(406)은 몰드 컴파운드(202)의 제2 면(202b)에 배치될 수 있다.

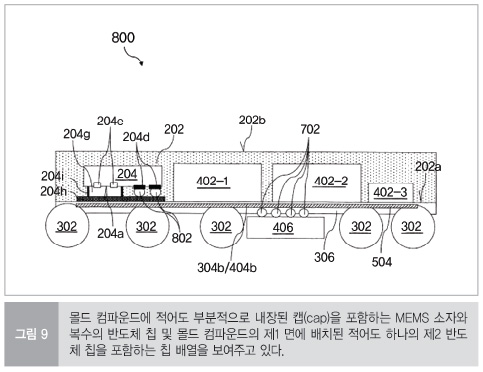

그림 9는 몰드 컴파운드(202) 내에 적어도 부분적으로 내장된, 캡(204f)을 포함하는 MEMS 소자(204)와 복수의 반도체 칩(402-1, 402-2, 402-3), 및 몰드 컴파운드(202)의 제1 면(202a)에 배치된 적어도 하나의 제2 반도체 칩(406)을 포함하는 칩 배열(800)을 보여주고 있다.

칩 배열(200 내지 700)에서, MEMS 소자(204)는 캡(204f)을 포함할 수 있고, 이는, 캐비티(204g) 내에 적어도 하나의 MEMS 구조(204e)를 캡슐화하도록 구성될 수 있다. 캡(204f)은, 습기, 먼지 및 기계적 손상으로부터 적어도 하나의 MEMS 구조(204e)를 밀봉 및 차폐할 수 있다. 그와 같이, 캡(204f)은 조밀할 수 있다. 캡(204f)은 콤팩트하게 및 타이트하게 팩킹(pack)될 수 있는 1 이상의 재료로 구성될 수 있거나 이를 포함할 수 있다. 다른 예로서, 캡(204f)은 강성 구성을 갖는 구조일 수 있거나 이를 포함할 수 있다.

MEMS 소자(204)의 캡(204f)은, 그림 9에 도시된 바와 같이, 포일(foil)(204h)(로 대체될 수 있다. 포일(204h)은 캐비티(204g) 내의 적어도 하나의 MEMS 구조(204e)를 밀봉 및 차폐할 수 있다. 즉, 포일(204h)은 MEMS 소자(204)의 적어도 하나의 MEMS 구조(204e)에 보호를 제공하도록 구성될 수 있다.

포일(204h)은, 그림 9에 도시된 바와 같이, 적어도 하나의 MEMS 구조(204e)에 측면으로 인접하게 그리고 MEMS 소자(204)의 제1 면(204a)에 배치된 밀봉 구조(204i)에 의해 적어도 하나의 MEMS 구조(204e)를 밀봉할 수 있다. 밀봉 구조(204i)는, 포일(204h) 및 MEMS 소자(204)(MEMS 소자(204)의 제1 면(204a))를 서로에 고정할 수 있다. 밀봉 구조(204i)는 포일(204h)에 및 MEMS 소자(204)에 접착 및 납땜될 수 있다.

그림 10은 칩 배열을 제조하는 방법(900)을 보여주고 있다. 그림 9에 도시된 칩 배열(800)에 관련해서, 캐리어 위에 MEMS 소자를 배치하는 단계(902)는 캐리어 위에 복수의 반도체 칩(402-1, 402-2, 402-3) 및 포일(204h)를 배치하는 단계를 포함할 수 있다. 포일(204h)은 복수의 반도체 칩(402-1, 402-2, 402-3)에 측면으로 인접하게 배치될 수 있다. 캐리어로부터 떨어져서 마주하는 포일(204h)의 면은 구축될 수도 있고 그렇지 않을 수도 있다.

캐리어 위에 MEMS 소자를 배치하는 단계(902)는 포일(204h) 위에 MEMS 소자(204)를 배치하는 단계를 더 포함할 수 있고, 여기서 포일(204h)은 MEMS 소자의 적어도 하나의 MEMS 구조(204e)를 밀봉할 수 있다. 이에 관련해서, MEMS 소자(204)의 제1 면(204a)은 포일(204h)과 마주할 수 있다.

포일(204h)은 밀봉 구조(204i)로 MEMS 소자(204)의 적어도 하나의 MEMS 구조(204e)를 밀봉할 수 있고, 이 밀봉 구조는 MEMS 소자(204)에 납땜 및 접착될 수 있다. 즉, MEMS 소자(204)는 밀봉 구조(204i)에 의해 포일(204h)에 고정될 수 있다. 포일(204h) 위에 배치될 수 있는 MEMS 소자(204)는 포일(204h)과 MEMS 소자(204)를 서로에게 전기적으로 연결하도록 구성될 수 있는 적어도 하나의 전기 전도성 상호연결(802)을 포함할 수 있다.