짧은 와이어 본드 형성 가능

플렉시블한 수정 및 변형도 장점

본 발명에 따르면, 짧은 와이어 본드들을 이용하여 많은 수의 반도체 다이들이 반도체 디바이스 내에 제공될 수 있게 하는 교번하는 계단형 반도체 다이 스택들을 포함하는 반도체 디바이스가 제공된다. 반도체 다이가 점점 얇아짐에 따라, 그리고 반도체 패키지들 내의 메모리 용량을 증가시키기 위하여, 반도체 패키지 내에 적층된 다이들의 개수가 점점 더 증가하고 있다. 하지만, 이러한 것은 상부 다이로부터 아래쪽 기판을 향한 본드들이 매우 길어지게 할 수 있다. 매우 긴 본드 와이어는 손상을 입기 쉽거나 혹은 다른 와이어 본드들과 쉽게 단락될 수 있으며, 또한 짧은 본드 와이어들에 비하여 높은 신호 대 잡음비를 갖는다.

발명의 설명

배경 기술

휴대용 소비자 전자제품에 대한 요구가 점점 커짐에 따라 고용량 저장 디바이스들에 대한 요구가 부각되고 있다. 가령, 플래시 메모리 저장 카드들 등과 같은 비휘발성 반도체 메모리 디바이스는, 디지털 정보의 저장 및 교환에 대한 점점 더 증대되는 요구를 충족시키기 위하여 더 널리 이용되고 있다. 이들의 휴대성, 다재다능함 및 견고한 설계는 이들의 높은 신뢰성 및 대용량과 함께 예컨대, 디지털 카메라, 디지털 음악 재생기, 비디오게임 콘솔, PDA 및 휴대전화 등을 포함하는 매우 다양한 전자 디바이스들에서 이러한 메모리 디바이스들이 이상적으로 이용될 수 있게 한다.

비록 다양한 많은 패키징 구성들이 알려졌지만, 플래시 메모리 저장 카드들은 자그마한 풋프린트 기판 상에 복수개의 다이들이 마운트되고 상호 연결되는 시스템-인-패키지(SiP) 혹은 멀티칩 모듈(MCM)로 제조되는 것이 일반적이다. 통상적으로 기판은 전도성 층이 한쪽 혹은 양쪽에 식각되어 있는 단단한 유전체 베이스를 포함할 수 있다. 다이와 전도성 층(들) 사이에서 전기적인 연결들이 형성되며, 전도성 층(들)은 다이를 호스트 디바이스에 연결하기 위한 리드 구조(lead structure)를 제공한다. 다이와 기판 사이에서 전기적인 연결들이 형성되면, 그 조립체는 몰딩 컴파운드로 둘러싸이며, 몰딩 컴파운드는 보호 패키지를 제공한다.

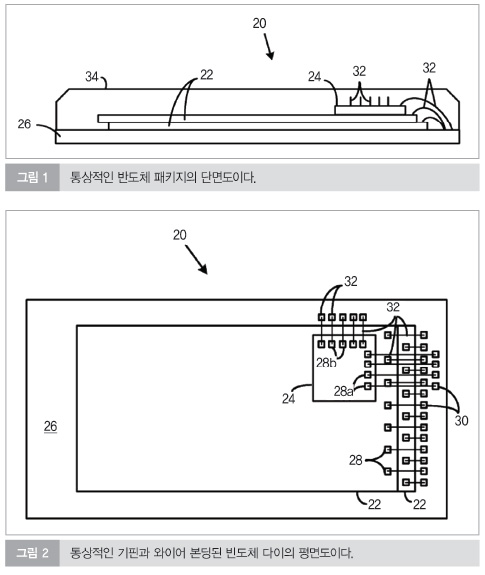

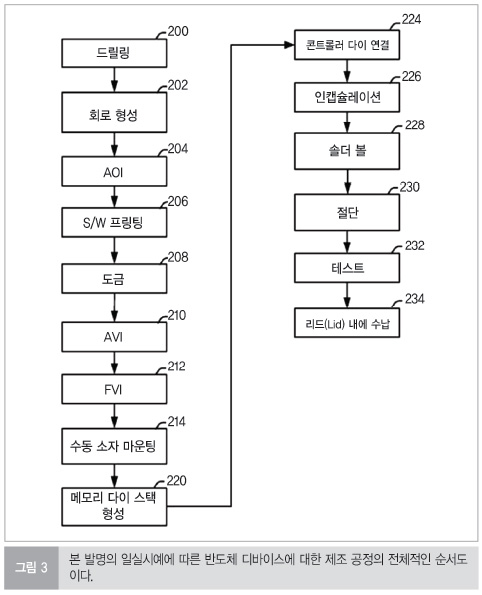

통상적인 반도체 패키지(20)의 단면도 및 평면도가 그림 1 및 그림 2에 도시된다(그림 2에는 몰딩 컴파운드가 없음). 전형적인 패키지들은 기판(26)에 부착된 플래시 메모리 다이(22) 및 컨트롤러 다이(24) 등과 같은 복수의 반도체 다이들을 포함한다. 다이 제조 공정 동안, 복수의 다이 본드 패드들(28)이 반도체 다이(22, 24) 상에 형성될 수 있다. 이와 유사하게, 복수의 콘택 패드들(30)이 기판(26) 상에 형성될 수 있다. 다이(22)는 기판(26)에 부착될 수 있으며, 그리고 다이(24)는 다이(22) 상에 마운트될 수 있다. 각각의 다이 본드 패드(28)와 콘택 패드(30) 쌍들 사이에 와이어 본드들(32)을 부착함으로써, 모든 다이들이 기판에 전기적으로 연결될 수 있다. 전기적인 모든 연결들이 형성되면, 다이 및 와이어 본드들은 몰딩 컴파운드(34) 내에 인캡슐레이션(encapsulation)될 수 있는 바, 이는 패키지를 밀봉하고 그리고 다이 및 와이어 본드들을 보호한다.

패키지 풋프린트를 가장 효율적으로 이용하기 위하여, 반도체 다이를 각각의 상부 위에 서로 적층하는 것이 알려져 있는바, 인접한 다이들 사이에 스페이서 층을 구비하면서 서로를 완전히 중첩하게끔 적층하거나 혹은 그림 1 및 그림 2에 도시된 바와 같이 오프셋(offset)을 갖게끔 적층할 수 있다. 오프셋 구성에서 다이는 다른 다이의 상부에 적층되며, 따라서 하부 다이의 본드 패드들은 노출된 채로 남는다. 오프셋 구성은 스택의 각각의 반도체 다이 상의 본드 패드들에 대한 편리한 액세스를 제공할 수 있다는 장점을 갖는다.

발명의 내용

해결하려는 과제

반도체 다이가 점점 얇아짐에 따라, 그리고 반도체 패키지들 내의 메모리 용량을 증가시키기 위하여, 반도체 패키지 내에 적층된 다이들의 개수가 점점 더 증가하고 있다. 하지만, 이러한 것은 상부 다이로부터 아래쪽 기판을 향한 본드들이 매우 길어지게 할 수 있다. 매우 긴 본드 와이어는 손상을 입기 쉽거나 혹은 다른 와이어 본드들과 쉽게 단락될 수 있으며, 또한 짧은 본드 와이어들에 비하여 높은 신호 대 잡음비를 갖는다.

발명을 실시하기 위한 구체적인 내용

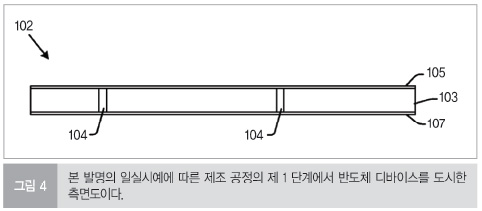

그림 3을 참조하여 본 발명이 설명될 것인바, 본 발명의 실시예들은 짧은 와이어 본드들을 이용하여 많은 수의 반도체 다이들이 반도체 디바이스 내에 제공될 수 있게 하는 교번하는 계단형(alternating stepped) 반도체 다이 스택을 포함하는 반도체 디바이스에 관한 것이다. 본 발명은 서로 다른 많은 형태들로 구현될 수도 있으며, 본 명세서에 서술된 실시예들만으로 한정되는 것이 아님을 유의해야 한다. 오히려, 이들 실시예들은 본 개시 내용이 철저하고 완벽해지도록 제공된 것이며 그리고 해당 기술분야의 당업자들에게 본 발명을 완전하게 전달해줄 것이다. 본 발명은 이들 실시예들의 대안예들, 수정예들 및 등가물들을 커버하도록 의도되었으며, 이들 대안예들 등은 청구범위에 정의된 바와 같은 본 발명의 범위 및 사상에 포함된다. 또한, 다음의 발명의 상세한 설명에서, 본 발명에 대한 완벽한 이해를 제공하기 위하여 다양한 세부 사항들이 서술된다. 하지만, 해당 기술분야의 당업자들라면 이러한 세부 내용들이 없이도 본 발명이 실시될 수도 있다는 점을 능히 이해할 수 있을 것이다.

본 명세서에 사용된 바와 같은 탑(top), 바닥(bottom), 상부(upper), 하부(lower), 수직 및 수평이라는 용어는 일례로서 그리고 예시를 위한 목적으로 사용된 것이며, 이러한 참조된 항목이 위치 및 방위에서 호환될 수 있기에, 본 발명의 설명을 한정하고자 의도된 것이 아니다. 또한, 본 명세서에서 사용되는 바와 같이, ‘실질적으로’ ‘대략적으로’ 또는 ‘약(about)’ 이라는 용어는, 주어진 애플리케이션에 대한 허용 가능한 제조 오차들 내에서 변동될 수 있는 특정 치수 혹은 파라미터를 의미한다. 일실시예에서, 허용 가능한 제조 오차는 ±.25% 이다.

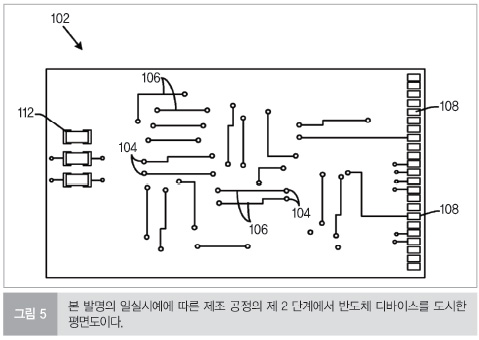

그림 3의 순서도 및 그림 4의 평면도 및 측면도들을 참조하여 본 발명의 실시예가 설명될 것이다. 비록 그림 4에서는 개별 디바이스(100) 혹은 이들의 일부를 도시하지만, 상기 디바이스(100)는 규모의 경제를 획득하기 위해 기판 패널 상의 복수의 다른 패키지들과 함께 배치 프로세스 될 수도 있음을 유의해야 한다. 기판 패널 상의 패키지들(100)의 로우들 및 컬럼들의 개수는 변할 수 있다.

기판 패널은 복수의 기판(102)들과 함께 시작된다(다시 한 번 말하지만, 이러한 하나의 기판이 그림 4에 도시된다). 기판(102)은 인쇄회로기판(PCB), 리드프레임 혹은 테이프 자동화 본딩된(TAB) 테이프를 포함하는, 다양한 종류의 칩 캐리어 매체가 될 수 있다. 기판(102)이 PCB인 경우, 기판은 그림 4에 도시된 바와 같이 탑 전도층(105)과 바닥 전도층(107)을 갖는 코어(103)로 구성될 수 있다. 상기 코어(103)는 예컨대, 폴리이미드 라미네이트, FR4 및 FR5를 포함하는 에폭시 수지, Bismaleimide Trianzine(BT), 기타 등등을 포함하는 다양한 유전 물질들로 형성될 수 있다. 비록, 본 발명에 대한 임계적인 내용은 아니지만, 상기 코어는 40㎛ 내지 200㎛의 두께를 가질 수 있으며, 대안적인 실시예들에서 코어의 두께는 상기 범위를 벗어날 수도 있다. 대안적인 실시예들에서 코어(103)는 세라믹 또는 유기물(organic)이 될 수도 있다.

코어를 둘러싸는 전도층(105, 107)은 구리 혹은 구리 합금, 도금된 구리 혹은 도금된 구리 합금, Alloy42(42Fe/58Ni), 구리 도금된 철, 혹은 기판 패널들 상에서 이용되는 공지된 다른 금속들 및 물질들로 형성될 수 있다. 전도층들은 약 10㎛ ~ 25㎛의 두께를 가질 수 있으며, 대안적인 실시예들에서 전도층들의 두께는 상기 범위를 벗어날 수도 있다.

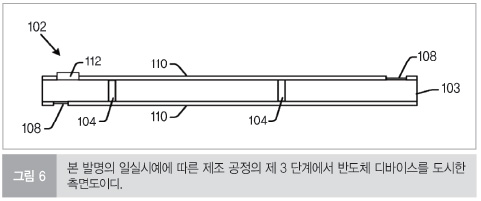

그림 3은 본 발명의 일실시예에 따라 반도체 디바이스를 형성하기 위한 제조 공정의 순서도이다. 단계 200에서, 기판(102)에 관통홀 비아(104)를 정의하도록, 기판(102)이 드릴링된다. 상기 비아(104)(도면들에서 이들 비아들 중 일부에만 도면부호가 부여됨)는 단지 일례로서 도시된 것이며, 기판은 도면에 도시된 것보다 훨씬 더 많은 비아들(104)을 포함할 수 있으며, 비아들(104)은 도면에 도시된 것과 다른 위치에 형성될 수도 있다. 다음으로, 단계 202에서, 탑 및 바닥 전도층들 중 하나 혹은 둘 다에 전도성 패턴이 형성된다. 예컨대, 그림 5 및 그림 6에 도시된 바와 같이, 전도성 패턴은 전기적인 트레이스들(106) 및 콘택 패드(108)를 포함할 수 있다. 트레이스들(106) 및 콘택 패드(108)(도면들에서 이들 중 일부에만 도면부호가 부여됨)는 단지 일례로서 도시된 것이며, 기판(102)은 도면에 도시된 것보다 더 많은 트레이스들 및 콘택 패드들을 포함할 수 있으며, 이들 트레이스들 및 콘택 패드들은 도면에 도시된 것과 다른 위치에 형성될 수도 있다.

본 발명의 실시예들에서, 완성된 반도체 디바이스(100)는 BGA 패키지로서 이용될 수 있다. 기판(102)의 하부 표면은 솔더 볼을 받아들이기 위한 콘택 패드(108)를 포함할 수 있으며, 이에 대해서는 후술한다. 다른 실시예들에서, 완성된 반도체 디바이스(100)는, 완성된 디바이스(100)를 호스트 디바이스 내에 착탈 가능하게 접속하기 위한 콘택 핑거를 포함하는 LGA 패키지가 될 수 있다. 이러한 실시예에서, 하부 표면은 솔더 볼을 수용하는 콘택 패드 대신에 콘택 핑거를 포함할 수 있다. 기판(102)의 탑 및 바닥 표면들 상의 전도성 패턴은, 예컨대, 다양한 포토리소그래픽 공정들을 포함하는 공지된 다양한 공정들에 의해서 형성될 수 있다.

다시 그림 3을 참조하면, 기판(102)은 단계 204의 자동 광 검사(automatic optical inspection: AOI)에서 검사될 수 있다. 검사된 후, 솔더 마스크(110)가 단계 206에서 기판에 적용될 수 있다. 솔더 마스크가 적용된 이후에, 콘택 패드, 콘택 핑거 및 전도성 패턴들 상의 임의의 다른 솔더 영역들은, 공지된 전기도금법 혹은 얇은 필름 증착 공정을 이용하여 단계 208에서 Ni/Au, Alloy42, 기타 등등으로 도금될 수 있다. 다음으로, 기판(102)은 전기적인 동작을 체크하고 그리고 오염, 스크래치, 및 변색(discoloration)에 대해서, 자동화된 검사 공정(automated inspection process)(단계 210) 및 최종적인 시각 검사(final visual inspection)(단계 212)에서 검사 및 테스트될 수 있다.

상기 기판(102)이 검사를 통과했다고 가정하면, 수동 소자들(112)이 단계 214에서 기판에 부착될 수 있다. 하나 이상의 수동 소자들은, 예컨대, 하나 이상의 커패시터들, 저항들 또는 인덕터들을 포함할 수 있으며, 다른 소자들도 또한 고려될 수 있다. 도시된 수동 소자들(112)(도면들에서 이들 중 일부에만 도면부호가 부여됨)은 단지 일례일 뿐이며, 이들의 개수, 유형 및 위치는 실시예에서 변할 수 있다.

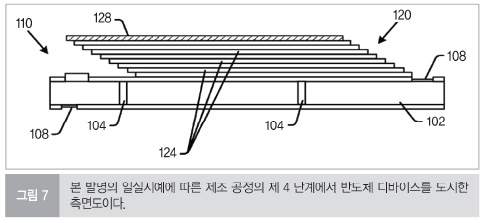

다음으로 본 발명의 기술에 따르면, 다수의 반도체 다이 스택들이 단계 220에서 기판(102) 상에 형성될 수 있다. 아래에 설명되는 바와 같이, 각각의 다이 스택은 반대되는 방향으로 적층(stepped)될 수 있으며, 여기서 인접한 다이 스택들 사이의 인터포저 층(interposer layer)에 의해서 인접한 다이 스택들 간의 천이(transition)가 이루어진다. 그림 7을 참조하면, 다수의 반도체 다이들(124)이 오프셋 계단 구조(offset stepped configuration)로 서로의 위에 적층되어 제 1 다이 스택(120)을 형성할 수 있다. 다이는 다이 부착 필름을 이용하여 기판에 부착되거나 또는 서로 부착될 수 있다. 일실시예에서, 다이 부착 접착제는 Henkel AG & Co. KGaA 회사의 8988UV 에폭시가 될 수 있는데, 이는 B-스테이지로 큐어링되어 스택(120) 내의 다이(124)를 예비적으로 부착하며, 그리고 이에 후속하여 최종 C-스테이지로 큐어링되어 스택(120) 내의 다이(124)를 항구적으로 부착한다. 예를 들어, 반도체 다이(124)는 가령, 낸드(NAND) 플래시 메모리 다이와 같은 메모리 다이가 될 수도 있지만, 다른 유형의 다이들(124)도 또한 이용될 수 있다. 그림 7은 8개의 다이들(124)이 스택(120)에 마운트되는 일실시예를 도시한다. 하지만, 다른 실시예에서는 8개의 다이들보다 더 많거나 더 적은 다이들(124)이 스택(120)에 존재할 수 있다.

다이 스택(120)이 형성된 이후, 그림 7에 도시된 바와 같이, 인터포저 층(128)이 스택(120)의 상부 다이(124)에 부착될 수 있다. 인터포저 층(128)은 스택(120) 내의 다른 다이(124)처럼, 동일한 방식으로 그리고 동일한 양 만큼 오프셋될 수 있다. 인터포저 층(128)은 예컨대, FR4 및 FR5로 형성된 단단한 층이 될 수도 있으며 또는 예컨대, 폴리이미드 테이프로 형성된 가요성 층(flexible layer)이 될 수도 있다. 인터포저 층의 상부 표면 상에는 전도성 패턴이 형성된다. 아래에 설명되는 바와 같이, 전도성 패턴과 인터포저 층은, 인터포저 층(128)의 일측 상의 콘택 패드들로부터 인터포저 층(128)의 반대 상의 대응 콘택 패드들로 신호를 전송하기 위한 목적으로 제공된다.

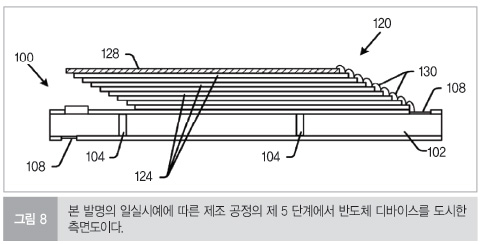

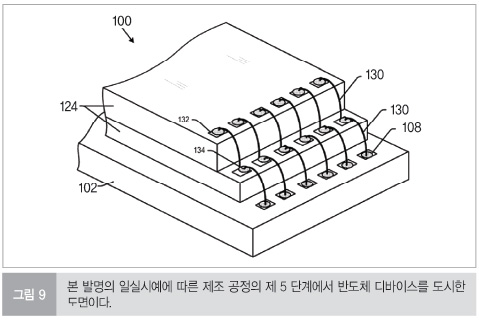

그림 8의 측면도를 참조하면, 다이 스택(120)이 형성되면, 스택(120) 내의 각각의 다이(124)는 와이어 본드(130)를 이용하여 기판에 전기적으로 연결될 수 있다(스택의 각각의 다이를 기판(102)에). 그림 9는 다이 스택(120) 내의 오직 2개의 아래쪽 다이들(124)과 기판(102)을 도시하는 간략화된 투시도이다. 도시된 바와 같이, 각각의 반도체 다이(124)는 다이(124)의 에지를 따라 있는 다이 본드 패드들(132)의 로우(row)를 포함할 수 있다. 각각의 다이(124)는 그림 9에 도시된 것보다 훨씬 많은 다이 본드 패드(132)를 포함할 수 있음을 유의해야 한다. 반도체 다이의 각각의 다이 본드 패드(132)는, 인접한 다음 반도체 다이의 대응하는 다이 본드 패드(132)에 와이어 본드(130)를 이용하여 전기적으로 연결될 수 있다. 바닥 반도체 다이(124)의 각각의 다이 본드 패드(132)는, 와이어 본드(130)를 이용하여 기판(102) 상의 콘택 패드들의 로우에 있는 대응 콘택 패드에 전기적으로 연결될 수 있다.

비록, 다양한 기술들을 이용하여 와이어 본드(130)가 형성될 수 있지만, 본 발명의 일실시예에서 와이어 본드(130)는 리버스 볼 본드(reverse ball bond)로 형성된다. 이들은 공지된 구조의 와이어 본딩 캐필러리(capillary)(미도시)를 이용하여 가령, 바닥 다이(124)와 같은 다이의 다이 본드 패드들 상에 볼 본드(134)를 먼저 형성함으로써, 만들어질 수 있다. 와이어 본딩 캐필러리의 중앙 캐비티를 통해 소정 길이의 와이어(전형적으로는 금 혹은 은 합금)를 공급함으로써, 볼 본드(134)(그림 9에서는 이들 중 하나에 도면부호가 부여됨)가 형성될 수 있다. 와이어는 캐필러리의 끝을 통해 돌출되며, 캐필러리 끝에 관련된 트랜스듀서로부터 고전압 전기 전하가 와이어에 인가된다. 이러한 전기 전하는 상기 캐필러리의 끝에서 와이어를 녹이며, 그리고 용융 금속의 표면 장력으로 인하여 와이어는 볼(134) 형상이 된다. 다음으로, 트랜스듀서가 초음파 에너지를 인가하는 동안, 상기 볼(134)은 하중(load)의 인가 하에서 다이 본드 패드(132)에 부착될 수 있다.

다음으로 와이어 본딩 캐필러리는 짧은 길이의 와이어가 나오게 할 수 있으며, 그리고 상기 와이어는 전도성 볼에서 절단되어 다이 본드 패드(132) 상에 볼 본드(134)가 남겨질 수 있다. 캐필러리의 끝에 매달려 있는 짧은 와이어 꼬리는 상기 로우에 있는 다음번 다이 본드 패드(132)를 위한 볼 본드(132)를 형성하는데 이용될 수 있다. 예컨대, 스터드 범핑 혹은 웨이퍼 레벨에서의 골드 범핑을 포함하는 다양한 다른 방법들에 의해서 혹은 다양한 또 다른 방법들에 의해서, 볼 본드(134)가 반도체 다이(124)의 본드 패드들에 형성될 수 있다. 그 이후에, 앞서 설명된 바와 같이, 다음 아래쪽 레벨 상에(예컨대, 기판 102 상에) 다른 볼 본드가 형성된다. 하지만, 와이어를 절단하는 대신에, 상기 와이어가 풀려져 나와서 다음 높이 레벨 상의 대응 볼 본드(134)와 접촉하게 될 수도 있다(비록, 다른 실시예들에서는 하나 이상의 레벨들을 빼먹을 수도 있지만). 트랜스듀서가 초음파 에너지를 인가하는 동안, 와이어는 하중의 인가 하에서 볼 본드(134)에 적용된다. 열, 압력 및 초음파가 결합된 에너지는 와이어와 볼 본드(134) 사이에서 본딩을 생성한다. 이후, 와이어 본딩 캐필러리는 짧은 길이의 와이어를 풀어낼 수 있으며, 그리고 상기 와이어가 절단되어 서로 다른 레벨들 상의 대응 패드들 사이에서 와이어 본드(130)를 형성할 수 있다. 이러한 공정은, 모든 와이어 본드들(130)이 형성될 때까지, 다이와 기판 상의 패드들을 가로질러 수평적으로 그리고 다이와 기판 상의 패드들 사이에서 수직적으로 반복될 수 있다. 와이어 본드(130)들이 수평적으로 혹은 수직적으로 형성되는 순서는 실시예들에 따라 다를 수 있다. 또한, 와이어 본드(130)들은 일반적으로 다이 스택(120)내의 하나의 층으로부터 다음 층으로 그리고 기판 쪽으로 일직선인 수직 컬럼의 형태로 도시되고 있지만, 하나 이상의 와이어 본드들은 하나의 층으로부터 다른 층으로 대각선 방향으로 연장될 수도 있다. 또한, 와이어 본드들은 다이 스택(120)의 하나 이상의 층들을 스킵할 수도 있다.

전술한 바와 같이, 인터포저 층(128)이 다이 스택(120)의 최상부 위에 부착될 수 있다. 인터포저 층(128)은 제 1 에지(128a)를 포함할 수 있는데, 제 1 에지(128a)는 그 개수 및 위치에 있어서 인터포저 층(128) 아래의 다이 스택(120)의 다이(124) 상의 다이 본드 패드(132)들의 로우에 대응하는 콘택 패드들의 로우를 갖는다. 인터포저 층(128)의 상기 에지(128a) 상의 콘택 패드들의 로우와 아래에 인접합 다이(124)(다이 스택 120의 꼭대기에 있는 다이) 사이에 와이어 본드들(130)이 형성될 수 있다(전술한 와이어 본드 130와 동일한 방식으로).

이러한 방식으로 인터포저 층(128)에 와이어 본딩하는 것은 통상적인 시스템에 비하여 장점을 갖는다. 먼저, 인터포저 층(128)에 와이어 본딩하기 위한 별도의 공정 혹은 별도의 장비(tool)가 필요치 않다는 점이다. 인터포저 층(128)에 와이어 본딩하는 것은, 인터포저 층 아래의 다이(124)에 와이어 본딩하는 것과 동일하다. 또한, 와이어 본드들이 인터포저 층(128)의 탑 표면의 콘택 패드들 상에 형성되기 때문에, 상기 콘택 패드들은 눈에 보이며 와이어 본드들이 눈에 보이는 콘택 패드들 상에 형성될 수 있으며, 그리고 예컨대, 인터포저 층의 하부 표면에 본딩을 시도하는 설계들(눈에 보이지 않으며 또는 용이하게 액세스할 수 없는 설계들)에 비하여 좀더 용이하게 시각적으로 검증될 수 있다.

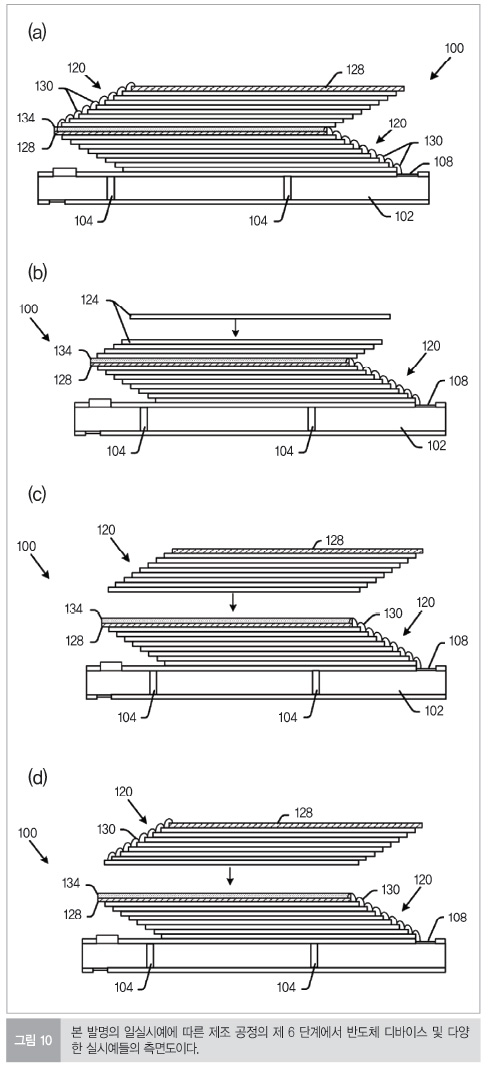

그림 10의 측면도를 참조하면, 다음으로 제 2 다이 스택(120)이 인터포저 층(128) 및 제 1 다이 스택(120)의 꼭대기 위에 부착될 수 있다. 앞서 설명한 바와 같이, 제 1 다이 스택(120)의 최상층 다이는 인터포저 층(128)의 탑 표면 상에 와이어 본딩된다. 이들 와이어 본딩들을 손상시키지 않기 위하여, 필름층(134)이 인터포저 층(128)의 상부 표면 상에 제공된다. 인터포저 층(128) 상의 와이어 본드(130)들은 필름층(134) 내에 매립되며, 상기 필름층(134)은 인터포저 층(128)으로부터 제 2 다이 스택(120)을 이격시킨다. 상기 필름층(134)은 이용 가능한 공지된 조성을 갖는 예컨대, 전기적으로 절연성인 접착제 에폭시가 될 수 있으며, 이러한 것들은 일본에 있는 니토-덴코(Nitto-Denko) 회사 혹은 캘리포니아에 있는 헨켈(Henkel) 회사로부터 입수할 수 있다.

필름층(134)은 점성이 있는 액체로 도포될 수 있으며, 이것은 리플로우 공정에서 큐어링될 때까지 그 상태를 유지하는바, 이에 대해서는 후술한다. 본 발명의 실시예들에서, 필름층(134)은 액체로 도포되지만, 제 2 다이 스택을 기계적으로 지지할 수 있는 충분한 고점성을 갖는다. 일실시예에서, 점성은 예를 들어 약 1-2 ×106센티포이즈(centipoise)가 될 수 있지만, 대안적인 실시예에서 상기 점성은 이보다 높은 수도 혹은 낮을 수도 있다.

대안적인 실시예에서, 스페이서 볼(spacer balls)들이 필름층(134) 내에 제공될 수도 있다. 스페이서 볼들은 제 2 다이 스택과 인터포저 층 사이에서 스페이서들로서 작용하는 중합 구체(polymeric spheres)가 될 수 있다. 이러한 스페이서 볼들은 해당 기술분야에 공지되어 있으며 예컨대, ‘Method for making a semiconductor package including stacked semiconductor die’라는 명칭의 미국등록특허 US 6,650,019에 개시되어 있는바, 상기 미국등록특허는 본 발명에 대한 참조로서 그 전체 내용이 본 명세서에 통합된다. 필름층(134)은 인터포저 층(128)으로의 와이어 본드들(130)을 그 안에 매립할 수 있을 정도의 두께를 가질 수 있으며, 따라서 제 2 다이 스택(120)의 바닥 다이는 매립된 와이어 본드(130)와 접촉하지 않는다.

필름층(134)이 인터포저 층(128)에 적용되면, 제 2 다이 스택(120)이 제 1 다이 스택(120) 위에 부착될 수 있으며 그리고 기판에 와이어 본딩될 수 있다. 특히, 인터포저 층(128)은 상기 제 1 에지의 반대편인 인터포저 층의 제 2 에지 상에 콘택 패드들의 제 2 로우를 포함한다. 인터포저 층(128) 상의 전도성 패턴은, 인터포저 층의 제 1 에지 상의 콘택 패드들과 인터포저 층의 제 2 에지 상의 대응하는 콘택 패드들을 전기적으로 연결한다.

인터포저 층(128)의 제 2 에지 상의 대응하는 콘택 패드들과 제 2 다이 스택(120)의 가장 아래쪽 다이(124) 사이에 와이어 본드130들(130)이 형성된다. 이러한 방식으로, 제 2 다이 스택의 가장 아래쪽 다이로부터의 다이 본드 패드들(132)은, 인터포저 층(128)의 전기적 트레이스들을 통해, 제 1 다이 스택의 가장 위쪽 다이 상의 대응 다이 본드 패드(132)들에 전기적으로 연결될 수 있다. 이와 같이, 제 2 다이 스택 내의 다이(124)는 오직 짧은(예컨대, 단일 점프) 와이어 본드들(130)만을 이용하여 기판(102)에 전기적으로 연결될 수 있다.

제 2 다이 스택(120) 내의 다이(124)는 제 1 다이 스택 내의 다이(124)와 동일한 방식으로 동일한 정도만큼 적층되지만, 반대되는 방향으로 적층되며, 따라서 제 1 다이 스택 및 제 2 다이 스택(120)의 풋프린트를 함께 최소화할 수 있다. 제 2 스택 다이는 인터포저 층(128)의 최상부 위에 여러 방법으로 형성될 수 있다. 그림 10의 (b)에 도시된 일례에서, 제 2 다이 스택(120)은 제 1 다이 스택(120)과 동일한 방식으로 형성될 수 있다. 각각의 다이 (124)는 오프셋 계단형 구조로 디바이스(100)에 부가될 수 있다. 제 2 다이 스택(120)의 모든 다이들이 스택에 부착되면, 전술한 바와 같이, 다이(124)는 서로서로 및 기판과 와이어 본딩될 수 있다.

그림 10의 (c)에 도시된 제 2 실시예에서, 다이(124) 및 제 2 다이 스택(120)은 디바이스(100)와는 별개로 서로 조립될 수 있으며, 그리고 디바이스(100)의 중요 조립 경로의 일부가 아닐 수도 있다. 제 2 다이 스택(120)는 조립될 수 있으며 그리고 미리 조립된 단일 스택으로서 인터포저 층(128) 및 필름층(134) 상에 전술한 바와 같이 부착될 수 있다. 제 2 다이 스택(120)이 스택에 부착되면, 제 2 다이 스택(120) 내의 다이(124)는 서로서로 및 기판과 전술한 바와 같이 와이어 본딩될 수 있다.

그림 10의 (d)에 도시된 제 3 실시예는 그림 10의 (c)에 도시된 바와 같은 미리 조립된 다이 스택(120)을 가질 수 있지만, 그림 10의 (d)의 일례에서, 제 2 다이 스택(120) 내의 다이(124)는 디바이스(100)와는 별개로 서로 와이어 본딩될 수 있으며 그리고 디바이스(100)의 중요 조립 경로의 일부가 아닐 수도 있다. 이러한 일례에서는, 디바이스(100)에서 필요로 하는 와이어 본드들만이, 제 2 다이 스택의 바닥 다이(124)의 다이 본드 패드들을 인터포저 층(128)에 연결한다.

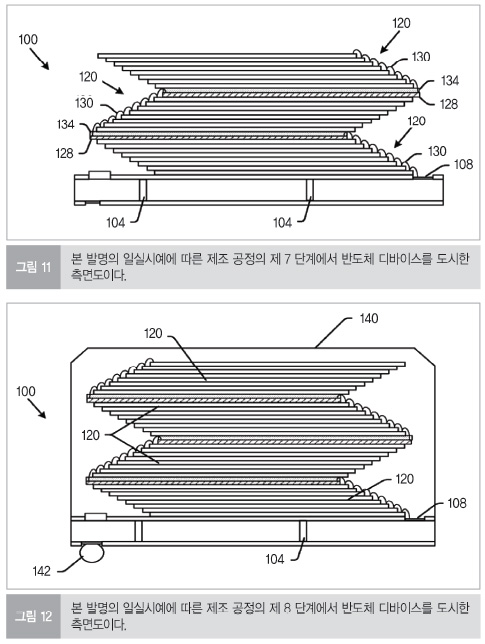

그림 11의 측면도를 참조하면, 추가적인 다이 스택들(120)이, 제 2 다이 스택(120)이 제 1 다이 스택에 부가되었던 것과 동일한 방식으로 디바이스(100)에 부가될 수 있다. 모든 다이 스택들의 풋프린트를 함께 최소화하기 위하여, 각각의 다이 스택은 그 아래에 있는 다이 스택과 반대되는 방향으로 적층될 수 있다. 그림 11은 총 24개의 다이들에 대해서 3개의 다이 스택들을 포함하는 일례를 예시한다. 그림 12는 총 32개의 다이들에 대해서 4개의 다이 스택들을 포함하는 일례를 예시한다. 예시된 디바이스들은 단지 일례일 뿐이며, 본 발명의 기술에 따른 더 많거나 더 적은 다이 스택들을 가질 수 있으며, 각각의 다이 스택은 더 많거나 더 적은 다이들을 포함할 수 있다. 또 하나의 일례로서, 8개의 다이 스택들(120)이 존재할 수 있으며, 그 각각은 8개의 다이들(124)을 포함하여 총 64개의 다이들이 디바이스(100)에 존재할 수 있다.

추가적인 다이 스택(120)이 디바이스(100)에 부가되는 경우, 아래에 있는 다이 스택(120)은 인터포저 층(128)과 필름층(134)을 포함할 수 있으며, 그리고 와이어 본딩이 전술한 바와 같이 형성될 수 있다. 디바이스(100)에 있는 최상층 다이 스택(120)은 인터포저 층(128)과 필름층(134)을 포함할 필요가 없다.

기판(102) 상에 다이 스택(120)을 마운트한 이후에, 컨트롤러 다이(미도시)가 마운트될 수 있으며 그리고 기판에 와이어 본딩될 수 있다(단계 224). 일실시예에서, 컨트롤러 다이는 최상층 다이 스택(120) 상에 마운트될 수 있다. 다른 실시예에서, 컨트롤러 다이는 최하층 다이 스택(120) 밑에 마운트될 수 있다. 예를 들어, 컨트롤러 다이는 기판(102)의 최상부 위에 마운트될 수 있다. 이러한 실시예의 일례는, 국제출원이 2013년 1월 9일이고 ‘Semiconductor Device Including an Independent Film Layer For Embedding and/or Spacing Semiconductor Die’라는 명칭의 국제출원(PCT/CN2013/070264)에 개시되어 있다. 또 다른 일례로서, 컨트롤러 다이는 기판(102) 내에 마운트될 수도 있다. 이러한 실시예의 일례는 국제출원이 2013년 1월 28일이고 ‘Semiconductor Device Including an Embedded Controller Die and Method of Making Same’라는 명칭의 국제출원(PCT/CN2013/071051)에 개시되어 있다. 상기 2개의 국제출원들 모두는 본 발명에 대한 참조로서 그 전체 내용이 본 명세서에 통합된다.

마운팅 및 다이 스택과 컨트롤러 다이의 전기적 연결 이후에, 그림 12에 도시된 바와 같이 단계 226에서 다이 스택들, 와이어 본드들 및 기판의 적어도 일부가 몰드 컴파운드(140)로 인캡슐레이션될 수 있다. 몰드 컴파운드(140)는 예를 들어, 고체 에폭시 수지(solid epoxy resin), 페놀 수지, 용융 실리카(fused silica), 결정질 실리카(crystalline silica), 카본 블랙(carbon black) 및/또는 금속 수산화물(metal hydroxide)을 포함할 수 있다. 이러한 몰드 컴파운드들은 예를 들어, 스미토모 회사와 니토-덴코 회사(두 회사 모두 일본에 본사가 있음)로부터 입수할 수 있다. 다른 제조자들로부터의 다른 몰드 컴파운드들도 또한 고려될 수 있다. 몰드 컴파운드는 예를 들어 트랜스퍼 몰딩 또는 인젝션 몰딩 기법을 포함하는 공지된 다양한 공정들을 따라 적용될 수 있다. 다른 실시예들에서, 인캡슐레이션 공정은 FFT(Flow Free Thin) 압축 몰딩에 의해서 수행될 수도 있다.

가령, 다이 접착 필름 및 필름층(134)과 같은, 큐어링 가능한 B-스테이지 접착제들은 인캡슐레이션 공정 동안, 최종 교차-결합된(cross-linked) C-스테이지로 큐어링될 수 있다. 다른 실시예들에서, 접착제들은 별도의 가열 공정에서 C-스테이지로 큐어링될 수도 있다.

그림 12에 도시된 바와 같이, 패널 상의 다이가 단계 226에서 인캡슐레이션된 이후, 디바이스가 BGA 패키지인 실시 예들인 경우, 솔더 볼(142)이 단계 228에서 각 패키지의 바닥 표면 상의 콘택 패드에 솔더링될 수 있다. 패키지들이 LGA 패키지인 경우 단계 226은 생략될 수 있다.

각각의 패키지들은 단계 230에서 패널로부터 절단되어(singulated), 그림 12에 도시된 바와 같은 완성된 반도체 디바이스(100)를 형성한다. 각각의 반도체 디바이스(100)는, 톱질(sawing), 워터 제트 컷팅, 레이저 컷팅, 워터 유도 레이저 컷팅, 건식 매체 컷팅(dry media cutting), 및 다이아몬드 코팅 와이어 컷팅을 포함하는 다양한 컷팅 방법들 중 임의의 방법에 의해서 절단될 수 있다. 비록, 일반적으로 직선형 컷팅들은 직사각형 혹은 정사각형 형상의 반도체 디바이스(100)를 정의할 것이지만, 반도체 디바이스(100)는 본 발명의 다른 실시예들에서 직사각형 및 정사각형 이외의 형상을 가질 수도 있음을 유의해야 한다.

패키지들(100)로 컷팅되면, 상기 패키지들이 단계 232에서 테스트되어, 상기 패키지들이 적절히 기능하는지가 판별된다. 해당 기술분야에 알려진 바와 같이, 이러한 테스팅은 전기적 테스트, 번인 테스트 및 다른 테스트들을 포함할 수 있다. 선택적으로는, 단계 234에서, 완성된 반도체 디바이스들이 리드(lid)(미도시) 내에 매립(encased)될 수 있다(예컨대, 반도체 디바이스들이 LGA 패키지들인 경우).

완성된 반도체 패키지(100)는 예를 들어, MMC 카드 등의 메모리 카드, SD 카드, 다용도(multiuse) 카드, 마이크로-SD 카드, 메모리 스틱, 컴팩 SD 카드, ID 카드, PCMCIA 카드, SSD 카드, 칩-카드, 스마트카드, USB 카드, MCP-유형 매립 카드 저장장치, 기타 등등이 될 수 있다.