범프와 패드를 직접적으로 접합하는 데는, 가압ㆍ가열 시간으로서 소요의 시간과 Al전극을 구성하는 Al을 모두 AuAl합금으로 바꾸는 시간이 필요하다. 이로 인해 반도체 칩 내장 배선 기판을 형성하는 데 걸리는 시간이 길어진다. 본 발명은 상기 반도체 칩의 접속 신뢰성을 높이면서 제조공정을 간소화할 수 있어서 제조 시간을 단축할 수 있는 반도체 칩 내장 배선 기판의 제조 방법을 제공하는 것을 제 1 목적으로 한다. 또한, 반도체 칩의 접속 신뢰성을 높일 수 있는 반도체 칩 내장 배선 기판을 제공하는 것을 제 2 목적으로 한다.

배경 기술

종래, 열가소성 수지를 포함하는 절연 기재에 배선부가 형성되고, 전자 부품이 내장된 부품 내장 기판의 제조 방법으로서, 예를 들면, 특허 문헌 1(일본국 특개2007-324550호 공보)에 기재된것이 알려져 있다. 이 제조 방법에서는 표면에 도체 패턴이 형성된 수지 필름, 비아 홀 내에 도전성 페이스트가 충전된 수지 필름을 포함하는 여러 장의 수지 필름을, 전자 부품을 내장하도록 적층하여 적층체로 한다. 그리고 적층체에 대하여 상하로부터 가압하면서 가열하는 것으로 수지 필름에 포함되는 열가소성 수지를 연화시키고, 이에 따라 수지 필름을 상호 접착하여 일괄해서 일체화하는 것과 함께, 전자 부품을 밀봉한다. 또한, 비아 홀 내에 충전한 도전 페이스트를 소결하여 층간 접속부(도전성 조성물)를 형성하고, 전자 부품의 전극과 대응하는 패드(도체 패턴)나 도체 패턴끼리를 전기적으로 접속한다. 이에 따르면, 전자 부품을 내장하는 다층 기판을 가압·가열에 의해 일괄해서 형성할 수 있어서, 제조 공정을 간소화할 수 있다.

그런데 소자가 집적된 반도체 칩(IC칩)에서는 소자의 고집적화, 고속화, 반도체 칩의 체격의 증대 억제 등 때문에, 전극의 간격이 파인 피치화되고 있다. 이 때문에, 내장되는 전자 부품으로서 반도체 칩(베어 칩)을 채용하고, 재배선하지 않고 플립 칩 실장하는 경우, 상기한 방법에서는 이웃하는 층간 접속부 간에서의 전기 절연성을 확보하고자 하면, 매우 소직경(예를 들면, 직경 수㎛~10㎛ 정도)의 비아 홀을 형성하지 않으면 안 되서, 비아 홀의 형성이나 도전성 페이스트의 충전이 곤란하게 되는 것이 생각된다.

또한, 도전성 페이스트의 충전량도 적기 때문에 반도체 칩의 전극이나 기판의 패드를 구성하는 금속과 확산 접합하는 데 충분한 양의 도전성 입자를 확보할 수 없는 것도 생각된다. 이에 대하여, 반도체 칩의 전극에 스터드 범프를 설치하고, 이 스터드 범프를 기판의 패드에 접속하는 플립칩 실장을 채용하는 것도 생각된다. 그중에서도 특허 문헌 2(일본국 특개2001-60602호 공보)에 기재된 바와 같이, 가압하면서 가열하는 것으로 반도체 칩의 Au범프와 기판의 구리 패드(전극)를 직접적으로 접합하면, 파인 피치에 대응하면서 전기적인 접속 신뢰성을 향상시킬 수 있다.

발명의 내용

발명을 실시하기 위한 구체적인 내용

제 1 실시 형태

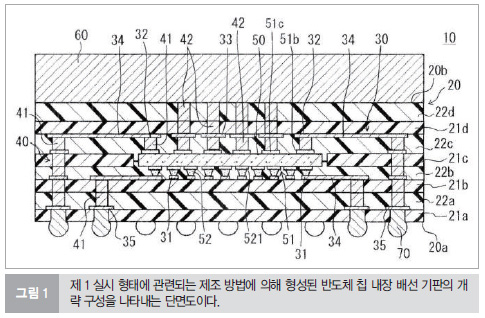

본 실시 형태에 관련되는 절연 기재(20)는 그림 1에 나타내는 바와 같이, 두께 방향에 있어서, 일면(20a)측으로부터 열경화성 수지 필름(21a), 열가소성 수지 필름(22a), 열경화성 수지 필름(21b), 열가소성 수지 필름(22b), 열경화성 수지 필름(21c), 열가소성 수지 필름(22c), 열경화성 수지 필름(21d), 열가소성 수지필름(22d)의 차례로 합계 8장의 수지 필름이 적층되어 이루어진다. 즉, 열가소성 수지 필름과 열경화성 수지 필름이 번갈아 적층되어 절연 기재(20)가 구성되어 있다. 또한, 열경화성 수지 필름(21a~21d)으로서, 유리 섬유 등의 무기 재료를 포함하지 않는, 열경화성 폴리이미드(PI)로 이루어지는 필름을 채용하고 있다. 한편, 열가소성 수지 필름(22a~22d)으로서, 유리 섬유 등의 무기재료나 선팽창 계수 등을 조정하기 위한 무기 필러를 포함하지 않는, 폴리에테르에테르케톤(PEEK) 30중량%와 폴리에테르이미드(PEI) 70중량%로 이루어지는 수지 필름을 채용하고 있다.

상기한 수지 필름 중, 열경화성 수지 필름(21b)이 반도체 칩(50)이 실장되는 기판(제 1 필름)에 상당하고, 열가소성 수지 필름(22b)이 반도체 칩(50)과 기판으로서의 열경화성 수지 필름(21b)의 사이를 밀봉하는 제 2 필름에 상당한다. 도체 패턴(30)은 도체박을 패터닝하여 이루어지는 것이고, 반도체 칩(50)과 외부를 전기적으로 접속하는 배선부로서 이용되는 것이다. 나아가서는, 전기적인 배선부 뿐만 아니라, 반도체 칩(50)에 구성된 소자의 동작에 의한 열을 외부로 방열하기 위한 방열 배선부로서 이용할 수도 있다.

본 실시 형태에서는 도체 패턴(30)과 층간 접속부(40)에 의해 반도체 칩(50)의 전극(51a, 51b)과 외부 접속용 전극(35)을 전기적으로 접속하는 배선부가 구성되어 있다. 또한, 상기 배선부를 구성하는 도체 패턴(30) 및 층간 접속부(40)는 별도의 도체 패턴(30)및 층간 접속부(40)에 의해 반도체 칩(50)의 더미 전극(51c)과 방열 부재(60)를 열적으로 접속하는 방열 배선부가 구성되어 있다.

또한, 전극(51a)은 후에 상세히 설명하지만, 가압·가열 공정 전에는 반도체 칩(50)에 설치된 Al계 재료로 이루어지는 전극이다.

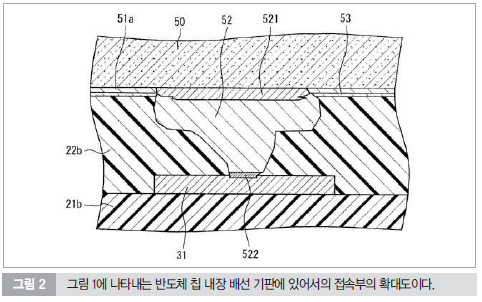

그러나 가압·가열 공정 후에 있어서는, 전극(51a)의 접속부(52)와 대향하는 부위의 두께 방향에 있어서, 전극(51a)을 구성하는 모든 Al이 AuAl합금화되어 Au4Al합금을 주로 포함하고 있는 AuAl합금층(521)으로 된다(그림 2 참조). 즉, 접속부(52)의 바로 아래는 AuAl합금층(521)으로 된다. 바꾸어 말하면, 반도체 칩(50)과 접속부(52)에 의하여 끼워진 부위는 전극(51a)을 구성하는 Al을 포함하지 않는 AuAl합금층(521)으로 된다. 또한, 적어도 반도체칩(50)과 접속부(52)에 의하여 끼워진 부위, 즉, 전극(51a)의 접속부(52)와 대향하는 부위의 두께 방향의 모두가 AuAl합금층(521)이면 좋다. 다만 그림 2에 나타내는 바와 같이 예를 들면, SiN 등으로 이루어지는 절연막(53)으로 덮인 부위는 전극(51a)을 구성하는 Al이 남아 있다.

배선부는 구체적으로, 도체 패턴(30)이 구리(Cu)박을 패터닝하여 이루어진다. 그리고 도체 패턴(30)으로서, 반도체 칩(50)의 전극(51a)에 대응하는 패드(31), 마찬가지로 전극(51b)에 대응하는 패드(32), 마찬가지로 더미 전극(51c)에 대응하는 패드(33), 수직방향으로 연장된 가로 배선부(34)를 포함하고 있다. 나아가서는, 외부기기와의 접속에 이용되는 외부 접속용 전극(35)도 도체 패턴(30)의 일부로서 포함하고 있다. 그리고 각 패드(31~33)는 반도체 칩(50)의 대응하는 전극(51)의 피치에 맞춘 피치로 설치되어 있다. 본 실시 형태에서는 전극(51a)이 1변 10개로 일렬인 직사각형 환상으로 배치되어 있으며, 전극(51a)에 대응하는 패드(31)도 전극(51a)의 배치에 대응하여 복수의 패드(31)가 직사각형 환상으로 설치되어 있다. 그리고 각 패드(31)는 그림 1에 나타내는 바와 같이, 동일층에 설치된 가로 배선부(34)에 의해 직사각형 환상의 고리의 외측 또는 내측으로 인출(재배선)되어 층간 접속부(40)와 접속되어 있다.

Cu로 이루어지는 도체 패턴(30)과 Ag-Sn합금으로 이루어지는 층간 접속부(40)의 계면에는 Cu와 Sn이 상호 확산하여 이루어지는 금속 확산층(Cu-Sn합금층)이 형성되고, 이에 따라, 도체 패턴(30)과 층간 접속부(40)의 접속 신뢰성이 향상되어 있다. 또한, Cu로 이루어지는 도체 패턴(30)으로서의 패드(31)와, 반도체칩(50)의 전극(51a) 상에 설치되어 금(Au)으로 이루어져서 반도체 칩(50)과 외부를 전기적으로 접속하는 배선부로서 이용되는 접속부(52)의 계면에는 Cu와 Au가 상호 확산하여 이루어지는 금속 확산층인 CuAu합금층(522)이 형성되고(그림 2 참조), 이에 따라, 패드(31)와 접속부(52)의 접속 신뢰성이 향상되어 있다. 또한, 본 실시 형태에서는 절연 기재(20)의 일면(20a)측 표층을 이루는 열경화성 수지 필름(21a)의 내면에 도체 패턴(30)으로서 외부 접속용 전극(35)이 형성되어 있다.

반도체 칩(50)은 실리콘 등의 반도체 기판에 트랜지스터, 다이오드, 저항, 콘덴서 등의 소자가 집적되어 회로가 구성된 IC칩이다. 이 반도체 칩(50)의 표면에는 외부와의 접속용으로 전극(51)이 형성되어 있으며, 이 전극(51)으로서, 적어도 상기 배선부가 접속되는 전극을 포함한다. 또한, 반도체 칩(50)은 상기한 절연 기재(20)에 의하여 밀봉되어 있다.

본 실시 형태에서는 그림 1에 나타내는 바와 같이, 상기 회로와 전기적으로 접속된 AuAl합금층(521), 전극(51b)과, 상기 회로와는 접속되지 않고, 전기적인 접속 기능을 제공하지 않는 더미 전극(51c)이 형성되어 있다. 반도체 칩(50)의 일면측에는 반도체 칩(50)의 전극(51a)의 Al과 접속부(52)를 구성하는 Au의 고상 확산에 의하여 Au-Al합금으로 이루어지고, 알루미늄(Al)을 금속 단체(單體)로 포함하지 않는 AuAl합금층(521)이 복수 형성되어 있다.

접속부(52) 하의 접합면(계면)에 있어서, AuAl합금층(521) 중에 단체로 Al이 잔존하면, 고온의 사용 환경에 있어서, 전극(51a)의 Al에 접속부(52)의 Au가 고상 확산하여 Au5Al2를 생성한다. 이 Au5Al2의 성장 속도는 Au4Al에 비하여 훨씬 빠르고, 이 때문에, Au5Al2의 생성에 Au의 확산이 완료되지 않아서, 반도체 칩(50)과 접합부(52)의 사이에 커켄달 보이드를 발생시킨다. 또한, 커켄달 보이드를 기점으로 하여 크랙이 발생한다. 이에 대하여, 본 실시 형태에서는 AuAl합금층(521)이 Al을 금속 단체로 포함하지 않고, Au-Al합금의 최종 생성물인 Au4Al합금을 주로 포함하고 있다. 따라서 고온의 사용 환경에 있어서도 커켄달 보이드, 나아가서는 크랙이 발생하는 것을 억제할 수 있다. 따라서 본 발명의 제조 방법에 의하여 제조된 반도체 칩 내장 배선 기판(10)은 차량의 엔진 룸 등에 배치되어, 사용 환경이 고온으로 되는 전자 장치 등에 가장 적합하다. 또한, 전극(51a) 간의 피치는 반도체 칩(50)의 반대측의 면에 형성된 전극(51b, 51c)의 피치보다도 좁은 것으로 되어 있다. 구체적으로는, 수십㎛ 피치로 되어 있다.

본 실시 형태에서는 Cu로 이루어지고, 절연 기재(20)의 일면(20b)과 대략 일치하는 크기 및 형상을 갖는 평판상의 방열 부재(60)를 채용하고 있다. 그리고 이 방열 부재(60)에 열가소성 수지 필름(22d)이 밀착하는 것으로 방열 부재(60)가 절연 기재(20)의 일면(20b)에 고정되어 있다. 또한, 방열 부재(60)에는 열가소성 수지 필름(22d)에 형성된 층간 접속부(42)의 일단이 접속되어 있다. 본 실시 형태에서는 Cu로 이루어지는 방열 부재(60)와, Ag-Sn합금으로 이루어지는 층간 접속부(42)의 계면에 Cu와 Sn이 상호 확산하여 이루어지는 금속 확산층(Cu-Sn합금층)이 형성되고, 이에 따라, 층간 접속부(42)와 방열 부재(60)의 접속 신뢰성이 향상되어 있다.

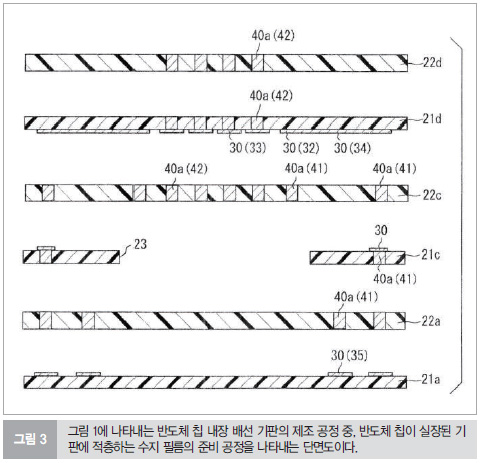

본 실시 형태에서는 그림 3에 나타내는 바와 같이, 6장의 수지필름(21a, 21c, 21d, 22a, 22c, 22d) 중, 열경화성 수지 필름(21a, 21c, 21d) 만, 편면에 동박이 부착된 필름을 준비하고, 동박을 패터닝하여 도체 패턴(30)을 각각 형성한다. 또한, 반도체 유닛(80)을 구성하는 나머지 2장의 수지 필름(21b, 22b)에 대해서도 열경화성 수지 필름(21b)만, 편면에 동박(동일하게 두께 18㎛)이 부착된 필름을 준비하고, 이 동박을 패터닝하여 도체 패턴(30)을 형성한다. 즉, 열경화성 수지 필름(21a~21d)은 편면에 도체 패턴(30)을 갖는 구성으로 하고, 열가소성 수지 필름(22a~22d)은 도체 패턴(30)을 갖지 않는 구성으로 한다. 또한, 6장의 수지 필름(21a, 21c, 21d, 22a, 22c, 22d) 중, 도체 패턴(30)으로서 외부 접속용 전극(35)을 편면에 갖고, 절연 기재(20)의 일면(20a)측의 표층을 구성하는 열경화성 수지 필름(21a)을 제외한 5장의 수지 필름(21c, 21d, 22a, 22c, 22d)에 비아 홀을 각각 형성하고, 해당 비아 홀 내에 도전성 페이스트(40a)를 충전한다. 그리고 충전 후, 건조 공정으로 용제를 휘발시킨다.

본 실시 형태에서는 열경화성 수지 필름(21a, 21c, 21d) 만에 도체 패턴(30)을 형성하기 때문에 도체 패턴(30)을 형성하지 않는 열가소성 수지 필름(22a, 22c, 22d)에 대해서는, 도전성 입자로서 Ag입자와 Sn입자를 소정의 비율로 포함하고, 또한, 상기한 바와 같이, 파라핀 등의 저융점 실온 고체 수지가 첨가된 도전성 페이스트(40a)를 이용한다.

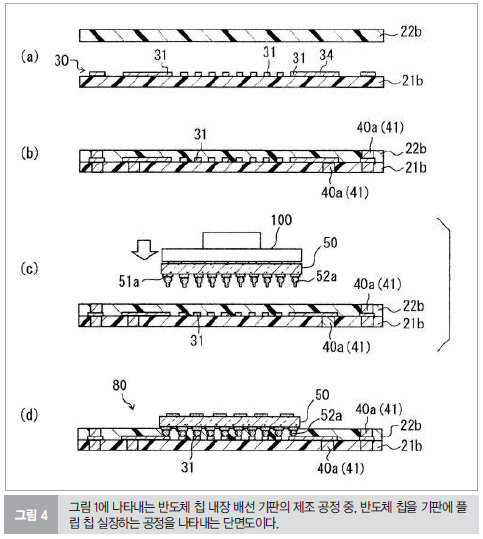

본 실시 형태에서는 그림 4의 (a)에 나타내는 바와 같이, 기판을 이루는 제 1 필름으로서의 열경화성 수지 필름(21b)과 제 2 필름으로서의 열가소성 수지 필름(22b)을 준비한다. 열경화성 수지 필름(21b)에 대해서는, 편면에 동박이 부착된 것을 준비하고, 이 동박을 패터닝하여 도체 패턴(30)을 형성한다. 이 때, 도체 패턴(30)으로서, 패드(31)도 형성된다. 이어서, 가열·가압하는 것으로 열가소성 수지 필름(22b)을, 패드(31)를 덮도록 기판의 패드 형성면에 부착한다.

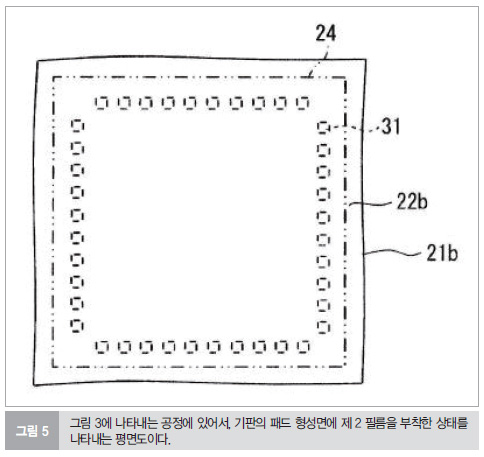

본 실시 형태에서는 그림 4의 (b) 및 그림 5에 나타내는 바와 같이, 열가소성 수지 필름(22b)을, 패드(31)를 덮도록 기판으로서의 열경화성 수지 필름(21b)의 패드 형성면에 열압착한다. 또한, 그림 5에 이점 쇄선으로 나타내는 영역은 반도체 칩(50)의 탑재 영역(24)을 나타내고 있다. 구체적으로는, 열가소성 수지 필름(22b)의 온도가, 해당 필름(22b)을 구성하는 열가소성 수지의 유리 전이점 이상, 융점 이하로 되도록 가열하면서 열경화성 수지 필름(21b)측에 가압하는 것으로 연화한 열가소성 수지를 열경화성 수지필름(21b)의 랜드 형성면 및 도체 패턴(30)의 표면에 밀착시킨다.

열가소성 수지 필름(22b)을 열경화성 수지 필름(21b)에 열압착한 후, 수지 필름(21b, 22b)에 도체 패턴(30)을 저면으로 하여 비아 홀을 형성하는 것과 함께, 비아 홀에 대하여 그림 4의 (b)에 나타내는 바와 같이, 도전성 페이스트(40a)를 충전한다. 여기에서는 어느 쪽도 도체 패턴(30)을 저면으로 하기 때문에 도전성 페이스트(40a)로서, 저융점 실온 고체 수지를 포함하지 않는 도전성 페이스트를 채용해도 좋고, 저융점 실온 고체 수지를 포함하는 도전성 페이스트를 채용해도 좋다.

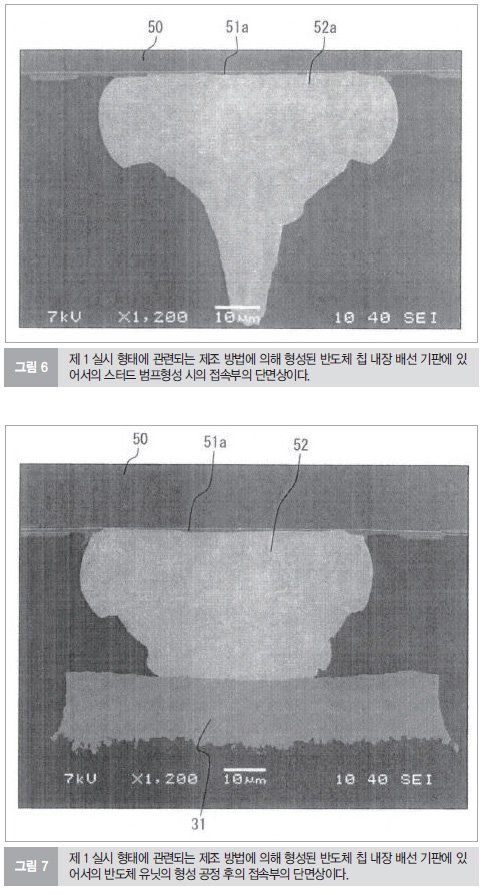

다음으로, 별도 준비한 반도체 칩(50)을 기판에 플립 칩 실장한다. 반도체 칩(50)에는 기판에 대한 탑재면의 전극(51a) 상에 스터드 범프(52a)가 형성되어 있다. 본 실시 형태에서는 Al계 재료로 이루어지는 전극(51a) 상에 예를 들면, 와이어를 사용한 주지의 방법으로 Au로 이루어지는 스터드 범프(52a)가 형성되어 있다. 또한, 그림 6에 나타내는 바와 같이 이 단계에서는 반도체 칩(50)과 스터드 범프(52a)의 사이에는 전극(51a)의 Al이 잔존해 있다. 그리고 그림 4의 (c)에 나타내는 바와 같이 예를 들면, 펄스 히트 방식의 열압착 툴(100)에 의해, 이 반도체 칩(50)을 기판 탑재면의 이면측으로부터 가열하면서 기판을 향하여 가압한다. 이 때, 열가소성 수지 필름(22b)을 구성하는 열가소성 수지의 융점(PEEK:PEI=30:70에서 330℃) 이상의 온도로 가열하면서 열경화성 수지 필름(21b) 측에 가압한다.

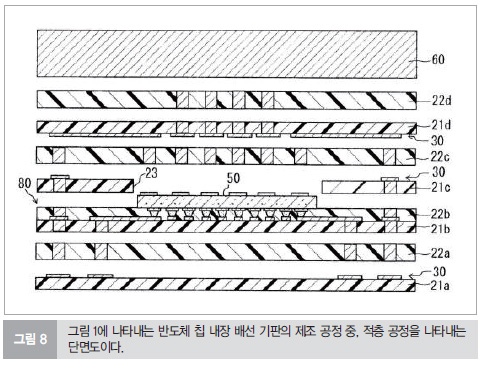

열압착 툴(100)로부터의 열이 반도체 칩(50)에 전해지고, 스터드 범프(52a)의 선단 온도가 열가소성 수지 필름(22b)을 구성하는 열가소성 수지의 융점 이상으로 되면, 스터드 범프(52a)가 접하는 열가소성 수지 필름(22b)의 부분이 용융한다. 따라서 열가소성 수지 필름(22b)을 용융시키면서 스터드 범프(52a)를 열가소성 수지필름(22b)에 밀어 넣어 대응하는 패드(31)에 접촉시킬 수 있다. 이에 따라, 그림 4의 (d)에 나타내는 바와 같이, 스터드 범프(52a)와 패드(31)를 압접 상태로 할 수 있다. 또한, 그림 7에 나타내는 바와 같이 반도체 칩(50)과 스터드 범프(52a)의 사이에는 전극(51a)의 Al이 잔존해 있다. 또한, 용융·연화한 열가소성 수지는 압력을 받아서 유동하고, 반도체 칩(50)의 기판 탑재면, 열경화성 수지필름(21b)의 패드 형성면, 도체 패턴(30), 전극(51a) 및 스터드 범프(52a)에 밀착한다. 따라서 그림 4의 (d)에 나타내는 바와 같이, 열가소성 수지 필름(22b)에 의하여 반도체 칩(50)과 열경화성 수지 필름(21b)(기판)의 사이를 밀봉할 수 있다. 이와 같이 하여 반도체 유닛(80)을 형성한다.

본 실시 형태에서는 플립 칩 실장 시의 가열 온도를 융점보다도 약간 높은 350℃ 정도로 하고, 하나의 스터드 범프(52a)에 걸리는 하중이 20~50gf 정도로 되는 압력을 인가한다. 이에 따라, 단시간에 스터드 범프(52a)와 패드(31)를 압접 상태로 할 수 있다. 또한, 압접 상태로 된 후에도 가열·가압을 계속하면, 스터드 범프(52a)를 구성하는 Au와 패드(31)를 구성하는 Cu가 상호 확산(고상 확산)하여 금속 확산층(Cu-Au합금층)을 형성한다. 또한, 스터드 범프(52a)를 구성하는 Au가 전극(51a)에 포함되는 Al에 대하여 고상 확산하고, 금속 확산층(Au-Al합금층)을 형성한다. 그러나 이와 같은 금속 확산층을 형성하는 데는, 상기한 압접 상태를 형성하는 데 비하여 가열·가압 시간으로서 장시간을 요한다. 또한, 그 동안 전극(51a), 스터드 범프(52a), 패드(31)의 전기적인 접속부 이외의 부분에도 불필요한 열이 인가되게 된다. 이 때문에, 이 실장 공정에서는 스터드 범프(52a)와 패드(31)의 접속 상태를 압접 상태로 머물게 한다.

다음으로, 적층체를 형성하는 적층 공정을 실시한다. 이 공정에서는 표면에 도체 패턴(30)이 형성된 수지 필름, 비아 홀 내에 도전성 페이스트(40a)가 충전된 수지 필름을 포함하는 여러 장의 수지 필름을 열가소성 수지 필름이 적어도 1장 간격으로 위치하면서 반도체 칩(50)의 전극 형성면 및 해당 전극 형성면의 이면에 인접하도록 적층한다.

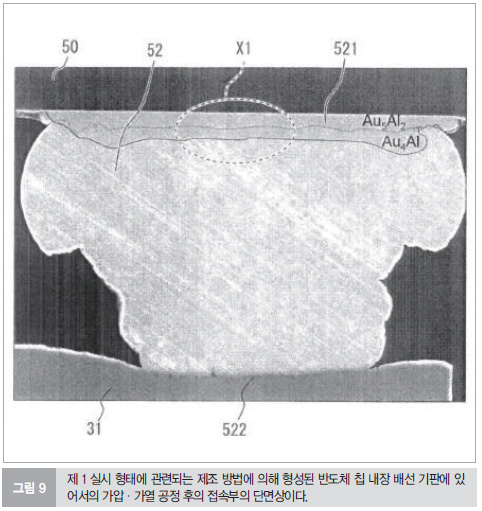

본 실시 형태에서는 그림 8에 나타내는 바와 같이, 적층 방향에 있어서의 일단측으로부터 열경화성 수지 필름(21a), 열가소성 수지 필름(22a), 열경화성 수지 필름(21b), 열가소성 수지 필름(22b), 열경화성 수지 필름(21c), 열가소성 수지 필름(22c), 열경화성 수지 필름(21d), 열가소성 수지 필름(22d)의 차례로 되도록 여러 장의 수지 필름(21a, 21c, 21d, 22a, 22c, 22d)과 반도체 유닛(80)을 적층한다. 그림 8에서는 편의상, 적층체를 구성하는 요소를 이간시켜서 도시하고 있다.

상세하게는, 열경화성 수지 필름(21a)의 도체 패턴 형성면 상에 열가소성 수지 필름(22a)을 적층하고, 열가소성 수지 필름(22a)상에 반도체 유닛(80)을, 열경화성 수지 필름(21b)을 탑재면으로 하여 적층한다. 반도체 유닛(80)에 있어서의 열가소성 수지 필름(22b) 상이며, 반도체 칩(50)의 주위에는 열경화성 수지 필름(21c)을, 도체 패턴 형성면과는 반대측의 면을 탑재면으로 하여 적층한다. 또한, 열경화성 수지 필름(21c) 및 반도체 칩(50) 상에 열가소성 수지 필름(22c)을 적층하고, 열가소성 수지 필름(22c) 상에 도체 패턴 형성면을 탑재면으로 하여 열경화성 수지 필름(21d)을 적층한다. 그리고 열경화성 수지 필름(21d) 상에 열가소성 수지 필름(22d)을 적층하고, 또한, 방열 부재(60)를 적층하여 하나의 적층체를 형성한다. 이 적층체에서는 적층 방향에 있어서, 반도체칩(50)에 인접하는 수지 필름이 열가소성 수지 필름(22b, 22c)으로 된다. 적어도 이들 수지 필름(22b, 22c)은 가압·가열 공정에 있어서, 반도체 칩(50)의 주위를 밀봉하는 기능을 완수한다. 본 실시 형태에서는 수직 방향에 있어서, 반도체 칩(50)을 둘러싸는 수지 필름이 열경화성 수지 필름(21c)이기 때문에 상기 2장의 수지필름(22b, 22c)이 반도체 칩(50)의 주위를 밀봉하는 기능을 완수한다. 이와 같이, 반도체 칩(50)을 밀봉하는 열가소성 수지 필름(22b, 22c)으로서는, 열가소성 수지 필름에 유리 섬유나 아라미드 섬유 등의 무기 재료를 포함하지 않을 뿐만 아니라, 선팽창 계수나 융점을 조정하기 위한 무기 필러(필러)도 포함하지 않는 것을 채용하는 것이 바람직하다. 이렇게 하는 것으로 가압·가열 공정에 있어서, 반도체 칩(50)에 국소적으로 응력이 걸리는 것을 억제할 수 있다. 그러나 선팽창 계수나 융점을 조정하기 위한 무기필러도 포함하지 않는 열가소성 수지 필름(22b, 22c)을 채용하면, 무기 필러가 없는 만큼 반도체 칩(50)과의 선팽창 계수차가 커지고, 이에 동반하는 응력이 증가하는 것이 생각된다. 따라서 응력저감을 위해, 열가소성 수지 필름(22b, 22c)으로서 탄성률이 낮은 수지 필름을 채용하면 좋다. 또한, 반도체 칩(50)을 밀봉하는 열가소성 수지 필름(22b, 22c)으로서는, 두께가 5㎛ 이상인 것을 채용하는 것이 바람직하다. 5㎛ 미만으로 하면, 가압·가열 공정에 있어서, 이들 수지 필름(22b, 22c)의 응력이 높아져서, 반도체 칩(50)의 표면으로부터 벗겨져 버릴 염려가 있기 때문이다. 이어서, 진공 열 프레스기를 이용하여 적층체를 적층 방향 상하로부터 가압하면서 가열하는 가압·가열 공정을 실시한다. 이 공정에서는 열가소성 수지를 연화시켜서 여러 장의 수지 필름을 일괄해서 일체화하는 것과 함께, 반도체 칩(50)을 밀봉하고, 도전성 페이스트(40a) 중의 도전성 입자를 소결체로 하여, 해당 소결체와 도체 패턴(30)을 가진 배선부를 형성한다.

가압·가열 공정에서는 수지 필름을 일괄해서 일체화하여 절연기재(20)로 하는 것과 함께, 도전성 페이스트(40a) 중의 도전성 입자를 소결체로 하기 위해, 수지 필름을 구성하는 열가소성 수지의 유리 전이점 이상 융점 이하의 온도, 수MPa의 압력을 소정 시간 유지한다. 본 실시 형태에서는 280℃~330℃의 프레스 온도, 4~5MPa의 압력을 5분 이상 유지한다.

우선, 가압·가열 공정에 있어서, 수지 필름 부분의 접속에 대하여 설명한다.

1장 간격으로 배치된 열가소성 수지 필름(22a~22d)은 상기 가열에 의해 연화한다. 이 때, 압력을 받고 있기 때문에 연화한 열가소성 수지 필름(22a~22d)은 인접하는 열경화성 수지 필름(21a~21d)에 밀착한다. 이에 따라, 복수의 수지 필름(21a~21d, 22a~22d)이 일괄해서 일체화하여 절연 기재(20)가 형성된다. 이때, 방열 부재(60)에도 인접하는 열가소성 수지 필름(22d)이 밀착하기 때문에 방열 부재(60)도 절연 기재(20)에 일체화한다. 또한, 반도체 칩(50)에 인접하는 열가소성 수지 필름(22b, 22c)은 압력을 받아서 유동하고, 반도체 칩(50)의 전극(51a) 형성면 및 그 이면인 전극(51b, 51c) 형성면에 밀착한다. 또한, 반도체 칩(50)의 측면과 열경화성 수지 필름(21c)의 간극에도 들어가서, 해당 간극을 메우는 것과 함께, 반도체 칩(50)의 측면에 밀착한다. 따라서 열가소성 수지에 의해 반도체 칩(50)이 밀봉된다. 다음으로, 가압·가열 공정에 있어서, 반도체 칩(50)의 전극(51), 도체 패턴(30), 층간 접속부(40)의 접속에 대하여 설명한다.

상기 가열에 의해 도전성 페이스트(40a) 중의 Sn(융점 232℃)이 용융하고, 마찬가지로 도전성 페이스트(40a) 중의 Ag입자로 확산하여 Ag-Sn합금(융점 480℃)을 형성한다. 또한, 도전성 페이스트(40a)에 압력이 가해져 있기 때문에 소결에 의해 일체화한 합금으로 이루어지는 층간 접속부(40(41, 42))가 비아 홀 내에 형성된다. 용융한 Sn은 도체 패턴(30)(패드(31~33))을 구성하는 Cu와도 상호 확산한다. 이에 따라, 층간 접속부(40)와 도체 패턴(30)의 계면에 금속 확산층(Cu-Sn합금층)이 형성된다. 용융한 Sn은 반도체 칩(50)의 전극(51b, 51c)을 구성하는 Ni와도 상호 확산한다. 이에 따라, 층간 접속부(40)와 전극(51b, 51c)의 계면에 금속확산층(Ni-Sn합금층)이 형성된다. 또한, 스터드 범프(52a)를 구성하는 Au가 반도체 칩(50)의 전극(51a)의 Al에 고상 확산한다.

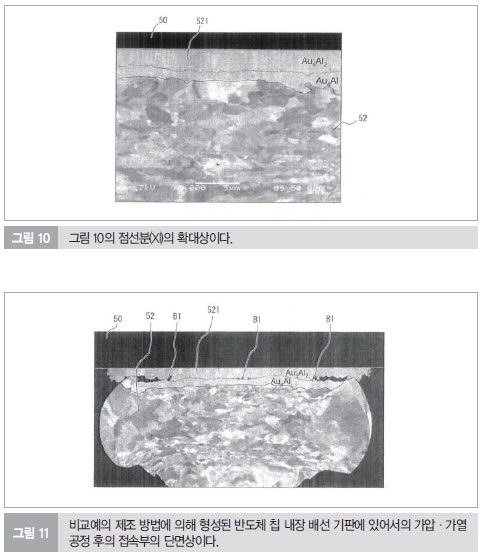

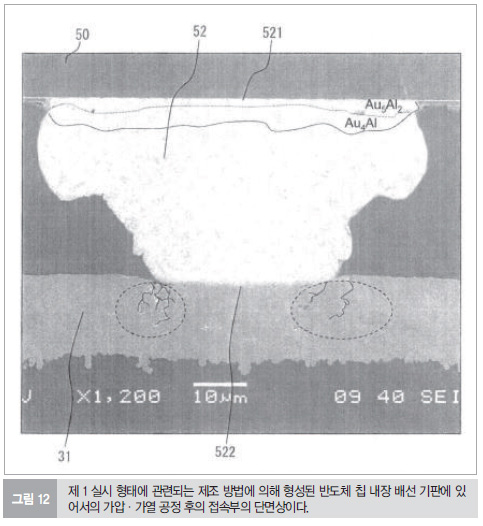

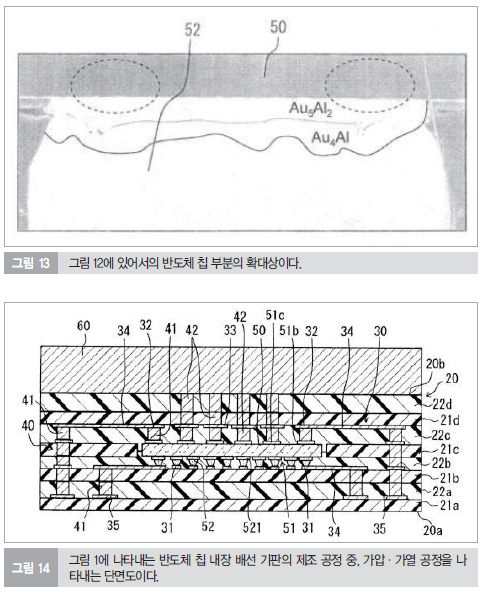

전극(51a)은 파인 피치 대응의 전극이기 때문에 전극(51a)의 Al의 양은 스터드 범프(52a)를 구성하는 Au의 양에 비하여 적고, 전극(51a)을 구성하는 모든 Al이 Au와의 합금화에 소비되어, 가압ㆍ가열 공정 후에는 상기한 바와 같이, Al을 금속 단체로 포함하지 않는 것으로 된다. 또한, 가압·가열 후의 전극(51a)은 Au-Al합금으로서, 주로 Au4Al합금을 포함하는 것으로 된다. 이 AuAl합금층(521)은 예를 들면, 그림 11에 나타내는 바와 같이, Au4Al과 Au5Al2로 이루어진다. 또한, 가압·가열 공정에 있어서, Au4Al합금이 생성되기 전에 성장 속도가 빠른 Au5Al2가 생성되었다고 해도 압력이 인가되어 있기 때문에 그림 9, 그림 10에 나타내는 바와 같이, 상기한 커켄달 보이드의 생성을 억제할 수 있다. 또한, 그림 9에 있어서는, 전극(51a)의 막두께를 1. 0㎛로 한 경우의 예이다. 이에 대하여, 비교예로서, 무가압(無加壓)으로 제조한 반도체 칩 내장 배선 기판에 있어서의 AuAl합금층(521) 부분의 단면상을 그림 11에 나타낸다. 그림 11에서도 명백한 바와 같이, 반도체 칩 내장 배선 기판을 무가압으로 제조한 경우, 보이드(B1)가 형성되게 된다. 또한, 스터드 범프(52a)를 구성하는 Au와 도체 패턴(30)을 구성하는 Cu가 상호 확산한다. 이에 따라, 그림 9에 나타내는 바와 같이, 스터드 범프 유래의 접속부(52)와 패드(31)의 계면에 CuAu합금층(522)(CuAu3합금)이 형성된다. Cu-Au합금은 250℃ 정도 이상의 가열이 있으면 생성할 수 있고, 상기한 가압·가열 조건에 따르면, CuAu3합금을 형성할 수 있다. 또한, 스터드 범프(52a)는 고상 확산 접합에 소비된 Au의 나머지에 의해 Au-Al합금으로 이루어지는 AuAl합금층(521)과, Cu로 이루어지고, 계면에 CuAu3합금을 갖는 패드(31)를 전기적으로 접속하는 접속부(52)로 된다. 이와 같이, 가압·가열 공정에 있어서, 스터드 범프(52a)와 패드(31)의 접속 상태를 직접적인 접합 상태로 한다.

또한, 패드(31)를 구성하는 Cu는 접속부(52)(스터드 범프(52a))의 Au보다도 저탄성률재를 채용하면 바람직하다. 이와 같이 함으로써 반도체 칩(50)과 절연 기재(20)의 열팽창률의 차에 기초하는 열응력을 Cu로 이루어지는 패드(31)에 집중시킬 수 있다. 이에 따라서, 그림 12에 나타내는 바와 같이, 패드(31)에 크랙을 발생시켜서 반도체 칩(50)에 인가되는 열응력을 완화할 수 있다. 따라서 그림 13에 나타내는 바와 같이, 반도체 칩(50)에 크랙이 발생하는 것을 억제할 수 있어서, 반도체 칩(50)이 파괴되는 것을 억제할 수 있다. 이상에 의해 그림 14에 나타내는 바와 같이, 절연 기재(20)에 반도체 칩(50)이 내장되고, 반도체 칩(50)이 열가소성 수지에 의하여 밀봉되며, 반도체 칩(50)과 외부 접속용 전극(35)이 배선부에 의하여 전기적으로 접속되고, 반도체 칩(50)과 방열 부재(60)가 방열 배선부에 의하여 열적으로 접속된 기판을 얻을 수 있다. 그리고 이 기판에 대하여, 절연 기재(20)의 일면(20a)측으로 부터 외부 접속용 전극(35)을 저면으로 하는 구멍을 형성하고, 구멍 내에 도금막 등의 도전 부재를 배치한 후, 도전 부재 상에 땜납볼(70)을 형성하는 것으로 그림 1에 나타내는 배선 기판(10)을 얻을 수 있다.

(제 2 실시 형태)

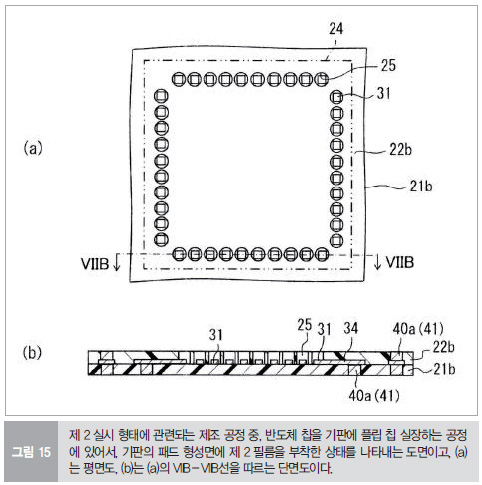

제 1 실시 형태에서는 반도체 칩(50)을, 기판으로서의 열경화성 수지 필름(21b)에 플립 칩 실장할 때에 스터드 범프(52a)를 열경화성 수지 필름(21b)의 패드 형성면 상에 부착한 열가소성 수지 필름(22b)에 밀어 넣어서 패드(31)와의 압접 상태를 확보하는 예를 나타냈다. 이에 대하여, 본 실시 형태에서는 그림 15의 (a), (b)에 나타내는 바와 같이, 열경화성 수지 필름(21b)의 패드 형성면에, 패드(31)에 대응하는 위치에 관통 구멍(25)이 설치된 열가소성 수지 필름(22b)을, 관통 구멍(25)이 패드(31)를 덮도록 부착해 두는 점을 특징으로 한다. 그림 15의 (a), (b)에 나타내는 예에서는, 각 패드(31)마다 관통 구멍(25)을 설치하고 있다. 이에 따르면, 스터드 범프(52a)와 패드(31)의 각 접속부의 사이에 열가소성 수지 필름(22b)이 위치하기 때문에 플립 칩 실장 공정에 있어서, 연화한 열가소성 수지가 접속부를 덮기 쉽다. 즉, 관통 구멍(25)을 설치하면서도 각 접속부 간에서의 전기적인 절연성을 확보하기 쉬워서 접속부에 있어서의 접속 신뢰성을 향상시키기 쉽다. 또한, 반도체 칩(50)의 전극(51a)이 파인 피치인 경우, 패드(31)도 파인 피치로 된다. 따라서 패드(31)보다도 작은 관통 구멍(25)을 형성하는 것은 곤란하다. 그러나 층간 접속부(40)를 형성하기 위한 비아 홀과는 달리, 관통 구멍(25)에는 도전성 페이스트(40a)가 충전되지 않고, 또한, 반도체 칩(50)의 전극(51a)과 패드(31)를 전기적으로 접속하는 접속부(52)의 체격을 규정하는 것도 아니다. 따라서 관통 구멍(25)에 대해서는, 패드(31)보다 크게 해도 좋기 때문에 비아 홀보다도 관통 구멍 형성의 자유도가 높아서, 패드(31)마다 설치할 수 있다. 그리고 열가소성 수지 필름(22b)을 구성하는 열가소성 수지의 유리 전이점 이상의 온도로 가열하면서 가압하여 반도체 칩(50)을 열경화성 수지 필름(21b)에 플립 칩 실장한다. 이에 따라, 반도체 칩(50)의 스터드 범프(52a)를, 관통 구멍(25)을 통하여 대응하는 패드(31)에 압접시키는 것과 함께, 연화한 열가소성 수지로 반도체 칩(50)과 열경화성 수지 필름(21b)의 사이를 밀봉한다. 이와 같은 방법을 이용해도 제 1 실시 형태에 나타낸 제조방법과 동일한 효과를 이룰 수 있다. 또한, 본 실시 형태에 나타내는 제조 방법에 따르면, 스터드 범프(52a)와 패드(31)의 압접 상태를 형성하는 데 있어서, 열가소성 수지 필름(22b)을 용융시키지 않아도 좋다. 열가소성 수지 필름(22b)을 구성하는 열가소성 수지의 유리 전이점 이상의 온도로 가열하면서 가압하는 것으로 연화한 열가소성 수지로 반도체 칩(50)과 열경화성 수지 필름(21b)의 사이를 밀봉할 수 있으면 좋다. 바꾸어 말하면, 반도체 칩(50)을 열가소성 수지 필름(22b)에 열압착할 수 있으면 좋다. 열가소성 수지 필름(22b)에는 플립 칩 실장 전에 미리 관통 구멍(25)을 설치하기 때문에 제 1 실시 형태에 나타내는 방법에 비하여 압접 상태를 용이하게 형성할 수 있다. 따라서 열량이 같으면 제 1 실시 형태에 나타내는 방법보다도 단시간에 스터드 범프(52a)와 패드(31)의 압접 상태 및 열가소성 수지 필름(22b)에 의한 밀봉 구조를 형성할 수 있다. 즉, 플립 칩 실장 공정에서의 가열ㆍ가압 시간, 나아가서는 배선 기판(10)의 제조 시간을 보다 단축할 수 있다. 또한, 가열ㆍ가압 시간 및 가압 조건이 같으면 제 1 실시 형태에 나타내는 방법보다도 적은 열량으로 스터드 범프(52a)와 패드(31)의 압접 상태를 확보할 수 있다. 또한, 관통 구멍(25)은 열가소성 수지 필름(22b)을 열경화성 수지 필름(21b)에 부착하기 전에 형성해도 좋고, 부착한 후에 형성해도 좋다. 본 실시 형태에서는 부착한 후, 열가소성 수지 필름(22b)에 있어서의 패드(31)에 대응하는 위치에 탄산가스 레이저 등에 의해 관통 구멍(25)을 형성한다. 이와 같은 방법을 채용하면, 위치 정밀도 좋게 관통 구멍(25)을 형성할 수 있다.