차세대 컴퓨팅 기술의 개발은 인공 지능 컴퓨터의 개발을 위해 필수적인 요소이며, 멤리스터는 차세대 컴퓨팅 기술의 핵심 기술이다. 현재는 해외의 학계를 중심으로 연구가 활발하게 이루어지고 있으며, 기술 개발 추세를 통해 유추해보면 10년 이내에 본 기술이 상용화 될 것으로 기대된다. 차세대 컴퓨팅 기술은 반도체 기술을 기반으로 개발될 것이며, 따라서 반도체 강국인 대한민국의 미래 기술 분야가 될 가능성이 높다. 하지만 이는 차세대 컴퓨팅 기술에 대한 지속적인 투자를 통해서만 가능하다. 따라서 미국이나 중국과 같이 본 기술에 대한 중요성을 인지하고 국가를 중심으로 전략적으로 기술 개발을 이끌어나갈 필요가 있다.

멤리스터(Memristor)는 차세대 전자 소자로 다양한 전자 소자로 활용될 수 있다. 특히 멤리스터를 컴퓨팅 기술에 이용하면 기존의 컴퓨팅 방식과는 완전히 다른 새로운 방식의 컴퓨팅이 가능하여 인간의 두뇌와 같은 방식으로 동작하는 컴퓨터를 만드는 것이 가능하다. 본고에서는 멤리스터의 컴퓨팅 응용 기술을 조사하여, 미래 국가산업으로 멤리스터 차세대 컴퓨팅 기술의 가능성을 알리고자 한다.

차세대 컴퓨팅 기술의 개발은 인공 지능 컴퓨터의 개발을 위해 필수적인 요소이며, 멤리스터는 차세대 컴퓨팅 기술의 핵심 기술이다. 현재는 해외의 학계를 중심으로 연구가 활발하게 이루어지고 있으며, 기술 개발 추세를 통해 유추해보면 10년 이내에 본 기술이 상용화 될 것으로 기대된다. 차세대 컴퓨팅 기술은 반도체 기술을 기반으로 개발될 것이며, 따라서 반도체 강국인 대한민국의 미래 기술 분야가 될 가능성이 높다. 하지만 이는 차세대 컴퓨팅 기술에 대한 지속적인 투자를 통해서만 가능하다. 따라서 미국이나 중국과 같이 본 기술에 대한 중요성을 인지하고 국가를 중심으로 전략적으로 기술 개발을 이끌어나갈 필요가 있다.

본고는 멤리스터 기술에 대한 소개부터 멤리스터가 어떻게 차세대 컴퓨팅에 이용될 수 있는지에 대해 구체적으로 조사하였다. 이를 위해 멤리스터 컴퓨팅 기술과 관련된 해외 발행 논문들 폭넓게 조사하고 이를 정리하였다. 또한 멤리스터 컴퓨팅 기술의 기초적인 배경 지식을 포함하고 있으며, 최신 기술 동향을 담고 있다.

서론

2016년 3월, Google DeepMind社는 자체 개발한 인공지능 컴퓨터에게 바둑을 학습시켜 한국의 이세돌 9단과 대국을 진행하여 화제가 되었다. Google Deepmind Challenge match라고 명명된 이 대국에서 더욱 놀라운 것은 그 결과로, Google의 AI(Artificial Interlligent) 컴퓨터인 알파고(AlphaGo)는 이세돌 9단을 4:1로 격파하였다. 컴퓨터와 인간의 대결에서 컴퓨터가 승리한 역사는 상당히 오래되었다. 하지만 바둑 대국에서 컴퓨터가 최고의 고수를 이겼다는 것은 단순한 승리 이상의 큰 의미를 갖고 있다. 이 대국에서 주목해야할 점은 알파고는 바둑을 둘 수 있도록 프로그램 된 것이 아니라, 바둑을 학습하였다는 것이다. 비슷한 예로, 1996년 체스 경기에서는 이미 IBM의 슈퍼컴퓨터인 딥 블루(Deep Blue)가 당시 체스 세계 챔피언이었던 가리 카스파로프(Garry Kasparov)를 이긴 바 있다. 이 당시 딥 블루가 수를 계산한 방식은 프로그램 된 알고리즘을 통해 모든 경우의 수를 따져 승리할 수 있는 수를 두도록 되어 있었다. 따라서 이 당시의 문제는 승리하기 위한 최적화 된 알고리즘을 짜는 것이었고, 이를 슈퍼 컴퓨터를 통해 빠르게 연산을 수행하여 답을 찾는 것이었다. 이는 체스라는 게임에서 말을 옮기는 경우의 수가 10의 40제곱 정도로 매우 적기 때문에 가능한 것이었다. 딥 블루는 매 순간 10의 40제곱의 경우의 수를 몇 수 앞까지 계산하였다(실제로 프로그램 알고리즘은 이 가운데 유효한 경우들만 계산하도록 짜여 있다).

바둑의 경우 산술적인 착수의 경우의 수가 약 10의 170제곱 정도에 이른다. 즉, 체스와 똑같은 방법을 쓴다면 10의 130 제곱 개의 딥 블루가 있으면 같은 방식으로 연산이 가능한 것이다. 즉, 딥 블루가 하늘의 별만큼 많으면 가능하다.

1996년에 비해 지난 20년간 컴퓨터의 성능이 급격히 발달했다고 하더라도 기존의 방식(즉, 프로그램 알고리즘과 컴퓨팅 능력)만으로는 이른바 완전한 바둑을 두는 것이 불가능하다. 이에 구글이 선보인 학습을 통한 컴퓨팅은 기존의 방식과 차별화 된 완전히 새로운 방식이며, 이는 인간의 두뇌가 지식을 학습하고 응용하는 것과 매우 유사하다. 실제로 이러한 학습을 통한 컴퓨팅은 오래전부터 연구가 되어 왔고, 구글은 이를 세계 최초로 바둑이라는 매개체를 통해서 대중 앞에서 시연한 의미가 있다. 이처럼 인간의 두뇌와 같은 방식으로 연산하는 것을 뉴로모픽 컴퓨팅(Neuromorphic computing) 이라 한다.

그렇다면 인간은 이제 인공지능에게 정복당한 것일까? 알파고가 갖고 있는 한계는 무엇이며 궁극의 인공지능을 위해서는 어떤 혁신이 필요한 것일까? 본고에서는 이러한 질문들에 대한 답변을 제시하고자 한다.

목적 및 필요성

알파고의 실력은 이른바 소프트웨어의 혁명이다. 구글은 혁신적인 소프트웨어 알고리즘을 통해 슈퍼컴퓨터인 알파고가 기존의 기보들을 통해 바둑을 학습하도록 하였고, 그 학습된 것을 바탕으로 바둑을 두도록 하였다. 알파고는 이 임무를 수행하기 위해 1,202개의 중앙처리장치(CPU)와 176개의 그래픽처리장치(GPU)를 사용한 것으로 알려져 있다. 여기에서 구글이 보여준 알파고 인공지능의 한계를 찾을 수 있다. 이들 프로세서들을 동작시키는 전력을 단순 계산하면 170kW 정도가 필요한데, 이는 20W 정도로 알려진 인간의 두뇌와 비교하면 약 8,500배 정도 많은 에너지를 소모하는 것이다. 인간에 비해 에너지 소모가 너무 많다.

인간의 연산에 비해 컴퓨터의 연산이 에너지 소모가 많은 이유는 두 가지이다. 첫째, 연산이 비효율적이라는 것과, 둘째, 단위 연산당 소모 에너지가 높다는 것이다. 연산의 비효율성은 인간과 컴퓨터의 근본적인 동작 방식의 차이에서 비롯된다. 인간의 두뇌에서는 뉴런과 시냅스가 복잡하게 연결되어 있고, 이들 간에 이온에 의한 정보 전달에 의해 기억과 연산이 이루어진다. 이 과정은 매우 복잡하여 여전히 완전히 이해되고 있지 않지만, 궁극적인 사실은 기억과 연산이 동시에 이루어진다는 점이다.

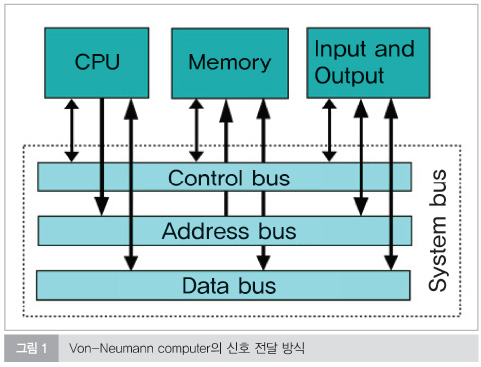

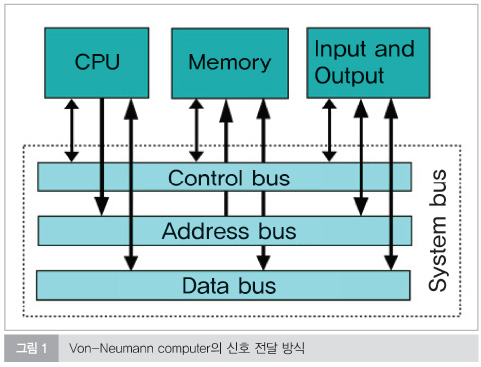

한편, 컴퓨터는 연산장치, 제어장치, 기억장치가 따로 분리되어 있고 이들 간에 전자에 의한 신호 전달을 통해 연산이 이루어진다. 이를 폰-노이만(Von Neumann)방식이라 한다. 폰-노이만 방식은 약 100년 전 초기 컴퓨터에서부터 적용된 방식이며, 현재까지의 컴퓨터의 발전은 폰-노이만 방식의 틀 안에서 컴퓨터를 더욱 빠르고 더욱 작게 만드는 방향으로 발전되어 왔다. 이 폰-노이만 방식의 특징은 연산부, 제어부, 기억부가 독립적으로 형성되어 연결된다는 점이다. 따라서 각각의 독립된 부분 간에 신호를 전달하는 과정에서 많은 에너지가 소모되며, 이것이 인간 두뇌에서와의 가장 큰 차이를 가져온다.

다음으로 컴퓨터의 경우 단위 연산당 사용 에너지가 높은데, 이는 다양한 원인에 기인한다. 우선, 컴퓨터에서의 연산 방식이 디지털 방식이며, 1과 0으로 구성된 바이너리 데이터가 불린 로직(Boolean logic)을 통해서 연산이 되는 과정을 거친다. 이를테면, 2와 3을 더하는 경우를 가정하면, 2와 3이 각각 2진수인 010과 011로 인식되고, 여기서 각각의 단위를 더한다. 이 때 첫 번째 단위는 0과 1의 합이므로 1이 되고, 두 번째 단위는 1과 1의 합이므로 0을 출력하고 1을 세 번째 단위로 넘긴다. 세 번째 단위에서는 0과 0의 합에 두 번째 단위에서 입력된 1이 합쳐져 1을 출력한다. 그 결과 100의 값이 얻어지며, 이는 다시 10진수인 5로 변환되어 출력된다.

컴퓨터에서는 이 연산을 위해 이러한 여러 단계를 거치며, 이 과정은 오류가 없이 매우 정확하게 이루어진다. 하지만 연산이 복잡해질수록 연산의 단계는 기하급수적으로 증가하고, 이는 에너지 소모의 증가로 이어진다. 하지만 인간이 이를 계산하는 경우, 직관적으로 5라는 답이 얻어진다. 이는 학습에 의해 얻어진 효과이다.

인간도 학습을 잘 못 받거나 학습 받지 못한 경우에는 정확한 답을 할 수 없다. 2와 3을 더하는 것은 매우 간단한 문제였고, 만약 어떠한 문제가 매우 복잡해서 답을 찾기가 컴퓨터도 인간도 답을 찾을 수 없는 문제가 있다면 어떻게 될까? 이를 일반화해서 정답이 있는 문제와 없는 문제로 비교할 수 있다.

2+3과 같이 정답이 있는 경우에는 컴퓨터의 연산은 빠르고 정확하다. 하지만 정답이 없는 경우라면, 인간의 학습과 연산을 통한 직관이 효율적이다. 체스의 경우, 경우의 수가 제한적이고 따라서 우수한 컴퓨터 성능을 바탕으로 최선의 수에 대한 정답을 찾을 수 있는 경우였다. 하지만 바둑은 경우의 수가 무한에 가깝기 때문에 정답은 없지만 주어진 시간 내에 최선의 선택을 해야 하는 경우이며, 이는 컴퓨터보다 항상 인간이 앞서는 영역이었다. 하지만 알파고를 통해 이제 컴퓨터가 이러한 인간이 장점을 갖는 영역을 침범하고 있음을 보여준다. 이처럼 인간과 같이 학습을 통해 습득하고 연상을 통해 답을 즉시 생각해낼 수 있는 직관 능력이 컴퓨터가 궁극적으로 나아가고자 하는 방향이다. 이를 이루기 위해서는 결국 더욱 인간의 두뇌와 같은 방식으로 계산할 수 있는 장치가 만들어져야 한다.

조사내용

소프트웨어와 컴퓨팅 알고리즘 개선을 통한 인공 지능의 혁신은 구글이 그 비전을 보여주었으며, 향후 구글의 기술을 따라잡기 위한 전 세계적인 노력이 계속될 것임이 분명하다. 이러한 소프트웨어의 혁신과 더불어 필요한 것이 하드웨어의 혁신이다. 이 차세대 컴퓨팅 기술은 기존의 폰-노이만 컴퓨팅 방식에서 벗어나 완전히 새로운 방식의 컴퓨팅을 추구한다.

현재 이 기술을 실현시키기 위한 연구가 미국과 중국을 중심으로 진행 중이다. 미국에서는 2015년 10월 ‘Nanotechnology-Inspired Grand Challenge for Future Computing’이라는 제목으로 차세대 컴퓨팅 기술을 백악관 과제로 선정하여 미래 기술에 집중적으로 투자하기로 결정하였다. 또한 중국에서도 정부를 중심으로 차세대 컴퓨팅 기술에 대한 연구가 활발히 진행 중이다. 차세대 컴퓨팅 소자도 결국 반도체 기술을 기반으로 하게 되는데, 현재 메모리 반도체 기술에서 완전히 도태되어 돌파구를 찾지 못하고 있는 중국은 차세대 컴퓨팅 소자 개발을 통해 반도체 기술에서의 돌파구를 찾고자 하고 있다.

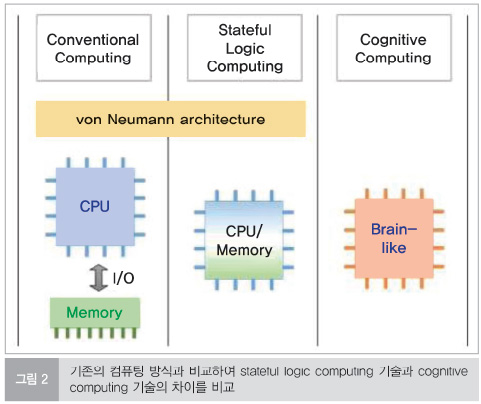

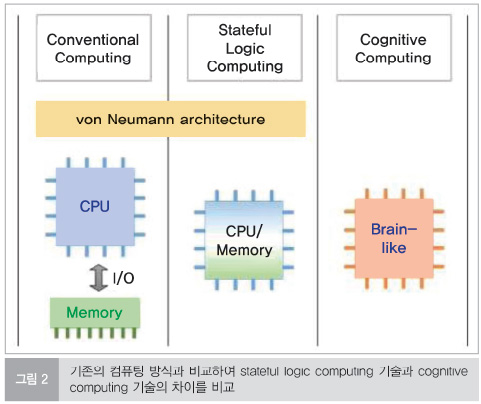

차세대 컴퓨팅 기술과 관련하여 그 핵심은 인간의 두뇌를 모사하는 것이다. 그리고 그 방법은 크게 두 가지로 나눌 수 있다. 그 첫째는 현재의 컴퓨터의 기반을 유지하고 인간 두뇌의 장점을 차용하는 것으로, 현재 독립적으로 동작하는 CPU와 메모리를 하나의 소자에 합치는 방법이 있다. 이를 stateful logic 이라 부른다. 이러한 방식은 기존의 컴퓨팅 방식의 틀은 유지하며, 두뇌의 특성을 모방하는 방식으로, 기존의 방식을 개선한다는 점에서 실현 가능성이 높은 방식이며, 이를 ‘cognitive computing’ 이라고 부른다.

두 번째 방식은 두뇌에서 수행되는 사고방식을 완전히 모방하는 방식인데, 이는 기존의 컴퓨팅 패러다임을 완전히 바꾸는 완전히 새로운 패러다임의 컴퓨팅 방식이다. 그만큼 아직 기술적 완성도는 낮지만 궁극적으로 두뇌를 모방하기 위해서는 이러한 방식을 채택할 수 있을 것이다. 그림 2는 기존의 컴퓨팅 방식과 비교하여 stateful logic computing 기술과 cognitive computing 기술의 차이를 비교하여 보여준다. 기술의 난이도와 성숙도를 봤을 때 1차적으로는 첫 번째 방식의 컴퓨팅이 10년 이내에 선행 연구되어 개발될 것으로 기대할 수 있고, 두 번째 방식은 10년 이후의 궁극적인 기술 방식으로 간주되고 있다.

흥미롭게도 이러한 두 가지의 새로운 차세대 컴퓨팅은 모두 멤리스터(memristor)라 불리는 수동 소자 기술을 기반으로 한다. 멤리스터는 2005년 HP에서 개발한 새로운 전자 소자로 전기 신호의 값에 따라 저항이 변하는 소자이다. 이 저항 변화는 비휘발성이라 기록된 저항값이 또 다른 전기 신호가 입력되지 않는 한 변하지 않고 유지되며, 가역적이라 전기 신호를 통해 언제든 원하는 저항 값을 다시 만들 수 있다. 이러한 특성에 의해 멤리스터는 메모리와 스위치의 특성을 동시에 갖고 있는데, 이는 각각 메모리 소자와 로직 소자에 사용될 수 있는 특징이며, 하나의 소자에서 두 가지 특성을 모두 갖기 때문에 멤리스터를 이용하면 메모리와 로직이 통합된 소자를 만들 수 있다. 이를 stateful logic이라 한다.

더 나아가 멤리스터에서 나타나는 전기 신호에 따른 저항 변화, 즉 전기전도도의 변화는, 인간의 뉴런과 시냅스에서 나타나는 생체 신호의 전달 과정을 모사할 수 있다. 따라서 궁극적으로는 멤리스터를 이용하여 인간의 두뇌를 전기 소자로 구현할 수 있다. 본 고에서는 차세대 컴퓨팅 기술 중 멤리스터를 이용한 stateful logic 기술에 대해 조사하고자 한다. 이를 위해 멤리스터 소자가 무엇인지 살펴보고, 멤리스터를 이용한 stateful logic이 나오게 된 배경과 stateful logic의 구체적인 동작 방식 등에 대해 살펴보고자 한다.

멤리스터(Memristor) 기술

멤리스터 기술의 배경 및 의의

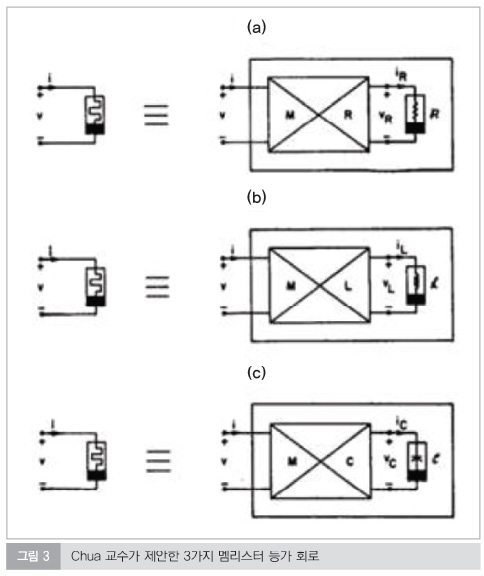

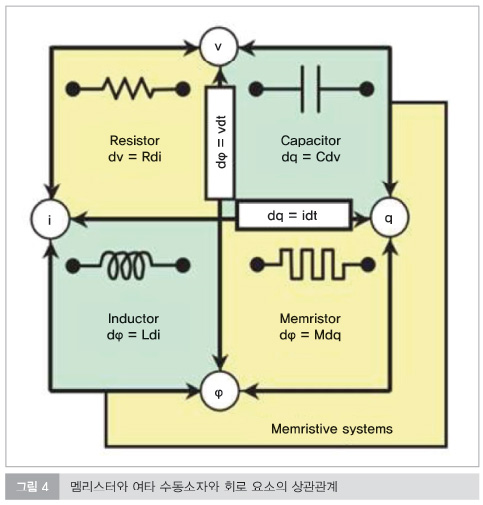

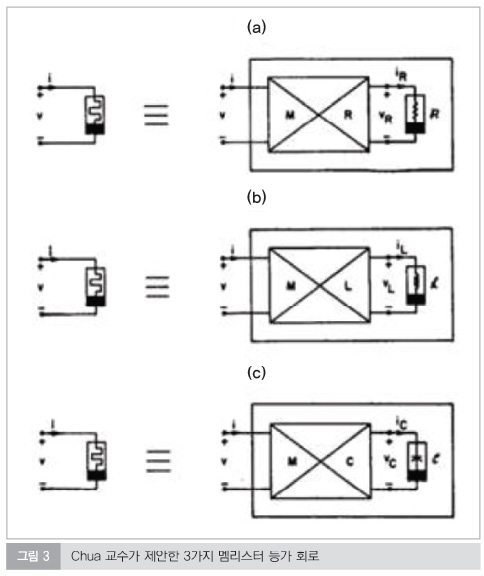

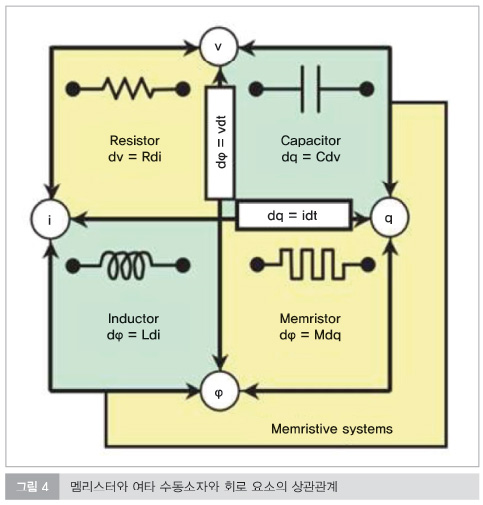

멤리스터는 1971년 UC Berkeley의 Leon Chua 교수가 제4의 수동 소자로 최초로 제안하였다. 당시 회로 구성 요소로 전압 (v), 전류 (i), 자속 (φ), 전하량 (q) 등이 잘 알려져 있었고, 이들 간의 관계를 나타내주는 수동 소자로 저항, 커패시터, 인덕터가 알려져 있었다. Chua 교수는 이들 관계로 부터 자속과 전하량의 관계를 나타내는 소자가 있을 것임을 예측하고, 이를 멤리스터라 명명하였다. 멤리스터는 전자기 flux와 전하량 charge의 관계를 나타내는 소자이며, 이를 각각 전압의 변화와 전류의 변화로 이해하면, 전압의 변화량에 따라 전류의 량이 변하는, 즉 저항이 변하는 소자를 의미한다. Chua 교수는 이 멤리스터 소자의 개념을 이론적으로만 제시하였을 뿐, 실제로 멤리스터 소자가 존재하는 것은 아니었다. 그림 3은 Chua 교수가 제시한 멤리스터 등가 회로도를 보여준다.

한편, 2000년 대 초반에 들어, 전하 저장형 메모리인 DRAM과 flash 메모리를 뒤이을 차세대 메모리에 관한 연구에 관심이 쏟아지기 시작하였다. 1970년 DRAM과 flash 메모리가 개발 된 이후, 이들 전하 저장형 메모리 기술은 지난 수 십 년간 비약적으로 발전하였고, 메모리 시장에서 독보적인 위치를 차지하였다. 그럼에도 불구하고, 이들 메모리의 미세 공정 기술이 10 nm대로 진입하면서 물리적인 집적화의 한계가 다가오기 시작하였고, 이에 대응하여 새로운 방식의 메모리 기술 대안에 대한 요구가 생겨났다.

그 중 하나는 산화물 박막에서 나타나는 비휘발성 저항변화 현상을 활용하는 저항변화 메모리 (Resistive RAM, RRAM)이다. RRAM에 사용된 저항 변화 현상은 1970년대부터 산화물을 포함한 다양한 물질에서 보고된 산화물에서 매우 일반적으로 관찰할 수 있는 현상이며, 이를 메모리로 사용할 수 있을 가능성이 오래전에 제시되었다. 하지만 전하 저장형 메모리 기술이 메모리 시장에서 널리 활용되면서 저항 변화형 메모리에 대한 연구는 한동안 잊혀 있었다. 하지만 2000년, IBM에서 기존의 전하 저장형 메모리 방식에 대한 대안으로 RRAM을 다시 제안하였다. 이후, RRAM 기술이 다시 각광받기 시작하였고, 차세대 비휘발성 메모리 응용을 위해 지난 10여 년간 그 기술이 비약적으로 발전하여 이제 RRAM의 제품이 양산을 눈앞에 두고 있다.

한편, HP는 저항변화 물질 중의 하나인 전이금속 산화물 TiO2 에서 나타나는 저항변화 현상을 해석하던 중, 이 저항변화 현상이 Chua 교수가 제시한 멤리스터 이론을 통해 해석이 가능함을 밝히고, 이 당시까지 폭넓게 연구되던 저항변화 현상이 곧 멤리스터 임을 이론적으로 입증하여 2008년 발표하였다. 그림 4는 HP에서 입증한 멤리스터와 여타 수동 소자와의 상관관계를 보여준다.

단순히 저항변화 메모리의 재료로만 간주되던 저항변화 현상이 HP의 발표로 멤리스터 임으로 알려지면서 제4의 수동 소자인 멤리스터는 메모리 분야에서 뿐만 아니라 회로 및 컴퓨팅 분야에서도 그 활용도를 찾기 위해 폭넓게 연구가 되었다. 그 결과 멤리스터를 이용한 stateful logic 컴퓨팅 소자, 인간의 생체 신호 발생 장치인 뉴리스터(neuron+memrisotr), 인공 신경 등의 분야 등의 새로운 응용 연구 분야들이 개발되었다.

멤리스터는 그 자체만으로도 매우 폭넓게 연구되고 있다. 멤리스터의 재료 기술, 신뢰성 향상 기술, 기초 연구 등, 멤리스터를 응용하기 위해 필요한 기반 연구는 이미 학계에서 폭넓게 이루어지고 있는 매우 중요한 분야이며, 이제 그 응용 연구가 활발히 이루어지고 있다. 특히 멤리스터를 차세대 컴퓨팅에 적용하기 위한 연구는 인공 지능 기술과 고효율 컴퓨팅 기술에 대한 요구에 부합하여 미국과 중국에서 국가의 주력 연구 분야로 선정하여 연구 중인 분야이다.

멤리스터 기술 연구 동향

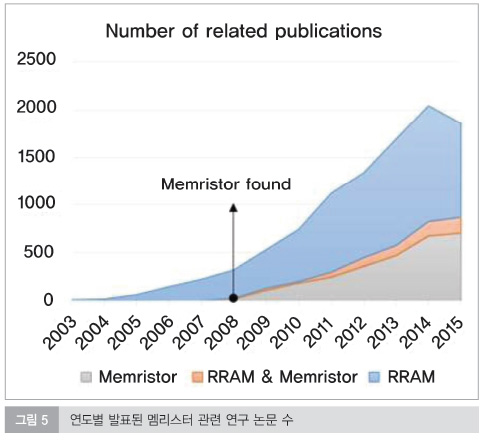

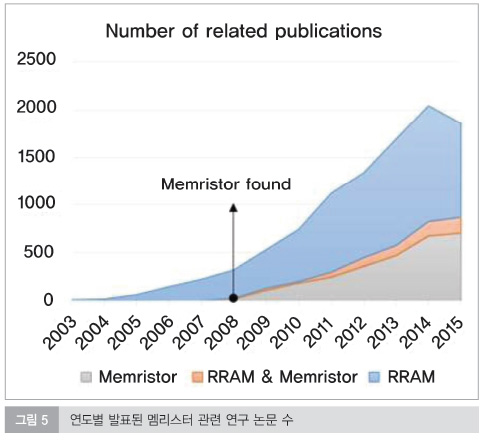

그림 5는 키워드로 검색한 연도별 논문 수를 보여준다. 여기서 키워드로는 Memristor, RRAM 그리고 Memristor & RRAM이 사용되었다. 멤리스터가 발견되기 이전인 2008년 이전에는 RRAM에 대한 연구가 활발히 이루어졌음을 확인할 수 있다. 그리고 2008년 이후 멤리스터 관련 연구의 비중이 꾸준히 증가하고 있다. 멤리스터 연구는 2008년에 시작이 되어 아직 10년이 채 되지 않은 연구 분야로 제품 개발 단계까지 고려하면 현재 매우 기초적인 연구 단계이며, 향후 10년 이상 해당분야에 대한 연구가 활발하게 지속될 것으로 기대된다.

멤리스터의 FPGA 응용 기술

FPGA 배경 기술

FPGA(field-programmable gate array)는 컴퓨팅 소자의 일종으로 소비자가 직접 집적된 소자의 구조를 구성하여 원하는 용도에 맞춰 사용할 수 있도록 만들어진다. 따라서 FPGA는 CPU(central processing unit)나 GPU(graphic processing unit)와 같이 제조자가 자기만의 방식으로 제작한 컴퓨팅 소자와 차별화 된 이용자 중심의 연산 소자이다. FPGA는 CPU 나 GPU에 비해 동작 속도가 느리고, 집적도가 낮은 단점이 있으나, 사용자가 자신이 원하는 목적에 따라 원하는 대로 구성할 수 있고, 값이 저렴하다는 측면에서 폭넓게 사용되고 있다. 본 단원에서는 멤리스터가 FPGA에 어떻게 적용이 될 수 있는지 그 기술적 배경을 살펴보고자 한다.

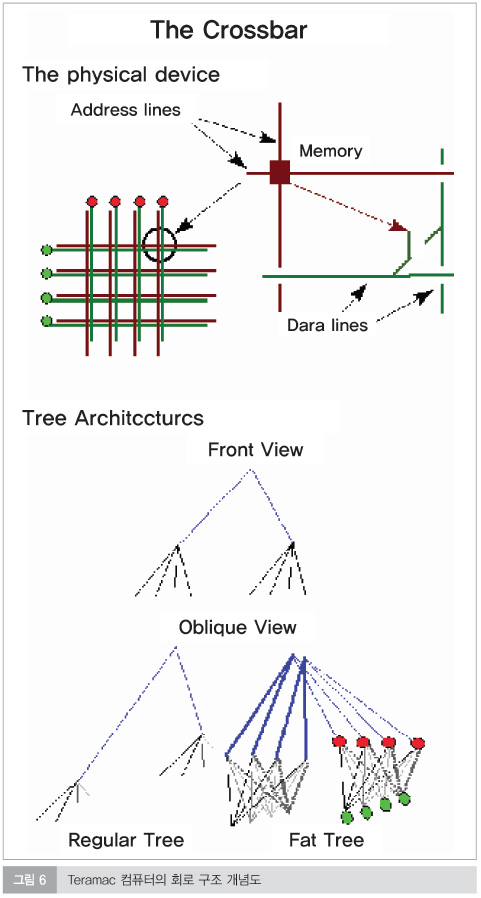

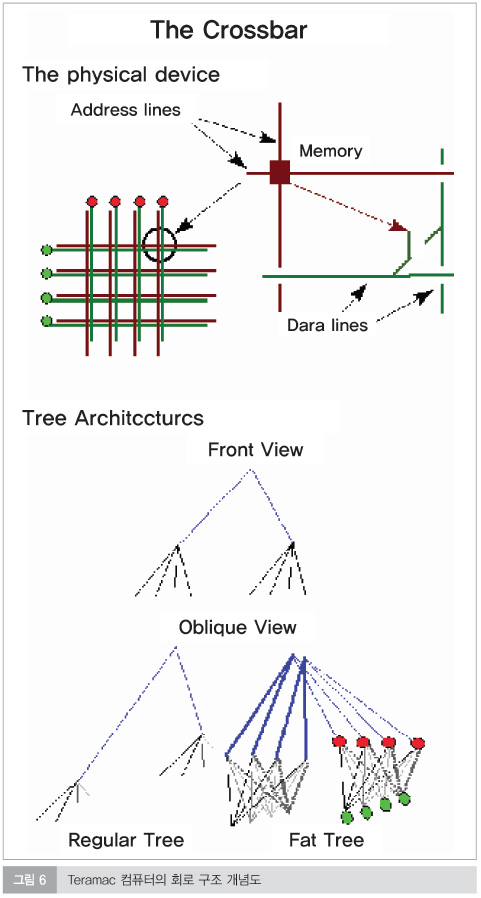

1998년 Heath 등은 defect-tolerant 컴퓨팅 기술을 개발하여 사이언스 지에 발표하였다. 이 컴퓨팅 기술의 기본적인 개념은 다수의 컴퓨팅 유닛을 병렬로 구성된 도선으로 연결하고, 중간에 망가진 컴퓨팅 유닛이 있는 경우 이들에 대한 정보를 메모리에 저장하여, 연산을 수행할 때 도선에서 데이터가 이 컴퓨팅 유닛을 지나가지 않고 회피해서 돌아갈 수 있도록 구성하도록 되어있다. 이 때 망가진 컴퓨팅 유닛에 대한 정보는 별개의 메모리에 저장하고, 이 메모리로 부터 데이터를 주고 받으며 컴퓨팅이 진행이 된다. 이 컴퓨팅 방식은 컴퓨팅 유닛에 결함이 있더라도 컴퓨터가 매우 잘 동작할 수 있도록 하였고, 이러한 방식을 이용한 ‘테라맥(Teramac);이라는 컴퓨터가 HP Lab에서 개발되었다. 그림 6은 테라맥 컴퓨터의 회로 구조의 개념도를 보여준다. 여기서 크로스바 구조를 확인할 수 있는데, 크로스바 구조는 테라맥을 구성하는 도선 네트워크의 핵심이다. 크로스바 구조가 2단으로 연결된 구조에서 각각의 크로스바는 각각 메모리와 스위치가 연결되어 있고, 메모리에 저장된 데이터에 따라 스위치가 열리거나 닫히면서 해당 데이터 라인이 유효한지 무효한지를 결정한다. 이 defect tolerant 구조에서 사용된, 메모리를 이용해 컴퓨터에 사용된 회로를 재구성하는 방식은 이후 FPGA의 기본 기술이 되었다.

일반적인 FPGA는 앞서 언급한 CMOSFET으로 구성된 논리 소자들이 임의로 연결될 수 있도록 하는 메모리와 스위치가 쌍으로 구성된 단위 소자를 포함하고 있다. 메모리에는 연결 구조에 대한 정보가 저장되며, 스위치는 메모리로부터 데이터를 받아 회로를 연결하거나 단락하는 역할을 수행한다. 따라서 FPGA는 일반적으로 여타의 CMOS 연산 소자에 비해 더욱 넓은 면적을 갖고, 낮은 집적도를 갖는다는 단점이 있다. 또 다른 단점은 FPGA 에서 주로 사용되는 메모리는 SRAM인데, SRAM은 휘발성 메모리이기 때문에 전력이 끊어지면 데이터가 손실되는 문제가 있어 지속적인 전원 공급이 필요하다. 따라서 SRAM의 이러한 단점을 대체할만한 새로운 비휘발성 메모리 소자가 필요하다. 또한 이 새로운 비휘발성 메모리 소자는 CMOSFET 로직 회로의 상단에 적층될 수 있으면, CMOSFET과 같은 평면상에 집적되는 SRAM에 비해 전체 소자의 면적을 줄일 수 있다는 장점도 갖게 된다. 이러한 목적에서 FPGA에 사용될 메모리로 ReRAM을 사용하는 것을 심각하게 생각해볼 수 있다. FPGA에 ReRAM을 사용하는 것이 앞서 잠깐 언급한 결함회피구조와는 직접적인 관련이 없을 수도 있다. 하지만 집적되는 메모리와 로직 회로의 밀도가 증가하게 되면, 그만큼 소자 내에 결함이 포함될 확률도 증가하고, 어떠한 형식으로든 필연적으로 결함회피구조를 탑재하는 것이 경제적으로 효과적인 옵션이 될 수 있다.

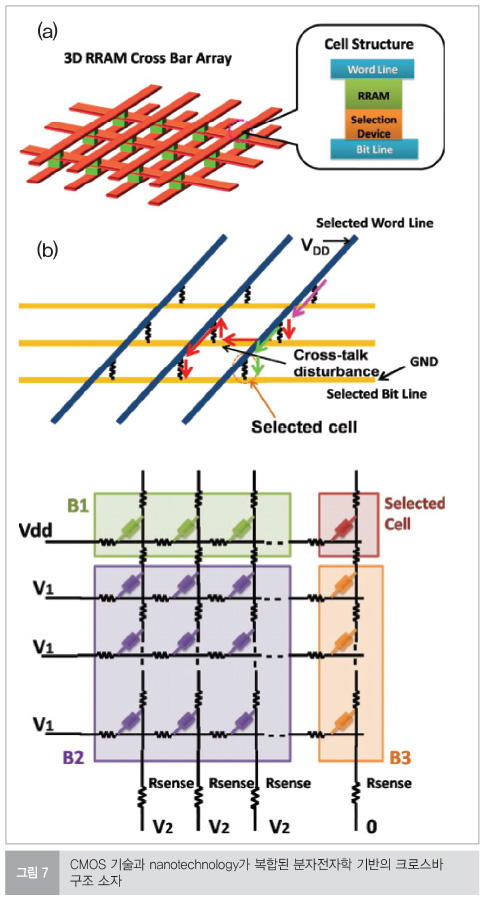

한편, 비슷한 시기인 2000년 경, 분자전자학(molecular electronics)이 광범위하게 연구되었다. 이 분자전자학은 두 전극 사이에 분자를 넣어, 이 구조가 전도체, 다이오드, 심지어는 메모리 특성 등의 다양한 전자적 특성을 구현하는 것이다. 그렇게 함으로써 유기재료를 통해 기존의 무기재료를 대체하는 것을 목표로 삼고자 하였고, 여기에는 열적 안정성, 공정 가능성 등의 문제가 여전히 남아있다. 이 분자전자학은 기본적으로 2개의 단자를 필요로 하며, 따라서 이 분자전자학의 장점을 극대화시킬 수 있기 위해서는 크로스바 구조가 요구되었다.

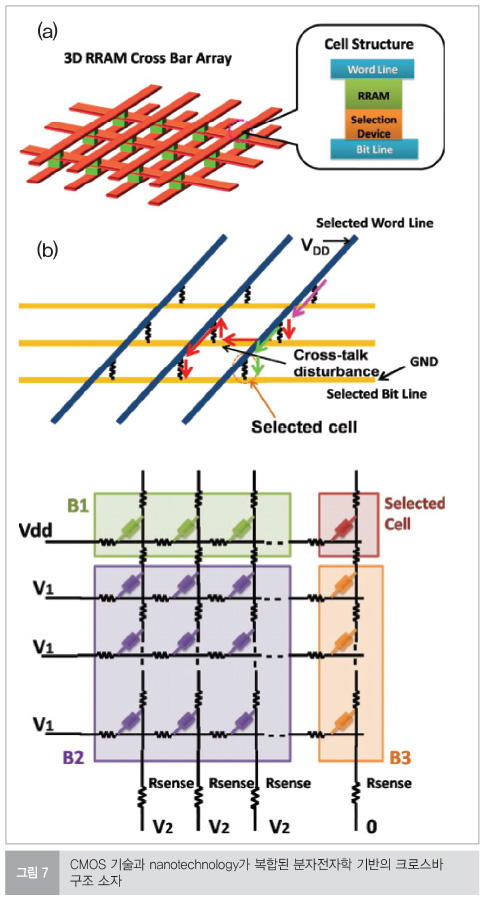

분자전자학을 통해 가장 먼저 만들어진 소자는 기존의 CMOS 기술과 결함한 것이었다. 이러한 점에서, Ziegler와 Stan이 2003년 발표한 연구는 CMOS 기술과 함께 크로스바 구조의 분자적자학을 접목하여 새로운 패러다임의 소자를 제안하였다. 그림 7은 이 소자의 모식도를 보여주는데, 가장 기초적인 크로스바 구조의 형태를 확인할 수 있다.

이러한 가능성에도 불구하고, 분자층의 열적 불안정성과, 불균일한 두께 등의 문제는 여전히 극복하기 힘든 문제로 남아있고, 이러한 유기물에서의 크로스바 구조가 아니라 보다 좋은 안정성을 갖고 있는 것으로 잘 알려진 무기물을 이용한 크로스바 구조가 더욱 가능성을 있을 것으로 보인다.

멤리스터 FPGA 기술

2005년에는 Strukov와 Likharev가 기존에 앞서 언급한 분자전자학 기술과 결함 회피 컴퓨팅의 재구성 가능한 배선 네트워크 개념이 크로스바 구조라는 공통점을 공유하고 있는 점을 착안하여 이들 두 기술을 결합하였다. 추가적으로 이들은 완전히 새로운 반도체-분자 혼성 구조를 발표하였는데, 여기에서 이들은 ‘latching switch’라고 이름붙인 흥미로운 특성을 보이는 분자를 사용하였다. 이 latching switch 는 메모리와 스위치 특성을 동시에 갖고 있는 소자이고, 이는 멤리스터와 동일한 개념이다. 즉, 2005년 당시 아직 멤리스터에 대한 이론적인 발견은 없었지만 분자 재료에서 이미 멤리스터 현상이 관찰되었고, 이를 소자에 적용하고자 하는 연구가 진행되고 있음을 알 수 있다. 이 latching switch가 메모리와 스위치의 특성을 동시에 갖고 있어서 하나의 소자가 결함 회피 컴퓨팅의 메모리와 스위치 2개의 소자를 한꺼번에 대체할 수 있고, 따라서 소자의 성능을 비약적으로 향상시킬 수 있다(실제로 하나의 메모리 유닛이 7개의 트랜지스터와 이들간의 연결 배선을 대체할 수 있었다).

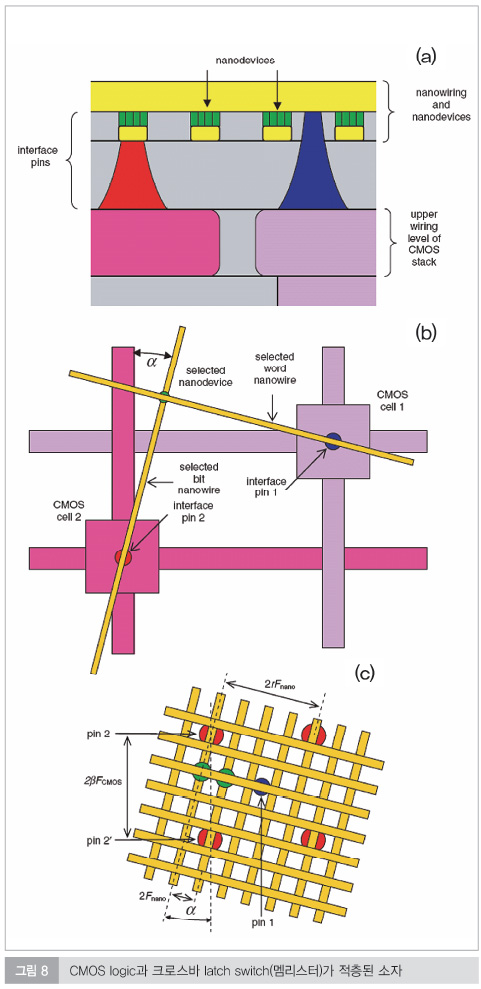

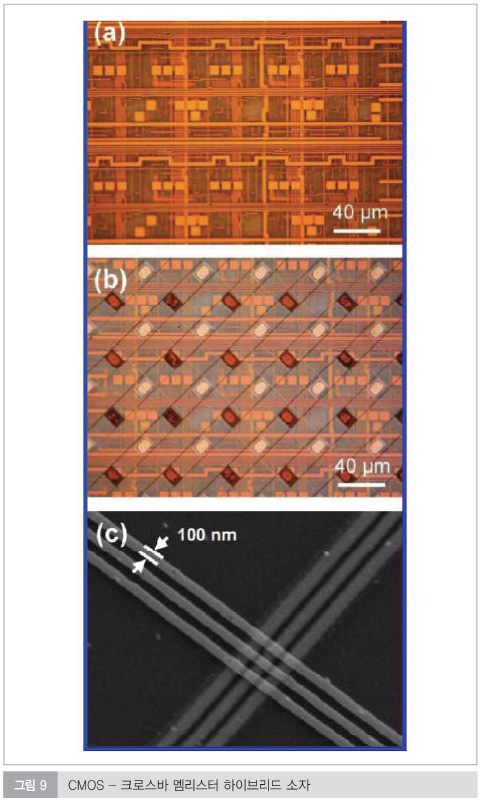

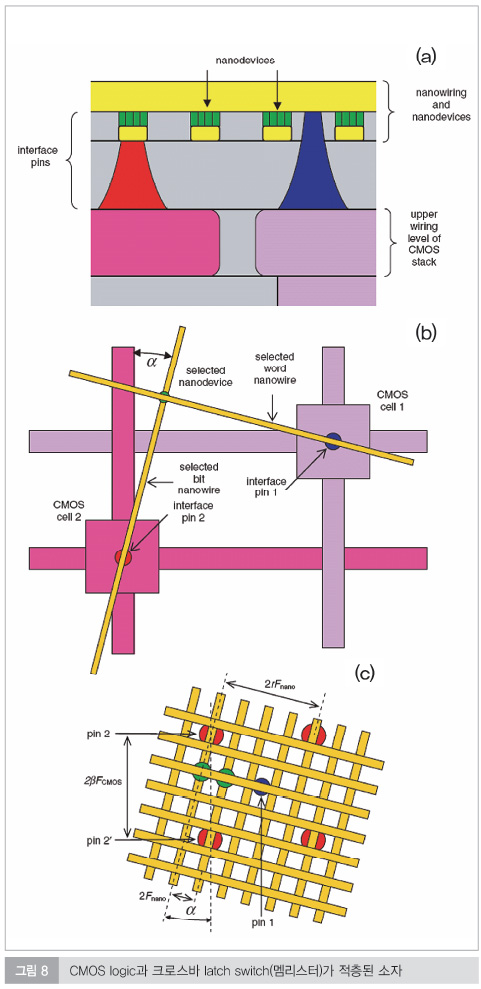

그림 8은 이 저자들이 제시한 진보된 형태의 소자 구조를 보여준다. 이 소자는 2층 적층 구조로 이루어져 있는데, 하단 부분은 기존의 CMOS array가 집적된 구조이며, 상단 부분에는 latching switch가 크로스바 구조로 집적되어 있다. 이 개념은 이후 Xia 등에 의해 memristor-CMOS 혼성 회로라는 이름으로 2009년에 실제 소자로 구현되었다. 이 연구에서, Xia와 그의 동료는, CMOS 소자를 집적하고, CMOS 소자의 상단에 TiO2 멤리스터를 크로스바 구조로 집적하고, 이들을 수직 배선을 통해 연결하였다. 이를 통해 각각의 CMOS 회로는 특정한 연산을 수행할 수 있도록, 멤리스터 크로스바 구조를 프로그래밍 하여 구현할 수 있다.

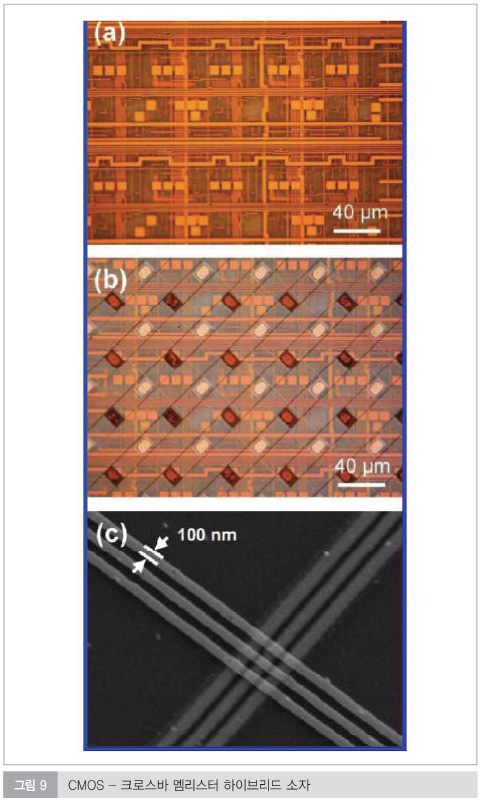

즉, 기존의 SRAM이나 FRAM 등을 이용하던 FPGA 소자를 멤리스터를 이용해 제작한 것이다. 그림 9는 이렇게 제작된 소자의 평면도이다.

멤리스터 FPGA 기술 전망

멤리스터를 FPGA에 응용하는 경우, 메모리가 집적되는 영역이 CMOS 기판 상단에 적층될 수 있어 기존에 메모리가 CMOS 기판과 같은 평면 상에 적층되던 것에 비해 소자의 면적을 최소화시킬 수 있다는 장점이 있으며, 또한 멤리스터 자체가 메모리와 스위치 특성을 동시에 갖고 있는 비휘발성 메모리이기 때문에 메모리 소자 자체의 면적도 최소화될 수 있다. 하지만 향후 멤리스터 FPGA가 상용화되기 위해서는 멤리스터 자체의 신뢰성이 향상되어야하는 과제가 남아 있으며, 또한 멤리스터를 저렴하게 대량 생산할 수 있는 기반이 갖추어져 가격 경쟁력을 갖출 수 있어야 할 것이다.