CMOS 디지털 회로에서의 전력소모의 주원인인 신호의 천이 중에서 회로의 동작에 직접적인 영향을 미치지 않는 불필요한 신호의 천이인 글리치를 줄이기 위한 효율적인 알고리즘을 제시하였다. 버퍼 자체에 의한 전력소모 증가보다 글리치 감소에 의한 전력감소가 큰 버퍼를 선택하여 삽입하며 이때 버퍼 삽입에 의한 전력감소는 다른 버퍼의 삽입 상태에 따라 크게 달라질 수 있어 ILP(Integer Linear Program)를 이용하여 적은 버퍼 삽입으로 전력감소를 최대화할 수 있는 저전력 설계시스템을 구현하는 것을 목적으로 하였다.

기술개요

CMOS의 개요

CMOS(Complementary Metal-Oxide Semiconductor)는 p채널의 MOS 트랜지스터와 n채널을 서로 절연하여 동일 칩에 만들어 넣어 양자가 상보적으로 동작하도록 한 것으로 소비전력은 μW 정도이고 동작은 고속, 잡음 배제성이 좋다. 상보성 금속산화막 반도체(相補性金屬酸化膜半導體)라는 용어도 통용되며 전원 전압의 넓은 범위에서 동작하고 TTL에 적합하며 동일회로 내에서 공존 가능하다.

P채널과 N채널의 MOSFET를 전원전압 간에 직렬로 구성하고 입력은 두 가지 MOSFET의 게이트에 같이 연결하고 출력은 두 가지 MOSFET 드레인 사이에 연결한 집적회로의 구조이다. 이 경우 각 MOSFET는 스위치로 간주될 수 있으며 같은 입력신호에 대하여 P채널과 N채널이 서로 반대로 동작하므로 전원 전압과 접지 사이에 기본적으로 흐르는 bleeding current가 거의 없어지므로 TTL 논리 소자에 비해 소비전력이 적은 논리회로를 구현할 수 있고 부하를 면적을 많이 차지하는 저항이 아닌 MOSFET를 사용하므로 집적도를 향상시킬 수 있다. MOSFET의 동작 영역에서 직류 전달특성은 선형영역에서 출력전압이 입력전압과 거의 같고 포화영역에서 출력전압은 게이트전압에서 ‘문턱전압’을 뺀 값이 된다. P-MOSFET가 포화영역일 때 N-MOSFET는 선형영역이고, N-MOSFET가 포화영역일 때 P-MOSFET는 선형영역이다.

CMOS 동작영역의 대부분은 선형영역이며 엄밀하게 양자의 ‘문턱전압’이 겹치는 영역이 존재하므로 사용하지 않는 입력 단자는 문턱전압 영역에 들어가지 않도록 풀업 또는 풀다운에 연결해 주는 것이 좋다.

CMOS 구조에서 게이트전압에 입력되는 제어 펄스를 ‘1’에서 ‘0’으로 변경했을 경우에 노이즈 없이 이전의 출력을 할 수 있고 ‘0’에서 ‘1’로 변경했을 경우 역시 노이즈 없이 입력신호를 출력할 수 있다. CMOS 구조의 논리회로는 전원전압을 낮게 하면 소비전력이 적은 반면 전달 지연시간이 커지는 특성을 가지고 있다. 제조 프로세서가 개선되어 낮은 전압의 동작과 고속 동작을 할 수 있게 되었다.

1990년대가 되면서 반도체 메모리나 마이크로프로세서의 논리 IC는 대부분 CMOS 구조가 되었으며 작은 규모의 전원회로, 아날로그-디지털 변환회로, 디지털-아날로그 변환회로 등이 포함되어 제작하기 시작하였다.

CMOS의 전력 소모 원인

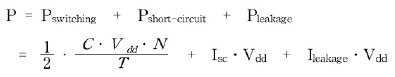

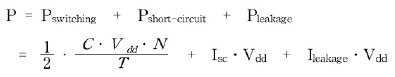

CMOS 회로에서 전력 소모의 원인은 다음과 같이 나타낼 수 있다.

여기서 P는 소모되는 전체 전력을 나타내며 Vdd는 공급전압, T는 클록 주기이다. Pswitching은 CMOS 회로의 입력의 스위칭에 따라 공급전압으로부터 충전되거나 접지로 방전될 때 발생되는 스위칭 또는 dynamic 전력소모를 나타낸다.

C는 load 커패시턴스를 나타내며 N은 각 클락 주기마다 게이트 출력에서의 천이 수 즉, 스위칭 동작 수를 나타낸다. Pshort-circuit은 NMOS와 PMOS가 동시에 동작할 경우 공급 전원에서 접지로 직접 흐르는 short-circuits전류에 의해 소모되는 것을 나타낸다. Pleakage는 벌크(bulk) 지역에서 역방향 다이오드의 누설전류에 의하여 발생하는 것인데 주로 공정기술에 의해 결정이 된다. 이밖에도 subthreshold 트랜지스터 전류도 전력을 소모한다.

CMOS 회로에서 소모되는 전력은 스위칭전력, short-circuit 전력, 누설전력이다. 이중에서도 VLSI 회로에서 스위칭전력이 전체 전력소모량의 대부분(90%)을 차지한다.

연구개발 동향

오스트리아 마이크로시스템즈의 풀 서비스 파운드리 사업부가 2011년 6월 제48회 설계자동화 컨퍼런스(Design Automation Conference: DAC)에서 0.18㎛ 고전압 CMOS 기술의 두 가지 새로운 아날로그/혼성신호 개발 킷(HIT-kit)을 발표했다. IBM과 공동 개발한 0.18㎛ 고전압 CMOS 공정기술은 오스트리아 마이크로 시스템즈에서 지속적으로 개선한 6세대 기술이다. Cadence Virtuoso 맞춤설계 플랫폼(IC5.1.41과 IC6.1.4 릴리즈)을 기반으로 한 이 HIT 킷 제품들은 아날로그 집약적 혼성신호, 스마트센서, 시스템 온칩이 경쟁력 있는 시스템 개발의 타임 투 마켓을 크게 향상시킨다. 복잡한 디자인으로도 단번에 혼성신호를 개발해야 하는 엔지니어를 지원하는 이 포괄적인 설계 환경은 고도의 정확한 시뮬레이션 모델 및 유연한 SKILL 기반 PCells를 통해 검증된 경로를 제공한다.

새 HIT 킷인 3.78버전(IC5.1.41용으로 퀄리파이)과 4.01버전(IC6.1.4용으로 퀄리파이)은 모두 업계에서 입증된 IBM의 파운드리 공정기술인 CMOS7RF을 기반으로 하는 0.18㎛ 공정기 술 H18(고전압 CMOS)이다.

이 개발 킷은 실리콘으로 검증된 디지털 및 아날로그와 RF무선 라이브러리 요소로써 완벽한 저전압소자(1.8V와 5.0V) 및 상이한 두께의 게이트 산화막(20V와 50V 소자)의 고전압 소자 세트와 함께 제공된다. 시뮬레이션 모델로써 두 버전 모두에서 동작하는 추출 및 검증실행 세트, Calibre와 Assura 및 자동 레이아웃 디바이스 발생기를 포함한다. 안전작동 영역 검증도구(SOAC)뿐만 아니라 수명주기 시뮬레이션 툴의 완벽한 H18 HIT 킷은 플러그엔 플레이 툴 세트로 설계자가 단 한 번에 완벽한 설계를 할 수 있다.

H18 HIT 킷에 포함된 디지털 표준 셀 라이브러리는 118kGates/㎟의 뛰어난 게이트 집적도를 가지고 있으며 표준과 저누설전류 버전으로 제공된다. 설계키트 내의 모든 I/O 구조는 실리콘으로 검증되며 군용정전기(ESD) 및 JEDEC 래치업 Test 규격 즉, 4kV HBM과 250㎃ 래치 업 성능을 만족시킨다.

ST 마이크로일렉트로닉스는 CMP(Circuits Multi Projects)와 공동으로 대학, 연구소, 기업이 프로토타입 개발에 CMOS 28㎚ 공정기술을 이용할 수 있도록 제공한다고 밝혔다. ST 마이크로일렉트로닉스의 CMOS 28㎚ 공정기술은 CMP가 제공하는 실리콘 중개 서비스를 통해 제공된다.

CMP는 또 ST 마이크로일렉트로닉스의 130㎚ SOI(Silicon-on-Insulator)와 130㎚ SiGe 공정기술도 제공한다. 지금까지 170개 대학 및 기업체들이 90㎚ CMOS 공정기술의 설계법과 설계키트를 제공받았으며 200개 이상의 대학 및 기업이 ST의 65㎚ 벌크 및 SOI CMOS 공정기술의 설계규칙과 설계키트를 제공받고 있다. ST 마이크로일렉트로닉스는 저전력, 무선 및 휴대용 컨슈머 애플리케이션에 적합한 차세대 SoC(System-on-Chip) 제품개발을 위한 45㎚(0.045micron) CMOS 디자인 플랫폼의 세부사항을 발표했다.

ST의 혁신적인 저 전력프로세스 옵션은 다수의 임계 트랜지스터를 갖추고 있어 65㎚ 기술로 구현된 설계와 비교해 실리콘 면적을 절반으로 감소시킨다. 이 프로세스는 속도를 최대 20%까지 향상시키거나 동작하는 동안 누설전류를 절반까지 감소시키고 정지모드 시 수십 배의 누설전류를 감소시킨다.

최첨단 45㎚ 저 전력 CMOS 플랫폼은 고집적 45㎚ 디모듈레이터 SoC 디바이스설계를 완성 또는 테잎-아웃하기 위해 이미 사용되고 있다. 이 칩 설계는 고성능 듀얼-코어 CPU 시스템과 관련 메모리 계층을 포함하고 있으며 새로운 수준의 성능을 낮은 소비전력으로 통합하기 위해 45㎚ 프로세스 기술 노드에서 요구되는 정교한 저전력 기법이 특징이다.

새로운 저전력 설계 플랫폼은 45㎚ 공정기술의 다양한 특징들과 모듈방식의 장점들을 모두 활용하고 있으며 프랑스 그레노블(Grenoble)에 근처의 크롤(Crolles)에 소재한 ST 마이크로일렉트로닉스에서 개발되었으며, 크롤2 연합(Crolles 2 Alliance)으로 운영되는 300㎚ 웨이퍼 시설단지에서 검증되었다.

보급이 완료된 다른 45㎚ 플랫폼과 공통적으로 ST의 저 전력 45㎚ 프로세스는 고밀도 및 고성능에서 요구되는 최첨단 모듈을 모두 갖추고 있다. 이러한 중요한 모듈은 중요한 패턴 레이어를 위한 193㎚ 이머전 리소그래피, 쉘로우-트렌치(shallow-trench) 절연 및 트랜지스터 스트레서(transistor stressor), 밀리세컨즈 어닐(anneal)을 통한 첨단 접합 엔지니어링, 인터커넥트 커패시턴스를 감소시킬 수 있는 로우-k 인터-메탈 쿠퍼 유전체를 포함하고 있다.

45㎚ 설계 플랫폼은 케이던스, 멘토 그래픽스, 시놉시스, 마그마 등의 EDA 업체들의 개별 R&D 그룹이 협력하여 개발된 설계 솔루션을 통해 업계 최고의 CAD 툴이 완벽 지원되어 친숙한 산업 표준 툴을 사용한 고성능 SoC 솔루션을 이용해 고객들이 곧바로 설계를 시작할 수 있다.

국내 연구개발 수준

매그나칩 반도체는 0.18㎛ 혼성 신호 모드 및 RF CMOS 공정을 이용한 IC설계에 애질런트테크놀로지스의 전자설계 자동화 소프트웨어인 RFDE(Radio Frequency Design Environment)를 사용할 수 있도록 새로운 프로세스 디자인 키트를 개발했다고 발표한 바 있다. 이 프로세스 디자인 키트는 기존 케이던스 설계 시스템을 지원하는 프로세스 디자인 키트를 확장한 것으로 DC에서 기저 대역을 포함하여 RF 대역에 이르는 전 주파수 범위를 지원한다. 따라서 설계자가 전체 시스템에 대한 칩 설계를 시뮬레이션 할 수 있게 되어 전 주파수 대역에서 정확한 운영이 가능하게 된다.

0.18㎛노드에서 이용 가능한 주파수는 기저 대역의 오디오 및 비디오 주파수에서 5GHz의 RF에까지 이르며 향후 0.13㎛ 노드에서 10GHz 이상의 주파수 대역을 확보할 것으로 예상된다.

4종의 정전용량(4, 6, 8, 10fF/u㎡)을 제공하는 금속-절연체-금속커패시터 공정기술은 고유전 유전막(high dielectric constant material layer) 사용을 통해 기존의 질화규소 절연막(silicon nitride insulator layer)을 대체했으며 누수전류를 최소화해 단위면적당 보다 높은 정전용량을 얻을 수 있는 장점이 있다. 소자의 단위면적을 크게 줄임으로써 전하축적량을 높이고 소자 간 신호 대비 잡음비율을 크게 낮췄으며 실리콘 기판에 작은 딥 트렌치(deep trench)들이 묶음으로 장착된 3-D 형태의 딥 트렌치 커패시터 공정기술은 22fF/u㎡의 높은 정전용량 및 25V의 파괴전압을 지니고 있다.

비메모리 반도체인 CMOS 로직의 0.18㎛ 기술은 메모리 반도체와 비교할 경우 1기가 D램과 동일한 수준으로 이의 양산화 성공은 0.25㎛ 기술이 상용화되고 있는 시점에서 한국 반도체 기술을 한 단계 높이고 있다.

프리스케일 세미컨덕터는 업계 최초로 CMOS 기술을 기반으로 한 3.3V UHF TV 무선 주파수(RF) 모듈레이터를 발표했으며, 이는 디자인에서 제품 출시에 이르는 과정을 단축시킬 수 있도록 설계된 비용 효율적인 저전력 솔루션이다. DVD/DVDR 플레이어, 모듈, 비디오게임과 같은 TV 관련 분야뿐만 아니라 위성, 지상파 또는 케이블 TV용 아날로그, 디지털, 인터넷 프로토콜(IP) 셋톱박스 등의 다양한 시스템 요구를 완화시켜 줄 수 있다.

MC44CM373과 MC44CM374 디바이스는 구성부품의 수를 줄이고 보드공간을 최소화한 제품으로 음성 하위 방송파와 UHF 전압 제어식 오실레이터를 하나의 칩에 통합했다. 이를 통해 구성부품의 추가조정 없이 주요 RF경로를 시스템 보드에 간편하고 손쉽게 통합하고 구현할 수 있다. 460MHz와 880MHz 범위에서 작동하며 완벽한 통합 형태로 외부의 능동 구성부품 또는 정밀부품이 필요하지 않다. 또한 광범위한 기능, 고속 I2C 호환 버스를 통한 손쉬운 제어 그리고 제품 테스트를 간소화할 수 있도록 여러 가지 모드를 제공한다. CMOS 기술의 사용은 탁월한 RF 성능을 제공할 뿐 아니라 소비전력 및 디바이스 비용절감의 효과를 얻을 수 있다.

삼성전자는 2005년 세계 최소형 720만 화소 CIS{CMOS(Complementary Metal Oxide Semiconductor) Image Sensor}를 출시하며 본격적으로 이 시장에 뛰어들었다. 이후 2006년에는 1.75㎛ 픽셀 840만 화소 CIS를 개발했으며 업계 최초로 초미세 픽셀사이즈 1.4㎛를 적용한 고급형 840만 화소 CIS를 발표하기도 했다. CIS는 카메라 렌즈를 통해 들어오는 빛을 감지해 전기신호로 바꿔주는 비메모리 반도체로 디지털카메라와 휴대전화의 핵심 부품이다.

2010년에는 광전(光轉)효율을 높여 소형 픽셀에서도 선명한 이미지를 구현하는 CMOS 이미지센서 신제품을 개발했다. 이번에 개발된 제품은 ▲ 1/4인치 구경, 1.4㎛ 픽셀사이즈의 스마트폰용 500만 화소 제품 ▲ 1/2.33인치 구경, 1.4㎛ 픽셀사이즈의 디지털카메라·디지털캠코더용 1460만 화소 제품 등 2종이다.

이미지센서에 이면조사형(BSI, Back Side Illumination) 기술을 적용했으며 이는 이미지센서의 수광부를 칩의 최상부에 배치해 배선층에 의한 빛의 난반사를 막고 단위 화소당 빛 흡수율을 높여 광전효율을 최대화할 수 있는 기술이다. 기존제품의 경우 표면조사형(FSI, Front Side Illumination) 기술이 적용되어 이미지센서 상부에 위치한 배선 때문에 센서의 감도를 저하시키는 단점이 있었다. 이번에 개발된 제품은 FSI 타입의 기존제품 대비 저 조도에서 감도가 30% 이상 개선되어 어두운 환경에서도 선명한 화질을 구현할 수 있다. 특히 최대 해상도에서 초당 30프레임, 풀 HD 해상도에서 초당 60프레임의 속도로 동영상을 촬영할 수 있다. 90나노 저 전력 공정을 적용해 전력소비를 줄였으며 1460만 화소 센서의 경우 방열성능이 우수한 TePLCC(Thermal enhanced Plastic Leaded Chip Carrier) 패키지 모듈로 제작되어 고화소·고성능 제품에서 발생하는 발열문제를 개선한 친환경 제품이다.

하이닉스반도체는 최근 들어 CMOS 이미지센서(CIS), 디스플레이 구동 칩(DDI) 등 시스템반도체 사업을 강화하고 있다. 200mm 라인인 청주 M8 공장에서 시스템 반도체 제품을 생산하고 있으며 500만 화소 이상의 CMOS 개발에 나서고 있고 90나노 공정에서 1.4 마이크로미터 픽셀 기술을 적용한 제품을 출시할 계획이다.

동부하이텍 반도체 부문은 중국 심천에서 열리는 IIC(International IC) China 2008 전시회에 참여하여 30만(VGA), 130만, 200만 화소급 CMOS 이미지 센서와 모듈 등 다양한 제품을 출시한 바 있다. 또한 Mobile Innovation, Ginwave 등 중국 중견 휴대전화 개발업체들의 주요 인사들을 초청하여 CIS 제품의 특징과 향후 제품 개발방향에 대해 소개하고 품질, 납기, 가격 등 주요 마케팅 이슈에 대해 토의하는 등 향후 협력방안에 대해 논의했다고 밝혔다. 200만 화소 휴대전화는 현재 카메라폰 시장에서 가장 큰 부분을 차지하고 있으며 중국·인도·브라질 등 최근 세계 경제의 성장세를 이끌고 있는 신흥 개발국들을 중심으로 그 시장이 점차 커질 것으로 기대하고 있다.

중국의 경우 일부지역에서만 시작했던 3G 서비스가 지난 2010년 5월부터 전국적으로 확대되면서 130·200만 화소 휴대전화의 생산량이 급격하게 늘어나고 있어 해당 CIS들의 수요가 크게 증가하고 있는 추세이다.

동부하이텍과 에스이티아이는 지난 2004년부터 CIS 칩 위탁생산 계약을 맺고 30만화소급·130만화소급에 이어 향후 110나노공정을 이용한 300·500만화소급의 다양한 CIS 제품을

추가로 개발할 예정이다. 동부하이텍은 300만 화소 이상의 고품질의 CIS 칩과 모듈을 개발하는데 역량을 집중하는 한편 센서 설계에서 모듈 생산까지의 안정적인 일관 생산체계를 기반으로 대형 거래선을 발굴해 나갈 계획이다. 또한 자동차 후방 카메라, CCTV용 이미지센서 등 차세대 제품을 개발하여 내년 중으로 양산하는 등 부가가치가 높은 이미지센서 사업을 점차 확대해 나갈 것이라고 밝혔다.

에스이티아이(SETi)가 비메모리반도체인 이미지센서 누적 출하량 1억 개를 돌파하면서 이미지센서 업계 신흥 강자로 부상하고 있다.

3세대(3G) 휴대전화에 들어가 영상통화 기능을 지원하거나 신흥시장을 겨냥한 저가폰 등에 들어가는 30만 화소(VGA) 이미지센서에 주력(현재까지 출하한 1억600만개 가량 이미지 센서 가운데 30만 화소 제품이 9700만개 수준)하고 있다.

CMOS 이미지센서는 과거에 많이 사용됐던 고체 촬상소자(CCD: Charge-Coupled Device)보다 소비전력이 적어 현재 디지털카메라와 휴대전화 등 저전력이 요구되는 많은 촬상기기에 사용되고 있다.

특허 측면에서 CMOS 이미지센서는 반도체 관련 출원이 많으며 현재에도 계속 증가추세를 보이고 있다. 특히 1997년 이후 한국, 일본, 미국의 특허출원이 모두 급증하는 추세를 보이는 것은 그 동안 기술적으로 문제가 됐던 CMOS 타입의 카메라 칩과 CMOS 타입 액티브 픽셀센서(APS)의 문제가 해결된데 따른 것으로 분석된다.

고화질이 요구되는 애플리케이션에서 CCD 센서에 열세를 보이는 결점이 있으나 이 문제는 빠른 속도로 개선되고 있다. 국내에서도 500만화소급의 CMOS 센서가 개발돼 그 이상의 고화질 분야로 계속 발전해 나가고 있다. 따라서 CMOS는 저소비전력과 소형화, 저가 등에 이어 고화질까지 갖춰 주력 영상센서로 급부상할 것으로 전망되기 때문에 관련 산업계에서는 CMOS 센서가 올해를 기점으로 CCD 센서를 능가할 것으로 예상하고 있다.

5~10년 후 예측

새로운 저전력 설계 플랫폼은 45㎚ 공정기술의 다양한 특징들과 모듈방식의 장점들을 모두 활용하고 있다. 최첨단 45㎚ 저전력 CMOS 플랫폼은 고집적 45㎚ 디모듈레이터 SoC 디바이스 설계를 완성 또는 테잎-아웃하기 위해 사용되고 있다.

반도체 분야의 기술발전 예측에 의하면 반도체 게이트 산화막의 두께는 휴대전화에 쓰이는 저전력 소자의 경우 0.8∼1.2㎚, 컴퓨터 CPU와 같은 고성능 소자에서는 0.5∼0.8㎚에 이를 것으로 예상되고 있다. 그러나 현재 게이트 산화막으로 사용되는 SiO2(이산화실리콘)로는 얇아진 박막두께로 인해 전류의 누설이 일어나 반도체 소비전력이 급격하게 증가하게 되기 때문에 SiO2보다 유전상수가 큰 고유전체 산화막으로 교체하려는 연구가 진행되고 있다. 이러한 고유전체 산화막을 나노크기에서 박막화 하는데 필수적으로 사용되는 기술이 원자층 증착기술(ALD: Atomic Layer Deposition)이다.

기존의 ALD 공정으로 여러 소재를 이용하여 우수한 특성을 가지는 박막을 형성하려고 하였으나 박막증착 시 이온들에 의해 기판 및 박막에 손상을 가져와 박막의 특성이 나빠지는 결과를 가져왔다. 특히 전하의 이동성 저하로 인해 Intel을 비롯한 반도체 업체들은 2008년도 이전에 45㎚급 CMOS 소자에 고유전체 게이트 산화막을 적용하려던 계획을 2010년 이후 32㎚ 이하 기술로 미루게 되었다.

‘원거리 플라즈마 ALD’ 기술과 이를 이용한 원자층 증착장치는 플라즈마 발생지역과 기판사이의 간격을 기존의 방식보다 크게 하여 플라즈마 이온에 의한 영향을 최소화함으로써 기판과 박막의 손상을 획기적으로 줄였다. 직접(direct) 플라즈마 방식에 비해 전자이동도가 50% 향상되어 앞으로 이 기술이 테라급 나노 CMOS 소자를 제작하는데 필수적인 기술이 될 것으로 기대된다.

글로벌 파운드리즈는 스마트 모바일기기 시장을 위한 신기술과 2GHz가 넘는 프로세싱 파워를 필요로 하는 고성능 프로세서를 소개했다.

2011년 4사분기에 시범생산이 시작될 예정인 28㎚ 고성능 플러스(High Performance Plus, HPP)기술은 기존 28㎚ 고성능(HP)제품보다 10%가 넘는 성능촉진을 제공한다. 뿐만 아니라 옵션으로 초저누출 트랜지스터와 고성능에서부터 저전력에 이르기까지 애플리케이션을 확대한 S램도 소개했다. 더욱이 풍부한 RF CMOS도 제공함으로써 저전력에서부터 고성능 기기에 이르기까지 광범위하게 대처할 수 있는 시장에서 이 기술을 차세대 고성능 SoC 설계에 이상적인 플랫폼으로 만들었다.

새로운 28㎚-HPP 기술은 글로벌 파운드리즈의 28㎚ 제품군을 완성한다. 여기에는 고성능 유선 어플리케이션과 전력 민감형 모바일 및 소비자 애플리케이션용 SLP(the Super Low Power) 기술을 겨냥한 28㎚ 고성능(HP) 기술이 포함된다.

모든 28㎚ 기술은 글로벌 파운드리즈의 혁신적인 HKMG에 대한 게이트 퍼스트(Gate First) 접근을 특징으로 하며 접근법은 다른 28㎚ HKMG 솔루션보다 확장성과 제조능력 면에서 모두 뛰어나며 실제로 더 작은 다이 크기와 비용을 필요로 할 뿐 아니라 증명된 설계요소와 함께 호환성 그리고 이전기술 노드에서 나온 과정흐름을 제공한다.

글로벌 파운드리즈는 현재 28㎚ 기술 설계를 채택하고 있다. 다양한 설계가 이미 실리콘 확인을 거쳤고 더 많은 제품과 IPrja社 칩이 독일 드레스덴에 있는 글로벌 파운드리즈의 팹 1

에서 확인되고 있다.

CMOS 디지털 회로에서의 전력소모의 주원인인 신호의 천이중에서 회로의 동작에 직접적인 영향을 미치지 않는 불필요한 신호의 천이인 글리치를 줄이기 위한 효율적인 알고리즘을 제시한다. 제안된 알고리즘은 회로의 지연 증가 없이 게이트 사이징과 버퍼 삽입에 의해 경로균등(Path Balancing)을 이룸으로써 글리치를 감소시킨다.

경로 균등화를 위하여 먼저 게이트 사이징을 통해 글리치의 감소와 동시에 게이트 크기의 최적화를 통해 회로 전체의 커패시턴스까지 줄일 수 있으며 게이트 사이징만으로 경로 균등화가 이루어지지 않을 경우 버퍼 삽입으로 경로 균등화를 이루게 된다.

5~10년 후 예측은 버퍼 자체에 의한 전력소모 증가보다 글리치 감소에 의한 전력감소가 큰 버퍼를 선택하여 삽입할 것이며 버퍼 삽입에 의한 전력감소는 다른 버퍼의 삽입 상태에 따라 크게 달라질 수 있어 ILP(Integer Linear Program)를 이용하여 적은 버퍼 삽입으로 전력감소를 최대화할 수 있는 저전력 설계 시스템을 구현할 것으로 예측된다.

결 론

스위칭 전력을 최소화하는 저전력 방법은 Pswitching의 식에서 알 수 있듯이 공급전압 Vdd을 줄이거나 커패시턴스를 줄이거나 스위칭 동작수(N/T)를 줄이는 것이다. 소모되는 전력은 공급전압의 자승에 비례하므로 공급전압을 줄이는 것은 매우 효과적이다. 하지만 공급전압이 감소함에 따라 회로의 지연시간이 늘어나게 된다. 따라서 병렬화, 파이프라이닝 등을 사용하여 회로의 성능을 증가시킨 다음 공급전압을 낮추어 처리량(throughput)을 유지하는 것이다. 이를 위해서 제안된 방법으로 병렬화, 파이프라이닝 등을 들 수 있다.

소비전력을 감소시키는 두 번째 방법은 소비전력이 주파수와 직접 비례하기 때문에 속도를 감소시키는 것이다. 하지만 고정된 타이밍 제한 조건을 가지는 실시간 응용분야에는 주파수를 감소시킬 수 없다. 외부 데이터율(external data rate)은 고정되지만 하드웨어가 시간을 최대로 활용할 수 있도록 내부 클럭을 선택할 수 있다.

소비전력을 감소시키는 세 번째 방법으로 유효정전 용량을 감소시키는 것이다. 유효정전 용량을 감소시키는 방법은 분산계산(distributed computing)을 하거나 참조의 국부성(locality of reference)을 이용하거나 사용하지 않고 있는 모듈을 전력관리를 통하여 power-down을 한다.

자원 공유를 최소화하여 데이터 상관을 보존하여 스위칭 활동도를 감소시키거나 programmability를 필요로 하는 응용분야에 범용 프로세서 유닛보다 작은 전력을 소비하는 특정한 모듈을 사용하는 방법 등이 있다.