본고는 ‘고집적 구리기둥 범프의 도금층 균일성 향상 공정기술 개발’로써 MCP 기술을 구현하는데 핵심기술 중의 하나로써 그 밖의 여러 가지 관련 기술들과 조화를 이루면서 그 기능을 발휘하게 되므로 본 연구의 구리기둥 범프를 둘러싸고 있는 주변 기술들과 함께 최신 MCP 기술에 대한 국내외 현황과 동향 및 발전 방향과 관련된 산업 환경을 기술한다.

국내외 기술동향

세계 반도체생산은 주요 5개국이 총생산량의 95% 이상을 차지하는 가운데 한국이 세계 3위의 생산규모를 자랑하고 있는 산업이다. 메모리 분야는 핵심 수출부품으로 우리나라가 부동의 세계 1위를 차지하고 있으나 비메모리는 세계적 기술과는 큰 기술적 차이를 보이고 있다. 특히 비메모리 산업은 메모리 산업보다 4배 이상 큰 시장을 갖고 있는 고부가가치 산업임에도 불구하고 국내기반은 아직도 매우 취약한 상황에 있다.

반도체 관련 장비·재료산업 역시 반도체 시장의 20% 이상을 차지하는 핵심 후방산업이나 국내기업의 경쟁력은 미흡하여 반도체 관련 장비산업은 일본·미국의 대형장비 재료업체들이 대부분의 시장을 차지하고 있으며 그 시장점유율이 더욱 더 확대되는 추세로 세계 톱 10업체 중 일본 5개 업체, 미국 4개 업체, 유럽 1개 업체가 전체 장비·재료시장의 60%를 점유한다.

Intel社 공동창업자인 Gordon Moore가 주장하였던 마이크로칩의 밀도가 매 18개월마다 2배로 늘어난다는 법칙, 즉 Moore의 법칙을 뛰어넘는 기술로서 기대되는 기술이 3차원 MCP (Multi-Chip Packaging) 기술이다. MCP 기술은 다수의 칩을 2차원적인 배열이 아니라 다수의 칩을 박층화하고 이들을 3차원적으로 적층한 후 각 칩을 서로 연결하는 기술로 휴대용 통신기기 및 멀티미디어기기의 경박 단소 요구에 대응 가능한 새로운 반도체 패키지 기술이다. MCP 기술은 제품의 무게와 전력소모량도 줄일 수 있으며 특히 이차원 배열에 비하여 삼차원 배열을 통해 interconnection 길이를 최소화함으로 이차원 배열시 발생하는 신호지연, 임피던스 부정합 등의 손실을 최소화 할 수 있고 공간적으로도 수직방향을 활용하므로 단위면적당 실장면적을 극대화하여 대용량, 초소형 부품을 개발할 수 있기 때문이다. 반도체 공정의 핵심기술인 lithography의 한계(현재 30㎚) 및 물리적인 한계에 의한 반도체칩의 소형화 한계를 고려할 때 기술적 추세는 3차원 반도체 적층기술, 즉 차세대 MCP 기술이 ‘More than Moore’를 구현할 수 있는 대안 기술로 기대된다.

본고는 ‘고집적 구리기둥 범프의 도금층 균일성 향상 공정기술 개발’로써 MCP 기술을 구현하는데 핵심기술 중의 하나로써 그 밖의 여러 가지 관련 기술들과 조화를 이루면서 그 기능을 발휘하게 되므로 본 연구의 구리기둥 범프를 둘러싸고 있는 주변 기술들과 함께 최신 MCP 기술에 대한 국내외 현황과 동향 및 발전 방향과 관련된 산업 환경을 기술한다.

1. 국내

국내 MCP 분야의 연구 및 제조는 삼성전자와 SK하이닉스가 주도하고 있으며 주로 플래시 메모리에서 Stack MCP를 제조하여 시장을 성장시키고 있다. 반도체 산업은 메모리·비메모리로 구분할 수 있으며 메모리 분야는 RAM·ROM, 비메모리는 1만종 이상의 개별품목으로 구성되어 있다. 시장의 대부분을 차지하는 비메모리(시스템 반도체)가 세계시장 대부분(약 80%)을 차지하고 있으며 그 규모가 지속적으로 확대되는 추세이다. 산업연구원 발표의 ‘반도체 산업의 2020 비전과 전략’에서 보면 반도체 산업은 2015년 5,985억 달러의 시장을 형성하고 매년 7.5%의 성장을 거듭하여 2020년에는 8,610억 달러의 시장으로 확대될 것으로 전망하고 있다. 또한 반도체 산업의 전 세계 수출규모도 지속적인 증가를 보여 2015년에는 3,650억 달러, 2020년에는 5,530억 달러의 거대 글로벌 시장을 형성할 것이라고 예측된다.

삼성전자의 경우 3G 휴대전화를 타깃으로 256M NAND 플래시, 128M NOR 플래시, 64M Ut RAM 그리고 128M Mobile DRAM을 단일 패키지에 구현한 스택 MCP를 개발하였으며, SK하이닉스는 단일 패키지에 플래시 메모리와 SRAM을 결합하여 휴대전화용 MCP를 생산하고 있다.

2007년 4월, 삼성전자는 세계 최초로 TSV(Through Silicon Via)칩 접속방식인 WSP(Wafer-Level Processed Stack Package) 기술을 적용한 4단 적층 DRAM칩과 모듈 개발에 성공하였고 개발품은 512Mb DDR2 DRAM을 4개 쌓은 2Gb 대용량의 DRAM 적층칩과 4GB(기가바이트) 모듈로서 WSP 기술은 기존 패키지 방식인 MCP에 비해 패키지 사이즈 소형화, 용량과 속도, 소비전력 등 성능 대폭 개선의 최첨단 복합 칩이다.

WSP는 칩을 수직 관통하는 홀(Hole)을 통해 칩끼리 직접 접속하는 패키지 방식으로 칩 상하 간 별도의 간격이나 와이어 연결을 위한 공간이 필요 없어 패키지 크기 축소 성능 개선형이다. 또한 삼성전자는 2006년 4월에도 이 기술을 세계 최초로 NAND 플래시 메모리에 적용한데 이어 이번에는 DRAM에도 활용함으로써 기존 기술의 DRAM 패키지에 비해 면적은 15%, 두께는 50% 이상 감축했다. 삼성전자는 또 개발품에 웨이퍼를 박막화할 경우 발생하는 웨이퍼 휨 현상(Warpage)을 없애기 위해 2006년 11월 개발에 성공한 16단 MCP 패키지에 적용된 웨이퍼 박막화 기술을 활용하였다.

2007년 3월, 삼성이 선언한 융합반도체의 개념은 메모리+로직+소프트웨어까지를 한 개 칩에 구현한 것으로, (주)유오씨에 의하여 이미 2004년에 제시했던 UOC이다. 이것은 디지털기기의 소형화, 경량화, 슬림화, 고기능화를 견인한다는 점에서 주목할 만한데 제3세대 융합반도체에 해당되는 제품이 Flex-One NAND 이다.

제1세대 융합반도체는 MCP·SiP 등과 같이 칩과 칩을 적층하거나 한 패키지에 넣는 물리적 결합에 그친 형태이고 제2세대 융합반도체는 메모리·로직·센서·CPU·소프트웨어 등의 기능을 한 패키지에 집적하여 ‘One Package’한 것이다. 대표적인 제품이 One-NAND로서 쓰기속도가 빠른 NAND 플래시와 읽기속도가 빠른 노어플래시의 장점을 결합한 것이지만 또한 Single칩이 아닌 Single 패키지여서 진정한 융합반도체는 아니다. 최근에 출시되는 제3세대 융합반도체는 두 종류 이상의 반도체를 Single-chip 즉, 원 패키지와 달리 회로가 하나로 연결되어 있다. Flex-One NAND는 대용량 메모리인 MLC NAND 플래시·코드저장형 고속 메모리인 SLC NAND 플래시·컨트롤러와 같은 3개 칩의 기능이 회로 상에서 하나로 통합되어서 그 칩을 사용하면 휴대전화의 멀티미디어 구현에 사용됐던 4개 칩(MLC·SLC·컨트롤러·DRAM)을 단 2개(Flex One-NAND·DRAM)로 줄인다.

현존하는 메모리를 융합해 개발할 수 있는 가장 이상적인 모바일 반도체는 속도가 빠른 노어플래시와 용량이 큰 MLC NAND 플래시다. 하지만 개념적으로만 가능할 뿐 NAND와 NOR는 그 구조가 달라 각각의 컨트롤러가 필요하기 때문에 하나의 패키지로 구현할 수 있으나 Single 칩으로는 불가능하다.

2008년 8월, SK하이닉스반도체는 스위스 뉴모닉스와 차세대 낸드플래시 기술 및 제품에 대한 포괄적인 공동개발 계약을 체결하고 낸드플래시에 대한 포괄적인 공동개발을 비롯해 휴대전화용 MCP 제품에 사용되는 모바일 램에 대한 협력도 추진할 계획이다. SK하이닉스반도체는 2007년 9월, 24단 MCP의 개발에 성공하고 발표했다.

LG전자도 자체 설계한 칩을 외주하는 형태로 SiP 개발을 추진 중이다. LG측은 디지털가전의 발전 방향이 각종 통신기능 부가와 영상처리에 따른 데이터 처리량이 늘어나고 있는 추세에 따라 SiP 개발을 가속화하고 있다.

AMD 코리아도 ATI 테크놀로지스 인수를 통해 모바일기기를 위한 단독형 미디어 프로세서 설계와 제조에 있어 선두업체로 자리매김하고 있는 실정으로 2008년 5월 40개의 반도체칩 적층패키징(40Stacks CSP)의 성공사례를 발표하였다.

학계에서도 명지대학교 전자공학과 반도체공학전공 교수 및 반도체기술센터 소속 연구원들을 비롯하여 세종대학교 박주혁 교수(기계공학과 나노전자패키징연구실), 성균관대학교 정승부 교수(금속재료공학연구실), 서울산업대학교 좌성훈 교수(기계공학과 MEMS/나노공정연구실), 성균관대학교 석창성 교수(기계공학전공연구실), 충남대학교 김형일 교수(고분자공학연구실), 부산대학교 강남현 교수(재료공학과), 충북대학교 신재섭 교수(고분자화학과) 등 많은 전문 연구인들은 최근 MCP 핵심기술 연구에 박차를 가하고 있으며 ‘차세대 반도체 MCP 핵심기술 개발’의 연구노력을 경주하고 있다.

명지대학교 전자공학과 지능형 마이크로전자연구실(홍상진 교수) 및 나노전자연구실(조일환 교수)을 비롯하여 반도체 기술센터 소속 연구원은 최근 MCP 기술의 핵심요소에 속하는 ‘구리도금 주석 범프(CPTB) 제작과 특성 분석 연구’와 또한 이를 제작기술 측면에서 뒷받침해 줄 수 있는 ‘구리도금 기술 및 도금액 관리 실시간 모니터링 기술’을 상호 공동협력 관계를 유지하며 다수의 연구논문, 특허등록 등 높은 성과의 연구결과들을 발표하고 있다.

이와 관련하여 최근 대학가를 중심으로 이뤄지고 있는 ‘반도체공정진단’ 산학협력활동 사례를 살펴보면 지난 2007년 8월에 삼성전자, SK하이닉스를 비롯하여 표준과학기술원을 중심으로 “반도체 공정진단기술교류회(www.aspd.or.kr)”가 구성되어 반도체 공정진단에 대한 관심을 급부상시키고 있으며 그 활동으로 반도체 공정진단기술은 공정, 센서를 이용한 모니터링, 소프트웨어를 이용한 진단알고리즘 및 네트워크를 이용한 데이터의 실시간 전송이 주를 이루며 최근 산업자원부에서는 전략기술 개발사업 중 “차세대 반도체 장비용 진공공정 원천기술 개발”의 제목으로 대규모 국책과제가 추진되고 있으며 과제의 핵심이 공정모니터링 및 진단에 관한 내용이 주를 이루고 있고 앞에서 언급한 반도체 공정진단기술은 주로 진공공정 또는 플라즈마를 이용한 공정에 초점이 맞춰져 있으나 화학공정은 제외되어 화학공정을 정확히 모니터링 할 수 있는 센서기술의 부족 요인에서 기인하고 있는 점을 고려하여 문제의식과 함께 그 대안 마련에 노력하고 있다.

2. 해외

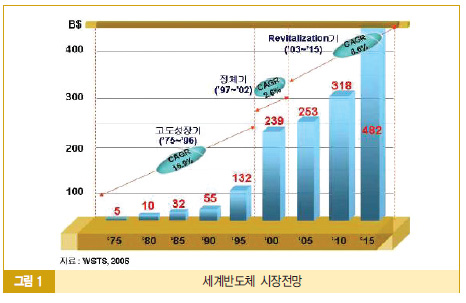

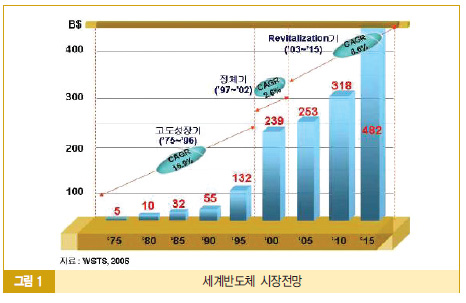

WSTS는 세계 반도체시장은 1977년부터 1996년까지는 컴퓨터의 급속한 발전과 함께 S/W가 고성능의 컴퓨터를 요구하여 빠른 속도로 컴퓨터가 교체되면서 고도성장을 구가하였으나 1997년부터는 전 세계적으로 몰아닥친 경기침체와 S/W가 고성능의 컴퓨터 사양의 요구가 작아지면서 연간 2.6% 내외의 성장을 이룬 시장 정체기가 되었고 2003년 이후는 휴대전화를 중심으로 한 모바일 제품, 각종 디지털 가전의 시장 확대로 반도체 산업의 제2 부흥기가 될 것으로 발표한 바 있다(그림 1 참조).

가. 미국

미국의 경우 대학 간의 협력 연구프로그램인 MURI(Multi-disciplinary University Research Initiative)와 DARPA (Defense Advanced Research Projects Agency), ONR(Office of Naval Research) 등 정부지원 연구프로그램에서 마이크로 열전냉각기술을 중요한 연구과제로 선정하여 진행하고 있으며 현재 박막 형태로 ZT=2.4의 장치개발을 발표한 바 있다. 또한 일본의 동경대와 독일의 MicroPelt社와 대학을 중심으로 기초 연구가 이루어지고 있다.

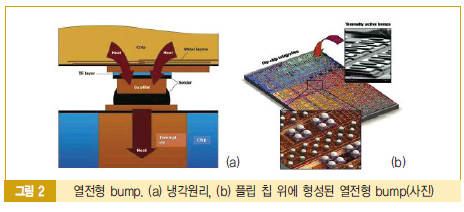

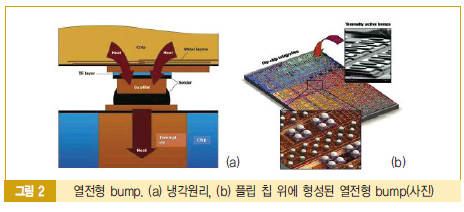

미국의 Nextreme社에는 박막형 열전소재를 이용한 전자패키지 냉각기술을 개발하고 있으며 그림 2와 같이 기존의 CPB(Copper Pillar Bump)에 박막형 열전소재를 융합한 새로운 패키지 냉각기술을 발표하였다.

미국의 텍사스유니버시티 미세전자연구센터(Microelectronics Research Center, The University of Texas at Austin, Austin, TX 78758)의 Yiwei Wang, Kuan H. Lu, Jay Im and Paul S. Ho 등은 최근 발표한 연구논문 ‘Reliability of Cu Pillar Bumps for Flip-Chip Packages with Ultra Low-k Dielectrics’, (2010 Electronic Components and Technology Conference, IEEE, pp. 1404-1410)에서 Cu/low k의 Cu pillar bump를 Sn-Ag팁을 갖는 접촉구조로 제작하여 무연 Sn-Ag solder bump와 비교하여 보고한 바 있다.

나. 독일

독일의 Fraunhofer 연구소에서는 반도체 및 각종 센서, 의료용 분석장비 등에 사용될 수 있는 미소열전소자를 개발하여 보고 하였으며 이 소자는 그림 3과 같이 웨이퍼에 대량으로 제조할 수 있으며 기존의 열전소자에 비하여 매우 작은 크기의 구성이 가능한 미세구조물 형태이다.

Micro-channel을 이용하는 냉각방식은 IBM을 중심으로 마이크로프로세서의 냉각에 사용되며 유체 순환장치를 필요로 하기 때문에 초소형/휴대용 전자제품에는 적용되기에 어려운 면이 있다. 반면에 열전형 bump를 이용한 냉각기술은 초소형으로 냉각시스템을 구성하는 것이 가능하므로 고집적 다기능 휴대용 전자제품의 냉각방식으로 매우 유망할 것으로 전망된다.

고집적 칩의 냉각에 적용될 수 있는 미세열전소자 기술은 다양하게 개발되어 왔으며 그림 4와 같이 5가지의 대표적인 기술이 있다. 차세대 3차원 적층형 패키지에서는 Microchannel을 이용하여 액체나 공기를 순환시켜서 냉각시키는 방식과 열전(thermoelectric cooling)형 bump를 이용하는 방식이 가장 유망할 것으로 보인다(출처: Yole, 2008).

다. 대만

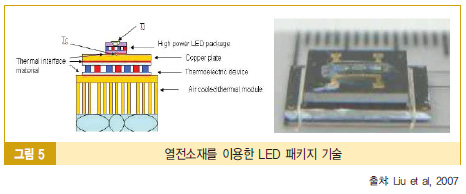

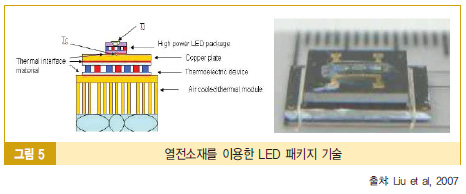

대만의 연구자들은 LED(Light-Emitting-Diode) 패키지용으로 열전소재를 활용하였으며 그림 5와 같은 구조를 통하여 LED를 효과적으로 냉각할 수 있다는 연구결과를 발표하였다(출처: Liu et al, 2007).

라. 기타

그 외의 CPTB의 응용기술로써 플립칩 패키징의 향상된 성능 신뢰성과 소형화 능력 그리고 무연(leadless)화 규제 준수로 인한 IC 조립 및 테스트 서비스(SATS) 제공업체인 Advanced Interconnect Technology(AIT)社는 AIT의 리드프레임 기반 패키지에 그 기술, 특히 QFN(quad flat no-lead) 방식을 채용하기 위해 Advanpack Solutions사와 라이선스 계약을 체결한 사례를 들 수 있으며 미국의 Texas Instrument社에서 발표된 자료(2007년10월)에 의하면 NIR(near infrared) 스펙트로미터를 통해 물과 희석된 불산(diluted hydrofluoric acid)의 성분함량 모니터링 기술이 발표되었다.

불산(HF)은 반도체공정 시에 SiO2 제거용도로 흔히 ~5%가 사용되며 HF의 함량에 따라 산화막 습식 에칭속도가 다르므로 그 함량 실시간모니터링을 위한 기술이다. NIR을 사용하여 반도체공정 모니터링이 시도되고 있는 영역은 다수 있지만 패키징 배선공정 모니터링의 구체적인 기술은 아직 없으며 더구나 RGB 센서를 이용한 기술은 전무하다. 고가의 NIR 센서보다는 저가의 RGB 센서를 활용하는 진단알고리즘을 탑재한 모니터링 및 진단 시스템이 개발되면 고부가가치의 제품생산뿐만 아니라 국제경쟁력 확보에도 큰 파급효과가 기대되는 기술이다.

결 론

본 연구과제는 대학공동연구 활동의 일환으로 고집적 패키징 기술에 바탕공정으로 사용되는 구리도금-막 제작 기술을 통하여 구리기둥 범프의 제작과 신뢰성 개선을 위한 측벽 산화방지용 주석도금층의 활용 방안을 구현하였다. 구리기둥 주석 범프(CPTB) 제작에서 소자의 산소환경 노출의 위험을 방지하는 self-protect 기능의 소자구현 방안을 강구하였다.

고집적 패키징 기술에서 CPTB 제작공정은 매우 유용한 기술이며 날로 진보되어 집적도 및 특성 향상과 전자기기의 소형화에 크게 기여하고 있다. 또한 CPTB 제작공정에서 구리도금은 핵심기술 중의 하나로서 특성과 집적도 향상에 크게 영향을 미친다.

제안된 전류제어차단-막(insulating gate) 구조의 구리도금 조에서 도금전류는 center hole을 통하여 가까운 직선거리 위치에 있는 웨이퍼의 중심부에 고밀도 전류를 흐르게 한다. 그 결과 도금 층 두께는 중심부가 크게 되어야 한다. 하지만 도금의 결과는 중심부와 가장자리 부근의 두께 차이를 현저히 완화시키는 것으로 나타났다. 이것은 전류제어차단-막이 없을 경우에 가장자리 부근의 edge effect 등으로 도금 층 두께가 크게 형성되던 현상이 완화되어 나타난 효과로 분석된다. 그러므로 구리도금 층이 원활하게 이루어질 때 후속공정 기술도 향상될 수 있다. 도금 층 균일화 모색을 위한 방안으로 insulating gate 역할의 전로제어차단-막 기법을 제안, 구현하였고 전로제어차단 효과를 실험을 통하여 확인하였다. 따라서 CPTB 제작공정에 기여하는 구리도금 기술과 그에 따른 구리도금 층 균일화를 위한 제안기술의 적극적인 개발 노력을 지속함으로써 insulating gate 역할의 전로제어차단-막 기법이 유용하게 적용될 수 있을 것으로 기대된다.