RRAM에서 selector 기술은 저항변화 물질 기술이 확보된 이후에 연구가 되기 시작하였다. 저항변화 물질은 대학과 연구소에서 중점적으로 연구가 많이 이뤄진데 비해 selector 기술은 RRAM을 양산하기 위한 기업을 중심으로 이루어지고 있어 구체적인 물질에 대한 정보는 기업의 기밀로 남겨져 있다. RRAM의 3D 구조 개발에 대한 요구가 분명하며, 따라서 ALD를 이용한 신뢰성 있는 저항변화 물질 개발에 대한 연구는 지속적으로 이루어질 것으로 예상된다. 또한, 아직 많은 연구가 이루어지지는 않고 있지만, 저항변화 물질 뿐만 아니라 selector 물질도 ALD 기술을 통해 형성되어야할 필요가 있으며, 이에 대한 연구도 활발하게 이루어질 것으로 예상된다.

RRAM의 Selector 기술 연구동향

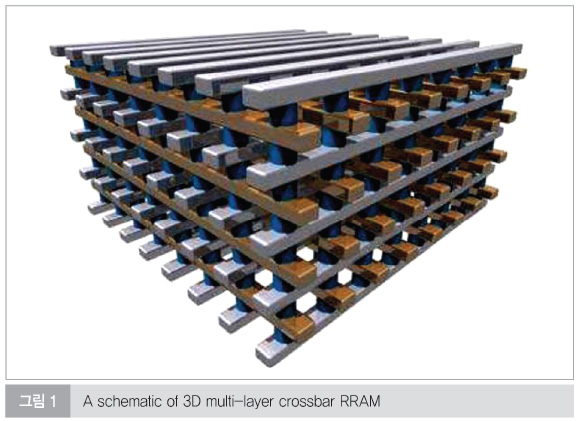

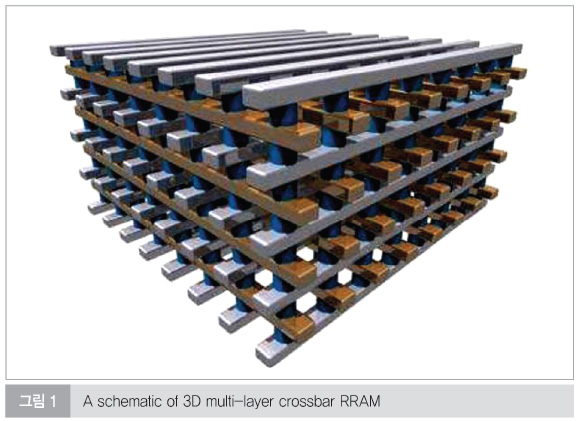

RRAM의 가장 큰 장점은 2개의 access line 만으로 소자를 구현할 수 있어 소자의 집적도를 최대화할 수 있는 crossbar 구조 구현이 가능하다는 점이다. 이 crossbar 구조는 3차원적인 다층 적층도 가능하여 초고밀도의 기록매체로 매우 높은 가능성을 갖고 있다. 그림 1은 3차원 crossbar 구조의 RRAM 모식도를 보여준다.

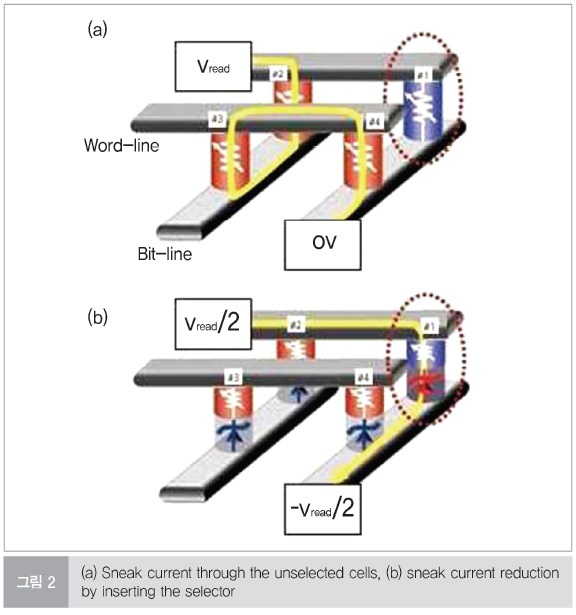

다만 DRAM과 flash memory에는 transistor가 있어 임의의 cell을 독립적으로 access하는데 문제가 없는 반면, crossbar 구조에서는 하나의 access line에 여러 개의 cell이 연결되게 되고, 이들 이웃한 cell로부터의 의도치 않은 누설 전류(sneak current)가 발생하게 된다. RRAM도 기존의 memory와 같은 방식으로 cell마다 transistor를 연결해 구성하는 것이 가능하지만 이 경우 RRAM의 장점을 잃게 되어 기존의 memory에 비해 큰 장점을 갖지 못하게 되고, 따라서 RRAM에서의 sneak current를 해결하는 문제는 매우 중요하다.

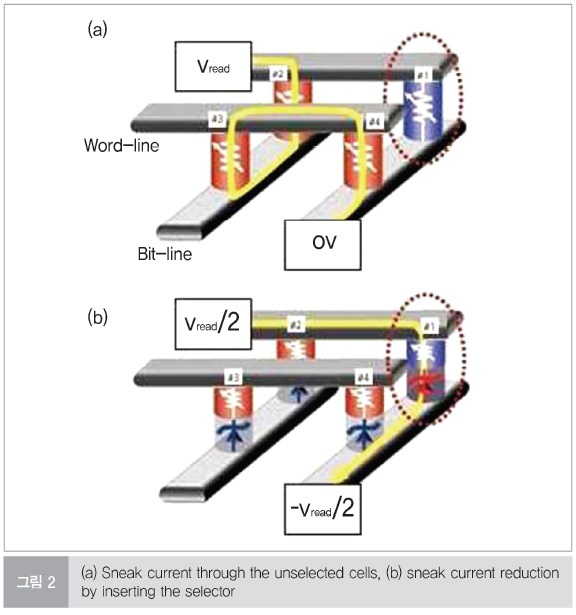

이 문제를 해결하기 위하여 cell 내부에 저항변화 물질과 함께 selector 물질을 넣는 방법이 제시되었다. 그림 2의 (a)는 unselected cell(red cells)로부터의 sneak current(yellow line)가 selected cell(blue cell)로부터의 sensing current에 간섭을 주는 것을 보여주고 있으며, (b)는 selector를 삽입함으로써, sneak current가 억제되고 selected cell의 전류를 간섭 없이 sensing할 수 있음을 보여준다. Crossbar 구조에서 selected cell에 읽기나 쓰기시 V의 전압이 걸린다고 하면, un-selected cell에는 ½ V 이하의 전압이 인가되게 된다. Selector 물질은 V의 전압에서는 저항이 매우 작지만, ½ V 이하의 전압에서는 저항이 매우 큰 비선형적인 IV 특성을 갖는 물질을 통칭하며, threshold switch, oxide tunneling barrier, mixed ion-electron conductor 등의 메커니즘이 알려져 있다.

수년전만 해도 RRAM을 제품화 하는데 있어 가장 큰 기술 장벽이 저항변화 재료로 여겨졌으나, TaOx와 HfOx를 중심으로 하는 저항변화 재료의 혁신이 일어나 저항변화 재료의 신뢰성에 대한 큰 장벽이 무너진 이후로는 RRAM 재료에 대한 초점이 selector 물질로 기술의 개발로 옮겨 온 상황이다. 본고에서는 다양한 selector 기술에 대해 알아보고, selector 물질의 최신 동향에 대해 알아보고자 한다.

RRAM의 최신 selector 기술

Crossbar 구조에서 selector 물질에 대한 요구가 생긴 이후 다양한 방식의 selector 물질이 제안되었다. 본 단원에서는 대표적인 RRAM 기업에서 발표한 selector 기술의 동향을 요약해보고자 한다.

a. Samsung의 OTS

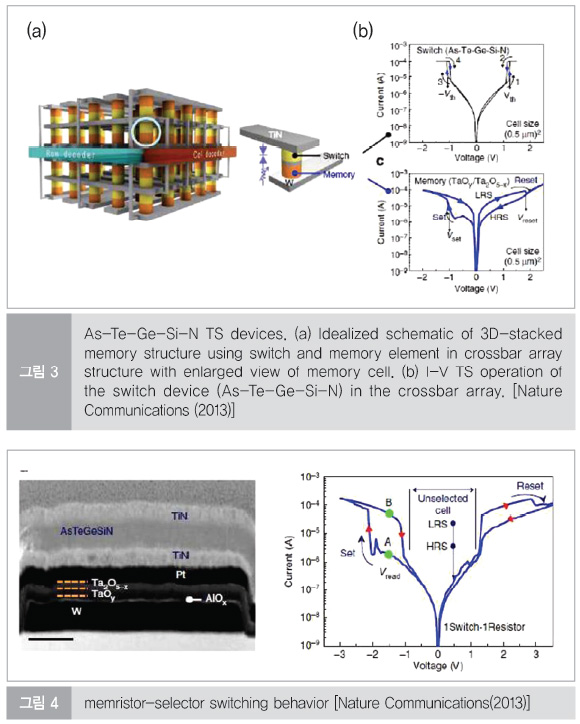

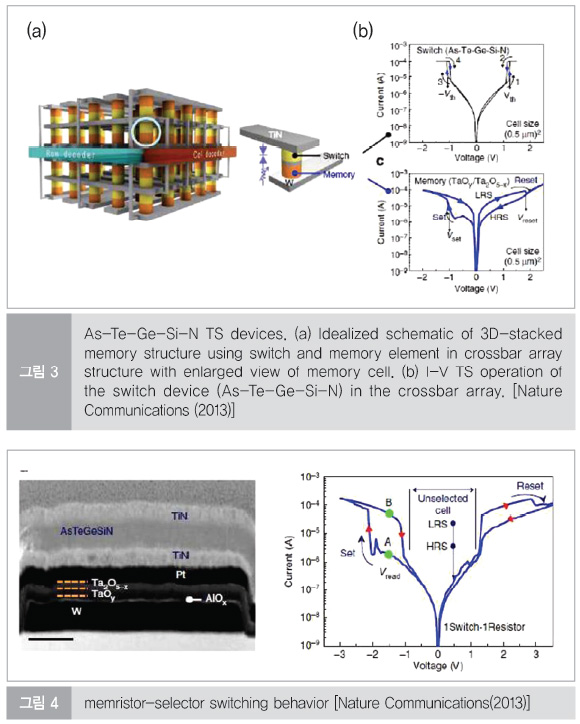

Samsung에서는 ovonyx threshold switch(OTS) 라고 불리는 chalcogenide 물질의 공정과 조성비를 최적화하여 안정적인 switch 물질을 개발하였다. 이 switch 소자는 30nm 크기의 cell size에서 2ns의 switching speed를 보이는 매우 우수한 특성을 보임을 주장하였다. 그림 3은 Samsung이 발표한 OTS의 switch 특성을 보여준다.

또한 selector와 memristor를 하나의 소자로 구현하여 실제로 1S1R(1 selector + 1 resistance switching material)에서의 RRAM 동작을 확인하였다(그림 4). 이 경우 3V 정도의 동작 전압에서 on/off 상태의 저항비가 ~100 정도가 확보되었다.

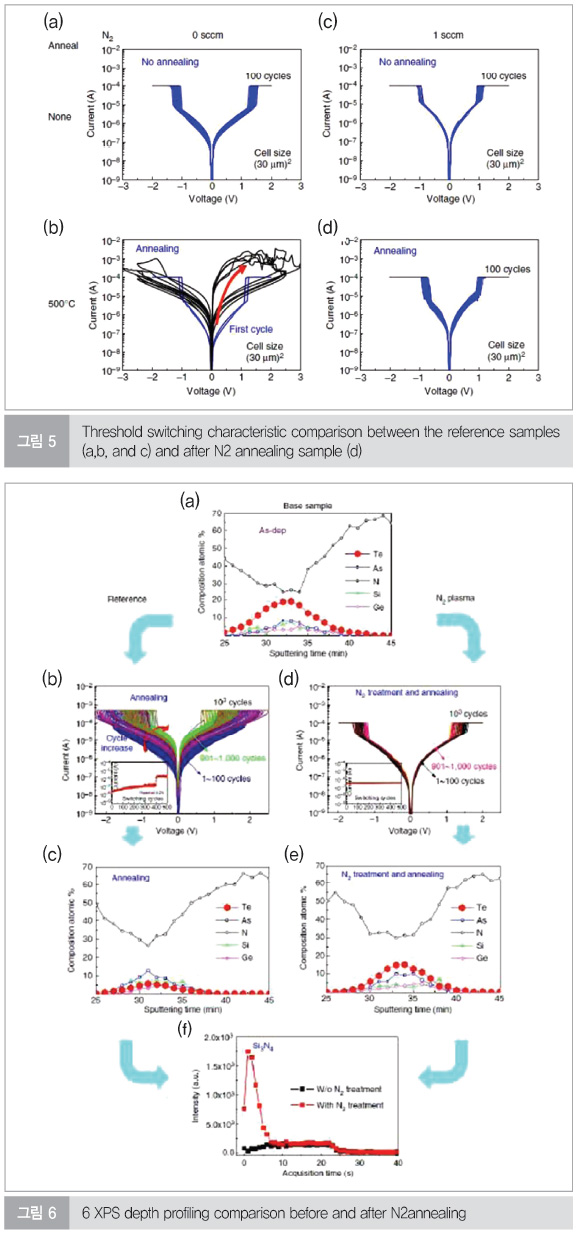

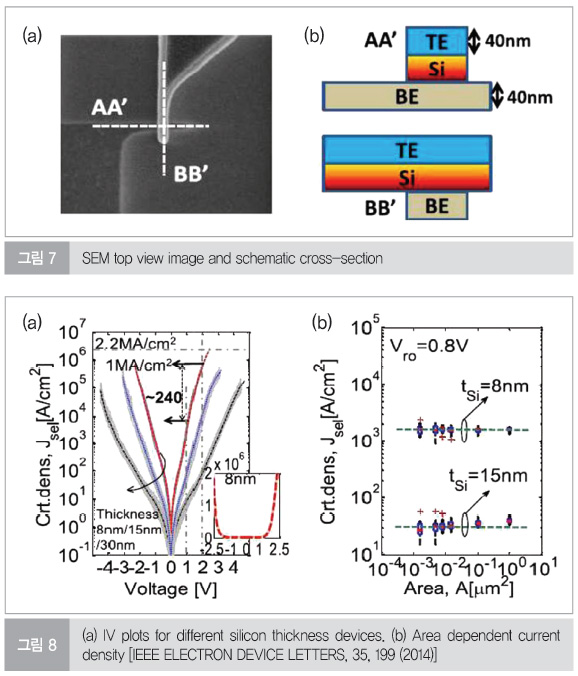

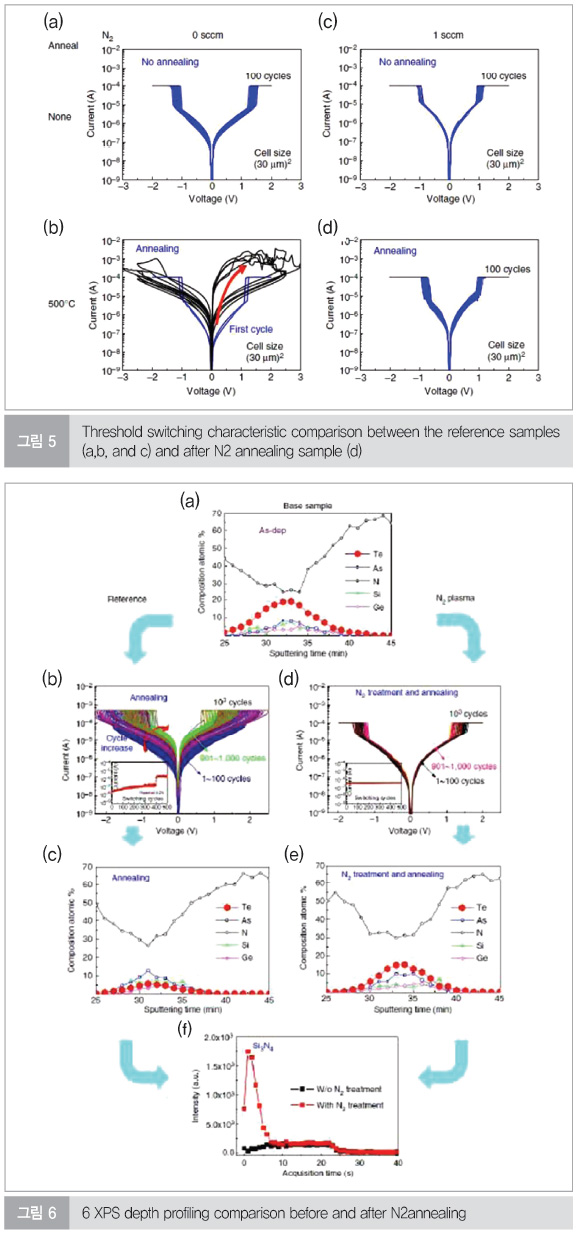

OTS의 threshold switching 특성은 Samsung의 발표 이전에도 이미 잘 알려져 있었지만, 물질의 신뢰성에 문제가 있는 것으로 알려져 있었다. Samsung에서는 OTS의 특성이 열화되는 이유를 밝혀내고, N2annealing을 통해 이러한 신뢰성 문제를 해결하였다고 보고하였다. 그림 5는 N2gasannealing 전·후의 switch 특성을 보여주고 있으며, 그림 6의 OTS 소자가 열화되기 전·후의 XPS depth profile 분석 결과를 보여준다. 분석 결과를 통해 OTS 소자가 열화되는 이유가 박막 내의 Te의 휘발성 특성 때문임을 알 수 있다. 여기에 N2annealing을 진행하면 N2gas가 박막 내의 Si과 반응하여 표면에 Si3N4를 형성하며, 이 Si3N5layer가 Te의 휘발을 막아주어 switch 특성의 열화가 일어나지 않는 것임을 보였다.

OTS 물질은 우수하고 안정적인 switch 특성을 갖고 있으나, As-Te-Ge-Si-N로 이루어진 glass 물질로 조성이 매우 복잡하여 실제로 이 물질이 반도체 공정에서 적용될 수 있을지는 의문시 된다. 또한 OTS 물질의 동작 전류는 ~mA 정도로 매우 높은 편인데, Samsung이 개발하고자 하는 flash memory向의 RRAM은 동작 전류가 매우 낮아야 하기 때문에 OTS 물질이 Samsung의 전략과 일치하지는 않는 것으로 보인다. 즉, OTS 물질 자체의 switch 특성은 매우 우수하지만, 동작 전류의 한계와 공정 용이성 등의 문제를 극복하지 못한다면 제품에 적용될 가능성은 낮을 것으로 판단된다.

b. IMEC

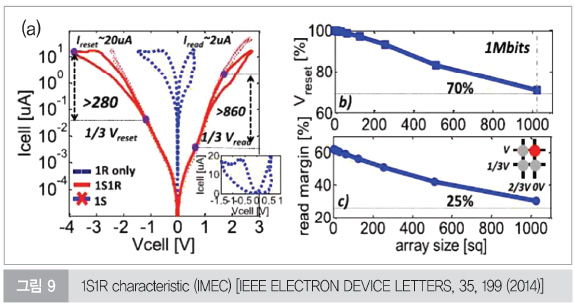

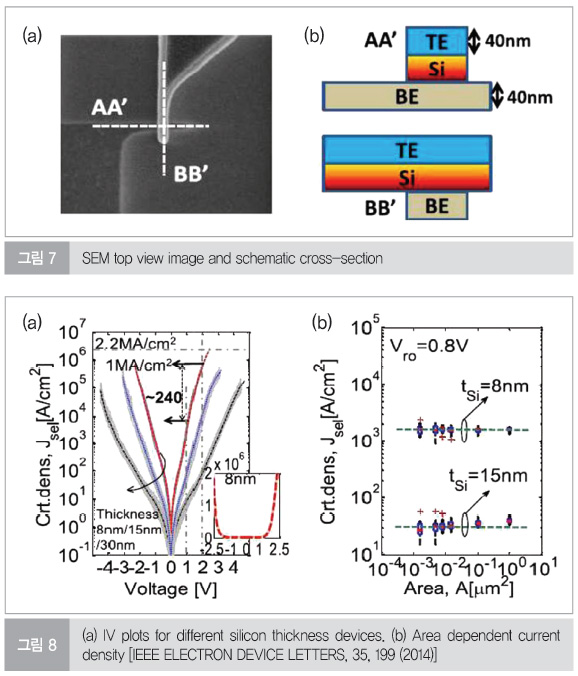

IMEC에서는 Metal/Amorphous-Silicon/Metal Diode 형태의 nonlinear IV 형 selector를 개발하여 발표하였다. 이 diode형 selector는 최소 40nm 크기에서 2.2MA/㎠의 고전류 밀도를 허용할 수 있고, 1ns 이하의 switching speed를 갖으며, 108이상의 endurnace를 보이는 것으로 보고하였다. 그림 7은 소자의 image이며, 그림 8은 selector 소자의 특성을 보여준다.

IMEC이 발표한 selector는 a-Si의 두께를 조절하여 current density와 nonlinearity 특성, 즉 비선형성의 정도 특성을 조절할 수 있어 RRAM의 용도에 따라 유연하게 조절하여 폭넓게 쓰일 수 있다는 장점이 있다.

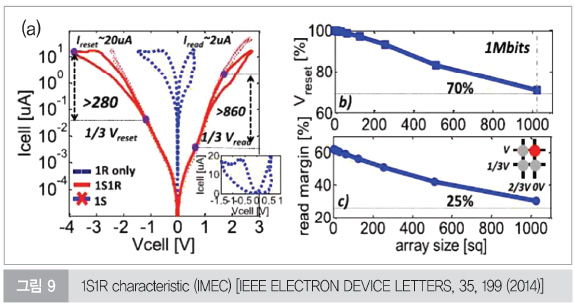

IMEC에서는 추가로 selector에 저항변화 물질을 연결한 1S1R의 결과를 보고하여 약 1Mb 정도의 array 크기에서 25% 이상의 read margin과 75% 이상의 write margin을 가질 수 있을 것으로 예측하였다(그림 9). 이러한 nonlinear 한 형태의 selector는 물질 자체의 conduction 특성을 이용하기 때문에 switching 중에 물질 내부의 변화를 수반하지 않는다. 따라서 신뢰성 측면에서는 가장 우수하다고 할 수 있다. 또한 물질 구조도 매우 간단하여 CMOS 공정에서 구현하는데 있어 용이하다는 장점이 있다. 하지만 앞서 언급한 Samsung의 OTS와 같은 threshold switch에 비해 switch 자체의 동작을 위한 전압이 크기 때문에 소자 전체의 동작 전압이 증가한다는 단점이 있으며, 또한 nonlinearity가 상대적으로 작아 고밀도를 구현하는데 있어 부적절할 것으로 판단된다.

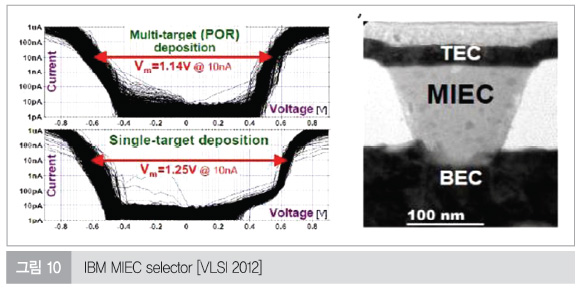

c. IBM

IBM은 2012년 Mixed Ionic Electronic Conduction(MIEC)이라는 이름의 selector를 발표하였다. IBM에서는 이 기술을 PRAM에 적용한다고 알려져 있으나, selector 기술은 PRAM과 RRAM에 공통적으로 적용될 수 있다는 점에서 RRAM에서도 MIEC가 매우 우수한 selector로 기대되고 있다.

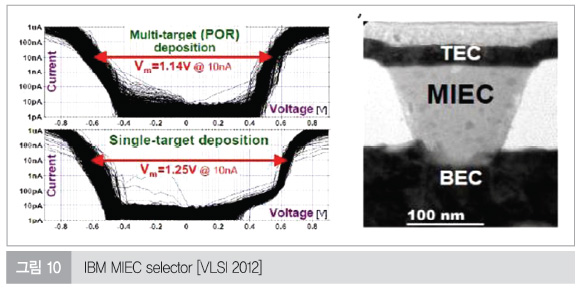

IBM의 MIEC selector는 512 × 1024 크기의 array에 CD(critical dimension) < 35nm의 구조로 만들어졌으며, 100%의 수율을 보임을 강조하였다. 또한 동작 전압이 1V 이하로 매우 작고, 105이상의 nonlinearity 특성을 갖고 있어 Samsung의 OTS와 IMEC의 selector에 비해 우수한 특성을 갖고 있다고 할 수 있다. 이 selector의 leakage current는 <10pA 이하로 이 역시 매우 우수하다. 또한 공정적으로도 single target sputtering을 통해 만든 것으로 보고하여 공정이 용이함을 강조하고 있다. 그림 10은 MIEC selector의 구조와 특성을 보여준다.

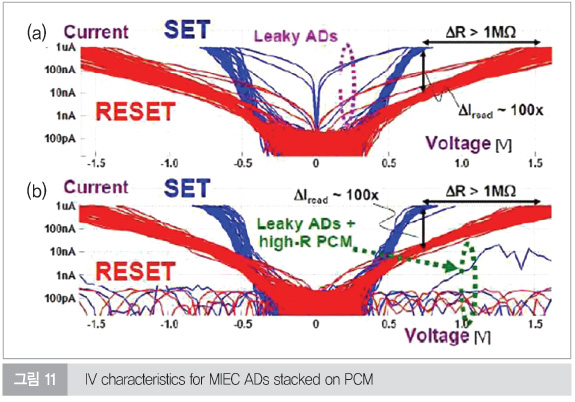

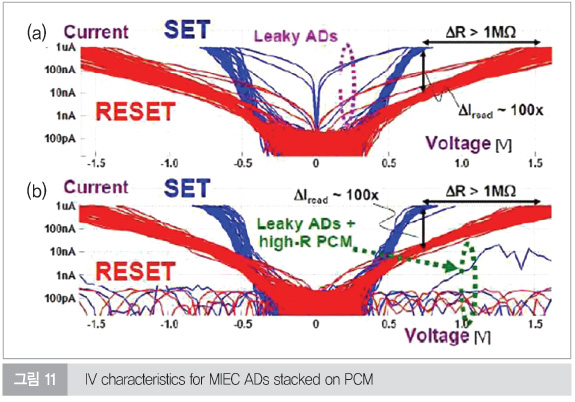

MIEC의 상세한 물질 정보는 공개하지 않았으나, Cu ion이 핵심적으로 selector 동작에 관여하는 것으로 알려졌다. 그림 11은 MIEC와 PRAM이 연결된 구조에서의 MIEC selector의 특성을 보여준다.

IBM은 자체적으로 PRAM 개발을 위해 많은 노력을 쏟은 만큼 MIEC 기술도 상당한 노하우가 축적된 우수한 결과라고 볼 수 있다. 또한 실제 양산을 위한 기술을 개발 중이라는 점에서 앞선 Samsung과 IMEC의 기술과 차별화 된다고 볼 수 있고, 실제 제품에 적용될 가능성이 높을 것으로 판단된다.

d. Crossbar社의 Field Assisted Superlinear Threshold (FAST) Selector

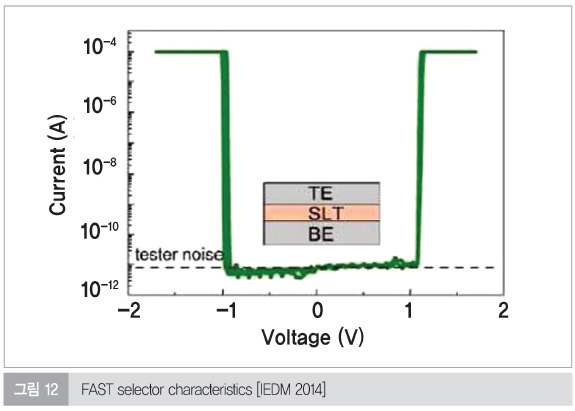

Crossbar社는 자체적인 기술로 Field Assisted Superlinear Threshold(FAST)라는 이름으로 현재까지 알려진 가장 획기적인 특성의 selector 기술을 발표하였다.

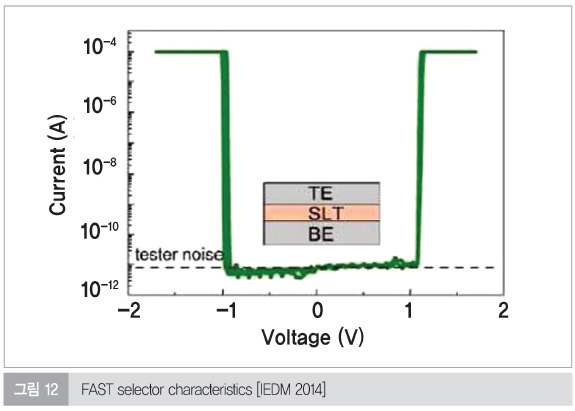

그림 12는 FAST selector의 특성을 보여주는데 switch가 off 된 상태와 on 된 상태에서의 전류비가 >106이상임을 발표하였다. 또한 switching slope < 5mV/dec, selectivity >1010, 50ns 이하의 동작 속도, >100M의 endurance, 300℃ 이하의 공정 온도 등의 장점을 발표하였고, 4Mb size의 crossbar array에서 sneak current가 0.1nA 이하임을 측정하였다.

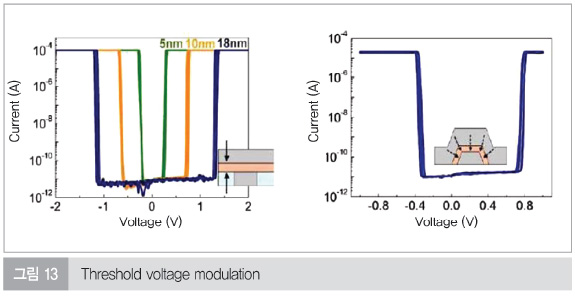

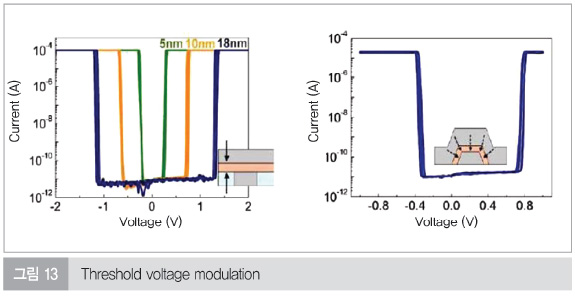

더 나아가 우수한 switch 특성뿐만 아니라, switch 물질의 두께와 전극의 구조를 조절하여 switch의 turn on 전압을 조절할 수 있음을 보여주었는데, 이는 RRAM의 읽기/쓰기 전압을 원하는 데로 조절할 수 있음을 의미하여 RRAM을 효과적으로 설계할 수 있게 해주는 장점이 있다. 그림 13은 switch layer의 두께와 구조에 따른 threshold voltage의 변화를 보여준다.

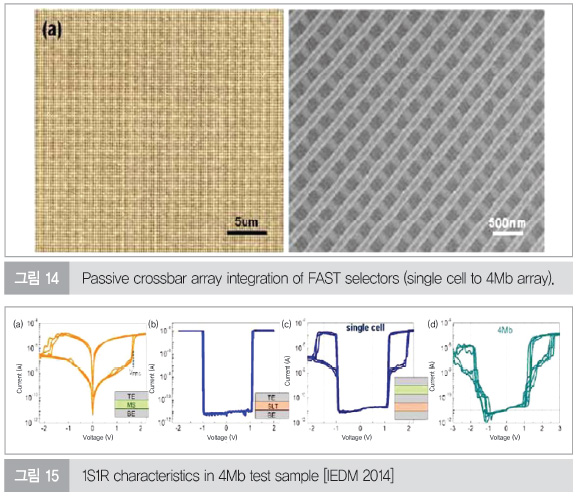

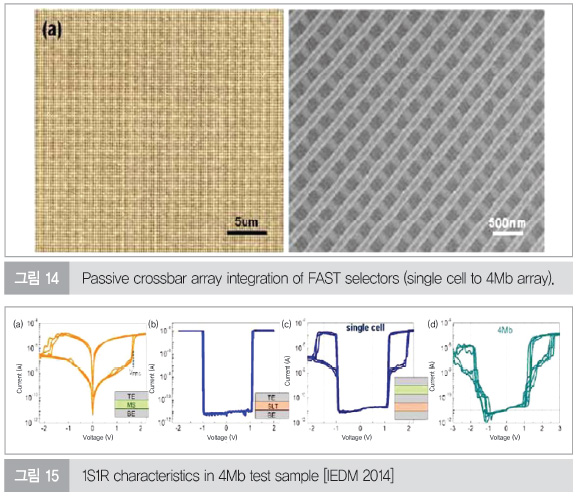

또한 4Mb size의 array에 1S1R이 집적된 소자를 개발하여 특성을 확보하였다. 그림 14는 4Mb size의 crossbar array image를 보여주며, 그림 15는 1S1R 특성을 보여준다. 1S1R 집적 후에도 매우 안정적으로 동작이 가능함을 보여준다.

결론

RRAM에서 selector 기술은 저항변화 물질 기술이 확보된 이후에 연구가 되기 시작하였다(저항변화 물질이 성공적으로 개발되지 못했다면 selector 물질은 연구가 시작되지도 않았을 것이다). 저항변화 물질은 대학과 연구소에서 중점적으로 연구가 많이 이뤄진데 비해 selector 기술은 RRAM을 양산하기 위한 기업을 중심으로 이루어지고 있어 구체적인 물질에 대한 정보는 기업의 기밀로 남겨져 있다.

비록 기업들이 함구하고 있긴 하지만 최근의 우수한 결과들을 보면, 양이온의 휘발성 전도성 특성을 이용하는 것이 핵심으로 보인다. 즉, 일정한 전압이 가해지면 양이온이 전도성 통로를 형성하여 전류가 급격히 증가하고, 전압을 제거하면 양이온 통로가 자연스럽게 소멸하는 원리이다. 이러한 selector 의 동작 원리에 대한 암묵적 합의가 이루어진 이상 차후에는 selector 기술도 급격한 진전이 있을 것으로 기대된다.

RRAM의 ALD 기술 연구동향

최근 double patterning 등 lithograph 기술의 지속적인 발전과 3차원 vertical 공정 기술의 혁신, multi-bit operation을 위한 data processing 및 error correction code(ECC)의 최적화 등을 통해 flash memory의 기술은 급속히 발전 중이다.

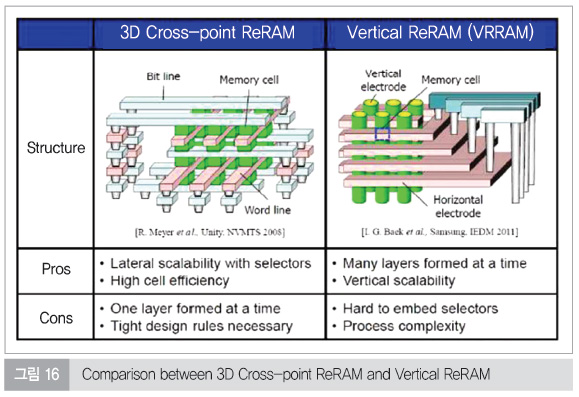

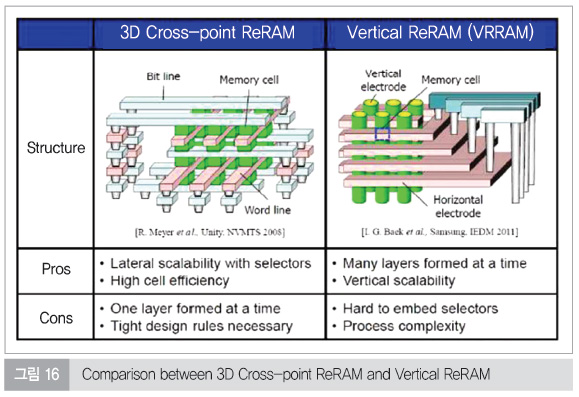

Samsung은 2014년 32단 3 bit의 multi-level cell flash memory를 개발하여 발표하며 flash memory 시장을 이끌고 있다. 하지만 flash memory의 경우에도 WL-WL 간의 leakage current 문제와 인접한 cell 간의 coupling 문제, cell size 감소에 따른 저장된 전하량 감소의 문제 등으로 인해 scaling에 대한 한계가 지속적으로 제기되고 있다. 물질 내부의 이온의 움직임에 따른 저항변화 현상을 이용하는 RRAM은 원리상 근본적으로 전하를 축적해 데이터를 저장하는 flash memory가 갖고 있는 이러한 문제들을 갖지 않기 때문에 scaling에 대한 한계가 상대적으로 적고, 따라서 향후 flash memory를 대체할 후보로 각광받고 있다. 그리고 flash memory 이상의 data 저장 밀도를 달성하기 위해서는 planar 다층 구조보다는 vertical 구조의 RRAM(VRRAM)이 적합할 것으로 예측된다. 그림 16은 RRAM에서 평판다층적층구조(3D Cross-point ReRAM)와 수직형다층구조(Vertical ReRAM) 기술의 차이를 간단히 보여준다. VRRAM은 다층이 한 번의 사진 공정을 통해 형성될 수 있어, 적층구조에 비해, layer의 수가 늘어날수록 비용 측면에서 장점을 갖는다.

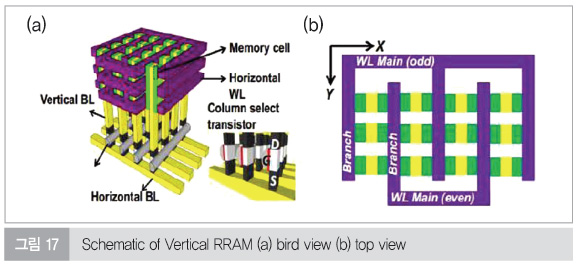

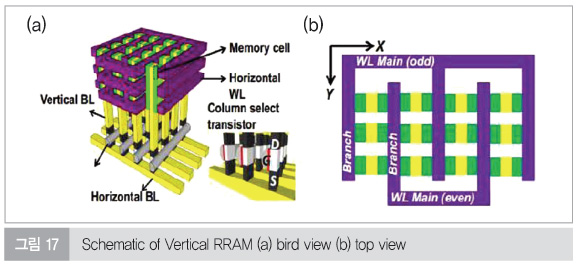

이러한 VRRAM이 구현되기 위해서는 그림 17과 같이 RRAM 물질이 다층의 금속 전극의 측벽에 형성되어야 하며, 이를 위해서는 ALD 공정이 필수적이다.

그럼에도 불구하고 ALD 공정을 통해 고신뢰성의 RRAM 물질을 만드는 것은 쉽지 않은 문제이다. RRAM은 원리적으로 박막 내에 존재하는 산소 이온(혹은 금속 양이온)의 움직임을 이용한다. 이 산소 이온은 박막의 결함으로 부터 형성되고 따라서 RRAM에 쓰이는 물질은 기본적으로 많은 결함을 포함하고 있어야 하며 또한 결함의 농도도 조절될 수 있어야 한다. 하지만 ALD 공정의 경우 박막이 성장하는 동안 reactant 간에 saturation reaction이 일어나기 때문에, 박막 내에 intrinsic한 산소 결함을 만들거나 조절하는 것이 어렵고 이 점 때문에 RRAM에 활용되기가 쉽지 않다. 이를 위해 현재 보고되고 있는 대부분의 신뢰성 있는 RRAM의 핵심 박막 공정은 대부분 PVD로 이루어지고 있다. 하지만 ALD 기술에 대한 요구가 분명한 만큼 ALD를 이용한 RRAM 물질 개발에 대한 필요성이 대두되고 있는 상황이다.

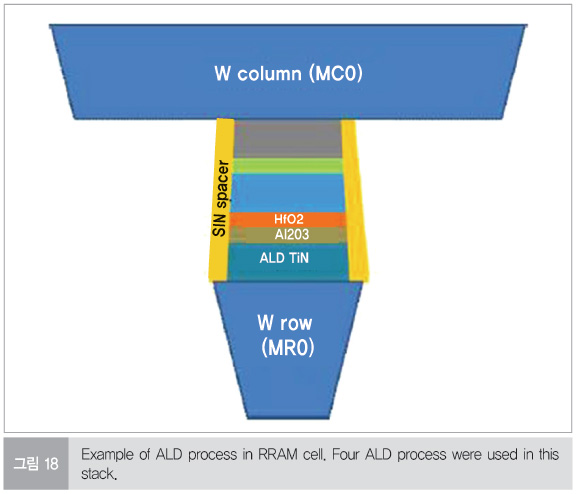

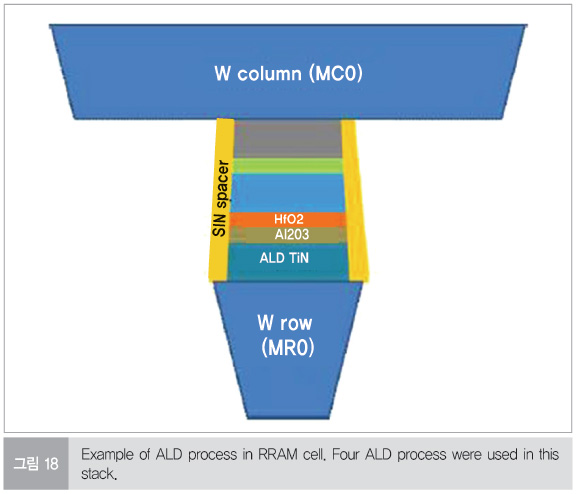

RRAM 물질 자체뿐만 아니라 RRAM cell은 저항변화층, 산소공급층, 확산방지층 등 다양한 역할의 다층의 박막으로 구성되게 되는데, 이러한 박막은 매우 얇고 균일하게 형성될 수 있어야 한다. ALD 공정은 특히 수 nm 수준의 박막을 균일하게 증착할 수 있다는 장점 때문에 특히 RRAM에서는 핵심 공정 중 하나이다.

그림 18은 RRAM의 핵심 cell의 단면 예시 도면으로, RRAM cell 자체에 4개의 서로 다른 ALD 공정이 적용되고 있음을 보여준다.

RRAM에서의 ALD 공정의 기술 개발 동향을 파악하고, 향후 기술의 전개 방향에 대해 알아보고자 한다.

ALD in RRAM

RRAM에서 ALD 공정은 저항변화 물질, 전극 물질, 산소 확산 방지막 등의 보충물질, passivation 물질 등에 적용되고 있다. 여기서는 ALD 공정을 통해 형성된 RRAM 물질이 어떤 특성을 갖고 있는지 알아보고자 한다.

앞서 간단하게 언급한 바와 같이 ALD 방법으로는 산화막 내의 산소 농도를 바꾸는 것이 쉽지 않기 때문에 RRAM에서 필요로 하는 적절한 농도의 결함을 포함하는 박막을 만드는 것이 쉽지 않다. 그럼에도 불구하고 ALD 기술을 이용한 RRAM 물질에 대한 연구가 활발히 이루어지고 있다. 특히 최근 들어 신뢰성 있는 RRAM 물질은 HfO2와 Ta2O5기반의 물질로 압축되었고, 따라서 이들에 대한 ALD 공정에 대한 연구도 활발히 이루어지고 있다.

a. ALD HfO2 RRAM

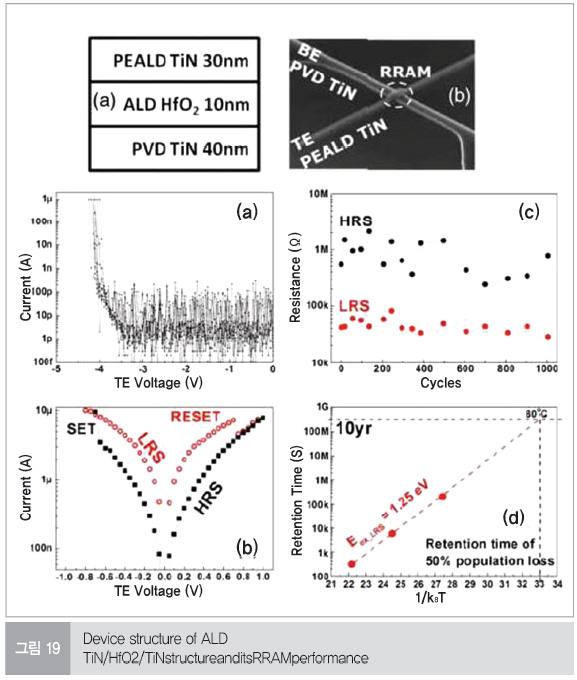

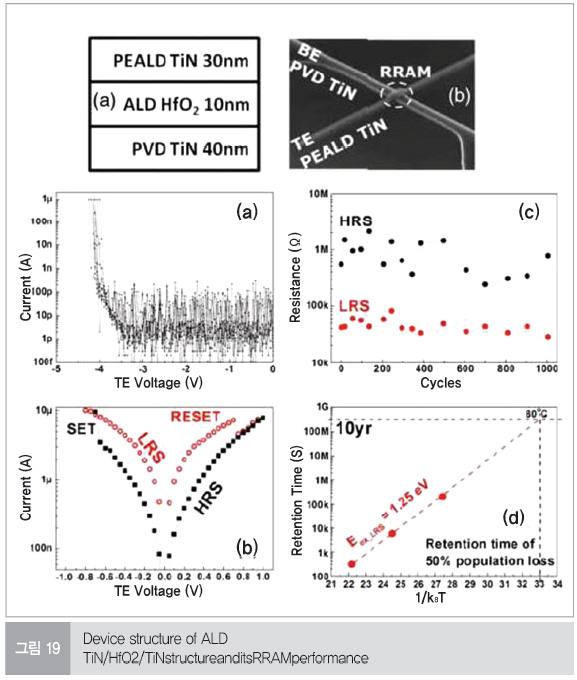

우선 HfO2는 Ta2O5와 함께 RRAM으로써 고신뢰성을 갖고 있음이 여러 연구 결과에서 보고되고 있어 RRAM에 적용될 가능성이 높은 물질이다. 그림 19는 Stanford university에서 발표한 ALD HfO2 RRAM의 구조와 특성을 보여준다. 여기서는 HfCl4와 H2O가 각각 전구체와 산화제로 사용되었고, HfO2의 두께는 10nm이며, 증착 온도는 300℃이다. 보고에 따르면 RRAM의 endurance 는 약 1000회 정도로 PVD를 통해 형성된 HfO2에 비해 RRAM으로 사용되기에는 부족한 수준이나, 전극 물질로 CMOS 공정에 호환이 가능한 TiN을 이용하였고, 45nm 크기의 contact 크기에서 소자 특성이 평가되었다는 점에서 RRAM의 ALD 기술로 큰 도약을 이룬 것으로 평가할 수 있다. 특히 본 연구에서는 전극 물질도 ALD TiN을 사용하여, RRAM cell 전체를 ALD 공정을 통해 형성할 수 있는 가능성을 보여줌으로써 향후 VRRAM에 적용될 수 있을 것으로 기대된다.

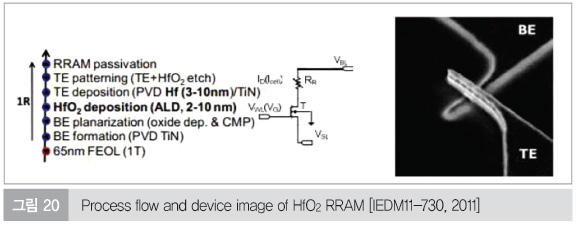

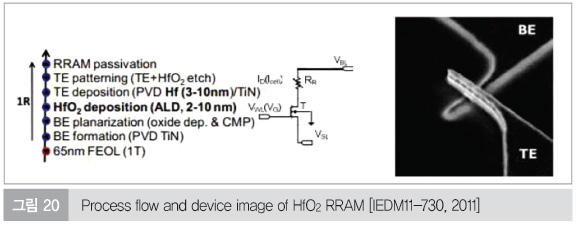

또한 IMEC에서도 ALD HfO2를 이용하여 우수한 특성의 RRAM을 발표하였다. 다음 그림 20은 IMEC이 보고한 10nm × 10nm 크기의 crossbar RRAM의 공정 순서와 device 구조를 보여준다.

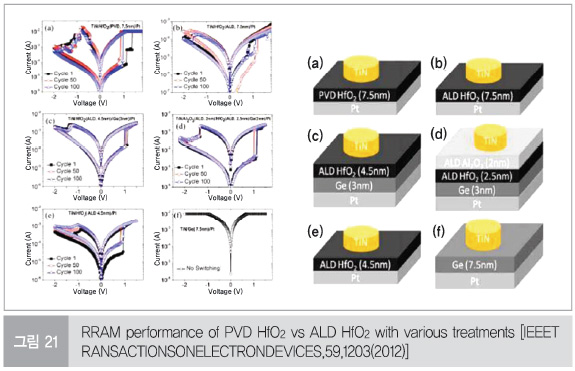

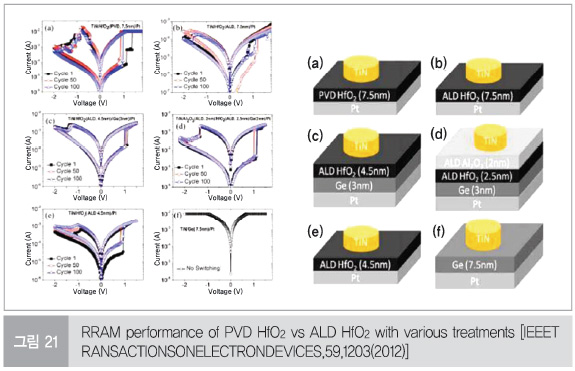

이 소자는 TiN/Hf/HfO2/TiN구조이며, Hf metal layer가 ALD HfO2를 환원시켜 산소 defect를 형성하고, 이를 통해 우수한 RRAM 특성을 갖는다고 보고하고 있다. 또한 Singapore의 Nanyang Technological University에서는 그림 21과 같이 PVD HfO2과 ALD HfO2의 RRAM 특성을 비교하여 보고하였다. 이들의 결과에 따르면 PVD HfO2는 기본적으로 우수한 RRAM 특성을 갖고 있으나, ALD HfO2는 상대적으로 좋지 않은 RRAM 특성을 갖고 있다. 하지만 HfO2 ALD 증착 전에 3nm의 Ge 층을 evaporation을 통해 증착하고 ALD HfO2 RRAM을 제작하면 PVD HfO2에 버금가는 수준의 HfO2 RRAM이 얻어지는 것을 관찰하였다. 이는 얇게 증착된 Ge이 HfO2에 doping 된 효과를 주어 HfO2 내에서 결함을 만들어 주는 역할을 하고 있음을 보여준다. 즉, ALD 방식이 갖고 있는 산소 이온 결함을 만드는데 제한적인 단점을 추가적인 layer를 삽입하여 해결할 수 있음을 보여주고 있다.

b. ALD Ta2O5 RRAM

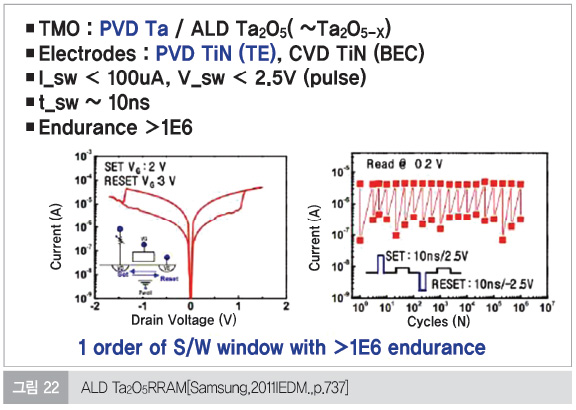

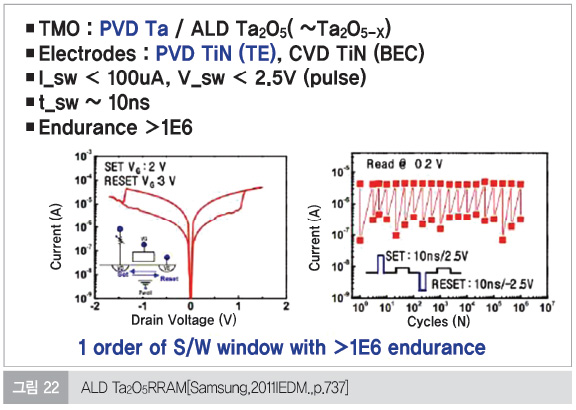

Ta2O5도 RRAM에서 가장 각광받는 물질로 PVD를 통해 증착한 TaOx/Ta2O5의 구조에서 1012회의 endurance가 측정되어 향후 RRAM에 적용될 가능성이 가장 높은 물질이다. 따라서 ALD 공정을 통해 신뢰성 있는 Ta2O5를 형성하는 것도 중요한데, 이때 어떠한 방식으로 oxygen defect를 포함하는 TaOx를 형성해야 할지가 핵심 기술이 된다. 일반적인 ALD를 통해 증착된 Ta2O5에는 oxygen defect의 농도가 충분하지 않다. 그 대표적인 방법 중의 하나는 metal Ta 층을 이용하여 ALD Ta2O5를 환원시키는 방식이다. 그림 22는 Samsung에서 이러한 방법을 이용해 형성한 RRAM의 특성을 보여준다. 이렇게 형성된 Ta/Ta2O5구조에서는 10ns의 programming speed에서 100만회 정도의 endurance를 갖고 있어 PVD를 통해 형성된 Ta2O5 RRAM에 버금가는 우수한 특성을 보이고 있다. 본 보고에서는 구체적인 박막 증착 공정은 보여주지 않고 있다.

다만 이러한 방식에서 ALD Ta2O5를 적용하긴 했지만, 금속 물질인 Ta는 PVD를 통해 형성되어 Ta 증착을 3차원 공정에 적용하는데 어려움이 있다.

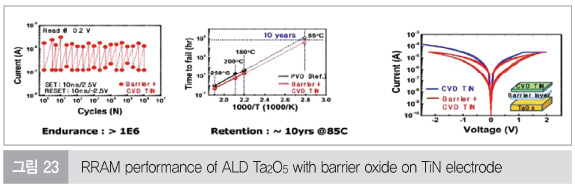

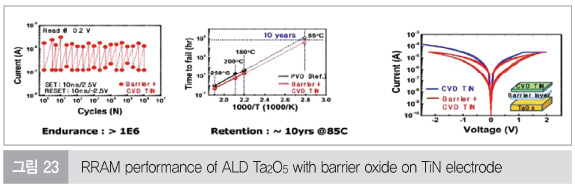

한편, Ta이 아닌 ALD로 증착이 가능한 TiN을 전극으로 쓰는 경우에는 Ta2O5의 우수한 저항변화 특성을 관찰할 수 없는데, 이는 TiN과 Ta2O5의 계면 사이에서 산소 이온이 잘 움직일 수 있어, Ta2O5내의 결함을 유지하는 것이 어렵기 때문이다. 이때 TiN과 Ta2O5 사이에 barrier 물질을 넣어주면 이러한 산소의 이동을 방지해주어 저항변화 특성을 향상시킬 수 있다. 그림 23은 barrier 삽입 전·후의 저항변화 특성의 차이를 보여주며, barrier가 삽입된 물질에서의 특성을 보여준다.

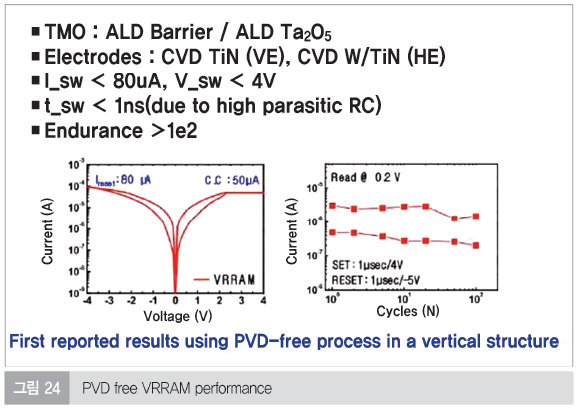

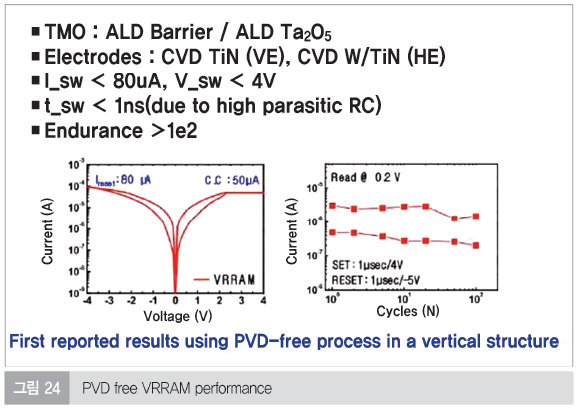

Samsung에서는 더 나아가 이를 실제 VRRAM 구조에 적용하여 특성을 보고하였다. 여기서 전극 물질은 CVD TiN을 이용하고, barrier 물질과 저항변화 물질은 ALD oxide를 이용하여, VRRAM에 적용이 가능한 RRAM 구조와 그 특성을 발표하였다. 그림 24는 Samsung이 발표한 VRRAM의 특성을 보여주고 있다. 그림 21과 그림 22의 평판 구조에 비해 on/off 비와 endurance 등의 특성은 좋지 않으나 실제로 RRAM이 VRRAM에서 동작함을 보여줌으로써 향후 VRRAM의 가능성을 보여주고 있다.

c. 기타 ALD RRAM

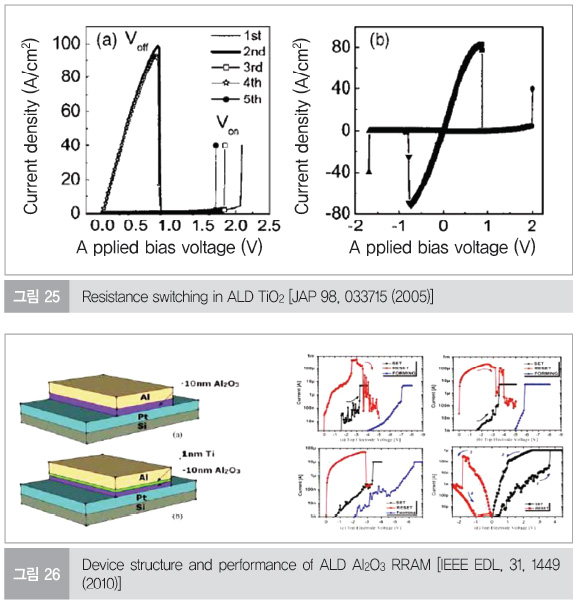

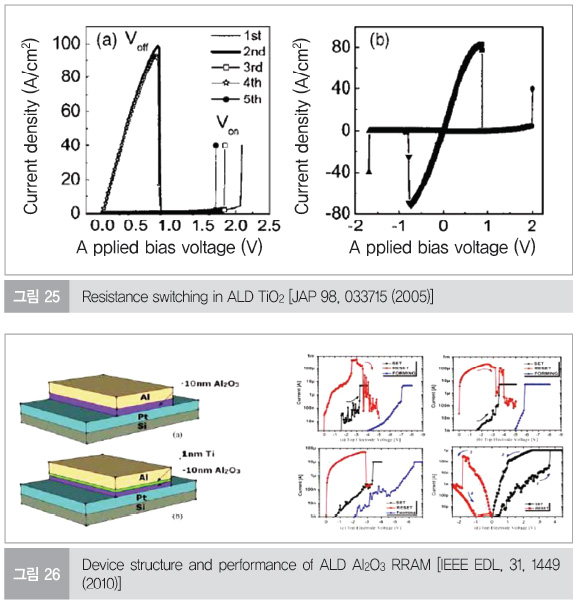

현재는 HfO2와 Ta2O5가 RRAM 의 후보 물질로 압축되었으나, RRAM 연구 초기부터 다른 물질에서도 ALD 공정을 통한 물질 연구가 활발히 이루어졌다. 우선 ALD TiO2는 가장 잘 알려지고 가장 많이 연구 된 저항변화 물질 중 하나이다. 하지만 RRAM으로 쓰이기에는 신뢰성에 문제가 있는 것으로 알려져 최근에는 연구가 많이 이루어지지 않는 추세이다. 하지만 ALD TiO2의 RRAM에서 RRAM의 저항변화 메커니즘이 규명되는 등 RRAM의 기술 발전에 공헌한 바가 매우 크다고 할 수 있다. 그림 25는 TTIP precursor와 O2 plasma를 이용한 TiO2에서의 저항변화 현상을 보여주고 있다. TiO2의 두께는 20nm ~ 60nm에서 저항변화 현상이 관찰되며, 증착온도는 350℃이다.

Al2O3도 잘 알려진 저항변화 물질로, ALD로 증착된 Al2O3에서도 RRAM 특성이 보이는 것으로 보고되었다. 그림 26는 ALD Al2O3 device의 구조와 RRAM 특성을 보여준다. 여기서 Al2O3의 증착을 위해 TDMA와 H2O가 사용되었으며, 증착 온도는 100℃와 300℃에서 10nm 두께로 증착하였다. 이때 열처리 조건과 ALD 박막의 증착 온도에 따라 저항변화 특성이 변하는데, 저온인 100℃에서 증착한 Al2O3의 경우 매우 불안정한 저항변화 현상을 보이지만, 이후 350℃ 15분간의 열처리를 통해 이를 개선할 수 있다. 고온인 300℃에서 증착한 Al2O3의 경우, 우수한 저항변화 특성을 갖고 있다. 흥미롭게도 Ti interstitial 층을 삽입하는 경우 저항변화 특성이 변하는 것을 볼 수 있는데 이는 Ti 자체가 저항변화 스위칭에 관여하기 때문으로 이해할 수 있다.

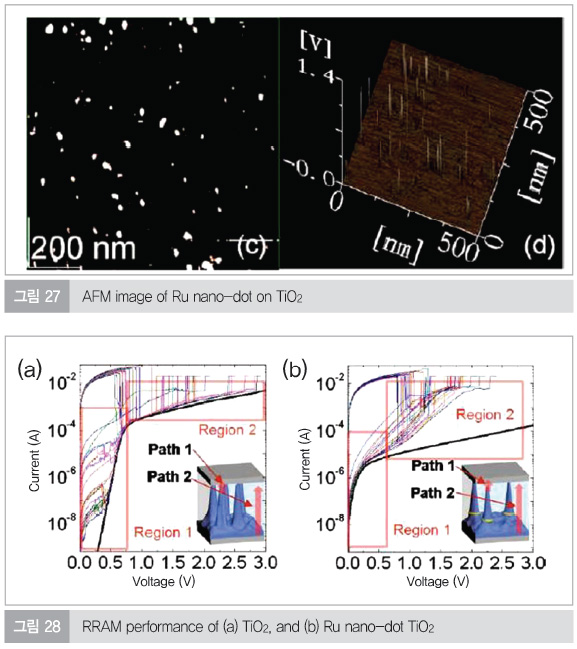

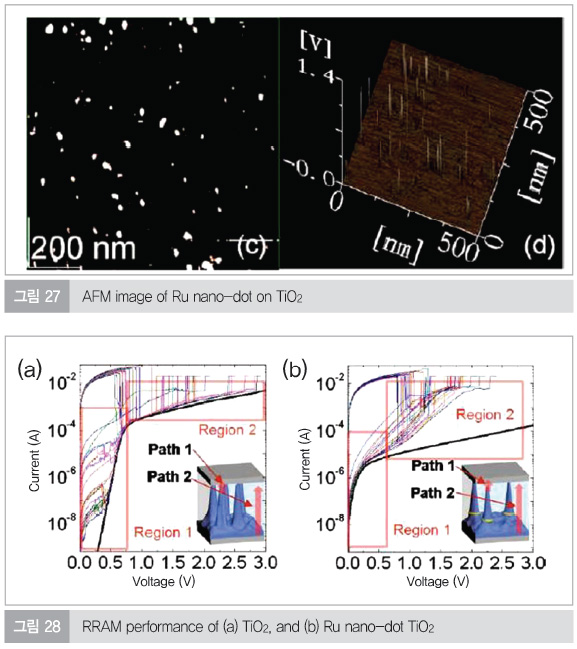

한편으로 ALD 공정이 RRAM의 물질로 직접 쓰이는 것이 아닌 간접적인 방법으로 RRAM의 특성을 향상시키는 역할을 하기도 한다. 그림 26은 ALD TiO2에 Ru을 얇게 증착한 후 AFM을 통해 표면을 관찰한 결과로, TiO2 상에 5nm 정도 크기의 Ru nano-dot이 형성됨을 보여준다. 여기서는 Ru source로 2,4-(Dimethylpentadienyl)(ethylcyclopentadienyl)Ru (DER)을 ethylcyclohexane(ECH)에 0.2M 농도로 용해한 용액이 사용되었고, O2 gas가 reactant로 사용되었다. 증착 온도는 300℃이다.[Chem. Mater. 22, 9, 2850-2856, (2010)]

TiO2의 저항변화 현상은 필라멘트라 불리는 국부적인 전도성 path에서 발생하는데, 기존에는 이러한 path가 random하게 형성되어 RRAM의 신뢰성을 떨어트리는 것이 문제였다. 하지만 이러한 방식으로 Ru nano-dot을 삽입하면 이것이 filament path의 징검다리 역할을 하여, filament의 형성을 균일하게 만들어주는 역할을 한다. 그림 28은 이런 방식으로 Ru nano-dot이 TiO2의 내부에 삽입되어 RRAM의 균일성을 향상시키는 결과를 보여준다.

맺음말

RRAM의 3D 구조 개발에 대한 요구가 분명하며, 따라서 ALD를 이용한 신뢰성 있는 저항변화 물질 개발에 대한 연구는 지속적으로 이루어질 것으로 예상된다. 또한, 아직 많은 연구가 이루어지지는 않고 있지만, 저항변화 물질 뿐만 아니라 selector 물질도 ALD 기술을 통해 형성되어야할 필요가 있으며, 이에 대한 연구도 활발하게 이루어질 것으로 예상된다. 현재까지는 RRAM 물질에 필수적인 산소 결함을 ALD를 통해 직접적으로 만드는 기술 보다는 추가적인 metal 층을 삽입하여 ALD oxide를 환원시키는 방식이 보고되고 있는데, 이는 효율성 측면에서 직접적으로 산소 결함을 만들고 조절할 수 있는 PVD 공정에 비해 단점이 된다. 따라서 향후에는 직접적으로 결함을 포함하는 RRAM 물질을 성장하는 기술이 요구된다.