본고는 마이크로전자 및 마이크로기계 칩 패키지들을 위한 소켓 분야에 관한 것이고, 특히 소켓 또는 근처의 컴포넌트들을 이용하여 다이 패키지와 시스템 보드 사이의 접속들을 변형하는 것에 관한 것이다.

다이 패키지와 시스템 보드 사이의 접속들의 변형이 기술된다. 일례에서, 패턴 재배치 모듈이 소켓에서 이용된다. 모듈은 자신의 일측면 상의 제1 콘택트 어레이를 갖는다. 콘택트들은 소켓에 접속하기 위한 제1 구성을 갖는다. 제2 콘택트 어레이는 제1 콘택트 어레이에 대향하여 모듈의 다른 측면 상에 존재하며, 다이를 포함하는 패키지에 접속하기 위한 제2 구성을 갖는다. 제1 콘택트 어레이의 콘택트들을 제2 콘택트 어레이의 콘택트들에 상호접속하기 위해, 제1 콘택트 어레이와 제2 콘택트 어레이 사이에 보드가 존재한다.

배경 기술

다수의 컴퓨터 및 전자 시스템들, 마이크로프로세서들 및 기타 전자 및 마이크로기계 다이 또는 칩들이 패키지 내에 수용된다. 다이 또는 칩을 포함하는 패키지는 이제 소켓을 이용하여 지지 시스템에 부착된다. 소켓은 마더보드, 시스템 보드, 로직 보드, 인쇄 회로 기판(PCB), 또는 유사한 디바이스에 탑재된다. 패키지 및 소켓에 비하여 매우 커다란 보드는, 통상 높은 기계적 및 전자적 스트레스를 견딜 수 있는 값이 싸고 밀도가 낮은 재료들로 구성된다.

보드에 사용되는 재료들의 결과로서, 작은 공간에 다수의 전자 접속들을 지지하는 것은 비용이 많이 들거나 또는 불가능하다. 그 결과, 보드에 접속된 소켓의 핀들은, 원하는 전기적 및 비용적인 목표들을 충족시키기 위하여 일정 레벨의 공간을 유지해야 한다. 이것은 또한 다이에 대한 패키지가 동일한 레벨의 공간을 유지할 것을 요구한다.

마이크로프로세서들의 핀 카운트가 증가하게 되면, 중앙 처리 장치(CPU)들 및 기타 전자 및 마이크로기계 디바이스들, 지지 패키지들 및 소켓들은 접속들 사이에 동일한 공간을 유지하기 위하여 크게 만들어져야 한다. 그렇지 않으면, 핀들은 너무 가깝게 모이게 되어 시스템 보드의 원하는 전기적인 및 비용적인 목표들을 충족시키지 못한다. 큰 패키지 및 소켓 크기는 다이 또는 칩 및 그에 대응하는 패키지에 대하여 높은 비용을 발생시킨다. 그 대신에 소켓의 PCB측의 핀 피치가 감소하면, 신호선들을 라우팅하고 적절한 비아(via) 유극(clearance)들을 제공하기 위하여 PCB에 대해 더 발전된 기술이 요구된다. 이러한 더 발전된 기술은 소켓 및 시스템 보드에 대한 비용을 증가시킨다. 추가로, 현재의 소켓 기술로 소켓 상의 피치를 더 작게 하면, 기존 기술로 소켓을 제조하는 것이 더욱 어렵거나 불가능해진다.

현재의 마이크로프로세서들에서, 다이는 약 150~250㎛의 범프 피치(bump pitch)를 가질 수 있는 반면, LGA(Land Grid Array), BGA(Ball Grid Array) 또는 PGA(Pin Grid Array)로서의 소켓에 대한 패키지의 접속은 1000~1270㎛의 납땜 볼(solder ball) 피치를 가질 수 있다. 시스템 보드는 동일한 피치를 가질 것이다. 1000㎛ 이상의 볼 피치 및 지지 구조는 소켓을 다이에 비해 크게 만든다. 15㎜×15㎜의 다이는 37.5㎜×37.5㎜의 패키지를 필요로 한다. 이것은 다이에 비해 6배 큰 것이다. 소켓에 매칭시키기 위한 패키지의 추가적인 크기는 패키지된 다이를 제조하고 배치하는 비용을 증가시킨다.

발명의 내용

발명의 실시를 위한 구체적인 내용

본 발명의 실시예들은 유사한 참조 번호들이 유사한 특징들을 가리키는데 사용되는 그림들에 예시로서 도시되지만, 한정적인 것이 아니다. 일부 실시예들에서, 본 발명은 소켓의 핀 피치를 감소시키는 것을 통해 증가된 패키지 조밀화를 제공한다. 이것은 시스템 보드 또는 PCB의 기술 레벨 또는 비용에 영향을 주지 않고 CPU 패키지 크기 및 비용을 감소시킨다.

본 발명의 일 실시예에 따르면, 로우 프로파일 LGA 소켓 또는 임의의 다른 소켓이 추가의 PCB 또는 인터포저(interposer)를 통해 패키지된 다이에 부착될 수 있다. 추가의 PCB는 핀 패턴을 재배치하거나, 핀 위치를 이동시키거나, 또는 핀 밀도를 변경하거나, 또는 패키지와 소켓 사이에서 이들의 임의의 조합을 행하도록 기능할 수 있다. 인터포저의 LGA측은 콘택트 피치에서 패키지 상호접속에 최적화된 배치로 구성될 수 있다. 인터포저의 마더보드측의 볼 피치(ball pitch) 및 패턴은 애플리케이션 또는 플랫폼의 시스템 요구에 대해 최적화될 수 있다. 이러한 패턴, 위치, 또는 피치 인터포저는 별개의 부분으로서 구현되기보다는 소켓 내에 대안적으로 통합될 수 있다. 양쪽의 경우에서, 패턴, 위치 또는 피치 변경 기능들을 갖는 소켓에는 또한 추가의 피처들 및 기능이 부착될 수 있다. 이들은 전력 전달을 위한 수동 소자들, 신호 조절을 위한 IC들(집적 회로들), 커패시터들 및 저항기들을 포함할 수 있다. 그러한 PRM(패턴 재배치 모듈) 소켓은 또한, LSC(Land Side Capacitors)를 위한 유극을 제공하기 위해 공동(cavity)을 가질 수 있다. PRM 소켓은 또한, 디버그 또는 조립 성공/실패 테스트를 위한 테스트 포인트 액세스를 제공하기 위해 그것의 몰딩된 소켓 하우징의 주변 외부에 콘택트 패드들을 가질 수 있다.

다른 실시예에서, PRM은 PTS(pitch translation socket)로 불리거나 또는 PTS로 구현될 수 있다. PTS는 패키지와 시스템 보드 사이의 밀도 또는 핀 피치를 변경할 수 있다. 그것은 또한, 패턴, 스케일 및 크기를 변경할 수 있다. 마찬가지로, PRM은 접속들의 스케일뿐만 아니라 피치를 변경시키기 위해 사용될 수도 있다. 이러한 인터포저 또는 소켓을 이용하여, 패키지 측 또는 소켓의 상부 측의 콘택트 피치를, 더 작은 높은 밀도의 패키지들에 호환되도록 스케일링하는 것이 가능하다. 동시에, 소켓의 하부측은 시스템 보드의 PCB 구조의 라우팅 능력에 대해 최적화될 수 있다. 이것은 시스템이 더 작은 피치의 상부 콘택트들을, 저가의 PCB 기술과 호환 가능한 소켓의 하부의 더 큰 피치 콘택트 패턴으로 산개(fan out)하는 것을 가능하게 한다. 다이 패키지의 크기는 패키지의 비용에서 중요한 요소이다. 한편, 피처들의 밀도 또는 접속들 사이의 공간 및 접속들의 복잡성은 시스템 보드의 비용에서 중요한 요소이다.

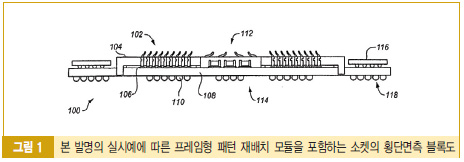

그림 1은 패키지와 시스템 보드 사이에서 핀 패턴을 재배치할 수 있는 소켓(100)의 일례의 단면도를 도시한다. 소켓의 상부에서, LGA 핀 세트는 패키지 상의 핀 어레이와 맞추도록 구성된다. 일 실시예에서, 이러한 핀 어레이는 다이 상의 것과 동일하다. 이것은 패키지 기판에 대하여 다이에서 소켓 LGA까지 간단하고 직선이며 저 비용인 접속을 제공한다. 다른 실시예에서, 패키지는 다이 상의 핀 피치를 보다 미세한 다이 피치에서 보다 큰 소켓 피치로 변환한다는 점에서 통상적이다. 다른 실시예에서, 다이는 패키지를 수용할 보다 큰 핀 피치를 갖기 위해서 필요한 것보다 크게 만들어진다.

LGA 핀은 핀을 담고 유지하고 LGA 핀의 탄성 리프 스프링(resilient leaf spring) 메커니즘을 위한 구조를 제공하는 LGA 바디(104)로부터 뻗어 있다. 다른 종류의 접속기에 대해서는 그 구조에 특히 적합한 상이한 바디를 사용할 수 있다. LGA 바디의 하부에는, LGA 핀의 맞은편에 볼 어레이(106)가 있다. 이것들은 패턴 재배치 모듈(108)과의 콘택트를 형성하는데 사용된다. 패턴 재배치 모듈(108)은 그 상부 표면(top surface)에 LGA 바디와 접속하는 접속기 어레이를 갖는다. 그것은 제2 접속기 어레이(110)를 가지며, 이 경우, 그 하부 표면(botton surface)에 시스템 보드와 접속하는 솔더 볼이다. 패턴 재배치 모듈은 그 상부 표면에 접속 배열을 갖고 그 하부 표면에 대하여 패턴, 위치 및 밀도 중 하나 이상을 재배열한다. 이것은 패키지에 대한 상부 표면 접속을 최적화하고, 접속할 시스템 보드 또는 피스(piece)에 대한 하부 표면 접속을 최적화한다.

패턴 재배치 모듈이 그것에 할당되는 핀 밀도 및 패턴 설계를 만족시키기 위해서 값비싼 고급 재료로 구성되더라도, 이러한 모듈은 시스템 보드에 비해 매우 작다. 이것이 의미하는 것은 시스템 보드에 패키지 핀 밀도를 이용하는 것보다 비용이 매우 덜 든다는 것이다. 마찬가지로, 현재의 시스템에서 일반적으로 행해지는 대로, 패키지에 의해 동일한 재배치 기능을 수행하는 경우, 비용도 보다 높아지는데, 그 이유는 패키지가 소켓에는 통상적으로 요구되지 않는 고유한 밀폐적, 열적, 기계적, 및 다른 제약을 갖기 때문이다.

패턴 재배치 모듈은 프리-임프레그네이티드(pre-impregnated)(프리프레그) 글래스 파이버, 세라믹, 실리콘, 폴리머, 수지 등을 포함하는 각종 상이한 재료로 구성될 수 있다. 재료 및 구성 기술의 특정 선택은 임의의 구현에 적합하도록 변경 가능하다. 일례로, 다중 층과 함께 고밀도(HD) 인쇄 회로 기판(PCB) 재료를 이용한다. HD PCB는 그 기판에 인쇄되는 피처를 보다 작게 할 수 있다. 전력 접속은 입력 및 출력 접속과 분리되어 층들에 라우팅된다. 각 층의 물리적 특성은 운반하는 신호의 종류에 최적화된다.

그림 1의 예에서, 패턴 재배치 모듈(108)은 소켓(100)의 하부 표면을 형성한다. 이 하부 표면은 시스템 보드에 부착되도록 구성된다. LGA 바디(104)는 모듈의 하부에 부착된다. 패턴 재배치 모듈은 또한 소켓이 추가의 피처들을 수용하도록 한다. 예시한 예에서, 모듈(108)은 LGA 소켓보다 크며, 중앙 캐비티(114)에 랜드 측 커패시터(112)를 갖는다.

LGA 바디의 주변을 넘어 뻗어 있는 끝단에서, 모듈은 디버깅, 테스팅 및 다른 기능을 위해 테스트 포인트 액세스(118)를 구동하는 신호 조절기 또는 리피터(116)를 갖는다. 테스트 포인트 액세스(118)는 제조자 테스팅을 위해 마련되거나, 완전한 시스템에 대한 진단 및 서비스 요구를 위해 마련될 수도 있다. 예시한 예에서, 테스트 포인트 액세스는 시스템 보드에 접속하는 PRM의 하부 상의 솔더 볼을 특징화한다. 신호 조절기 또는 리피터는 패키지에 인접하나 패키지를 유지하는 영역 밖에서 PRM의 상부 표면에 위치한다. 모듈은 또한 특정 애플리케이션에 따라 각종 수동 디바이스, 전력 전달 및 조절 디바이스, 신호 조절 디바이스를 수용할 수 있다.

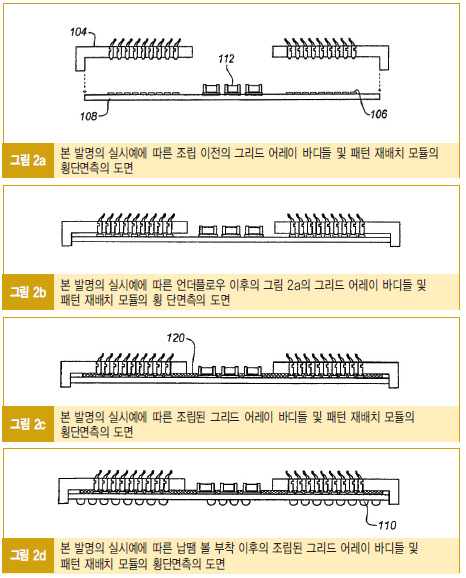

그림 2a 내지 그림 2d는 패턴 재배치 모듈(108)을 갖는 소켓(100)을 생성하는 예시적인 조립 흐름을 도시한다. 그림 2a에서, 패턴 재배치 모듈(108)은 콘택트 어레이(106)와 랜드 측 커패시터(112)를 구비한다. 그림 2b에서, 패턴 재배치 모듈 또는 PCB의 상부 표면에는 LGA 소켓(104)이 부착된다. 이 모듈은 여러 형태로 불릴 수 있으며, 여기서는 인터포저(interposer)라고도 한다. 그림 2c에서, 소켓은 언더필드(under filled)(120)되고, 여기서 필요하다면 이차 조립 공정에 대한 기계적 강도 또는 공정 양립성을 위해 PRM에 LGA 바디가 접속된다.

그림 2d에서, PRM 소켓은 하부 표면 상의 볼 어태치를 통해 시스템 보드에의 접속을 위한 솔더 볼(110)과 부착된다. 이로써 조립이 완료된다. 그림 2d에서, 소켓(100)에서는 그림 1의 테스트 포인트 액세스(118)가 보이지 않는다. 이것은 테스트 포인트 액세스가 요구되지 않는 구현이나, 테스트 포인트 액세스가 이 단면도에서는 볼 수 없는 상이한 부분에 위치하는 구현을 위한 대체 설계를 의미한다.

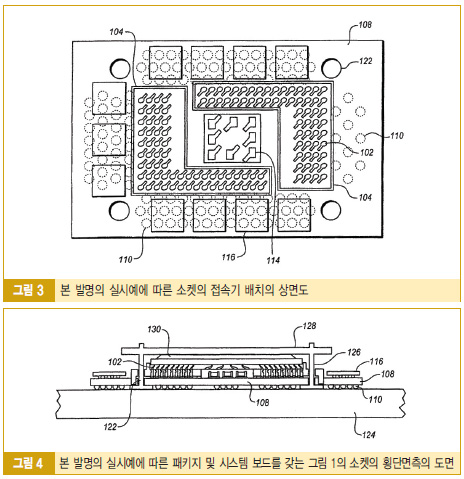

그림 3은 그림 1의 소켓(100)의 상면도이다. 그림 1에서, 위에서 본 소켓의 직사각형 아웃라인은 각각이 LGA 어레이(102)를 갖는 2개의 LGA 바디(104)를 포함한다. LGA 바디들 사이의 중앙 캐비티(114)는 랜드 측 커패시터(114)를 위한 공간을 제공한다. LGA 바디 및 패키지 접속 표면 밖의 3개의 측면 상의 주변을 따라, 신호 조절기 또는 리피터(116)가 위치한다. 이들은 테스트 포인트 액세스용으로 또는 시스템 보드에 대한 접속을 위한 보다 넓은 영역을 제공하도록 구성될 수 있다.

그림 3의 예에서와 같은 다층 PRM 소켓은 밀도 변환을 위해 패턴과 피치를 모두 재배치할 수 있다. 예시한 예에서, 이러한 재배치는 PCB 인터포저(108)를 소켓 바디(104)보다 크게 한다. 예시한 예에서, 인터포저에는 4개의 유지 탑재 홀(122)이 있다. 이들은 유지 탑재 기둥(122)에서부터 LGA 소켓 콘택트(102)까지의 거리를 최소화하도록 내부 배치된다.

그림 4는 소켓의 하부 상의 솔더 볼(110)을 통해 시스템 보드(124)에 탑재된 그림 1의 소켓을 도시한다. 이 경우, LGA 유지 홀(122)은 유지 판 사이의 휨 모멘트(bending moments)를 줄이기 위해서 소켓 하우징 내부의 PRM을 통해 배치된다. 탑재 기둥(126)은 유지 홀에 정착된다. 압착 판(128)은 다이 패키지(130)를 유지하기 위해서 4개의 탑재 기둥에 모두 걸치도록 기둥에 부착된다. 패키지는 MMAP(Molded Matrix Array Package), CSP(Chip Scale Package) 등을 포함하는 각종 상이한 종류 중 어느 하나일 수 있다. 패키지는 압착 판(128)과 LGA 핀(102) 사이에 위치한다. 이 예에 도시한 바와 같이, 압착 판은 시스템 보드(124)는 통하지 않고 PRM(108)만을 통하여 정착된다. 이러한 구성은 또한 인터포저(108) 내의 LGA 유지 홀을 시스템 보드 내의 탑재 홀과 맞추어 탑재 기둥이 시스템 보드에 직접 부착되도록 변경 가능하다. 유지 홀, 탑재 기둥 및 압착 판의 특정 설계 및 위치는 특정 구현에 적합하도록 개조 가능하다. 또한, 시스템은 다른 종류의 패키지 및 패키지 상호접속에 따라 수정 가능하다.

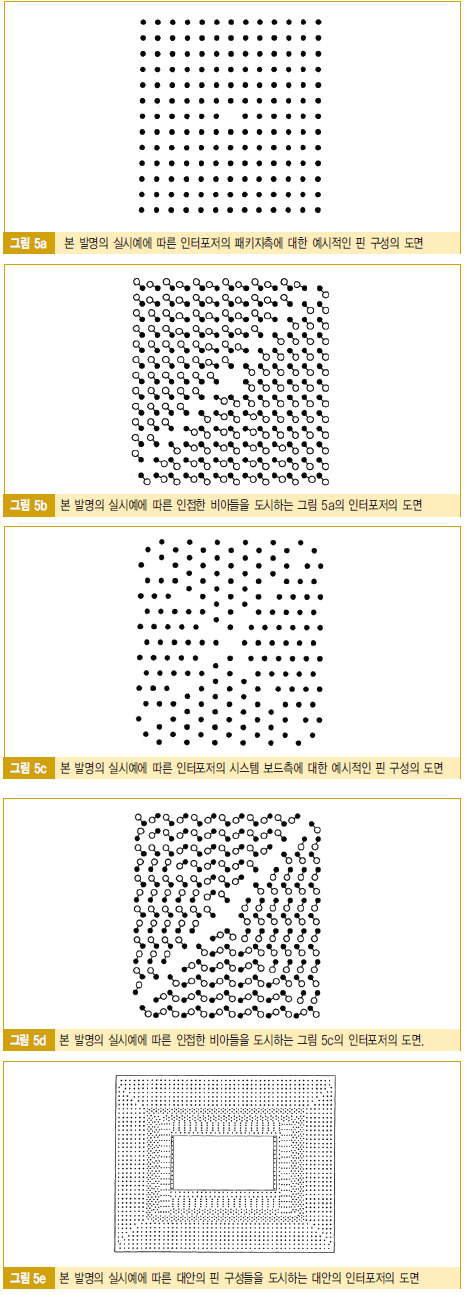

그림 5a 내지 그림 5d는 패키지에서 시스템 보드로의 핀 밀도를 줄이기 위한 상기한 인터포저의 이용 방법의 일례를 도시한다. 그림 5a는 소켓 상의 통상적인 LGA 접속 패턴의 상면도이다. 도시한 예에서, 어레이는 등간격의 접속기의 13개의 행과 13개의 열을 갖는다. 그러한 패턴은 예컨대 그림 1의 인터포저(108) 상의 상부 패턴(106)으로서 이용될 수 있다.

그림 5c는 동일한 인터포저의 상호접속 표면의 하면도이다. 그림 5c에서, 핀 패턴은 패키지의 직사각형 또는 정사각형 배열에서 제2층 상의 지그재그형(staggered) 또는 헥스 팩(hex pack) 배열로 재배치된다. 도면을 일렬로 볼 경우, 인접한 열들에 있는 핀들은 지그재그형이 된다. 즉, 하나의 열의 핀들은 인접한 열의 중간에서 수직 위치한다. 이러한 구성은 또한 일련의 동심 아크로서 보일 수 있다. 또한 패턴에는 개구 또는 갭이 있을 수 있다. 이것은 인터포저 내에 라우팅하기 위한 보다 많은 공간을 제공한다.

인터포저는 LGA 소켓에 대하여 스탬프드(stamped) 핀 및 핀 싱귤레이션(singulation) 공정의 변경 없이 지그재그형, 육변형, 다른 패턴을 제공할 수 있도록 한다. 직사각형 콘택트 패턴을 다른 종류의 배치, 예컨대 지그재그형 또는 헥스 팩 배열로 재배치함으로써, 동일한 시스템 보드 설계 룰 세트에 대하여 보다 높은 콘택트 밀도를 달성할 수 있다. 일반적으로, 정사각형 콘택트 패턴에서 헥스 패턴으로 옮기면서 동일한 최소 콘택트 공간을 유지하는 것은 핀 밀도를 15% 증가시킨다. 이와 달리, 그림 5a 및 5b에 도시한 바와 같이 정사각형 콘택트 패턴에서 헥스 패턴으로 옮기면서 동일한 영역에서 동일한 수의 핀을 유지하는 것은 최소 콘택트 공간을 증가시킨다. 최소 콘택트 공간이 클수록, 이용할 시스템 보드 기술에 대한 비용이 줄어든다.

그림 5b는 그림 5a와 동일한 핀 패턴을 도시하며, 또한 정사각형에서 헥스 패턴으로의 변환을 허용하는 인터포저를 통한 비아의 가능한 위치를 도시한다. 그림 5d는 그림 5c의 하부 헥스 패턴과 함께 동일한 비아 위치를 도시한다. 도면에서 알 수 있는 바와 같이, 상부 표면 핀과 대응하는 하부 표면 핀 사이에 비아를 위치시킴으로써, 두 구성 간의 변환은 각 핀에서 각자의 비아로의 변환이 매우 적게 요구된다.

그림 5e는 본 발명의 일부 실시예들에 따라 가능할 수 있는 가능한 재구성의 상이한 형태를 도시한다. 그림 5e는 인터포저 또는 PRM의 패키지 또는 시스템 보드 측의 핀 구성을 나타낼 수 있는 도면이다. 그림 5e에 도시한 바와 같이, 하나의 어레이에 4개의 상이한 종류의 핀 구성이 존재한다. 그 구성은 중앙으로부터 또는 바깥 에지로 부터의 거리에 따라 변한다. 직사각형 어레이의 가장 바깥 구성은 저밀도 핀의 외주 5개의 행 깊이를 갖는다. 이것들은 균일한 직사각형 구성에 존재하며 도시한 예에서는 7개의 행 및 열 깊이이다. 외주에 의해 둘러싸인 안쪽에는 고밀도 접속의 다른 영역이 존재한다.

고밀도 접속은 일 열에서의 핀들의 간격이 다음 행에서의 핀들 사이에 수직으로 배열되나 인접한 열들로부터 수평으로 이격되도록 교호하는 행으로 구성된다. 이와 달리, 균일한 직사각형 패턴이므로, 인접한 행들 사이에서 수평으로 행들이 배열되거나, 교호하는 대각선으로 핀들이 배열될 수 있다. 헥스 팩에 관하여 전술한 바와 같이, 이것은 핀들이 더욱 밀접하게 이격될 수 있도록 한다. 제2 영역은 4개의 행 및 열 깊이이다. 제3 영역은 내부에 있으며, 제2 영역에 의해 둘러싸이고, 수평 및 수직으로 중앙쪽을 향하여 밀집한 라인들로 배열된 핀을 갖는다. 각 라인들에서의 핀들은 함께 인접하지만, 라인들은 이격되어 있다. 공간은 부재하는 하나 또는 두 개의 행들 마다에 대해 대략적으로 동등하다.

최종적으로, 제4 최내측 영역은 내부 라인들에 직교하는 핀들의 직선이다. 도면들에서, 이것은, 그것의 중심 근처의 인터포저의 어느 한 측면 상에 있는 2개의 수직 열들의 핀들이다. 2개의 수평 행들에서 유사한 핀들의 라인이 또한 제공될 수 있거나 대안적으로 제공될 수 있다. 인터포저의 중심에 하나의 추가적인 영역이 존재한다. 이 영역은 핀들을 갖지 않는다. 그림 5e는, 접속기들을 전혀 갖지 않는 인터포저의 주변부와 동일한 종횡비를 갖는 직사각형 영역을 도시한다. 이 공간은 수동 컴포넌트들, 냉각, 전력 접속들 또는 그 외의 목적들을 위해 보존될 수 있다.

그림 5e 중 상이한 영역들이, 단일 인터포저 또는 PRM에서 결합될 수 있는, 상이한 가능한 구성들의 예들로서 도시된다. 상이한 영역들은 서로에 관하여 재배치되거나 이동될 수 있다. 일부 애플리케이션들에서, 일부 구성들을 이용하는 것이 바람직할 수 있으나, 그 외의 구성들은 아닐 수 있다. 그 외의 애플리케이션들에서, 다른 핀 구성들이 추가되거나, 또는 도시된 것들 대신에 이용될 수 있다. 대신에 중심 개방 영역이 접속기들에 대해 이용될 수 있다. 그림 5e에 도시된 바와 같이, 단일 인터포저의 핀들은 상이한 핀 피치들 또는 밀도들을 갖는 그룹들 내에 있을 수 있다. 피치는 또한 인터포저의 표면에 걸쳐 변화할 수 있다. 핀들 사이의 보다 큰 간격, 즉, 보다 느슨한 구성(looser configuration)이 핀들 간의 라우팅 채널을 넓히기 위해 이용될 수 있다. 예를 들어, 이격된 라인들을 갖는 제3 영역은 라인들 간의 채널들을 라우팅하기 위한 공간을 허용한다. 처음 2개의 영역들에 대해 도시된 바와 같이, 외부 영역은 가장 근접한 보다 내측의 영역보다 더 큰 간격을 갖는다. 외부 영역에서의 더 큰 간격은 외부 핀들 간의 신호들을 보다 밀집된 내부 핀들로 라우팅하는데 사용될 수 있다.

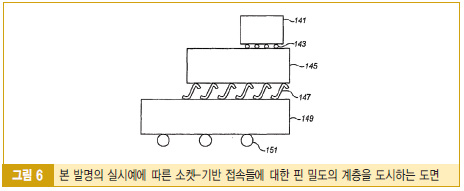

그림 6은 본 발명의 실시예들의 인터포저 또는 패턴 재배치 모듈의 애플리케이션의 도면이다. 그림 6에서 다이(141)는 패키지 기판(145)의 상부 표면과 접속을 형성하기 위해, BGA와 같은 하부 콘택트들(143)의 세트를 갖는다. 패키지 기판은 소켓(149)의 상부 표면과 접속을 형성하기 위해 LGA와 같은 하부 콘택트들(147)의 세트를 갖는다. 도시된 예에서, 패키지 접속기는 다이 접속기들보다 더 멀리 이격되어 있다.

소켓은 시스템 보드와 접속을 형성하기 위해, 그것의 하부 표면 상에, 솔더 볼들과 같은 제3 콘택트들의 세트를 갖는다. 하위 소켓 접속기들은 상위 소켓 또는 패키지 접속기들보다 더 멀리 이격되어 있다. 일례에서, 소켓(149) 인터페이스(147)에 대한 패키지(145)의 콘택트 피치는 PCB 인터페이스(151)에 대한 소켓(149)의 콘택트 피치(예를 들어, 1.0mm 이상)보다 작다(예를 들어, 0.5mm 이하). 이 예에서 PCB에 대한 소켓 인터페이스가 솔더 볼들로 도시되지만, 이것은, 특정 구현에 따라, 또 다른 LGA 압착 콘택트 또는 임의의 그 외의 적절한 유형의 접속일 수도 있다. 피치의 증가는 전술한 인터포저를 통해 이루어질 수 있으며, 이전에 언급한 바와 같이 명확한 비용 및 신뢰도 상의 장점들을 제공할 수 있다.

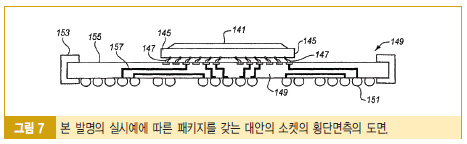

그림 7은 본 명세서에서 설명된 인터포저를 이용하여 함께 접속된 다이, 패키지 및 소켓의 다른 예를 횡단면으로 도시한다. 그림 6의 도면에서와 같이, 다이(141)의 하부는 패키지 기판(145)의 상부에 결합된다. 이 예에서, 패키지는 오직 기판만을 갖는, 매우 단순화된 형식으로 도시되지만, 이 예에서 및 그 외의 모든 예들에서, 다이는 훨씬 더 복잡할 수 있어서, 예를 들어, 커버, 방열판(heat fins)과 같은 쿨러(cooler), 테스팅을 위한 액세스 포트들, 추가적인 콘택트들, 추가적인 다이들, 및 그 외의 전기적 컴포넌트들 또는 신호 조절기들을 포함할 수 있다. 다수의 애플리케이션들에서, 패키지는 환경적인 영향들로부터 다이를 보호하기 위해 외부의 영향을 받지 않도록 밀봉된 커버를 포함할 것이지만, 다이의 특정 구성이 본 발명에 중요한 것은 아니다. 이 경우, 패키지 기판(145)은 인터포저(155)에 직접 접속하기 위한 LGA(147)를 갖는다. 인터포저는, 인터포저 주변 둘레에 확장하는 소켓 프레임(153)에 탑재된다. 소켓 프레임은 또한, 전술한 바와 같이 그 외의 컴포넌트들을 수용할 수 있다. 소켓(149)은 또한 매우 단순화된 형식으로 도시된다. 그것은, 본 도면에서 어느 것도 도시되지 않은 추가적인 층들, 추가적인 컴포넌트들, 소켓에 대해 패키지를 안전하게 하는 메커니즘 등을 포함할 수 있다.

일례에서, 내장형 콘택트들은 소켓 바디를 형성하는 PCB에 적층된다(laminated). 콘택트 형상들은 표준 포토 에칭 기법들을 이용하여 정의되고, 상승된 형상(raise form) 내로 스탬프된 후에 PCB 바디에 적층된다. 콘택트 형상들은, LGA 콘택트들이, PCB 상의 그리고 PCB 내의 적절한 상호접속들에 접속되는 곳에 적층된다. 라우팅 또는 다이(141)에서 인터포저(155)를 통해 소켓(151)의 하부 콘택트들에 내부적으로 접속된 상부 콘택트들의 팬 아웃(fan out)의 예가 또한 도 7에 도시된다. 인터포저는 각각의 패키지 접속기를 하나 이상의 솔더 볼들에 접속하는 도전성 라인들을 포함한다. 도시된 라인들은 PCB(printed circuit board) 기법들을 이용하는 제조에 특히 적합한 수평 및 수직 컴포넌트들을 갖는다. 수평 라인들은 PCB의 층 상의 트레이스(trace)로서, 그리고 수직 라인들은 층들 간의 도전성 비아들(conductive vias)로서 생성될 수 있다.

시작 패키지 패턴에 대한 최종 소켓 볼 패턴의 피치 및 관계에 따라, 인터포저는 저비용의 2층 PTH(Plated through hole), 4층 설계, 8층 HDI(High density interconnect), 또는 그 외의 다양한 기술들 및 설계들에서 PCB의 형태로 만들어질 수 있다. 8층 HDI에 있어서, 2개의 층들은 상호접속을 위한 것일 수 있다. PCB 기술들을 이용하면, 인터포저는 8개의 층들에 대해 약 0.5mm 두께이거나 2층 버전에 대해 0.1mm 두께일 수 있다. 다양한 그 외의 기술들이 대안들로서 이용될 수 있다.

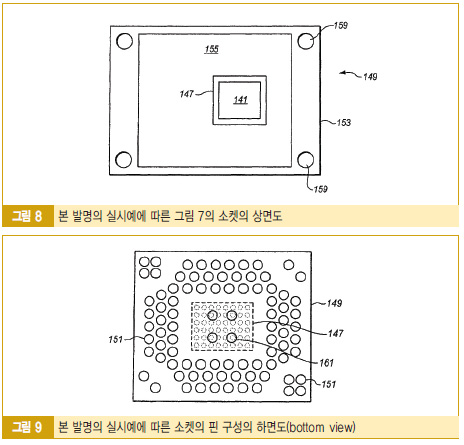

그림 8은 그림 7의 예에 대해 적절한 대안의 구성의 상면도를 다시 도시한다. 그림 8에서, PCB 인서트(PCB insert)(155)는, 소켓에 대하여 패키지를 압착 로딩하는 탑재 홀들(mounting holes)(159)을 포함하는 몰딩된 플라스틱 프레임(153) 내에 수용된다. 이것은 압착 판이 그림 4의 것과 유사하게 사용되도록 한다. 패키지(147)는 소켓의 중심 근방에 수용되며, 패키지는 다이를 수용한다. 이 예에서, 소켓은 대략 패키지의 면적의 18배의 면적을 갖는 것으로서 도시된다. 이것은, 패키지의 크기 및 비용에 있어서 중요한 절감을 나타낸다.

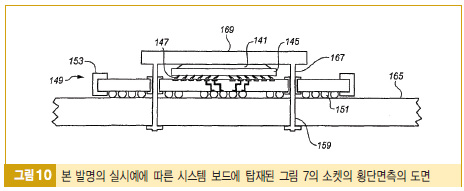

그림 9는 그림 7의 인터포저를 이용하여 달성될 수 있는 예시적인 피치 밀도 변환의 도면이다. 도면은 시스템 보드(151)에 대한, 예시적인 핀 패턴 상에 중첩된, 패키지(147)에 대한 예시적인 핀 패턴을 도시한다. 다수의 상이한 패턴들이 가능하다. 이 예는 다수의 가능성들 중 오직 하나만을 도시하도록 의도된다. 도시된 바와 같이, 패키지는 소켓의 중심에서 고밀도 직사각형 피치(147)를 갖는다. 이것은 소켓을 통해 더 큰 피치의 PCB BGA 콘택트 구성(151)으로 인터포저에 의해 변환된다. 콘택트들은 패키지 콘택트들의 주변 둘레에 배치되어 소켓의 중심에서 그 외의 유형들의 접속기들에 대한 공간을 만든다. 대안적으로, 소켓은 중심에서 콘택트들을 가질 수도 있다. 도시된 바와 같이, 변환된 피치는 PCB BGA 콘택트들에 걸쳐서 균일할 필요는 없다. 또한, 다수의 기능적 BGA 패드들(161)이 도시된다. 다수의 추가적인 패드들의 유형들이 인터포저의 설계 내에 포함될 수 있다. 이 예에서, 패드들은 소켓의 중심에서의 추가적인 전력 전달 BGA 패드들이다. 그 외의 예들에서 도시된 바와 같이, 이 영역은 또한 저항기들 및 커패시터들과 같은 그 외의 수동 컴포넌트들을 위해 이용될 수 있다.

그림 10은 그림 7 및 그림 8에서와 같이 다이(141) 및 패키지 기판(145)에 접속하고, 시스템 보드(165)에 탑재되는 프레임된 인터포저(149)의 예를 도시한다. 그림 10의 예는 도 4의 것과, 소켓의 설계가 단순화되었다는 점만 제외하면 유사하다. 그림 10의 경우에 있어서, 어떠한 LGA 바디들도 이용되지 않으며, 패키지 기판은 인터포저(149)에 직접 접속된다. 그림 4의 예에서와 같이, 그림 10에서는, 패키지 및 소켓은 이해의 용이함을 위해 단순화되었으며, 추가적인 다이들, 접속기들 및 방열판들 또는 액체 냉각 판들과 같은 냉각 시스템들을 포함하는 다수의 추가적인 컴포넌트들을 포함할 수 있다.

그림 10에서, 소켓은 그것의 하부 표면 상의 솔더 볼들(151) 및 유지 기둥(retention post)을 이용하여 마더보드(165)의 상부에 설치된다. 패키지의 하부(145)는 소켓의 상부 상의 LGA(147)에 탑재된다. 패키지는, 패키지의 상부에 걸쳐 놓이고, 소켓 및 시스템 보드를 통해 확장하는 유지 기둥(167)에 부착되는 압착 판(169)을 이용하여 소켓에서 적소에 수용된다.

그림 4와 같이, 그림 10은 소켓 하우징 내에서 유지 홀들(159)을 통해 유지 판으로부터 소켓 방향으로 수직으로 연장되는 탑재 기둥들(167)을 설치하여 보호되는 압착 유지 판(169)을 도시한다. 그러나 그림 4의 예에서, 탑재 기둥들은 시스템 보드가 아니라 소켓의 하부 기판을 통해 보호된다. 본 예에서, 탑재 기둥들은 소켓 및 유지판을 적소에 유지하기 위해 시스템 보드를 통해 확장한다. 특정 구현에 따라 어느 유형의 소켓이라도 어느 탑재 기둥 구성과도 이용될 수 있다.

그림 10은 또한 LGA 유지 홀들(159)이 유지 판과 LGA 콘택트들 간의 휨 모멘트들을 감소시키기 위해 소켓 하우징(153)에 대해 내부에 위치되는 것을 또한 도시한다. LGA 콘택트 영역은 종래의 소켓에 비교하여 크기가 감소되며, 유지 홀들의 종래의 외부 배치는 패키지로부터 더 큰 거리를 두고 홀들을 배치할 것이다. 이것은 홀들을 패키지 및 LGA 콘택트 영역에 대해 안쪽으로 보다 근접하도록 이동시킴으로써 보상된다.

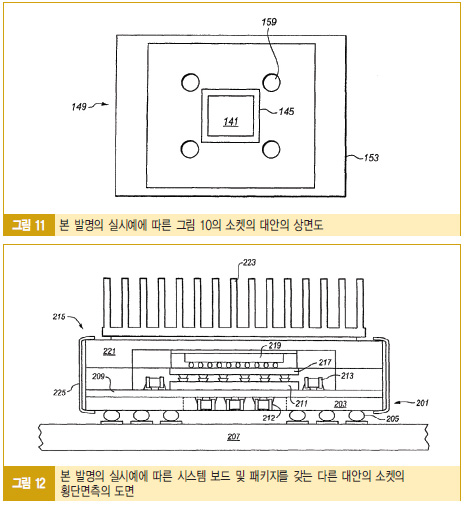

그림 11은 이러한 구성을, 특히 도 8과 비교하여 보다 명확하게 도시한다. 두 도면들에 도시된 바와 같이, 다이 기판(145)은 소켓 프레임(153), 및 프레임에 의해 수용되는 인터포저(149)보다 현저하게 작다. 그림 10에 대응하는, 그림 11의 예에서, 유지 홀들(159)은, 그림 8의 유지 홀들에 비교하여 패키지(145) 및 다이에 근접하여 위치된다. 패키지가 소켓에 부착되는 방법 및 이용되고 있는 물질의 물리적인 특성들에 따라 어느 쪽의 구성도 이용될 수 있다. LGA 콘택트 영역을 갖는 전술한 압착 유지 판 구성에 있어서, 그림 11의 구성은 패키지와 소켓 사이에 보다 안전한 접속을 제공한다.

그림 12는 전술한 바와 같은 인터포저 또는 PRM을 이용하는 대안적인 다른 구성을 도시한다. 또한, 그림 12는 시스템 보드에 탑재된 패키지 및 소켓을 수평 단면으로 도시한다. 그림 12에서, 소켓(201)은 솔더 볼들(205)을 통해 접속들을 수용하기 위한 프레임(203)을 포함한다. 솔더 볼들은 시스템 보드(207)의 상부에 대한 하부 전기 인터페이스를 형성한다. 소켓은 접속들 위의 인터포저(209)를 수용하여, 시스템 보드 피치에 대해 패키지 피치를 재배치한다.

도시된 예에서, 0.5mm의 패키지 피치가, 약 1.27mm의 시스템 보드 피치로 산개(fanned out)된다. 임의의 구성의 특정 치수들은 구현에 따라, 그리고 기술이 발전함에 따라 변할 수 있다. 이러한 예에서, 소켓의 핀 피치가 더욱 큰 경우, 그것은 랜드 측 커패시터들(212)이 탑재되는 중앙 개구부를 허용한다. 이들은 원하는 바에 따라 인터포저 또는 소켓을 통해 접속될 수 있다.

인터포저 위에서, 소켓은 패키지와 인터페이스하기 위한 LGA 접속기들을 수용하는 LGA 기판(211) 또는 바디를 또한 수용한다. 도시된 예에서, LGA 기판은, 핀 피치에서의 차이 때문에, 인터포저보다 실질적으로 작다. 핀들의 수는 대략 동일하고, 핀 피치는 훨씬 더 작기 때문에, 소켓의 상부 표면 상의 LGA 기판은 소켓의 하부 표면 상의 BGA보다 훨씬 더 작다. LGA 기판이 더 작기 때문에, 인터포저의 상부 측면 상에 추가적인 미사용 표면이 존재한다. 도시된 예에서, 다이 측 커패시터들(213)이 설치된다. 인터포저 및 LGA 기판은, 커패시터들을 원하는 대로 결합하는데 필요한 접속들을 포함할 수 있다. 패키지(215), 예를 들어, CSP(Chip Scale Package)가 LGA 접속기들을 통해 LGA 기판(211)의 상부에 결합된다. 이러한 예에서, 패키지는 LGA 소켓 기판(211)에 접속된 패키지의 하부에 패키지 기판(217)을 포함한다. 다이(219)가, 예를 들면, BGA를 통해 패키지 기판에 결합된다. 패키지는 다이의 상부 위에서 패키지 기판에 접속된 집적 열 확산기(221)를 또한 구비하여, 다이를 패키지 내부에 밀봉함으로써, 그것을 외부 환경에 대하여 보호한다. 또한, 집적 열 확산기는 다이의 상부 표면과의 열적 접촉을 형성한다. 핀(fin)들의 형태의 히트싱크(223)가 집적 열 확산기와 열적으로 결합되어, 다이로부터 열을 외부로 전도시킨다. 히트싱크는 공기 냉각(air cooled) 또는 액체 냉각(liquid cooled)될 수 있다.

소켓(203)은 스프링 클립(spring clips)으로서 도시된 유지 디바이스(225)를 이용하여 패키지(215)를 유지하지만, 클램프, 스크류 및 다양한 종류의 레버들이 이용될 수 있다. 스프링 클립은 패키지 상의 립(lip) 위 및 소켓 상의 립 아래에서 연장되어, 패키지를 소켓 상에 유지한다.

전술한 내장형 콘택트 기술에 의하면, 현재의 LGA 소켓 기술에 의해 달성될 수 있는 것보다 작은 피치들이 가능하다. 이것은 심지어 훨씬 더 작은 패키지들에 대한 가능성을 제공하므로, 보다 낮은 비용이 가능하다. 소켓에서의 피치 변환은 패키지 피치 스케일링을 가능하게 하도록 PCB 기술 향상들의 요건을 완화시킨다. 패키지 크기의 감소 이외에도, PCB 기술 및 소켓 바디에 대한 층형 구성을 이용함으로써, 현재의 방안들과 비교하여, 소켓 내로의 추가적인 회로 집적을 가능하게 한다. 그러한 특징들은 내장형 쉘딩(shielding), 커패시터, 저항기 등을 포함할 수 있다. 이들은 소켓 및 시스템의 고속, 전력 전달 및 밀도 성능을 향상시키는데 이용될 수 있다.

패턴 재배치 모듈은 여러 가지 상이한 형태로 생성될 수 있다. 도시된 바와 같이, 그것은 상부에 탑재된 접속 바디를 갖는 소켓의 하부 콘택트 표면으로서 이용될 수 있다. 대안적으로, 그것은 시스템 보드 및 패키지에 직접 접속하기 위한 소켓의 두 콘택트 표면들을 위해 이용될 수 있다. 다른 대안으로서, 그것은 종래의 소켓 접속기들과 패키지 사이의 종래의 소켓에 추가될 수 있다. 본 명세서에서 기술되지 않은 다양한 다른 구성들이 이용될 수도 있다. 따라서, 핀 구성들이 여러 가지 상이한 방법들로 변경될 수 있는 소켓, 인터포저 및 소켓에 대한 모듈이 기술된다. 이들은 프로세서, 제어기, 조절기, 전력 전달 디바이스, 마이크로기계 디바이스 또는 다른 유형의 디바이스들을 포함하는 매우 다양한 상이한 다이들을 포함하는 패키지를 위해 이용될 수 있다. 본 명세서에 기술된 원리들은, 본 명세서에서는 단지 몇 개의 상이한 예들이 도시되었지만, 상이한 갯수 및 유형의 다이들을 포함하는 상이한 유형의 패키지에 적용될 수 있다. 소켓 모듈 및 인터포저는 인쇄 회로 기판 및 반도체 처리 기술들을 이용하여 형성되도록 잘 적응된다.

핀 구성들은 패턴, 위치, 밀도 또는 유형에 있어서 변경될 수 있으며, 본 명세서에서 기술된 원리들은 LGA, BGA, PGA, 또는 임의의 다른 유형의 접속들 및 접속기들을 포함하는 광범위한 상이한 접속기 기술들에 적용될 수 있다. 본 발명의 실시예들은 구조적 특징들 또는 방법론적 동작들에 특정적인 언어로 기술되었지만, 첨부된 특허청구범위에 정의된 본 발명은 기술된 특정한 특징들 또는 동작들에 한정될 필요는 없다. 기술된 특정한 특징들 및 동작들은 본 발명을 제한하기보다는 예시하기 위해 이용된다.