본 발명의 실시예는 마이크로전자 패키지(microelectronic package)에 관한 것이다. 마이크로전자 패키지는, 제1 영역, 제2 영역, 제1 면, 및 상기 제1 면으로부터 이격된 제2 면을 갖는 기판(substrate)을 포함한다. 하나 이상의 마이크로전자 요소(microelectronic element)는 제1 영역 내에서 제1 면의 위에 위치한다. 전기 전도성 요소는 제2 영역 내에서 기판의 제1 면 및 제2 면 중의 하나 이상의 면에 노출되어 있으며, 전도성 요소의 적어도 일부가 하나 이상의 마이크로전자 요소에 전기적으로 접속되어 있다.

배경 기술

반도체 칩 등의 마이크로전자 소자는 다른 전자 부품에 연결하기 위한 많은 입력 및 출력 접속을 필요로 하는 것이 일반적이다. 반도체 칩 또는 이와 유사한 소자의 입력 및 출력 콘택은 일반적으로 상기 소자의 표면을 실질적으로 피복(cover)하는 그리드형 패턴(grid-like pattern, 일반적으로, ‘영역 어레이(area array)’라고 함)으로 배치되거나, 소자의 앞면의 각각의 에지에 평행하게 그리고 이들 소자의 앞면의 각각의 에지에 인접하게 연장될 수 있는 길에 연장된 열로 배치되거나, 앞면의 중앙에 배치된다. 전형적으로, 반도체 칩 등의 소자는 인쇄 회로 기판 등의 기판상에 물리적으로 실장되어야 하고, 소자의 콘택은 회로 기판의 전기 전도성 요소에 전기적으로 연결되어야 한다.

반도체 칩은 일반적으로 제조 과정 중에 그리고 회로 기판이나 다른 회로 패널 등의 외부 기판상에 반도체 칩을 실장하는 중에, 반도체 칩의 취급을 용이하게 하도록 패키지 형태로 제공된다. 예를 들어, 많은 반도체 칩은 표면실장(surface mounting)에 적합한 패키지 형태로 제공된다. 이러한 일반적인 타입의 많은 패키지가 다양한 용도로 제안되어 왔다. 가장 보편적으로, 이러한 패키지는 일반적으로 ‘칩 캐리어(chip carrier)’라 불리는 유전체 요소(dielectric element)를 포함하며, 이 유전체 요소는 유전체 상에 도금 처리한 또는 에칭 처리한 금속 구조체로서 형성된 단자(terminal)를 구비한다. 이들 단자는 전형적으로 칩 캐리어를 따라 연장하는 얇은 트레이스와 같은 요소에 의해, 그리고 칩의 콘택과 단자 또는 트레이스 사이에서 연장하는 리드 또는 와이어에 의해 자체적으로 칩의 콘택에 연결된다. 면 실장 공정에서, 패키지는 회로 기판 상에 배치되어, 패키지 상의 각각의 단자가 회로 기판상의 대응하는 콘택 패드(contact pad)와 정렬되도록 배치된다. 단자와 콘택 패드 사이에는 땜납(solder) 또는 다른 본딩(bonding) 재료가 제공된다. 패키지는 땜납을 용융 또는 ‘리플로우(reflow)’하거나, 다른 방식으로 본딩 재료를 활성화하기 위하여, 어셈블리를 가열하여 제 위치에 영구적으로 결합될 수 있다.

많은 패키지에서는 직경이 통상적으로 대략 0.1㎜ 내지 대략 0.8㎜인 땜납 볼(solder ball)의 형태를 갖는 땜납 덩어리(solder mass)가 패키지의 단자에 부착된다. 패키지의 바닥 면으로부터 돌출하는 어레이 형태의 땜납 볼을 갖는 패키지를 일반적으로 BGA(ball grid arrray) 패키지라고 한다. 기판에는, LGA(land grid array) 패키지라고 하는 다른 패키지가 땜납으로 형성된 얇은 층 또는 랜드에 의해 고정 부착된다. 이러한 타입의 패키지는 매우 콤팩트하게 할 수 있다. 일반적으로 CSP(chip scale package)라고 하는 소정의 패키지가 회로 기판에서 차지하는 면적은 패키지 내에 포함되는 소자의 면적과 동일하거나 이보다 약간 더 크다. 이에 의하면, 어셈블리의 전체 크기를 감소시킬 수 있으며, 기판 상에 다양한 소자 간의 접속을 짧게할 수 있다는 장점을 가지며, 소자 간의 신호 전파 시간을 제한할 수 있고, 이에 따라 어셈블리의 동작을 고속으로 행할 수 있게 된다.

패키지화한 반도체 칩은 ‘적층형(stacked)’ 구성으로 제공되는 경우가 많은데, 이는 하나의 패키지를, 예를 들어 회로 기판상에 제공하고, 다른 패키지를 첫 번째 패키지의 위에 실장하는 것이다. 이러한 구성에 의하면, 회로 기판상의 단일의 풋프린트(footprint) 내에 여러 상이한 다수의 칩을 실장할 수 있으며, 패키지들 간의 짧은 상호접속만으로 고속의 동작을 가능하게 할 수 있다. 많은 경우에, 이러한 상호접속 거리는 칩 자체의 두께보다 약간 더 크다. 칩 패키지의 적층 구조체 내에 달성해야 할 상호접속의 경우, 각 패키지의 양쪽에 기계적 접속 및 전기적 접속을 위한 구조체를 제공할 필요가 있다. 이러한 구성은 칩이 실장되는 기판의 양쪽에 콘택 패드 또는 랜드를 설치함으로써 이루어지며, 콘택 패드는 전도성 비아(conductive via) 등에 의해 기판을 통해 접속된다. 하부 기판의 상단에 있는 콘택 사이의 갭을 상위 기판의 바닥에 있는 콘택에 가교(bridge)하기 위해 땜납 볼 등을 사용해 왔다. 땜납 볼은 콘택을 접속하기 위해 칩의 높이보다 더 높게 되어야 한다.

길게 연장된 포스트 또는 핀의 형태로 된 마이크로콘택 요소(microcontact element)는, 마이크로전자 패키지를 회로 기판에 접속하는 데에 사용되며, 마이크로전자 패키징에서 다른 접속에도 사용될 수 있다. 일부의 경우에, 마이크로콘택은 하나 이상의 금속성 층을 포함하는 금속 구조체를 에칭함으로써 형성해왔다. 이러한 에칭 공정은 마이크로콘택의 크기를 제한한다. 종래의 에칭 공정으로는, 본 명세서에서 ‘어스펙트 비(aspect ratio)’라고 하는, 최대 폭에 대한 높이의 비율을 가진 마이크로콘택을 형성할 수 없다. 이웃하는 마이크로콘택들 사이의 매우 작은 피치 또는 스페이스와 상당한 높이를 가진 마이크로콘택의 어레이를 형성하는 것이 어렵거나 불가능했다. 또한, 종래의 에칭 공정에 의해 형성되는 마이크로콘택의 구성은 제한적이다. 이러한 종래 기술의 진보에도 불구하고, 마이크로전자 패키지를 제조하고 검사하는 데에 추가로 개선할 사항이 있다.

발명을 실시하기 위한 구체적인 내용

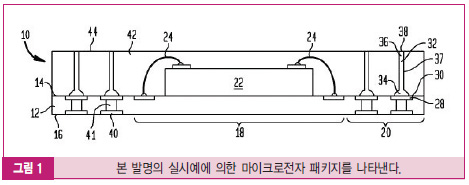

그림 1에는, 본 발명의 실시예에 의한 마이크로전자 어셈블리(microelectronic assembly)(10)를 도시하고 있다. 그림 1의 실시예는 컴퓨터나 다른 전자기기에 사용되는 반도체 칩 어셈블리와 같은 패키지형 마이크로전자 요소로 이루어진 마이크로전자 어셈블리이다. 그림 1의 마이크로전자 어셈블리(10)는 제1 면(14)과 제2 면(16)을 갖는 기판(12)을 포함한다. 기판(12)은 실질적으로 평평한 유전체 요소(dielectric element)로 이루어지는 것이 일반적이다. 유전체 요소는 판형(sheetlike)이면서 얇게 할 수 있다. 일례로, 유전체 요소는 폴리이미드(polyimide), 폴리테트라플루오로에틸렌(PTFE), 에폭시(epoxy), 에폭시-글라스(epoxy-glass), FR-4, BT 레진, 열가소성 또는 열경화성 플라스틱 재료와 같은 유전성 복합 재료(composite dielectric material) 또는 유전성 유기 재료(organic dielectric material)로 된 하나 또는 둘 이상의 층을 포함할 수 있다. 제1 면(14)과 제2 면(16)은 서로에 대해 실질적으로 평행하고, 기판(12)의 두께를 정하는 상기 면(14, 16)에 대하여 직교하는 방향으로 소정의 거리만큼 이격되어 있는 것이 바람직하다. 기판(12)의 두께는 본 발명에서 대략 허용 가능한 범위 내인 것이 바람직하다.

바람직한 예로서, 기판(12)은 제1 영역(18)과 제2 영역(20)으로 분할될 수 있다. 제1 영역(18)은 제2 영역(20) 내에 위치하며, 기판(12)의 중앙 부분을 포함하고, 이 중앙 부분으로부터 바깥쪽으로 연장되어 있다. 제2 영역(20)은 제1 영역(18)을 실질적으로 둘러싸며, 제1 영역으로부터 바깥쪽으로 기판(12)의 외측 에지까지 연장되어 있다.

마이크로전자 요소(22)는 제1 영역(18) 내에서 기판(12)의 제1 면(14)에 실장된다. 마이크로전자 요소(22)는 반도체 칩 또는 이와 유사한 소자가 될 수 있다. 그림 1의 예에서, 마이크로전자 요소(22)는 종래의 방식 또는 ‘페이스 업(face-up)’ 방식으로 알려진 방식으로, 제1 면(14)에 실장된다.

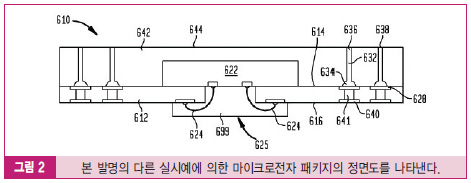

전도성 요소(28)는 기판의 제1 면(14)에 노출된 ‘콘택(contact)’ 또는 패드(pad)(30)를 포함한다. 본 명세서에서, 전기 전도성 요소가 유전성 구조체를 갖는 다른 요소의 표면에 ‘노출’되어 있다는 표현은, 전기 전도성 구조체가 유전성 구조체의 가장 바깥부터 유전성 구조체의 표면을 향해 유전성 구조체의 표면에 직각인 방향으로 이동하는 이론적인 점과 접촉할 수 있게 되어 있다는 것을 의미한다. 따라서 유전성 구조체의 표면에 노출된 단자 등의 전도성 요소는 이러한 표면으로부터 돌출되거나, 표면과 동일한 높이를 갖거나, 표면 아래로 함몰되어 있을 수 있으며, 유전체 내의 홀이나 구멍을 통해 노출되어 있을 수 있다. 전도성 요소(28)는 패드(30)가 기판(12)의 제1 면(14)에 노출된 평평하고 얇은 요소로 해도 된다. 전도성 요소(28)는 적어도 기판(12)의 제2 영역(20)에 형성될 수 있다. 또한, 일례로, 전도성 요소(28)는 제1 영역(18)에 형성해도 된다. 이러한 배치는 마이크로전자 요소(122) 상의 콘택이 마이크로전자 요소(122)의 바로 아래에 위치한 땜납 범프(solder bump)(126) 등에 의해 제1 영역(118) 내의 전도성 요소(128)에 접속될 수 있는 ‘플립칩(flip-chip)’ 구성으로 알려진 방식으로, 마이크로전자 요소(122)를 기판(112)에 실장할 때에 특히 유용하다. 그림 2에 나타낸 다른 구성으로서, 마이크로전자 요소(622)는 기판(612)상에 페이스-다운(face-down) 방식으로 실장되고, 와이어 리드(624)에 의해 칩 상의 전도성 요소에 전기적으로 접속된다. 와이어 리드(624)는 기판(612)의 면(616) 등과 같이 외측을 향하는 면(outwardlyfacing surface)의 상부로 연장된다.

전도성 요소(28) 중의 적어도 일부는, 전도성 요소(28)에 대응하는 요소로서, 기판(12)의 제2 면(16)에 노출된 전도성 패드 등의 제2 전도성 요소에 상호접속될 수 있다. 이러한 상호접속은 전도성 요소(28, 40)와 동일한 재료로 이루어질 수 있는 전도성 금속으로 피복되거나 이러한 금속으로 채워질 수 있는, 기판(12)에 형성된 비아(41)를 사용하여 구성될 수 있다. 전도성 요소(40)는 기판(12)상의 트레이스에 의해서도 상호접속될 수 있다.

마이크로전자 어셈블리(10)는 전도성 요소(28) 중의 적어도 일부에, 예를 들어 전도성 요소(28)의 패드(30) 상에 접합된 다수의 와이어 본드(32)를 더 포함한다. 와이어 본드(32)는 전도성 요소(28)의 베이스(base)(34)에 접합되고, 베이스(34)와 기판(12)으로부터 이격된 자유 단부(free end)(36)까지 연장되어 있을 수 있다.

와이어 본드(32)의 자유 단부(36)는 마이크로전자 요소(22) 또는 마이크로전자 어셈블리(10) 내에서 마이크로 전자 요소(22)에 접속된 임의의 다른 전도성 요소에 전기적으로 접속되거나 다른 방식으로 연결되어 있지 않다는 점에서 자유 단부로서의 특징을 가진다. 다시 말해서, 자유 단부(36)는 마이크로전자 어셈블리(10)의 외부의 전도성 요소에, 땜납 볼이나 본 명세서에서 설명하는 다른 요소에 의해 직접 또는 간접으로, 전자적 접속에 사용될 수 있다. 자유 단부(36)는, 예를 들어 캡슐화 층(encapsulant layer)(42)에 의해 미리 정해진 위치에 유지되거나 다른 전도성 요소에 다른 방식으로 접합 또는 전기적으로 접속된다는 것은, 이러한 임의의 요소가 마이크로전자 요소(22)에 전기적으로 접속되어 있지 않은 한, 이러한 자유 단부가 본 명세서에서 설명하는 바와 같이 ‘자유롭게’ 되어 있지 않다는 것을 의미하는 것은 아니다. 이와 달리, 베이스(34)는 본 명세서에서 설명하는 바와 같이, 마이크로전자 요소(22)에 직접 또는 간접적으로 전기 접속되기 때문에 자유롭게 되어 있지 않다. 그림 1에 나타낸 바와 같이, 베이스(34)는 실질적으로 곡선형으로 될 수 있으며, 베이스(34)와 자유 단부(36) 사이에 있는 와이어 본드(32)의 에지 면(edge surface)(37)으로부터 바깥쪽으로 연장되어 있을 수 있다. 베이스(34)의 크기와 형태는 와이어 본드(32)를 형성하기 위해 사용되는 재료의 유형, 와이어 본드(32)와 전도성 요소(28) 사이의 접속력 및 와이어 본드(32)를 형성하기 위해 사용되는 특정의 공정에 따라 달라질 수 있다. 기판(12)의 제2 면(16)상에 노출된 전도성 요소(40)에, 제2 면(16)으로부터 멀어지는 방향으로 연장된 와이어 본드(32)가 추가로 또는 다른 방식으로 접합되는 대체 실시예가 가능하다.

와이어 본드(32)는 구리, 금, 니켈, 땜납, 알루미늄 등과 같은 전도성 재료로 이루어질 수 있다. 또한, 와이어 본드(32)는 구리 또는 알루미늄과 같이, 전도성 재료의 코어(core)와 같이 재료의 조합으로부터 이루어질 수 있으며, 예를 들어 코어 상부에는 코팅이 피복되어 있다. 이 코팅은 알루미늄, 니켈 등과 같은 다른 전도성 재료가 될 수 있다. 이와 달리, 코팅은 절연 외피(insulating jacket)와 같은 절연성 재료로 이루어질 수 있다. 일례로, 와이어 본드(32)를 형성하기 위해 사용되는 와이어는, 와이어의 길이에 대하여 횡단하는 치수, 즉 두께가 대략 15㎛ 내지 150㎛가 될 수 있다. 웨지 본딩이 사용된 실시예를 포함한 다른 예에서, 와이어 본드(32)는 대략 500㎛ 이하의 두께를 가질 수 있다. 와이어 본드를 형성하기 위한 와이어 세그먼트의 소망하는 길이는 본딩 툴(bonding tool)로부터 인출해 낸 다음, 원하는 길이에서 절단하면 된다. 알루미늄으로 된 와이어 본드를 형성하기 위해 사용될 수 있는 웨지 본딩(wedge bonding)은 와이어의 가열된 부분을 표면에 대하여 대략 평행하게 위치한 웨지(wedge)를 형성하기 위해 상기 수용 면을 가로질러 연장시키는 공정이다. 웨지 접착 방식의 와이어 본드는, 필요에 따라 상방으로 만곡시켜도 되고, 절단하기 전에 소망하는 길이 또는 위치까지 연장시켜도 된다. 일례로, 와이어 본드를 형성하기 위해 사용되는 와이어는 단면이 원통형인 것으로 해도 된다. 이와 달리, 와이어 본드 또는 웨지 접착 방식의 와이어 본드를 형성하기 위해 본딩 툴로부터 공급되는 와이어는 단면을 사각형 또는 사다리꼴 등의 다각형으로 해도 된다.

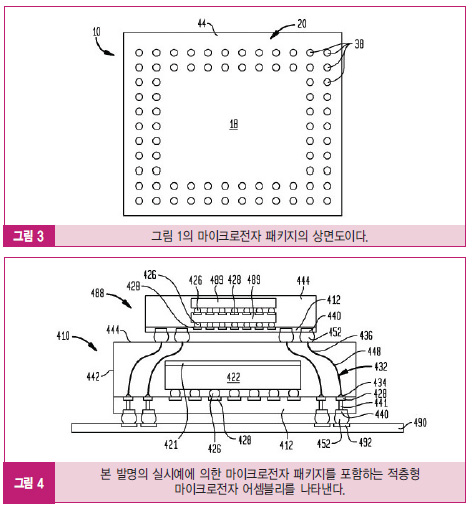

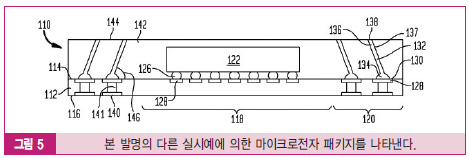

와이어 본드(32)의 자유 단부(36)는 단부 면(end surface)(38)을 포함한다. 단부 면(38)은 다수의 와이어 본드(32)의 각각의 단부 면(38)에 의해 형성되는 어레이 형태로 된 콘택의 적어도 일부분을 형성할 수 있다. 그림 3은 단부 면(38)에 의해 형성된 콘택의 어레이에 대한 패턴의 예를 나타낸다. 이러한 어레이는 면적 어레이(area array) 구성으로 형성해도 되고, 그 변형예는 본 명세서에서 설명하는 구조체를 사용하여 구현할 수 있다. 이러한 어레이는 마이크로전자 어셈블리(10)를, PCB 또는 그림 4에 나타낸 것과 같은 다른 패키지형 마이크로전자 요소 등의 다른 마이크로전자 구조체에 전기적 및 기계적으로 접속하는 데에 사용될 수 있다. 이러한 적층형 구조에서, 와이어 본드(32)와 전도성 요소(28, 40)는 다수의 전자 신호를 운반할 수 있으며, 여러 신호가 단일의 적층 구조체 내의 여러 마이크로전자 요소에 의해 처리될 수 있도록 상이한 신호 전위를 각각 갖는다. 이러한 적층 구조체의 마이크로전자 어셈블리를, 예를 들어 전기적 및 기계적 부착용 단부 면(38)에 의해 전도성 요소(40)에 상호접속하기 위해 땜납 덩어리(solder mass)(52)를 사용할 수 있다. 마이크로전자 어셈블리(10)는 유전체 재료로 이루어지는 캡슐화 층(encapsulation layer)(42)을 더 포함한다.

그림 1의 실시예에서, 캡슐화 층(42)은 기판(12)의 제1 면(14) 중의, 마이크로전자 요소(22)에 의해 피복되어 있지 않거나 점유되어 있지 않은 부분의 상부 또는 전도성 요소(28)의 상부에 형성된다. 마찬가지로, 캡슐화 층(42)은 전도성 요소(28)의 패드(30)를 포함하여, 와이어 본드(32)에 의해 덮여있지 않은, 전도성 요소(28)의 일부의 상부에 형성된다. 캡슐화 층(42)은 마이크로전자 요소(22), 베이스(34)를 비롯한 와이어 본드(32) 및 에지 면(37)의 적어도 일부를 실질적으로 덮을 수 있다. 와이어 본드(32)의 일부분은 캡슐화 층(42)에 의해 피복되어 있지 않은 상태가 될 수 있으며, 이러한 부분을 비캡슐화 부분이라고도 하며, 이러한 부분에 의해 와이어 본드를 캡슐화 층(42)의 외부에 위치한 요소와 전기적으로 접속하는 데에 사용할 수 있다.

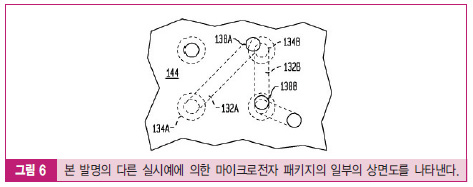

그림 5는 와이어 본드(132)를 포함하는 마이크로전자 어셈블리(110)의 실시예를 나타내고 있는데, 이 와이어 본드(132)의 단부(136)는 베이스(134)의 위에 일직선으로 위치하고 있지 않다. 즉, 실질적으로 평면을 이루기 위해, 2개의 측면 방향으로 연장하고 있는 기판(112)의 제1 면(114)을 보면, 단부(136) 또는 와이어 본드(132) 중의 적어도 하나가 베이스(134)의 대응하는 측면 위치로부터 이들 측면 방향들 중 적어도 한 방향으로 이동되어 있다. 그림 5에 나타낸 바와 같이, 와이어 본드(132)는 이 와이어 본드의 길이방향 축(longitudinal axis)을 따라 실질적으로 직선을 이루며, 그림 1의 예에서와 같이, 이 길이방향 축은 기판(112)의 제1 면(114)에 대하여 각도(146)만큼 각을 이루고 있다. 그림 5의 단면에서는 제1 면(114)에 직각인 제1 평면을 통하는 각도(146)만을 나타내고 있지만, 와이어 본드(132)는 제1 평면과 제1 면(114) 모두에 직각인 다른 평면에서 제1면(114)에 대하여 각을 이루도록 해도 된다. 이러한 각도는 각도(146)와 실질적으로 동일하게 해도 되고 상이하게 해도 된다. 즉, 단부(136)가 2개의 측면 방향으로 베이스(134)에 대하여 변위될 수 있으며, 이들 방향에서의 거리는 동일하게 해도 되고 상이하게 해도 된다. 일례로, 와이어 본드(132)는 마이크로전자 어셈블리(110) 전체를 통해 여러 방향으로 그리고 상이한 거리만큼 변위될 수 있다. 이러한 구성에 의하면, 마이크로전자 어셈블리(110)는 기판(12)의 레벨에서와 비교해서 표면(144)의 레벨에서 다르게 구성되는 어레이를 가질 수 있다. 다른 예로서, 그림 6에 나타낸 바와 같이, 와이어 본드(132)는, 하나의 와이어 본드(132A)의 단부(136A)가 다른 와이어 본드(134B)의 베이스(134B)의 실질적으로 상부에 위치되고, 해당 와이어 본드(134B)의 단부(132B)는 그 외의 어느 위치든 위치될 수 있도록 구성될 수 있다. 이러한 구성은, 콘택 어레이 내의 콘택 단부 면(136)의 상대적인 위치가, 제2 면(116)상의 대응하는 콘택 어레이의 위치에 비해, 변경된 것이라고 할 수 있다.

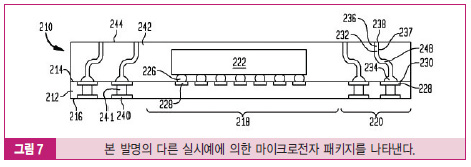

그림 7은 와이어 본드(232)를 포함하는 마이크로전자 서브어셈블리(microelectronic subassembly)(210)의 실시 예를 나타내는데, 이 와이어 본드(232)의 단부(236)는 베이스(234)에 대하여 측방(lateral) 위치로 변위되어 있다. 그림 7의 예에서, 와이어 본드(132)는 내부에 곡선 부분(curved portion)(248)을 포함함으로써 이러한 측방 변위(lateral displacement)를 달성한다. 곡선 부분(248)은 와이어 본드 형성 공정 중에 추가의 단계로서 형성해도 되고, 이러한 곡선 부분의 형성은 와이어의 일부를 원하는 길이만큼 인출해내는 중에 이루어져도 된다. 이러한 단계는 하나의 머신을 사용하는 것을 포함하여, 시판되는 와이어 본딩 장비를 사용해서 수행할 수 있다.

곡선 부분(248)은 와이어 본드(232)의 단부(236)의 원하는 위치를 달성하기 위해, 필요에 따라, 다양한 형태로 구성할 수 있다. 예를 들어, 곡선 부분(248)은 다양한 형태 중에서, 그림 7에 나타낸 것과 같은 S자형 곡선이나 더 평탄한 형태(그림 8에 나타낸 것 참조)로 형성할 수 있다. 또한, 곡선 부분(248)은 단부(236)보다는 베이스(234)에 더 가깝게 위치할 수 있으며, 반대로 베이스보다 단부에 더 가깝게 위치하도록 해도 된다. 곡선 부분(248)은 나선형이나 루프 형태로 해도 되고, 다수의 방향으로 또는 상이한 형태나 특징을 갖는 곡선을 포함하는 혼합형으로 해도 된다.

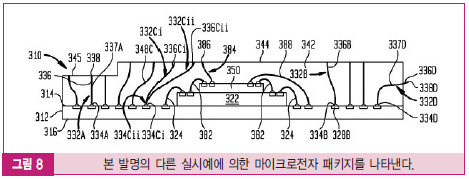

그림 8는 베이스(334)와 단부(336) 사이의 상대적인 측방 변위를 가능하게 하는 다양한 형태를 갖는 와이어 본드(332)의 조합을 구비하는 마이크로전자 패키지(310)의 실시예를 나타낸다. 와이어 본드 중의 와이어 본드(332A)는 베이스(334A)의 상부에 위치된 단부(336A)와 함께 실질적으로 직선형이며, 다른 와이어 본드(332B)는 단부(336B)와 베이스(334B) 사이의 약간의 상대적인 측방 변위가 있는 약간의 곡선 부분(348B)을 포함한다. 어떤 와이어 본드(332C)는 단부(336C)가 베이스(334C)로부터 단부(334B)보다 더 긴 거리만큼 측방으로 변위된 한쪽으로 휩쓸린 형태(sweeping shape)를 갖는다. 그림 8은 또한 기판 레벨 어레이(substratelevel array)의 동일한 열에 위치한 베이스(334Ci, 334Cii)와 이에 대응하는 표면 레벨 어레이(surface-level array)의 상이한 열에 위치한 단부(336Ci, 336Cii)를 갖는 쌍으로 된 와이어 본드(332Ci, 332Cii)를 나타낸다.

와이어 본드(332D)의 다른 변형예는 와이어 본드가 그 측면(side surfac)(47) 상의 캡슐화 층(342)에 의해 피복되어 있지 않은 것으로 도시되어 있다. 자유 단부(336D)가 피복되어 있지 않은 것으로 도시된 예에서, 에지면(337D)의 일부는 캡슐화 층(342)에 의해 추가로 피복되어 있지 않거나, 자유 단부 대신에 피복되어 있지 않게 되어 있을 수 있다. 이러한 구성은 마이크로전자 어셈블리(310)의 측방에 배치된 다른 요소에의 기계적 또는 전기적 접속을 위해, 또는 적절한 요소에의 전기적 접속에 의해 마이크로전자 어셈블리(10)의 평탄화(grounding)를 위해 사용될 수 있다. 또한, 그림 8은 표면(344)보다 기판(312)에 더 가깝게 위치한 오목한 면(recessed surface)(345)을 형성하기 위해 캡슐화 층(342)의 에칭으로 제거하거나, 몰딩하거나, 그외 다른 방법으로 형성된 부분을 나타낸다. 와이어 본드(332A)와 같은 하나 또는 둘 이상의 와이어 본드는 오목한 면(345)에 따른 영역 내에서는 피복되어 있지 않아도 된다. 그림 5에 나타낸 예에서, 에지 면(337A)의 일부와 단부 면(338A)은 캡슐화 층(342)에 의해 피복되어 있지 않다. 이러한 구성에 의하면, 예를 들어 땜납 볼 등에 의해, 땜납을 에지 면(337A)을 따라 위크처리(wick) 하고 단부 면(338)에 접합하는 것에 추가로 상기 에지 면에 접합하도록 함으로써, 다른 전도성 요소에 접속할 수 있다.

그림 8은 2개의 마이크로전자 요소(322, 350)를 구비하는데, 마이크로전자 요소(350)가 마이크로전자 요소(322) 상에 페이스 업 방식으로 적층된 마이크로전자 어셈블리(310)를 나타낸다. 이러한 구성에서, 마이크로전자 요소(322)를 기판(312)상의 전도성 요소에 전기적으로 접속하기 위해 리드(lead)(324)를 사용한다. 마이크로전자 요소(350)를 마이크로전자 어셈블리(310)의 다른 다양한 요소에 전자적으로 접속하기 위해 다양한 리드가 사용된다. 예를 들어, 리드(380)는 마이크로전자 요소(350)를 기판(312)의 전도성 요소에 전기적으로 접속하며, 리드(382)는 마이크로전자 요소(350)를 마이크로전자 요소(322)에 전기 접속한다. 또한, 다양한 와이어 본드(332)를 갖는 구조체에서와 유사하게 될 수 있는 와이어 본드(384)는, 캡슐화 층(342)의 표면(344)상에, 마이크로전자 요소(350)에 전기적으로 접속되는 콘택 면(contact surface)(386)을 형성하는 데에 사용된다. 이것은 다른 마이크로전자 어셈블리의 요소를 캡슐화 층(342)의 상부로부터 마이크로전자 요소(350)에 직접 전기적으로 접속하는 데에 사용될 수 있다. 마이크로전자 요소(322)에 다른 마이크로전자 요소(350)가 부착되지 않은 경우를 포함하여, 마이크로전자 요소(322)에 접속되는 리드가 포함될 수도 있다. 캡슐화 층(342)에는, 표면(344)으로부터 리드(380)에 따른 지점까지 연장하는 개구를 형성함으로써, 표면(344)의 외부에 위치한 요소에의 전기적 접속을 위해 리드(380)에 접근할 수 있도록 해도 된다. 와이어 본드(332C)의 상부와 같이, 와이어 본드(332) 또는 임의의 다른 리드의 상부에, 단부(336C)로부터 멀리 떨어진 지점에 상기 개구와 유사한 개구를 형성해도 된다. 이러한 예에서, 단부(336C)는 표면(344) 아래에 위치하도록 해도 되고, 이 경우 개구는 전기적 접속을 위한 접근용으로만 제공된다.

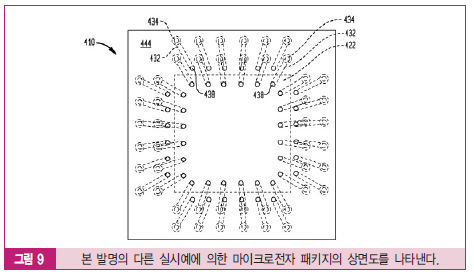

그림 4에 나타낸 구성에서, 와이어 본드(432)는 단부(436) 중의 적어도 일부가 마이크로전자 요소(422)의 주 표면(424)상의 영역까지 연장되는 곡선 부분(448)을 포함하는 구성이 가능하다. 이러한 영역은 마이크로전자 요소(422)의 외측 주변에 의해 이루어지며, 마이크로전자 요소로부터 상방으로 연장될 수 있다. 이러한 구성의 예는 그림 9에 나타낸 기판(412)의 제1 면(414) 쪽을 본 도면으로 도시되어 있다. 이 구성에서, 와이어 본드(432)는 마이크로전자 요소(422)의 뒷면 상에 위치하며, 마이크로전자 요소의 앞면(425)에서 기판(412)에 플립칩 접착된다. 다른 구성(그림 8 참조)으로서, 마이크로전자 요소(422)는 기판(312)에 페이스 업 방식으로 실장될 수 있으며, 앞면(325)은 기판(312)으로부터 먼 쪽을 향해 있으며, 하나 이상의 와이어 본드(336)는 마이크로전자 요소(322)의 앞면 상에 위치한다. 기판(312)에 접착된 와이어 본드(336)는 마이크로전자 요소(350)의 앞면 또는 뒷면 상에 배치될 수 있다. 그림 9에 나타낸 마이크로전자 어셈블리(410)의 실시예에서는, 전도성 요소(428)가 마이크로전자 요소를 둘러싸는 행과 열로 배치된 제1 어레이를 형성하는 패턴으로 구성되며, 개별의 전도성 요소(428) 사이에서는 소정의 피치(pitch)를 가질 수 있다.

와이어 본드(432)는 와이어 본드의 각각의 단부(436)가 제2 어레이 구성에 따라 다른 패턴으로 배치될 수 있는 구성을 갖는다. 또한, 전도성 요소(428)는 기판(412) 전체를 통해 위치한 어레이의 집합으로 구성될 수 있으며, 와이어 본드(432)는 단부(436)가 단일의 어레 또는 어레이의 여러 집합이 되도록 구성해도 된다.

그림 4는 마이크로전자 요소(422)의 표면을 따라 연장된 절연층(421)을 나타낸다. 절연층(421)은 와이어 본드를 형성하기 전에, 유전체 또는 다른 전기 절연성 재료로 형성해도 된다. 절연층(421)은 마이크로전자 요소가 마이크로전자 요소의 상부로 연장된 어떠한 와이어 본드(423)와도 접촉하지 않도록 구성해도 된다. 특히, 절연 층(421)은 와이어 본드 사이의 전기적 단락과 와이어 본드와 마이크로전자 요소(422) 사이의 단락을 방지할 수 있다. 이에 의하면, 절연층(421)은 와이어 본드(432)와 마이크로전자 요소(422) 사이에서의 의도하지 않은 전기적 접촉에 기인한 고장이나 손상을 피할 수 있다.

그림 4 및 그림 9에 나타낸 와이어 본드 구성에 의하면, 예를 들어 마이크로전자 어셈블리(488)와 마이크로전자 요소(422)의 상대적인 크기가 허용되지 않는 경우에, 마이크로전자 어셈블리(410)를 마이크로전자 어셈블리(488) 등의 다른 마이크로전자 어셈블리에 접속할 수 있다. 그림 4의 예에서, 마이크로전자 어셈블리(488)는 일부의 콘택 패드(440)가 마이크로전자 요소(422)의 앞면(424) 또는 뒷면(426)의 면적보다 더 작은 면적 내에서 어레이 형태로 될 수 있는 크기를 갖는다. 와이어 본드(432) 대신에, 필러(pillar) 등과 같이 실질적으로 수직의 전도성 요소를 갖는 마이크로전자 어셈블리에서, 전도성 요소(4428)와 패드(440) 사이의 직접 접속은 허용되지 않을 것이다. 그러나 그림 4에 도시된 바와 같이, 적절하게 구성된 곡선 부분(448)을 갖는 와이어 본드(432)는 마이크로전자 어셈블리(410)와 마이크로전자 어셈블리(488) 사이의 필요한 전자 접속을 이루기 위한 적절한 위치에 단부(436)를 가질 수 있다. 이러한 구성은, 마이크로전자 어셈블리(418)가, 예를 들어 미리 정해진 패드 어레이를 갖는 DRAM 칩 등이고, 마이크로전자 요소(422)는 DRAM 칩을 제어하도록 구성된 논리 칩(logic chip)인 경우의 적층형 패키지를 구성하는 데에 사용될 수 있다. 이에 의하면, 단일 유형의 DRAM 칩으로, DRAM 칩보다 크기가 큰 것은 물론, 다양한 크기를 갖는 여러 개의 상이한 논리 칩과 함께 사용할 수 있는 데, 이는 와이어 본드(432)가 DRAM 칩과 원하는 접속을 이루는 데에 필요한 위치에 배치된 단부(436)를 포함하기 때문에 가능한 것이다.

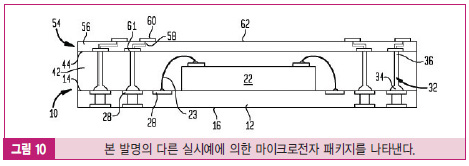

그림 10은 그림 1에 나타낸 유형의 마이크로전자 어셈블리(10)로서, 캡슐화 층(42)의 표면(44)을 따라 연장하는 재배열 층(redistribution layer)을 포함하는 마이크로전자 어셈블리를 나타낸다. 그림 10에 나타낸 바와 같이, 트레이스(58)가 와이어 본드(32)의 단부 면(38)에 전기적으로 접속된 내측 콘택 패드(inner contact pad)(61)에 전기적으로 접속되며, 재배열 층(54)의 기판(56)을 통해 기판(56)의 표면(62)상에 노출된 콘택 패드(60)까지 연장되어 있다. 콘택 패드(60)에는, 땜납 덩어리 등에 의해, 추가의 마이크로전자 어셈블리를 접속해도 된다.

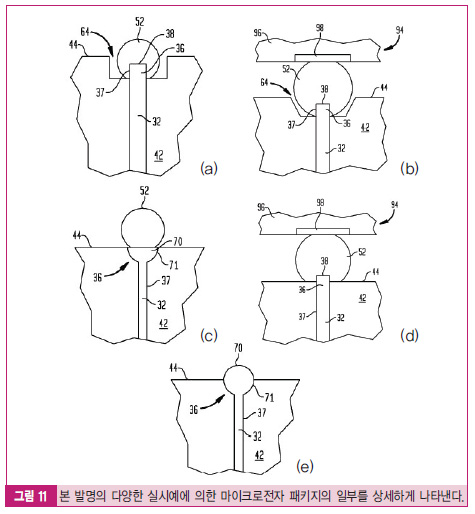

그림 11은 그림 1 내지 그림 10과 유사한 구조체에서, 와이어 본드(32)의 단부(36)의 구조 또는 그 부근의 구조로 구현될 수 있는 다양한 구성을 나타낸다. 그림 11a는 캡슐화 층(42)의 일부분에 캐비티(cavity)(64)가 형성된 구조체를 나타낸다. 이 구성에서, 와이어 본드(32)의 단부(36)는 캐비티(64)에서 캡슐화 층의 작은 쪽의 면(minor surface)(43) 위로 돌출되어 있다. 도시한 예에서, 단부 면(38)은 캡슐화 층(42)의 큰 쪽의 면(major surface)(44)의 아래에 위치하며, 캐비티(64)는 단부 면(38)을 표면(44)에서 노출시켜, 전자 구조체가 단부 면에 접속될 수 있는 구조를 갖는다. 단부 면(38)이 표면(44)과 실질적으로 평행하게 되거나 표면(44)의 상부로 이격된 실시예도 가능하다.

그림 11b는 그림 11a의 구조체와 유사한 구조체를 갖는 캐비티를 나타내지만, 그림 8b의 캐비티는 테이퍼링된(tapered) 측벽(65)을 포함하고 있다. 또한, 그림 11은 기판(98)의 표면에 노출된 콘택 패드(96)에서 땜납 덩어리(52)에 의해 와이어 본드(32)에 전기적 및 기계적으로 접속된 제2 마이크로전자 어셈블리(94)를 나타낸다. 그림 11c 및 그림 11e는 와이어 본드(32) 상의 단부 부분(70)이 실질적으로 곡선형으로 된 단부 구조를 나타낸다. 곡선형의 단부 부분(70)은 와이어 본드(32)의 베이스(34)와 단부(36) 사이의 부분의 단면보다 폭이 넓은 단면을 갖도록 구성된다. 또한, 곡선형 단부 부분(70)은 에지 면(71)을 포함하는데, 이 에지 면(71)은 에지 면(37)과 에지 면(71) 사이의 전이 부분(transition)에서 와이어 본드(32)의 에지 면(37)으로부터 바깥쪽으로 연장되어 있다. 곡선형의 에지 부분(70)을 포함함으로써, 고정 요소(anchoring feature)를 제공함으로써 와이어 본드(32)를 캡슐화 층(42) 내에 고정시킬 수 있다. 이 경우, 에지 면(71)의 방향에서의 변화에 의해 3개의 측면 상의 단부 부분(70)을 둘러싸기 위한 위치에 캡슐화 층(42)을 제공할 수 있다. 이에 의하면, 와이어 본드(32)가 기판(12)상의 전도성 요소(28)로부터 분리되어 전기적 접속이 불량으로 되는 것을 방지하는 데에 도움이 될 수 있다. 추가로, 곡선형의 단부 부분(70)은 표면(44) 내에서 전자적 접속이 이루어질 수 있는, 캡슐화 층(42)에 의해 피복되지 않은 표면 면적을 증가시킬 수 있다. 그림 11e에 도시된 바와 같이, 곡선형의 단부 부분(70)은 표면(44)의 상부로 연장될 수 있다. 이와 달리, 그림 11c에 도시된 바와 같이, 곡선형 단부 부분(70)은 표면(44)과 실질적으로 동일한 높이가 되는 표면을 제공하기 위해 연마 또는 평탄화될 수 있으며, 와이어 본드(32)의 단면보다 큰 면적을 가질 수 있다.

그림 11d는 와이어 본드(32)의 단부(36)가 캡슐화 층(42)의 주 표면(44)의 상부로 이격된 표면(38)을 포함하는 마이크로전자 어셈블리(10)의 구성을 나타낸다. 이러한 구성은 특히, 에지 면(37) 중에서 표면(44) 상의 캡슐화 층(42)에 의해 피복되지 않은 부분을 따라 위크처리(wick)하는 땜납 덩어리(68)에 의해 더 견고한 접속을 제공함으로써, 캐비티(64)에 대하여 앞서 설명한 것과 유사한 장점을 가질 수 있다. 일실시예에서, 단부 면(38)은 표면(42)의 상방으로 대략 10㎛ 내지 50㎛ 사이의 거리만큼 이격될 수 있다. 추가로, 그림 11d의 실시예와, 에지 면(37)의 일부가 캡슐화 층(42)의 표면의 상부에서 캡슐화 층(42)에 의해 피복되지 않은 다른 실시 예에서, 상기 단부는 보호층(protective layer)을 상부에 포함할 수 있다. 이러한 층은 금, 산화물 코팅, 또는 OSP로 이루어진 층을 포함하여, 산화 보호층을 포함할 수 있다.

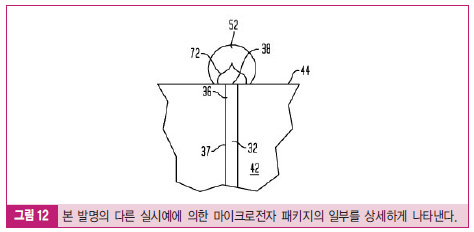

그림 12는 와이어 본드(32)의 단부 면(38)상에 스터드 범프(stud bump)(72)가 형성된 마이크로전자 어셈블리(10)의 실시예를 나타낸다. 스터드 범프(72)는 다른 변형된 와이어 본드를 단부 면(44)의 상단에 제공하고 표면(44)의 일부를 따라 선택적으로 연장함으로써, 마이크로전자 어셈블리(10)를 제조한 후에 형성해도 된다. 변형된 와이어 본드는, 와이어를 인출해내지 않아도, 베이스 부근에서 절단하거나 다른 방식으로 잘라낸다. 소정의 금속을 함유하는 스터드 범프(72)는, UBM과 같은 접착층(bonding layer)을 먼저 제공하지 않아도, 단부 면(38)에 직접 제공할 수 있어서, 땜납에 의해 직접 침윤(wettable)되지 않는, 본드 패드에의 전도성 상호접속을 형성하는 방식을 제공한다. 이러한 것은 와이어 본드(32)를 비칩윤성 금속(non-wettable metal)으로 형성한 경우에 유용할 수 있다.

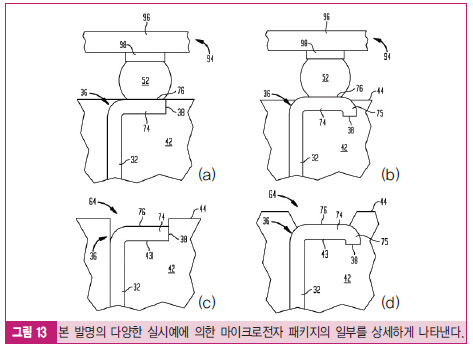

그림 13은 구부러진(bent) 또는 곡선(curved) 형상을 포함하는 와이어 본드(32)의 단부(36)에 대한 구성을 나타낸다. 각각의 실시예에서, 와이어 본드(32)의 단부(36)는, 단부의 일부분(74)이 캡슐화 층(42)의 표면(44)에 실질적으로 평행하게 연장되도록 구부러져 있으며, 에지 면(76)의 적어도 일부분은, 예를 들어 주 표면(44)에 의해 덮여 있지 않도록 되어 있다. 에지 면(76)의 상기 부분은 표면(44)의 외측에서 상방으로 연장되거나, 표면(44)과 실질적으로 동일한 높이로 연장되도록 연마 또는 평탄화될 수 있다. 그림 13a의 실시예는 단부(36) 중의 표면(44)과 평행하며 표면(44)에 실질적으로 직교하는 단부 면(38)에서 종단하는 부분(74)에서 와이어 본드(32)가 급격하게 구부러진 구성을 포함한다. 그림 13b는 그림 13a에 나타낸 것보다, 단부(36) 중의 표면(44)에 평행한 부분(74) 부근에서 더 완만한 곡선부를 갖는 단부(36)를 나타낸다. 또한, 그림 13b에 나타낸 실시예는 와이어 본드의 단부 상에 후크 형상의 부분(hooked portion)(75)을 포함하며, 단부 면(38)은 캡슐화 층(42) 내에서 표면(44) 아래에 위치하게 된다. 이에 의하면, 단부(36)가 캡슐화 층(42) 내에서 제자리를 덜 벗어나도록 하는 견고한 구조체를 제공할 수 있다. 그림 13c와 그림 13d는 그림 13a와 그림 13b에 나타낸 것과 각각 유사하지만, 캡슐화 층(42)에 형성된 캐비티(64)에 의해 표면(44)에 따른 위치에서 캡슐화 층(42)에 의해 피복되어 있지 않은 구조체를 나타낸다. 이들 캐비티는 그림 11a와 그림 11b와 관련해서 설명한 것과 구조적으로 유사하게 할 수 있다. 표면(44)에 평행하게 연장되어 있는 부분(74)을 갖는 단부(36)를 포함함으로써, 길게 연장되고 피복되지 않은 에지 면(75)에 의해, 표면과의 접속을 위한 면적을 증가시킬 수 있다. 이러한 부분(74)의 길이는 와이어 본드(32)를 형성하기 위해 사용되는 와이어의 단면의 폭보다 더 크게 해도 된다.

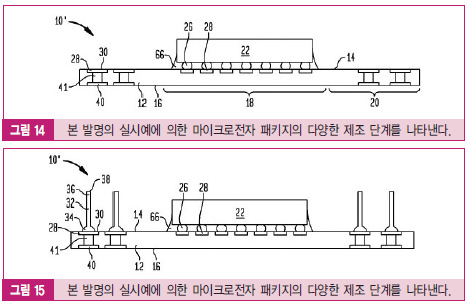

그림 14~그림 18은 마이크로전자 어셈블리(10)를 제조하는 방법 중의 여러 단계에서의 마이크로전자 어셈블리를 나타낸다. 그림 14는 마이크로전자 요소(22)가 기판(12)의 제1 면(14)상에 그리고 제1 영역(18) 내에서 상기 기판에 전기적으로 그리고 기계적으로 접속된 단계에서의 마이크로전자 어셈블리(10’)를 나타낸다. 마이크로전자 요소(22)는, 그림 14에서, 땜납 덩어리(26)에 의해 플립칩 구성으로 기판(12)상에 실장된 것으로 도시되어 있다. 이러한 플립 칩 구성 대신에, 그림 1에 나타낸 것과 같은 페이스 업 본딩을 사용해도 된다. 그림 14에 나타낸 공정의 실시예에서, 마이크로전자 요소(22)와 기판(12)의 사이에 언더필 유전체 층(dielectric underfill layer)(66)을 제공해도 된다.

그림 15는 기판(12)의 제1 면(14)상에 노출된 전도성 요소(28)의 패드(30) 상에 와이어 본드가 도포된 마이크로전자 어셈블리(10”)를 나타낸다. 앞서 설명한 바와 같이, 와이어 본드(32)는 그 와이어 세그먼트의 끝 부분을 가열하여 연화(soften)시킴으로써 제공될 수 있는데, 상기 끝 부분을 전도성 요소(28)에 대하여 가압해서 전도성 요소(28)에 증착 본드(deposition bond)를 형성하고, 베이스(34)를 형성한다. 이어서, 와이어를 전도성 요소(28)로부터 밖으로 인출해내고, 필요한 경우, 와이어 본드(32)의 단부 면(38)과 단부(36)를 형성하기 위해 절단하거나 다른 방식으로 잘라내기 전에, 특정의 형상으로 조작한다. 이와 달리, 와이어 본드(32)를 웨지 본딩(wedge bonding)에 의해, 예를 들어 알루미늄 와이어로 형성해도 된다. 웨지 본딩은 와이어 본드의 단부에 인접한 와이어 부분을 가열하고, 그 부분에 압력을 가하면서 전도성 요소(28)를 따라 드래그시킴으로써 형성된다.

그림 16에서, 마이크로전자 어셈블리(10”’)에는, 기판의 제1 면(14) 상에 도포하고, 제1 면의 상방으로 그리고 와이어 본드(32)의 에지 면(37)을 따라 연장시킨 캡슐화 층(42)이 추가되어 있다. 캡슐화 층(42)은 언더필 층(66)을 덮도록 되어 있다. 캡슐화 층(42)은 그림 15에 도시한 마이크로전자 어셈블리(10’) 상에 수지(resin)를 증착함으로써 형성할 수 있다. 이러한 구성은, 마이크로전자 어셈블리(10’)를 수용할 수 있도록 된 바람직한 형태의 캡슐화 층(42)에 캐비티를 갖는 적절한 구성의 몰드(mold) 내에 마이크로전자 어셈블리(10’)를 배치함으로써 이루어진다. 이와 달리, 캡슐화 층(42)을 적어도 부분적으로 컴플라이언트 재료(compliant material)에 의해 원하는 형태로 미리 제작할 수 있다. 이러한 구성에서, 유전체 재료의 컴플라이언트 특성에 의해, 캡슐화 층(42)을 와이어 본드(32) 및 마이크로전자 요소(22) 상의 위치에 가압할 수 있다. 이러한 공정에서, 와이어 본드(32)는 컴플라이언트 재료 내부로 침투하여 컴플라이언트 재료 내에 홀(hole)을 각각 형성하는데, 이 홀을 따라 캡슐화 층(42)이 에지 면(37)과 접촉하게 된다. 또한, 마이크로전자 요소(22)는 컴플라이언트 재료를 변형하여, 마이크로전자 요소가 컴플라이언트 재료 내에 수용될 수 있도록 할 수 있다. 이 유전성의 컴플라이언트 재료를 압축해서 외측의 면(440)상에 단부 면(38)이 노출되도록 해도 된다. 이와 달리, 캡슐화 층으로부터 잉여의 유전성의 컴플라이언트 재료를 제거하여 와이어 본드(32)의 단부 면(38)이 피복되어 있지 않은 표면(44)을 형성하거나, 표면(63) 내의 위치에서 단부 면(38)을 피복하지 않는 캐비티(64)를 형성해도 된다.

그림 16에 나타낸 실시예에서, 캡슐화 층은 처음에는 캡슐화 층의 표면(44)이 와이어 본드(32)의 단부 면(38)의 상부로부터 이격되도록 형성한다. 단부 면(38)을 노출시키기 위해, 캡슐화 층(42) 중에서 단부 면(38)의 상부에 있는 부분을 제거함으로써, 그림 17에 나타낸 바와 같이, 단부 면(38)과 실질적으로 동일한 높이를 이루는 새로운 표면(44’)이 노출된다. 이와 달리, 그림 11a 및 그림 11b에 나타낸 것과 같은 캐비티(64)를 형성할 수 있으며, 그 내부에서는 단부 면(38)이 캡슐화 층(42)에 의해 피복되어 있지 않다. 또 다른 예로서, 캡슐화 층(42)은, 표면(44)을 미리 단부 면(38)과 실질적으로 동일한 높이로 하거나, 표면(44)이, 그림 11d에 나타낸 것처럼, 단부 면(38) 아래에 위치하도록 형성할 수 있다.

그림 18에 나타낸 다른 실시예에서는, 와이어 본드(32)를 처음에, 와이어 루프(wire loop)(86)의 부분(32’)으로서 쌍으로 형성한다. 본 실시예에서, 와이어 루프(86)는 상기 설명한 바와 같이 와이어 본드의 형태로 되어 있다. 와이어 세그먼트를 상방으로 인출한 다음, 기판(12)의 제1 면(14)의 방향에서 하나 이상의 성분을 갖는 방향으로 구부려서, 이웃하는 전도성 요소(28)의 상부를 실질적으로 덮는 위치까지 끌어당긴다. 이어서, 와이어를 이웃하는 전도성 요소(28) 부근의 위치까지 실질적으로 하방으로 끌어당긴 다음, 절단 또는 다른 방식으로 잘라낸다. 이어서, 와이어를 가열하고, 증착 본딩 등에 의해 이웃한 전도성 요소(28)에 접속해서, 와이어 루프(86)를 형성한다. 다음으로, 이 와이어 루프(86)를 실질적으로 덮도록, 캡슐화 층(42)을 형성한다. 이어서, 연마 또는 에칭 등에 의해 캡슐화 층(42)의 일부를 제거하고, 와이어 루프를 절단하여 2개의 부분(32’)이 되도록 해서 캡슐화 층(42)상에 형성되는 표면(44)에 따른 위치에서 캡슐화 층(42)에 의해 피복되지 않은 단부 면(38)을 가진 와이어 본드(32)를 형성하도록 와이어 루프(86)의 일부를 제거한다. 이어서, 앞서 설명한 바와 같은 마이크로전자 어셈블리(10)에 대하여 후속하는 마감(finishing) 공정을 실시할 수 있다.

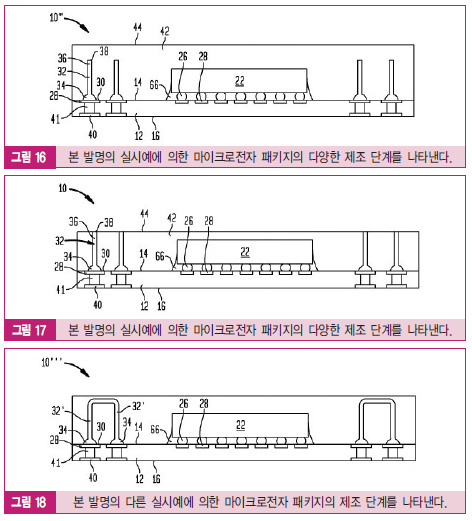

그림 19는 와이어 본드(32)의 단부(36)를 둘러싸는, 상기 설명한 캐비티(64)를 제조하는 다른 실시예에서의 공정을 나타낸다. 그림 19a는 그림 1 내지 그림 4과 관련해서 설명한 일반적인 유형의 와이어 본드(32)를 나타낸다. 와이어 본드(32)는 단부(36)에 희생 재료 덩어리(78)가 도포되어 있다. 희생 재료 덩어리(78)는 실질적으로 구형(spherical)으로 해도 되는데, 이러한 형상은 이 희생 재료 덩어리를 형성하는 중에 희생 재료의 표면 장력에 의해 생길 수 있으며, 본 기술분야의 당업자가 알 수 있는 다른 형상으로 해도 된다. 희생 재료 덩어리(78)는 와이어 본드(32)의 단부(36)를 솔더 페이스트(solder paste)에 담가서 단부를 코팅함으로써 형성할 수 있다. 단부를 담그기 전에 땜납 페이스트의 점도(viscosity)를 조절하여, 위크처리할 땜납 덩어리의 양과 단부(36)에 부착되도록 하는 표면 장력을 제어할 수 있다. 따라서 이에 의하면, 단부(36)에 도포되는 희생 재료 덩어리(78)의 크기를 조절할 수 있다. 이에 대한 대안으로서, 희생 재료 덩어리(78)는 와이어 본드(32)의 단부(36) 상에 가용성 재료를 증착(deposit)하여 형성해도 된다. 다른 희생 재료 덩어리(78)의 예로서, 각각의 땜납 볼이나 그외 다른 재료 덩어리를 사용해도 되고, 구리 또는 금 플래싱(flashing)과 같은 다른 재료를 사용해서 다른 수단에 의해 형성해도 되며, 나중에는 제거해도 된다.

그림 19b에서, 유전체 층(42)은 와이어 본드(32)의 에지 면(37)을 따라 상방으로 마이크로전자 어셈블리(10)에 추가된 것으로 도시되어 있다. 이 유전체 층은 희생 재료 덩어리(78)의 표면 일부를 따라 연장하며, 이에 의해 와이어 본드(32)의 단부(36)로부터 이격되어 있다.

그림 20c는 희생 재료 덩어리(78)의 일부를 제거해서 단부(36) 주위에 캐비티(64)를 형성하고 단부 면(37)의 일부를 노출시킨 구조체를 나타낸다. 본 실시예에서, 희생 재료 덩어리(78)의 대부분 또는 적어도 일부분을, 유전체 층(42)과 와이어 본드(32) 사이의 위치에 남겨도 된다. 그림 20c는 다른 마이크로전자 구조체(10A)의 콘택 패드(40A)에 와이어 본드(32)를 전기적 및 기계적으로 접속하는 땜납 덩어리(52)를 나타내고 있다.

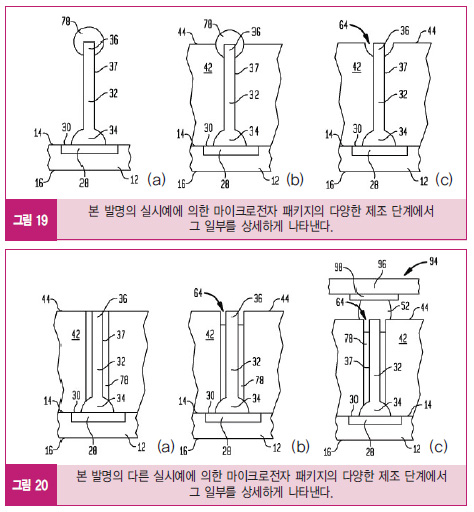

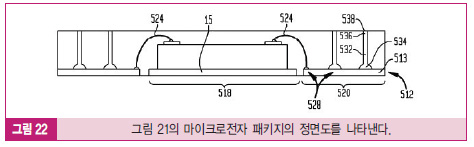

그림 21 및 그림 22는 와이어 본드(532)가 리드 프레임(lead-frame) 구조체 상에 형성된 마이크로전자 어셈블리(510)의 실시예를 나타낸다. 일반적으로, 리드 프레임은 구리 등의 전도성의 금속 시트로 이루어진 구조체이며, 이 전도성의 금속 시트는 다수의 리드(lead)와 추가로 패들(paddle)을 포함하는 세그먼트(segment)와 프레임(frame)으로 패턴화된다. 프레임은 리드와 패들을, 마이크로 전자 어셈블리를 제조하는 중에, 고정시키는 데에 사용된다. 일실시예에서, 다이(die) 또는 칩 등의 마이크로 전자 요소는 패들에 페이스 업 방식으로 접합될 수 있고, 와이어 본드를 사용해서 리드에 전기적으로 접속될 수 있다. 대안으로서, 마이크로전자 요소를, 마이크로전자 요소 아래에서 연장될 수 있는 리드 상에 직접 실장해도 된다. 그림 21의 측면도에 나타낸 와이어 본드(524)는 패들(515) 상에 위치하는 마이크로전자 요소(22)를 리드(515)의 전도성 요소(528)에 연결한다. 와이어 본드(532)는 베이스(534)에서 리드(515) 상의 추가의 전도성 요소(528)에 접합해도 된다.

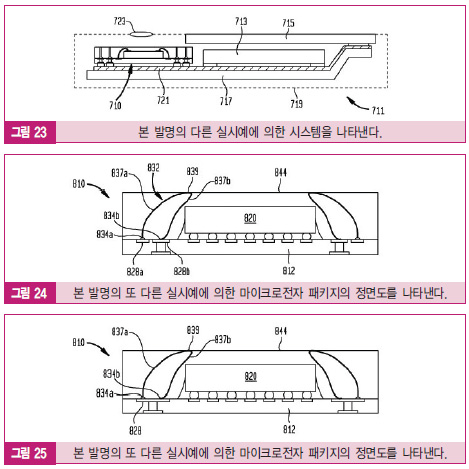

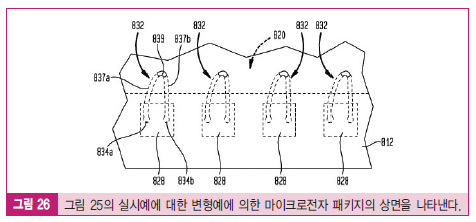

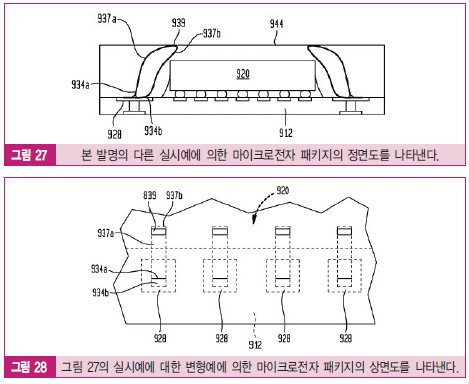

그림 24 내지 그림 26는 클로즈드-루프 와이어 본드(closed-loop wire bond)(832)를 구비하는 마이크로전자 패키지(810)의 또 다른 실시예를 나타낸다. 본 실시예의 와이어 본드(832)는, 그림 24에 나타낸 바와 같이, 이웃하는 전도성 요소(828a, 828b)에 접합될 수 있는 2개의 베이스(834a, 834b)를 포함한다. 이와 달리, 베이스(834a, 834b)가 모두, 그림 25 및 그림 26에 나타낸 바와 같이, 공통의 전도성 요소(828)에 접합되는 구성도 가능하다. 이러한 실시예에서, 와이어 본드(832)는 2개의 베이스(834a, 834b) 사이에서 연장하는 에지 면(837)을 루프 형태로 형성하고, 이에 의해 에지 면(837)은 베이스로부터, 기판(812) 상의 캡슐화 층(842)의 표면(844)에 있는 정점(apex)(839)까지 각각의 부분(837a, 837b)에서 상방으로 연장되어 있다. 캡슐화 층(842)은 에지 면 부분(837a, 837b)의 적어도 일부를 따라 연장되어, 각각의 에지 면 부분을 서로 그리고 패키지(810) 내의 다른 와이어 본드(832)로부터 분리시킨다. 정점(839)에서, 에지 면(837)의 적어도 일부는 캡슐화 층(842)에 의해 피복되고, 이에 의해 와이어 본드(832)는 다른 마이크로전자 부품이나, 커패시터 또는 인덕터 등의 별개의 요소 등이 될 수 있는 다른 부품과의 전기적 상호접속에 사용될 수 있다. 그림 24 내지 그림 26에 나타낸 바와 같이, 와이어 본드(832)는 정점(839)이 전도성 요소(828)로부터 기판(812)의 표면을 가로지르는 적어도 하나의 측방 방향으로 변위되도록 형성된다. 일례로, 정점(839)은 마이크로전자 요소(820)의 주 표면 위에 위치하거나, 마이크로전자 요소(820)가 정렬된 기판(812)의 제1 영역 위에 위치하도록 해도 된다. 와이어 본드(832)에 대한 다른 구성도 가능하다. 예를 들면, 정점(839)이, 다른 실시예에서 설명한 바와 같이, 와이어 본드의 단부 면의 임의의 위치에 배치되는 구성도 가능하다.

그림 27 및 그림 28는 그림 24 내지 그림 26에 나타낸 실시예의 변형예로서, 와이어 본드(834) 대신에 본드 리본(bond ribbon)(934)을 사용한 예를 나타낸다. 본드 리본은 와이어 본드를 형성하는 앞서 설명한 임의의 재료로 된 전도성 재료의 실질적으로 평탄한 부분이 될 수 있다. 본드 리본 구조체는 와이어 본드와 달리 두께보다 폭을 더 넓게 해서, 단면이 실질적으로 원형이 되도록 해도 된다. 그림 27에 나타낸 바와 같이, 본드 리본(934)은 전도성 요소(928)에 접착되어 이 전도성 요소의 일부를 따라 연장하는 제1 베이스(934a)를 각각 포함한다. 본드 리본(932)의 제2 베이스(934b)는 제1 베이스(934a)의 일부에 접합될 수 있다. 에지 면(937)은 2개의 해당하는 부분(937a, 937b)에서 베이스(934a, 934b) 사이로 정점(939)까지 연장되어 있다. 에지 면 중에서 정점(939)의 영역에 있는 부분은 주 표면(944)의 일부를 따라 캡슐화 층(942)에 의해 피복되어 있다. 본 명세서에서 설명하는 다른 실시예에서 사용되는 와이어 본드와 관련해서 설명한 바와 같이, 추가의 변형예가 가능하다.