일반적으로, CMP 더미 패턴의 크기, 수 및 배열은 CMP가 수행되는 각각의 층에서 최적화되도록 결정된다. 그러나 근래에 반도체 디바이스가 더 소형화됨에 따라, 패턴의 단락 및 파티클(particle)과 같은 결함을 검출하도록 광학 검사가 수행되는 경우에, 여러 문제점들이 발견되었다. 디바이스의 소형화로 인해 더 작은 결함 및 파티클을 검출해야 하므로, 검출 감도를 증가시킬 필요가 있다. 그러나 각각의 층에서 최적화되도록 더미 패턴을 배열하기 때문에, 검출 감도가 증가하는 경우에는, 상부 층의 더미 패턴과 하부 층의 더미 패턴 간의 차이가 무아레(간섭 프린지)로서 나타날 수도 있다.

기술 분야

본 발명은 반도체 디바이스 및 그 제조 방법에 관한 것으로, 상세하게는, CMP(Chemical Mechanical Polishing)에 의한 평탄화 프로세스를 이용하는 반도체 디바이스 및 그 제조 방법에 관한 것이다.

CMP는 반도체 디바이스의 제조 시 각각의 층의 표면을 평탄화하는데 종종 이용된다. CMP 에 의한 평탄화 프로세스에 있어서, CMP를 위한 더미 패턴(이하, ‘CMP 더미 패턴’ 또는 단순히 ‘더미 패턴(들)’로 지칭됨)은 디싱(dishing)및 침식의 발생을 회피하도록 배열된다(일본 공개특허출원공보 제 2006-39587 호 참조).

일반적으로, CMP 더미 패턴의 크기, 수 및 배열은 CMP가 수행되는 각각의 층에서 최적화되도록 결정된다. 그러나 근래에 반도체 디바이스가 더 소형화됨에 따라, 패턴의 단락 및 파티클(particle)과 같은 결함을 검출하도록 광학 검사가 수행되는 경우에, 다음 문제점들이 발견되었다. 즉, 디바이스의 소형화로 인해 더 작은 결함 및 파티클을 검출해야 하므로, 검출 감도를 증가시킬 필요가 있다. 그러나 상술한 바와 같이 각각의 층에서 최적화되도록 더미 패턴을 배열하기 때문에, 검출 감도가 증가하는 경우에는, 상부 층의 더미 패턴과 하부 층의 더미 패턴 간의 차이가 무아레(간섭 프린지)로서 나타날 수도 있다. 따라서 결함 검사에 있어서, 그러한 무아레가 결함으로서 검출될 수도 있고, 무아레에 의한 결함이 원래 검출되어야 할 결함 및 파티클과 혼합될 수도 있고, 이들 모두가 결함으로서 검출될 수도 있으므로, 결함의 수가 증가하게 된다. 한편, 검출 감도를 감소시켜 무아레의 생성을 방지하는 경우에는, 미세한 파티클 및 결함을 검출할 수 없으므로, 수율이 감소된다.

발명의 내용

과제의 해결 수단

일 실시형태에 있어서, 반도체 기판 위에 제공되며, CMP에 의해 평탄화되는 제 1 배선 패턴 및 제 1 배선 패턴과 동일한 재료로 이루어진 복수의 제 1 더미 패턴을 포함하는 제 1 층; 및 반도체 기판 위에 제공되며, CMP에 의해 평탄화되는 제 2 배선 패턴 및 제 2 배선 패턴과 동일한 재료로 이루어진 복수의 제 2 더미 패턴을 포함하는 제 2 층을 포함하는 반도체 디바이스가 제공되고, 제 2 더미 패턴 각각의 중심 축이 반도체 기판에 수직인 방향으로 제 1 더미 패턴 중 대응하는 더미 패턴의 중심 축과 일치한다.

다른 실시형태에 있어서, 반도체 기판 상에 제 1 및 제 2 CMP에 의해 평탄화되는 제 1 층 및 제 2 층을 형성하는 단계; 및 제 1 및 제 2 층을 형성하기 전에, 제 1 층에 형성되는 제 1 CMP를 위한 제 1 더미 패턴의 수 및 배열을 결정하는 단계; 및 제 2 더미 패턴의 중심 축이 반도체 기판에 수직인 방향으로 제 1 더미 패턴의 중심 축과 일치하도록 제 2 층에 형성되는 제 2 CMP를 위한 제 2 더미 패턴의 수 및 배열을 결정하는 단계를 포함하는 반도체 디바이스의 제조 방법이 제공된다.

발명의 효과

본 발명에 따르면, 제 1 층에 제공되는 제 1 더미 패턴의 중심 축이 반도체 기판에 수직인 방향으로 제 2 층에 제공되는 제 2 더미 패턴의 중심 축과 일치한다. 따라서 결함을 광학적으로 검출할 때에, 검출 감도가 증가하는 경우에도, 더미 패턴으로 인한 무아레를 억제할 수 있다. 다른 방법으로는, 더미 패턴으로 인한 무아레가 생성되는 경우에도, 그 무아레가 규칙성을 갖고 있고, 더미 패턴으로 인한 것으로서 결정될 수 있다. 따라서 미세한 파티클과 결함을 정확하게 검출할 수 있으므로, 수율을 개선할 수 있다.

발명을 실시하기 위한 구체적인 내용

이하, 첨부된 도면을 참조하여, 소정의 바람직한 실시형태의 다음 설명으로부터 본 발명의 상기 특징 및 이점을 더욱 명확하게 알 수 있다.

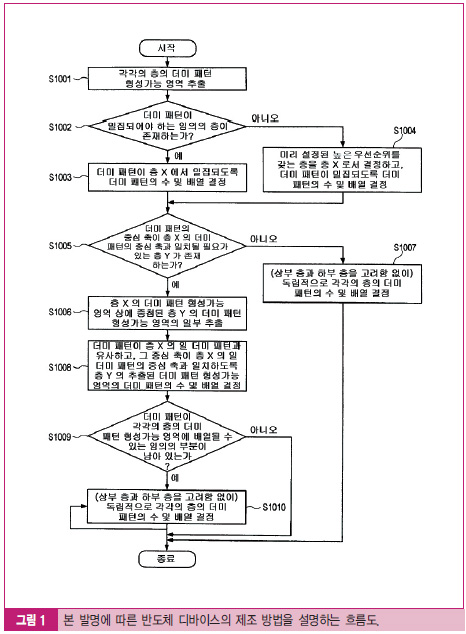

첫째로, 그림 1에 도시된 흐름도를 참조하여, 본 발명에 따른 반도체 디바이스의 제조 방법에서 더미 패턴을 형성하는 공정을 개념적으로 설명한다. 그림 1에 도시된 바와 같이, 첫째로, 각각의 층의 더미 패턴 형성가능 영역을 추출한다(단계 S1001). 그 다음에, 더미 패턴이 밀집되어야 하는 임의의 층이 존재하는지 여부를 결정한다(단계 S1002). 더미 패턴이 밀집되어야 하는 층(X로 표시)이 존재하는 경우에 (예), 층 X에서 더미 패턴이 밀집되도록 더미 패턴의 수 및 배열을 결정한다(단계 S1003). 한편, 더미 패턴이 밀집되어야 하는 층이 존재하지 않는 경우 (아니오), 미리 설정된 높은 우선순위를 갖는 층을 층 X로서 결정하고, 더미 패턴이 밀집되도록 더미 패턴의 수 및 배열을 결정한다(단계 S1004). 다음으로, 더미 패턴의 중심 축이 층 X의 더미 패턴의 중심 축과 일치될 필요가 있는 층 Y가 존재하는지 여부를 결정한다(단계 S1005). 일치될 필요가 있는 층 Y가 존재하는 경우에 (예), 층 X의 더미 패턴 형성가능 영역과 중첩하는 층 Y의 더미 패턴 형성가능 영역의 일부를 추출한다(단계 S1006). 한편, 더미 패턴의 중심 축이 층 X의 더미 패턴의 중심 축과 일치될 필요가 있는 층 Y가 존재하지 않는 경우에 (아니오), 상부 층과 하부 층 간의 관계를 고려함 없이 독립적으로 각각의 층에서 더미 패턴의 수 및 배열을 결정하고(단계 S1007), 더미 패턴 형성 공정이 종료한다.

단계 S1006 다음에, 더미 패턴이 층 X의 일 더미 패턴과 유사하고, 그 중심 축이 층 X의 일 더미 패턴의 중심 축과 일치하도록, 층 Y의 추출된 더미 패턴 형성가능 영역에서 더미 패턴의 수 및 배열을 결정한다(단계 S1008). 다음으로, 각각의 층의 더미 패턴 형성가능 영역에 더미 패턴을 배열할 수 있는 임의의 부분이 존재하는지 여부를 결정한다(단계 S1009). 그러한 부분이 남아 있지 않은 경우에 (아니오), 더미 패턴 형성 공정은 종료한다. 그러한 부분이 남아 있는 경우에 (예), 상부 층과 하부 층 간의 관계를 고려함 없이 독립적으로 각각의 층에서 더미 패턴의 수 및 배열을 결정한다(단계 S1010). 단계 S1009 및 S1010은 더미 패턴을 배열할 수 있는 어떠한 부분도 존재하지 않을 때까지 반복되고, 더미 패턴을 배열할 수 있는 부분이 제공되지 않는 경우에 더미 패턴 형성 공정이 종료한다.

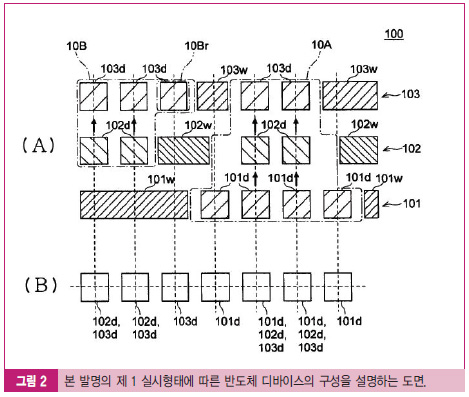

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시형태를 상세히 설명한다. 그림 2A 및 2B는 본 발명의 제 1 실시형태에 따른 반도체 디바이스의 구성을 설명하는 도면으로서, 그림 2A는 개략적인 단면도이고, 그림 2B는 반도체 디바이스를 그 상면에서 볼 때의 평면도이다. 단순화를 위해, 그림 2A에는 단지 배선 패턴과 CMP 더미 패턴만이 도시되어 있고, 반도체 기판이나 층간 유전체막 등은 생략되어 있으며, 그림 2B에는 단지 더미 패턴만이 도시되어 있다.

그림 2A 및 2B에 도시된 바와 같이, 제 1 실시형태에 따른 반도체 디바이스는 반도체 기판 상에 제공되며, CMP에 의해 평탄화되는 제 1 배선 패턴(101w)및 제 1 배선 패턴(101w)과 동일한 재료로 이루어진 복수의 제 1 더미 패턴(101d)을 포함하는 제 1 층(101), 반도체 기판 상의 제 1 층(101)상에 제공되며, CMP에 의해 평탄화되는 제 2 배선 패턴(102w)및 제 2 배선 패턴(102w)과 동일한 재료로 이루어진 복수의 제 2 더미 패턴(102d)을 포함하는 제 2 층(102)및 반도체 기판 위의 제 2 층(102)상에 제공되며, CMP에 의해 평탄화되는 제 3 배선 패턴(103w)및 제 3 배선 패턴(103w)과 동일한 재료로 이루어진 복수의 제 3 더미 패턴(103d)을 포함하는 제 3 층(103)을 포함한다.

각각의 층(101 내지 103)에서 배선 패턴(101w 내지 103w)이 형성되지 않는 영역은 더미 패턴 형성가능 영역(10A 및 10B)이 되고, 더미 패턴(101d 내지 103d)은 각각의 더미 패턴 형성가능 영역에 배열된다.

제 1 실시형태에 따르면, 제 1 더미 패턴(101d)은 제 1 층(101)의 더미 패턴 형성가능 영역(10A)에 밀집되도록 배열된다. 제 2 더미 패턴(102d)은, 그 중심 축이 점선으로 도시된 것과 같이 반도체 기판에 수직인 방향으로 제 1 더미 패턴(101d)중 대응하는 더미 패턴의 중심 축과 일치하도록 더미 패턴 형성가능 영역(10A)에 배열된다. 이와 유사하게, 제 3 더미 패턴(103d)은, 그 중심 축이 반도체 기판에 수직인 방향으로 제 1 더미 패턴(101d)중 대응하는 더미 패턴의 중심 축과 일치하도록 배열된다.

제 1 더미 패턴(101d)이 더미 패턴 형성가능 영역(10B)에 형성되지 않기 때문에, 제 2 더미 패턴(102d)은 영역(10B)에 밀집되도록 배열된다. 제 3 더미 패턴(103d)은, 그 중심 축이 반도체 기판에 수직인 방향으로 제 2 더미 패턴(102d)중 대응하는 더미 패턴의 중심 축과 일치하도록 더미 패턴 형성가능 영역(10B)에 배열된다.

이와 같은 구성을 가짐으로써, 더미 패턴(101d 내지 103d)이 서로 중첩되는(서로 대응하는)경우에, 그림 2B에 도시된 것과 같이, 그 중심 축은 항상 서로 일치한다. 따라서 광학적으로 결함을 검출할 때에 검출 감도가 증가하는 경우에도, 더미 패턴으로 인한 무아레의 생성을 방지할 수 있다.

따라서 미세한 파티클 및 결함을 정확히 검출할 수 있으므로, 수율을 개선할 수 있다.

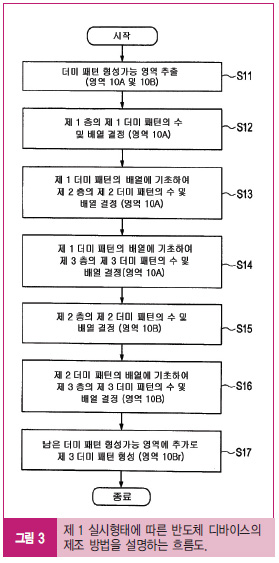

이하, 그림 2A, 2B 및 그림 3을 참조하여, 제 1 실시형태에 따른 반도체 디바이스의 제조 방법을 설명한다.

그림 3은 제 1 실시형태에 따른 반도체 디바이스의 제조 방법을 설명하는 흐름도로서, 그림 2A 및 2B에 도시된 반도체 디바이스(100)에 층을 형성하기 전에 제 1 층 내지 제 3 층(101 내지 103)에서의 더미 패턴(101d 내지 103d)의 수 및 배열을 결정하는 프로세스를 도시한다.

첫째로, 더미 패턴 형성가능 영역(10A 및 10B)을 추출한다(단계 S11). 그 다음에, 제 1 더미 패턴(101d)이 밀집 구조를 가져야 하는 제 1 층(101)을 포함한 더미 패턴 형성가능 영역(10A)에 밀집되도록, 제 1 더미 패턴(101d)의 수 및 배열을 결정한다(단계 S12). 그 다음에, 제 2 층(102)에 형성되는 제 2 더미 패턴(102d)의 중심 축이 반도체 기판에 수직인 방향으로 각각 제 1 더미 패턴(101d)의 중심 축과 일치하도록, 제 1 더미 패턴(101d)의 배열에 기초하여 제 2 더미 패턴(102d)의 수 및 배열을 결정한다(단계 S13). 또한, 제 3 층(103)에 형성되는 제 3 더미 패턴(103d)의 중심 축이 반도체 기판에 수직인 방향으로 각각 제 1 더미 패턴(101d)의 중심 축과 일치하도록, 제 1 더미 패턴(101d)의 배열에 기초하여 제 3 더미 패턴(103d)의 수 및 배열을 결정한다(단계 S14). 즉, 그림 2A의 영역(10A)에서 화살표로 도시된 것과 같이, 제 1 더미 패턴(101d)의 위치(중심 축)가 제 2 층(102)에 복제될 수 있고, 그 복제된 위치에 제 2 더미 패턴(102d)을 배치할 수 있는 경우에, 제 2 더미 패턴(102d)을 배열한다. 이와 유사하게, 제 1 더미 패턴(101d)의 위치(중심 축)가 제 3 층(103)에 복제될 수 있고, 그 복제된 위치에 제 3 더미 패턴(103d)을 배치할 수 있는 경우에, 제 3 더미 패턴(103d)을 배열한다.

다음으로, 제 2 더미 패턴(102d)이 밀집되도록, 더미 패턴 형성가능 영역(10B)에서 제 2 더미 패턴(102d)의 수 및 배열을 결정한다(단계 S15). 그 다음에, 제 3 층(103)에 형성되는 제 3 더미 패턴(103d)의 중심 축이 반도체 기판에 수직인 방향으로 각각 제 2 더미 패턴(102d)의 중심 축과 일치하도록, 제 2 더미 패턴(102d)의 배열에 기초하여 제 3 더미 패턴(103d)의 수 및 배열을 결정한다(단계 S16). 제 2 층이 밀집 구조를 갖더라도, 제 2 층에 비해 제 3 층의 평탄도가 크게 요구되는 경우에, 제 3 층은 밀집 구조를 가질 수 있고, 제 3 층에 기초하여 제 2 층(102)의 제 2 더미 패턴(102d)의 수 및 배열을 결정할 수 있다. 끝으로, 제 3 더미 패턴(103d)이 남은 더미 패턴 형성가능 영역(10Br)에 형성될 수 있기 때문에, 추가로 제 3 더미 패턴(103d)을 형성한다(단계 S17).

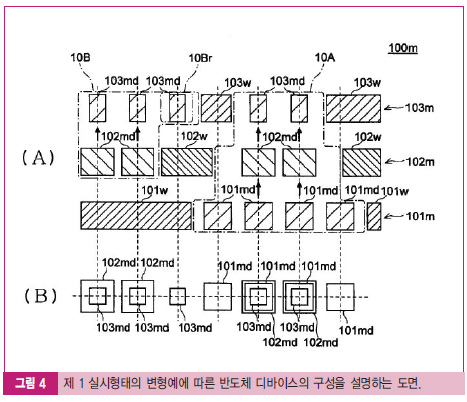

상술한 바와 같이, 각각의 층에 형성되는 더미 패턴의 수 및 배열을 결정한다. 각각의 층에 형성되는 더미 패턴의 평면 구성이 제 1 실시형태와 동일한 크기를 갖더라도, 각각의 층의 더미 패턴의 크기는 설계 표준에 따라 각각의 층에서 적절히 설정될 수 있다. 그러한 예는 그림 4A 및 4B에 도시되어 있다.

그림 4A 및 4B는 제 1 실시형태의 변형 예에 따른 반도체 디바이스(100m)의 구성을 설명하는 도면으로서, 그림 4A는 개략적인 단면도이고, 그림 4B는 반도체 디바이스(100m)를 그 상면에서 볼 때의 평면도이다. 단순화를 위해, 그림 4A에는 단지 배선 패턴과 CMP 더미 패턴만이 도시되어 있고, 반도체 기판이나 층간 유전체막 등은 생략되어 있으며, 그림 4B는 단지 더미 패턴만을 도시하고 있다. 그림 2A 및 2B에 도시된 것과 동일한 그림 4A 및 4B의 구성 요소는 동일 참조부호로 표시되고, 그 설명은 생략된다.

그림 4A 및 4B에 도시된 것과 같이, 제 1 층(101m)의 제 1 더미 패턴(101md), 제 2 층(102m)의 제 2 더미 패턴(102md)및 제 3 층(103m)의 제 3 더미 패턴(103md)은 반도체 디바이스(100m)에 있어서 상이한 평면 크기를 갖고 있고, 상이한 크기를 갖는 정사각형이다. 따라서 제 1 더미 패턴 내지 제 3 더미 패턴(101md 내지 103md)은, 그 중심 축이 서로 일치하도록 더미 패턴 형성가능 영역(10A)에 배열된다. 제 2 및 제 3 더미 패턴(102md 및 103md)은, 반도체 디바이스(100)와 같이 그 중심 축이 서로 일치하도록 더미 패턴 형성가능 영역(10B)에 배열된다.

그러나 평면도에 따르면, 그림 2B와 달리, 그 패턴들은 서로 완전히 일치하도록 중첩되지는 않는다. 그 대신에, 그림 4B에 도시된 것과 같이 동일한 중심 축을 갖도록, 상이한 크기를 갖는 패턴들이 중첩된다.

더미 패턴의 평면 구성은 정사각형에 한정되지 않고, 직사각형일 수 있고, 심지어 다각형일 수 있다. 상부 층과 하부 층의 더미 패턴이 서로 유사한 것이 바람직하다는 것에 주목하자. 상부 층과 하부 층의 더미 패턴의 중심 축이 서로 일치하는 경우에, 상부 층의 더미 패턴의 크기가 하부 층의 더미 패턴의 크기와 상이하더라도, 서로 중첩될 때의 상부 패턴과 하부 패턴 간의 차이(예를 들어, 수직 방향과 수평 방향의 차이)는 서로 일치하는 것이 바람직하다. 정사각형 패턴은 더미 패턴이 효율적으로 패킹되는 것을 가능하게 하는데, 즉, 밀집되는 것을 가능하게 한다. 따라서 칩 내의 밀도를 높은 정밀도로 보정할 수 있고, CMP 의 특징인 디싱 및 침식을 보다 효율적으로 억제할 수 있다.

이와 같은 구성을 갖는 반도체 디바이스(100m)에 따르면, 더미 패턴(101md 내지 103md)이 서로 중첩되는 경우에, 그 중심 축이 반도체 디바이스(100)와 같이 서로 일치한다. 따라서 광학적으로 결함을 검출할 때에 검출 감도가 증가하더라도, 더미 패턴으로 인한 무아레의 생성을 억제할 수 있다.

그림 4A 및 4B에 도시된 반도체 디바이스(100m)의 제조 방법은 반도체 디바이스(100)의 제조 방법과 동일하기 때문에, 그 설명은 생략된다.

제 1 층(101; 101m)에 형성되는 제 1 더미 패턴(101d; 101md)이 밀집되는 경우를 제 1 실시형태의 일 예로서 설명하였지만, 밀집 구조를 가져야 하는 층은 디바이스의 설계 표준에 따라 상이하다. 바닥 층의 더미 패턴을 항상 밀집시킬 필요는 없다. 디바이스의 설계 관리면에서 엄격한 의미로 요구되는 평탄도를 갖는 층을 밀집 구조를 갖는 것으로 결정한다. 따라서 본 발명의 제 2 실시형태는 그림 5A, 5B 및 그림 6을 참조하여 제 2 층이 밀집 구조를 갖는 경우를 설명한다.

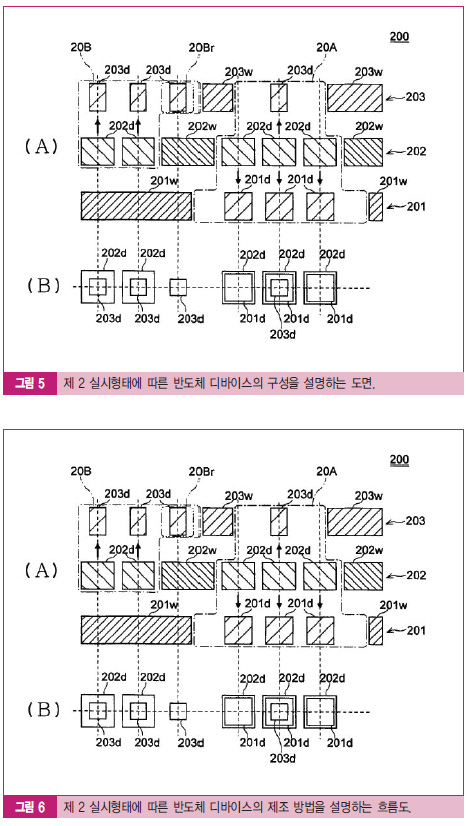

그림 5A 및 5B는 제 2 실시형태에 따른 반도체 디바이스(200)의 구성을 설명하는 도면으로서, 그림 5A는 개략적인 단면도이고, 그림 5B는 반도체 디바이스(200)를 그 상면에서 볼 때의 평면도이다. 단순화를 위해, 그림 5A에는 단지 배선 패턴과 CMP 더미 패턴만이 도시되어 있고, 반도체 기판이나 층간 유전체막 등은 생략되어 있으며, 그림 5B는 단지 더미 패턴만을 도시하고 있다.

그림 5A 및 5B에 도시된 것과 같이, 제 2 실시형태에 따른 반도체 디바이스(200)는 반도체 기판 상에 제공되며, CMP에 의해 평탄화되는 제 1 배선 패턴(201w)및 제 1 배선 패턴(201w)과 동일한 재료로 이루어진 복수의 제 1 더미 패턴(201d)을 포함하는 제 1 층(201), 반도체 기판 상의 제 1 층(201)상에 제공되며, CMP에 의해 평탄화되는 제 2 배선 패턴(202w)및 제 2 배선 패턴(202w)과 동일한 재료로 이루어진 복수의 제 2 더미 패턴(202d)을 포함하는 제 2 층(202)및 반도체 기판 위의 제 2 층(202)상에 제공되며, CMP에 의해 평탄화되는 제 3 배선 패턴(203w)및 제 3 배선 패턴(203w)과 동일한 재료로 이루어진 복수의 제 3 더미 패턴(203d)을 포함하는 제 3 층(203)을 포함한다.

각각의 층(201 내지 203)에서 배선 패턴(201w 내지 203w)이 형성되지 않는 영역은 더미 패턴 형성가능 영역(20A 및 20B)이 되고, 더미 패턴(201d 내지 203d)은 각각의 영역에 배열된다. 제 2 실시형태에 따르면, 제 2 더미 패턴(202d)은 제 2 층(202)의 더미 패턴 형성가능 영역(20A 및 20B)에 밀집되도록 배열된다.

제 1 더미 패턴(201d)은, 그 중심 축이 반도체 기판에 수직인 방향으로 제 2 더미 패턴(202d)중 대응하는 더미 패턴의 중심 축과 일치하도록 더미 패턴 형성가능 영역(20A)에 배열된다. 이와 유사하게, 제 3 더미 패턴(203d)은, 그 중심 축이 반도체 기판에 수직인 방향으로 제 2 더미 패턴(202d)중 대응하는 더미 패턴의 중심 축과 일치하도록 배열된다. 이와 같은 구성을 가짐으로써, 더미 패턴(201d 내지 203d)이 서로 중첩되도록 배열되는 경우에, 그림 5B에 도시된 것과 같이 그 중심 축이 항상 서로 일치한다. 따라서 제 2 실시형태는 제 1 실시형태와 동일한 효과를 달성할 수 있다.

이하, 그림 5A, 5B 및 그림 6을 참조하여, 제 2 실시형태에 따른 반도체 디바이스(200)의 제조 방법을 설명한다.

그림 6은 제 2 실시형태에 따른 반도체 디바이스(200)의 제조 방법을 설명하는 흐름도로서, 그림 5A 및 5B에 도시된 반도체 디바이스(200)에 층을 형성하기 전에 제 1 층 내지 제 3 층(201 내지 203)의 더미 패턴(201d 내지 203d)의 수 및 배열을 결정하는 프로세스를 도시한다.

첫째로, 더미 패턴 형성가능 영역(20A 및 20B)을 추출한다(단계 S21). 그 다음에, 제 2 더미 패턴(202d)이 밀집 구조를 가져야 하는 제 2 층(202)을 포함한 더미 패턴 형성가능 영역(20A 및 20B)에 밀집되도록, 제 2 더미 패턴(202d)의 수 및 배열을 결정한다(단계 S22). 제 1 층(201)에 형성되는 제 1 더미 패턴(201d)의 중심 축이 반도체 기판에 수직인 방향으로 각각 제 2 더미 패턴(202d)의 중심 축과 일치하도록, 제 2 더미 패턴(202d)의 배열에 기초하여 제 1 더미 패턴(201d)의 수 및 배열을 결정한다(단계 S23). 또한, 제 3 층(203)에 형성되는 제 3 더미 패턴(203d)의 중심 축이 반도체 기판에 수직인 방향으로 각각 제 2 더미 패턴(202d)의 중심 축과 일치하도록, 제 2 더미 패턴(202d)의 배열에 기초하여 제 3 더미 패턴(203d)의 수 및 배열을 결정한다(단계 S24). 즉, 그림 5A의 영역(20A)의 화살표에 의해 도시된 것과 같이, 제 2 더미 패턴(202d)의 위치(중심 축)가 제 1 층(201)에 복제될 수 있고, 그 복제된 위치에 제 1 더미 패턴(201d)을 배치할 수 있는 경우에, 제 1 더미 패턴(201d)을 배열한다. 이와 유사하게, 그림 5A의 영역(20A 및 20B)의 화살표에 의해 도시된 것과 같이, 제 2 더미 패턴(202d)의 위치(중심 축)가 제 3 층(203)에 복제될 수 있고, 그 복제된 위치에 제 3 더미 패턴(203d)을 배치할 수 있는 경우에, 제 3 더미 패턴(203d)을 배열한다. 남은 더미 패턴 형성가능 영역(20Br)에 제 3 더미 패턴(203d)을 형성할 수 있기 때문에, 제 3 더미 패턴(203d)을 추가로 형성한다(단계 S25).

제 1 실시형태와 제 2 실시형태에서는 배선 패턴이 형성되는 배선 층에 CMP 더미 패턴을 형성하는 경우를 설명하였지만, CMP 더미 패턴은 단지 배선 층에만 형성될 필요는 없다. 본 발명의 제 3 실시형태는 반도체 기판에 제공되는 소자 분리 영역으로서 STI(Shallow Trench Isolation)영역에 CMP 더미 패턴이 제공되는 경우를 설명한다.

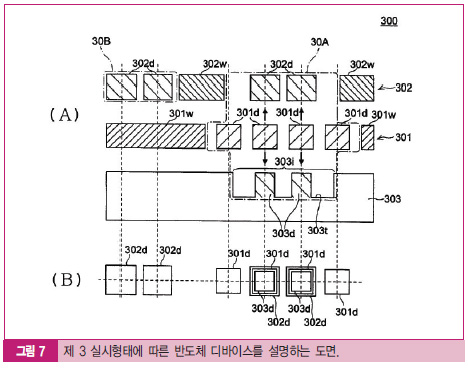

그림 7A 및 7B는 제 3 실시형태에 따른 반도체 디바이스(300)를 설명하는 도면으로서, 그림 7A는 개략적인 단면도이고, 그림 7B는 반도체 디바이스(300)를 그 상면에서 볼 때의 평면도이다. 단순화를 위해, 그림 7A에는 층간 유전체막 등은 생략되어 있으며, 그림 7B는 단지 더미 패턴만을 도시하고 있다.

그림 7A 및 7B에 도시된 것과 같이, 제 3 실시형태에 따른 반도체 디바이스(300)는 반도체 기판(303)상에 제공되며, CMP에 의해 평탄화되는 제 1 배선 패턴(301w)및 제 1 배선 패턴(301w)과 동일한 재료로 이루어진 복수의 제 1 더미 패턴(301d)을 포함하는 제 1 층(301), 반도체 기판 상의 제 1 층(301)상에 제공되며, CMP에 의해 평탄화되는 제 2 배선 패턴(302w)및 제 2 배선 패턴(302w)과 동일한 재료로 이루어진 복수의 제 2 더미 패턴(302d)을 포함하는 제 2 층,(302)및 각각이 반도체 기판(303)의 소자 분리 영역(303i) 내의 넓은 STI 영역(303t)과 그 STI 영역(303t)내의 반도체 기판(303)의 일부로 형성되는 복수의 제 3 더미 패턴(303d)을 포함한다.

제 1 및 제 2 층(301 및 302)에 배선 패턴(301w 및 302w)이 형성되지 않는 영역은 더미 패턴 형성가능 영역(30A 및 30B)이 된다. 반도체 기판(303)의 넓은 STI 영역(303t)의 안쪽 부분은 더미 패턴 형성 가능영역(30A)이 된다. 더미 패턴(301d 내지 303d)은 각각의 영역에 배열된다. 제 3 실시형태에 따르면, 제 1 더미 패턴(301d)은 제 1 층(301)의 더미 패턴 형성가능 영역(30A)에 밀집되도록 배열된다.

제 2 더미 패턴(302d)은, 그 중심 축이 점선에 의해 도시된 것과 같이 반도체 기판(303)에 수직인 방향으로 제 1 더미 패턴(301d)중 대응하는 더미 패턴의 중심 축과 일치하도록 더미 패턴 형성가능 영역(30A)에 배열된다. 이와 유사하게, 제 3 더미 패턴(303d)은, 그 중심 축이 반도체 기판(303)에 수직인 방향으로 제 1 더미 패턴(301d)중 대응하는 더미 패턴의 중심 축과 일치하도록 배열된다. 제 1 더미 패턴(301d)이 더미 패턴 형성가능 영역(30B)에 형성되지 않기 때문에, 제 2 더미 패턴(302d)은 이 영역에 밀집되도록 배열된다.

각각의 배선 층에 제공되는 더미 패턴(301d 및 302d)뿐만 아니라 반도체 기판(303)에 제공되는 더미 패턴(303d)도, 그림 7B에 도시된 것과 같이 제 3 실시형태에서 서로 중첩되는 경우에, 동일한 중심 축을 갖는다. 따라서 제 3 실시형태는 또한 제 1 실시형태 및 제 2 실시형태와 동일한 효과를 달성할 수 있다.

이하, 그림 7A, 7B 및 그림 8을 참조하여, 제 3 실시형태에 따른 반도체 디바이스(300)제조 방법을 설명한다. 그림 8은 제 3 실시형태에 따른 반도체 디바이스(300)의 제조 방법을 설명하는 흐름도로서, 그림 7A 및 7B 에 도시된 반도체 디바이스(300)에 각각의 층 및 소자 분리 영역을 형성하기 전에 제 1 및 제 2 층(301 및 302)과 소자 분리 영역(303i)의 더미 패턴(301d 내지 303d)의 수 및 배열을 결정하는 프로세스를 도시한다.

첫째로, 더미 패턴 형성가능 영역(30A 및 30B)을 추출한다(단계 S31). 다음으로, 제 1 더미 패턴(301d)이 밀집되도록, 밀집 구조를 가져야 하는 제 1 층(301)을 포함하는 더미 패턴 형성가능 영역(30A)에서 제 1 더미 패턴(301d)의 수 및 배열을 결정한다(단계 S32). 그 다음에, 제 2 층(302)에 형성되는 제 2 더미 패턴(302d)의 중심 축이 반도체 기판(303)에 수직인 방향으로 각각 제 1 더미 패턴(301d)의 중심 축과 일치하도록, 제 1 더미 패턴(301d)의 배열에 기초하여 제 2 더미 패턴(302d)의 수 및 배열을 결정한다.(단계 S33). 그 다음에, 반도체 기판(303)에 형성되는 제 3 더미 패턴(303d)의 중심 축이 반도체 기판(303)에 수직인 방향으로 각각 제 1 더미 패턴(301d)의 중심 축과 일치하도록, 제 1 더미 패턴(301d)의 배열에 기초하여 제 3 더미 패턴(303d)의 수 및 배열을 결정한다(단계 S34). 즉, 그림 7A의 영역(30A)에서 화살표로 도시된 것과 같이, 제 1 더미 패턴(301d)의 위치(중심 축)가 제 2 층(302)에 복제될 수 있고, 그 복제된 위치에 제 2 더미 패턴(302d)을 배치할 수 있는 경우에, 제 2 더미 패턴을 배열한다. 이와 유사하게, 제 1 더미 패턴(301d)의 위치(중심 축)가 반도체 기판(303)에 복제될 수 있고, 그 복제된 위치에 각각 제 3 더미 패턴(303d)을 배치할 수 있는 경우에, 제 3 더미 패턴을 배열한다. 끝으로, 제 2 더미 패턴이 밀집되도록, 더미 패턴 형성가능 영역(30B)에서 제 2 더미 패턴(302d)의 수 및 배열을 결정한다(단계 S35).

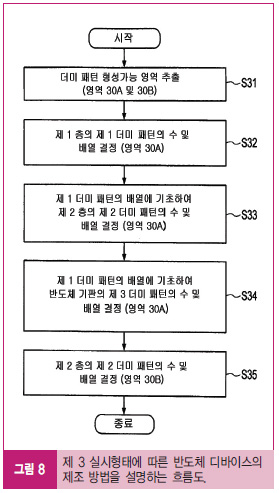

다음으로, 그림 9A, 9B 및 그림 10을 참조하여, 본 발명의 제 4 실시형태는 반도체 기판 상에 불투과성막이 제공되는 경우를 설명한다. 그림 9A 및 9B는 제 4 실시형태에 따른 반도체 디바이스(400)의 구성을 설명하는 도면으로서, 그림 9A는 개략적인 단면도이고, 그림 9B는 반도체 디바이스(400)를 그 상면에서 볼 때의 평면도이다. 단순화를 위해, 그림 9A에는 단지 배선 패턴과 CMP 더미 패턴만이 도시되어 있고, 반도체 기판이나 층간 유전체막 등은 생략되어 있으며, 그림 9B는 단지 더미 패턴만을 도시하고 있다.

그림 9A 및 9B에 도시된 것과 같이, 제 4 실시형태에 따른 반도체 디바이스(400)는 반도체 기판 상에 제공되며, CMP에 의해 평탄화되는 제 1 배선 패턴(401w) 및 제 1 배선 패턴(401w)과 동일한 재료로 이루어진 복수의 제 1 더미 패턴(401d)을 포함하는 제 1 층(401), 반도체 기판 상의 제 1 층(401)상에 제공되며, CMP에 의해 평탄화되는 제 2 배선 패턴(402w)및 제 2 배선 패턴(402w)과 동일한 재료로 이루어진 복수의 제 2 더미 패턴(402d)을 포함하는 제 2 층(402), 반도체 기판과 제 1 층 사이에 제공되며, CMP에 의해 평탄화되는 제 3 배선 패턴(403w)및 제 3 배선 패턴(403w)과 동일한 재료로 이루어진 복수의 제 3 더미 패턴(403d)을 포함하는 제 3 층(403)및 제 3 층(403)과 제 1 층(401)사이의 불투과성막(410)을 포함한다. 불투과성막(410)의 예로는 절연막으로서 이용되는 비정질 탄소와 커패시터용 판 전극으로서 이용되는 금속막이 있다.

각각의 층(401 내지 403)에서 배선 패턴(401w 내지 403w)이 형성되지 않는 영역은 더미 패턴 형성가능 영역(40A 및 40B)이 되고, 더미 패턴(401d 내지 403d)은 각각의 영역에 배열된다. 제 4 실시형태에 따르면, 제 1 더미 패턴(401d)은 제 1 층(401)의 더미 패턴 형성가능 영역(40A 및 40B)에 밀집되도록 배열된다. 제 2 더미 패턴(402d)은, 그 중심 축이 점선에 의해 도시된 것과 같이 반도체 기판에 수직인 방향으로 제 1 더미 패턴(401d) 중 대응하는 더미 패턴의 중심 축과 일치하도록, 더미 패턴 형성가능 영역(40A 및 40B)에 배열된다.

한편, 불투과성막(410)아래의 제 3 층(403)에서, 제 3 더미 패턴(403d)은 제 1 및 제 2 더미 패턴(401d 및 402d)의 배열에 기초하지 않고 더미 패턴 형성가능 영역(40A)에 밀집되도록 배열된다. 이는, 검사 광이 불투과성막(410)을 통해 전달되지 않으므로 불투과성막(410)아래의 더미 패턴이 광학 결함 검사의 결과에 영향을 미치지 않기 때문이다. 따라서 제 3 층(403)의 제 3 더미 패턴(403d)의 수 및 배열은 제 1 및 제 2 더미 패턴(401d 및 402d)에 관계없이 결정될 수 있다. 따라서 그림 9B에 도시된 것과 같이, 제 1 더미 패턴(401d)및 제 2 더미 패턴(402d)이 서로 중첩되도록 배열되는 경우에, 그 중심 축은 항상 서로 일치한다. 제 3 더미 패턴(403d)은, 그 중심 축이 반도체 기판에 수직인 방향으로(제 3 더미 패턴(403d)이 더미 패턴(401d) 상에서 적어도 부분적으로 중첩되는 경우에) 제 1 더미 패턴(401d) 중 대응하는 더미 패턴의 중심 축으로부터 시프트되도록 배열된다. 이와 같은 구성을 가짐으로써, 결함을 광학적으로 검출할 때에 더미 패턴으로 인한 무아레의 생성을 방지할 수 있고, 불투과성막(410)아래의 층에 더미 패턴을 배열할 수 있으므로 CMP에 의한 평탄도가 더욱 개선된다.

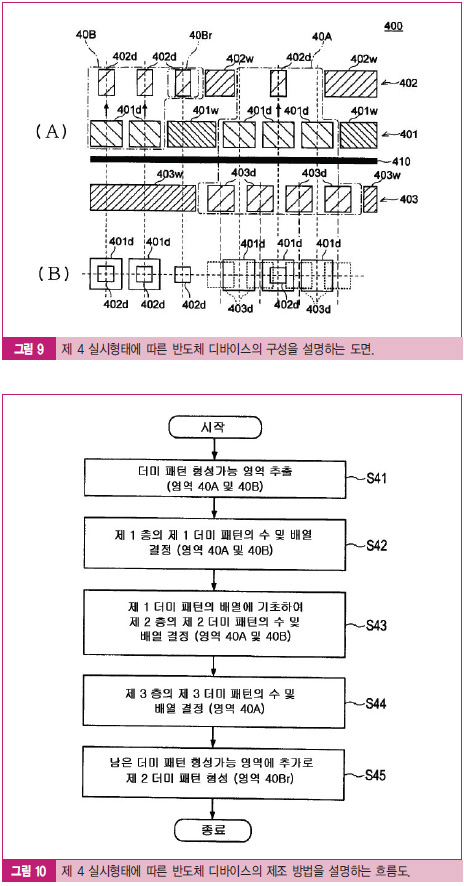

이하, 그림 9A, 9B 및 그림 10을 참조하여, 제 4 실시형태에 따른 반도체 디바이스(400)의 제조 방법을 설명한다.

그림 10은 제 4 실시형태에 따른 반도체 디바이스(400)의 제조 방법을 설명하는 흐름도로서, 그림 9A 및 9B 에 도시된 반도체 디바이스(400)에 층을 형성하기 전에 제 1 층 내지 제 3 층(401 내지 403)에서 더미 패턴(401d 내지 403d)의 수 및 배열을 결정하는 프로세스를 도시한다.

첫째로, 더미 패턴 형성가능 영역(40A 및 40B)을 추출한다(단계 S41). 그 다음에, 제 1 더미 패턴(401d)이 밀집되도록, 밀집 구조를 가져야 하는 제 1 층(401)의 더미 패턴 형성가능 영역(40A 및 40B)에서 제 1 더미 패턴(401d)의 수 및 배열을 결정한다(단계 S42). 그 다음에, 제 2 더미 패턴(402d)의 중심 축이 반도체 기판에 수직인 방향으로 각각 제 1 더미 패턴(401d)의 중심 축과 일치하도록, 제 1 더미 패턴(401d)의 배열에 기초하여 제 2 더미 패턴(402d)의 수 및 배열을 결정한다(단계 S43). 그 다음에, 제 3 더미 패턴(403d)이 밀집되도록, 제 3 층의 더미 패턴 형성가능 영역(40A)에서 제 3 더미 패턴(403d)의 수 및 배열을 결정한다(단계 S44). 끝으로, 남은 더미 패턴 형성가능 영역(40Br)에 제 2 더미 패턴(402d)을 형성할 수 있으므로, 그 영역에 추가로 제 2 더미 패턴(402d)을 형성한다(단계 S45).

제 1 실시형태 내지 제 4 실시형태에서는 각각의 층의 더미 패턴의 중심 축이 서로 일치하였지만, 그 중심 축이 서로 일치할 필요는 없다. 다음으로, 본 발명의 제 5 실시형태는 중심 축이 서로 일치하지 않는 더미 패턴을 포함하는 반도체 디바이스를 설명한다.

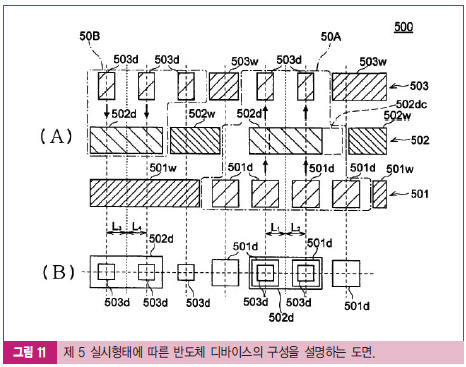

그림 11A 및 11B는 제 5 실시형태에 따른 반도체 디바이스(500)의 구성을 설명하는 도면으로서, 그림 11A는 개략적인 단면도이고, 그림 11B는 반도체 디바이스(500)를 그 상면에서 볼 때의 평면도이다. 단순화를 위해, 그림 11A에는 단지 배선 패턴과 CMP 더미 패턴만이 도시되어 있고, 반도체 기판이나 층간 유전체막 등은 생략되어 있으며, 그림 11B 는 단지 더미 패턴만을 도시하고 있다.

그림 11A 및 11B에 도시된 것과 같이, 제 5 실시형태에 따른 반도체 디바이스(500)는 반도체 기판 상에 제공되며, CMP에 의해 평탄화되는 제 1 배선 패턴(501w)및 제 1 배선 패턴(501w)과 동일한 재료로 이루어진 복수의 제 1 더미 패턴(501d)을 포함하는 제 1 층(501), 반도체 기판 상의 제 1 층(501)상에 제공되며, CMP에 의해 평탄화되는 제 2 배선 패턴(502w)및 제 2 배선 패턴(502w)과 동일한 재료로 이루어진 복수의 제 2 더미 패턴(502d)을 포함하는 제 2 층(502) 및 반도체 기판 위의 제 2 층(502)상에 제공되며, CMP에 의해 평탄화되는 제 3 배선 패턴(503w) 및 제 3 배선 패턴(503w)과 동일한 재료로 이루어진 복수의 제 3 더미 패턴(503d)을 포함하는 제 3 층(503)을 포함한다.

각각의 층(501 내지 503)에 배선 패턴(501w 내지 503w)이 형성되지 않는 영역이 더미 패턴 형성가능 영역(50A 및 50B)이 되고, 더미 패턴(501d 내지 503d)이 각각의 영역에 배열된다. 제 1 더미 패턴(501d)은 제 1 층(501)의 더미 패턴 형성가능 영역(50A)에 밀집되도록 배열된다. 직사각형 제 2 더미 패턴(502d)은 제 5 실시형태에 따라 제 2 층(502)의 더미 패턴 형성가능 영역(50A)에 배열된다.(점선으로 도시된)제 2 더미 패턴(502d)의 중심 축은(점선으로 도시된)제 1 더미 패턴(501d)의 중심 축과 일치하지 않는다. 즉, 하나의 직사각형 제 2 더미 패턴(502d)은 2 개의 제 1 더미 패턴(501d)에 대해 제공된다.

2 개의 제 1 더미 패턴(501d)과 하나의 직사각형 제 2 더미 패턴(502d)간의 관계는, 점선의 좌측 상의 제 1 더미 패턴(501d)의 중심 축과 제 2 더미 패턴(502d)의 중심 축 간의 거리 L1 이 점선의 우측 상의 제 1 더미 패턴(501d)의 중심 축과 제 2 더미 패턴(502d)의 중심 축 간의 거리 L2 와 같다는 것이다. 제 3 더미 패턴(503d)은, 그 중심 축이 제 1 실시형태 내지 제 4 실시형태와 같이 반도체 기판에 수직인 방향으로 제 1 더미 패턴(501d)중 대응하는 더미 패턴의 중심 축과 일치하도록, 더미 패턴 형성가능 영역(50A)에 배열된다. 제 1 더미 패턴(501d)이 더미 패턴 형성가능 영역(50B)에 형성되지 않기 때문에, 이 영역에서 제 3 더미 패턴(503d)은 밀집되도록 배열된다. 직사각형 제 2 더미 패턴(502d)은 제 2 층(502)의 더미 패턴 형성 가능 영역(50B)에 배열된다.(점선으로 도시된)더미 패턴(502d)의 중심 축은(점선으로 도시된) 제 3 더미 패턴(503d)의 중심 축과 일치하지 않는다. 즉, 하나의 직사각형 형상 제 2 더미 패턴(502d)은 2개의 제 3 더미 패턴(503d)에 대해 제공된다. 2 개의 제 3 더미 패턴(503d)과 하나의 직사각형 제 2 더미 패턴(502d)간의 관계는, 점선의 좌측 상의 제 3 더미 패턴(503d)의 중심 축과 제 2 더미 패턴(502d)의 중심 축 간의 거리 L3 이 점선의 우측 상의 제 3 더미 패턴(503d)의 중심 축과 제 2 더미 패턴(502d)의 중심 축 간의 거리 L4 와 같다는 것이다.

상부 층과 하부 층의 더미 패턴 간에 상술한 바와 같이 소정의 관계가 확립되기 때문에, 상기 구성은 광학적으로 결함을 검출할 때에 더미 패턴으로 인한 무아레의 생성을 억제할 수 있다. 따라서 단지 미세한 파티클과 결함만을 정확하게 검출할 수 있으므로, 수율을 개선할 수 있다.

제 5 실시형태는 제 2 더미 패턴(502d)의 폭(평면 구성에서 더 긴 변)을 설계 표준에 따라 제 3 더미 패턴(503d)의 폭 또는 제 1 더미 패턴(501d)의 폭보다 2 배 넓게 설정하는 경우를 나타낸다. 제 2 더미 패턴(502dc)을 그 중심 축이 제 1 내지 제 4 실시형태와 같이 제 1 더미 패턴(501d)의 중심 축과 일치하도록 더미 패턴 형성가능 영역(50A)에 배열하는 경우에, 제 2 더미 패턴은 그림 11A의 긴 점선에 의해 도시된 것과 같이 하나의 배선(502w)에 접근하도록 배열되고, 더미 패턴이 형성되지 않는 넓은 영역은 그 배선에 접근하는 측의 반대편에 있는 더미 패턴 측에 남아 있게 되므로, 디싱 등이 일어난다. 따라서 밀집되는 일 층에서의 더미 패턴보다 2배, 3배(또한 그 이상)더 큰 더미 패턴을 다른 층에 제공해야 하는 경우에는, 제 5 실시형태의 구성을 갖는 것이 바람직하다.

본 발명은 상기 실시형태에 한정되는 것이 아니라, 본 발명의 범위 및 사상으로부터 일탈함이 없이 변형 및 수정될 수도 있다는 것을 알 수 있다. 제 1 실시형태는 모든 더미 패턴의 평면 크기가 동일한 경우를 설명하였고, 제 2 내지 제 4 실시형태는 각각의 층의 더미 패턴의 평면 크기가 서로 상이한 경우를 설명하였지만, 본 발명은 이에 한정되지 않는다. 예를 들어, 복수의 층 중에서 적어도 2개의 층의 더미 패턴의 평면 크기가 동일하고, 다른 층의 더미 패턴의 평면크기가 서로 상이한 구성을 갖는 것이 가능하다.

기본적으로, 상부 층과 하부 층에서 서로 대응하는 더미 패턴의 중심 축이 제 1 내지 제 4 실시형태에서 설명된 것과 같이 서로 일치하는 것이 바람직하다. 그러나 결함 검사에 있어서 미세한 파티클과 결함을 정확하게 검출할 수 있는 한, 중심 축이 서로 일치하지 않는 더미 패턴이 존재하더라도 문제가 없다.

상기 실시형태에서는 층들 중 임의의 층에서 더미 패턴 밀집되어야 하는 경우를 설명하였지만, 그림 1을 참조하여 처음에 설명된 것과 같이 층들 중 임의의 층에서는 더미 패턴이 밀집될 필요가 없다. 더미 패턴이 밀집되어야 하는 임의의 층이 제공되지 않는 경우에는, 미리 설정된 높은 우선순위를 갖는 층에서 더미 패턴이 밀집되는 것으로 충분하다.