다이본드용 땜납 재료를 사용하여 형성된 표면 실장 부품을, 실장용 땜납 재료를 사용하여 프린트 기판에 솔더링할 때라도, 다이본드용 땜납 재료의 용해가 일어나지 않도록 하였다. 다이패드용 땜납 재료로서, Cu의 함유량이 소정값 이하인 Sn을 주성분으로 하는 (Sn-Sb)계의 고융점 땜납 재료를 사용하여 형성된 표면 실장 부품을, 회로 기판의 기판 단자부에 도포된 실장용 땜납 재료로서, (Sn-Ag-Cu-Bi)계 땜납 재료를 사용하여 솔더링한다. 다이본드용 땜납 재료의 고상선 온도는 243℃이고, 실장용 땜납 재료의 액상선 온도는 215 내지 220℃ 정도이므로, 리플로우 노의 가열 온도(240℃ 이하)에 의해서도 다이본드용 땜납 재료는 용해되지 않는다.

배경 기술

일반적으로 반도체의 패키징은, 회로 소자를 리드 프레임의 다이패드 전극부(아일랜드부)에 다이본딩하여 접합(브레이징)한 후, 수지 성형된 것이다. 열 발생이 큰 반도체 소자 등의 회로 소자의 경우, 다이본딩에는 납재로서 땜납(이하, 땜납 재료라 함)이 사용되고 있다. 이 땜납 재료로서 종래부터 (Sn-Pb)계를 기본으로 한 땜납 재료가 사용되고 있다. 이 중에서도 (Pb-5질량%Sn)(이후 질량% 생략) 근방에서, 융점이 300℃ 전후로 되는 비교적 고온인 땜납 재료가 사용되고 있다. 그 이유는, 면 실장 부품을 프린트 기판에 실장할 때의 땜납 재료(실장용 땜납 재료)의 가열 조건이 240℃ 내지 260℃이고, 또한 수 내지 100초간 가열 처리되므로, 다이본드용 땜납 재료가 용출되지 않도록 할 필요가 있기 때문이다.

회로 소자가 동작하고 있을 때에는 온도가 상승하고, 비동작 상태일 때에는 상온으로 되므로, 땜납 재료의 접합부는 큰 온도 변화를 받게 된다. 한편, 회로 소자와 리드 프레임의 다이패드 전극부는 열팽창 계수가 다르므로, 그 열팽창 계수의 차이에 기인하여 땜납 재료의 접합부는 온도 변화에 수반되는 반복 변형을 받고, 반복되는 이 변형에 의한 피로에 의해, 땜납 재료 접합부에 균열이 발생하는 경우가 있다. 따라서 이 균열의 진전에 수반하여, 땜납 재료 접합부에 있어서의 전기적 접속의 신뢰성을 저하시키는 경우가 있다. 이러한 이유로부터, 최근 (Pb-5Sn) 근방의 조성에, Ag, In, Bi, Cu 등의 금속을 미량 함유시킨 땜납 재료가 제안되어 있다. 그러나 이들을 다이본드용 땜납 재료로서 사용하여 열팽창 계수가 크게 다른 부재를 접합한 경우라도, 땜납 접합부에 가해지는 변형이 과대해져, 열사이클 성능에 현저한 개선 효과가 보이지 않는다고 하는 문제가 있었다.

이것에 더하여, 최근에는 (Pb-Sn)계 땜납 재료에 포함되어 있는 Pb의 인체에의 영향에 관심이 모아져, Pb를 포함하는 제품을 폐기하는 것에 따른 지구 환경의 오염, 생물에의 영향을 저감시키는 것이 과제로 되어 있다.

환경오염 등을 저감시키기 위해, 무연 땜납 재료가 요구되고 있다. 그로 인해 면 실장 부품을 프린트 기판 등의 회로 기판에 면 실장할 때에 사용되는 실장용 땜납 재료로서는, 최근 무연 땜납 재료(Pb 프리 땜납 재료)가 사용되고 있다. 또한, 최근까지는 반도체 소자를 리드 프레임의 다이패드 전극부에 접합할 때에 사용되고 있는 다이본드용 땜납 재료로서는, 납 함유 땜납 재료가 사용되고 있었지만, 이 다이본드용 땜납 재료에 있어서도, Pb-프리 땜납 재료의 사용이 요구되고 있다. 여기서, Pb를 85질량% 이상 함유하는 납 함유 땜납 재료의 경우에는, 그 고상선 온도가 260℃ 이상인 것이 많아 비교적 고온이므로, 반도체 소자 등의 회로 소자에의 악영향이 생각된다. 그것은, 이 경우 리플로우 노(爐)에서 사용하는 가열 온도는, 고상선 온도(260℃) 이상이 되므로, 땜납 재료 접합부나 다이패드 전극부에 균열이 발생하거나, 리드 프레임과 몰드의 계면에서 박리가 발생한 등의 상태에서 솔더링 처리되게 되기 때문이다. 이러한 관점에서 회로 소자와 리드 프레임의 접합에 사용하는 다이본드용 땜납 재료로서도, 저용융 온도이며 또한 Pb 프리의 땜납 재료를 사용할 수 있도록 연구가 행해지고 있다.

납 함유 땜납 재료보다도 고상선 온도가 낮은 무연 땜납 재료로서는, (Sn-Ag)계 땜납 재료, (Sn-Cu)계 땜납 재료, (Sn-Sb)계 땜납 재료 등이 알려져 있지만, 그 중, 리플로우 노 내의 가열 온도보다도 높은 고상선 온도의 고융점 땜납 재료로서는, (Sn-Sb)계 고융점 땜납 재료가 알려져 있다(특허문헌 1, 일본 특허 출원 공개 제2001-284792호 공보). 특허문헌 1에 개시된 (Sn-Sb)계 고융점 땜납 재료는, 표면 실장 부품(IC 패키지)을 프린트 기판에 실장할 때의 가열 온도에서도 다이본딩 시에 사용한 고융점의 땜납 재료 접합부에 보이드 등이 생성되지 않도록 그 조성비를 고안한 것이다.

발명의 내용

해결하려는 과제

그러나 상술한 특허문헌 1에 개시되어 있는 고융점 땜납 재료에서는, 특히 Sb의 함유량이 많다. Sb의 함유량이 많으면 고상선 온도가 상승하는 경향이 있지만, 그 반면 크랙 등을 일으키기 쉬워져, 땜납 재료의 기계적 신뢰성이 저하되는 경향이 있는 것이 여러 종류의 실험에 의해 확인되었다. 즉, 표면 실장 부품을 회로 기판에 솔더링할 때에, 다이본드용 땜납 재료 등에 의해 내부 잠열로서 흡열되므로, 열이 충분히 면 실장 부품이나 실장용 땜납 재료에 전달되지 않아, 가열 부족이라고 하는 현상이 일어나기 쉽다. 이 결과, 실장용 땜납의 젖음성이 나빠져, 보이드 발생을 야기하게 되고, 면 실장 부품을 회로 기판에 실장하는 경우의 신뢰성도 흔들리게 되기 때문이다.

상술한 (Sn-Sb)계 땜납 재료는, 확실히 납 함유 땜납 재료보다도 그 고상선 온도가 낮지만, 리플로우 노에 있어서 사용하는 처리 온도(가열 온도)와의 온도차는 그다지 없으므로, 실장용 땜납 재료로서는 가능한 한 그 고상선 온도가 낮은 땜납 재료를 사용할 필요가 있다. 이와 함께, (Sn-Sb)계 땜납 재료를 사용할 때에는 이하와 같은 문제도 야기한다.

(Sn-Sb)계 땜납 재료 성분 중에 Cu 등의 불순물이 포함되어 있으면, 땜납 재료의 고상선 온도가 10℃ 내지 20℃ 정도 저하되어 버린다. 예를 들어, (Sn-10Sb)계 땜납 재료에서는 그 고상선 온도가 243℃인 것에 대해, Cu를 함유한 (Sn-10Sb)계 땜납 재료에서는 그 고상선 온도가 10℃ 정도 저하되는 경향이 있다.

땜납 재료의 주성분인 Sn으로서 99.9%의 순도의 Sn을 사용하였다고 해도 나머지 0.1%는 불순물이다. 따라서 함유하는 불순물이 Cu였을 때에는 당연히 고상선 온도의 저하를 초래하는 경우가 있다. Cu의 함유량을 나타내는 JIS 규격은 0.02%이지만, 0.02% 정도의 Cu 함유에 있어서도 고상선 온도는 극단적으로 저하되는 것이 알려져 있다. 마찬가지로, 반도체 소자를 리드 프레임의 다이패드 전극부(땜납 접합부)에 솔더링하는 공정에 있어서는, 리드 프레임 중으로부터 Cu가 용출되어 접합 땜납 재료 중에 혼입되기 쉬운 환경 하에 있으므로, 이것에 의해서도 땜납 재료의 고상선 온도가 저하되게 된다. 예를 들어, 리드 프레임이 Cu를 주성분으로 하는 것일 때, 리플로우 솔더링 시에 리드 프레임이 가열되므로, 주 성분의 Cu가 용출(0.1 내지 2질량% 정도)되어, 이것이 다이본드용 땜납 재료 중에 혼입된다.

용해된 다이본드용 땜납 재료 중에 Cu 등이 용출되면, Cu를 함유한 땜납 재료를 사용한 것과 동일한 결과가 되므로, 그 고상선 온도가 저하되어 버린다. 고상선 온도가 저하되는 것은, 상술한 바와 같이 표면 실장 부품을 회로 기판에 솔더링할 때에, 다이본드용 땜납 재료에 흡수되어 열이 충분히 표면 실장 부품이나 실장용 땜납 재료에 전달되지 않고, 이에 의해 실장용 땜납 재료의 젖음성이 나빠져 보이드 발생을 야기하게 된다. 그로 인해, 표면 실장 부품을 회로 기판에 실장하는 경우의 신뢰성이 저하되어 버리므로, 리플로우 노의 가열 온도와의 관계로부터 바람직하지 않다.

따라서, 본 발명은 이러한 종래의 과제를 해결한 것이며, 고상선 온도를 저하시키는 성분을 가능한 한 포함하지 않거나, 포함하였다고 해도 기정값 이하로 되는 땜납 재료를 다이본드용 땜납 재료로서 사용하는 동시에, 땜납 재료 접합 공정 중에 고상선 온도를 저하시키는 성분이 용출되지 않도록 한 것이다. 또한 다이본드용 땜납 재료와 실장용 땜납 재료와의 고상선 온도차가 커지는 다이본드용 땜납 재료와 실장용 땜납 재료를 사용하여 표면 실장 부품을 솔더링함으로써 다이본드용 땜납 재료의 용해를 방지할 수 있도록 한 것이다.

과제의 해결 수단

표면 실장 부품의 솔더링 방법은, Ni 도금층이 형성된 전극면을 갖는 회로 소자가, Ni 도금층이 형성된 리드 프레임의 다이패드 전극면에, Cu의 함유량이 소정 값 이하인 Sn을 주성분으로 하는 (Sn-Sb)계 땜납 재료를 사용하여 솔더링된 표면 실장 부품을, 회로 기판의 기판 단자부에 도포된 (Sn-Ag-Cu-Bi)계 땜납 재료 혹은 (Sn-Ag-Cu-Bi-In)계 땜납 재료를 실장용 땜납 재료로서 사용하여 솔더링하는 것을 특징으로 한다.

또한, 본 발명에 관한 표면 실장 부품은, 회로 소자가 적재되는 다이패드 전극부와 회로 기판에 접합되는 리드부로 이루어지고, 상기 다이패드 전극부에는 Ni 도금층이 형성된 리드 프레임과, 다이패드 전극부에 대해, Cu의 함유량이 소정값 이하인 Sn을 주성분으로 하는 (Sn-Sb)계 땜납 재료를 통해 접합되는, Ni 도금층을 그 접합면으로 하는 회로 소자와, 리드부가, (Sn-Ag-Cu-Bi)계 땜납 재료, 혹은 (Sn-Ag-Cu-Bi-In)계 땜납 재료를 통해, 기판 단자부를 구성하는 랜드부에 접합되는 회로 기판으로 이루어지는 것을 특징으로 한다.

이 발명에서는 다이본드용 땜납 재료로서 (Sn-Sb)계 땜납 재료가 사용된다. 사용하는 (Sn-Sb)계 땜납 재료의 Cu 함유량은 기정값 이하로 억제한다. Cu의 기정 값으로서는 0.01질량% 이하, 바람직하게는 0.005질량% 이하이다. Cu의 함유량이 기정 값 이하일 때에는, 고상선 온도의 저하를 회피할 수 있는 것이 확인되었다.

리드 프레임은 Cu를 주성분으로 하는 것이므로, 회로 소자가 적재 고정되는 회로 소자 고정면으로 되는 다이패드 전극부(땜납 재료 접합면으로 되는 아일랜드부)는 도금한 것이 사용된다. 특히 다이패드 전극부가 Ni 도금된 리드 프레임이 사용된다. Ni 도금층에 의해 땜납 재료 접합시에 있어서의 Cu 성분의 용출을 방지한다. 동시에, 회로 소자의 전극면측도 Ni 도금층을 형성한다. 이렇게 함으로써, 회로 소자를 리드 프레임에 적재하여 땜납 재료로 접합하는 경우라도, Cu 성분의 용출이 없어져, 고상선 온도의 저하를 회피할 수 있다.

발명의 효과

본 발명에 따르면 종래보다도 고상선 온도를 낮출 수 있는 것에 더하여, (Sn-Sb)계 땜납 재료 본래의 고상선 온도도 그대로 유지할 수 있어, 결과적으로 가열 온도가 회로 소자에 미치는 영향을 회피할 수 있다. 또한, 실장용 땜납 재료로서, 고상선 온도가 낮은 (Sn-Ag-Cu-Bi)계 땜납 재료나, (Sn-Ag-Cu-Bi-In)계 땜납 재료를 사용함으로써, 리플로우 노의 솔더링할 수 있는 최소 가열 온도(리플로우 가능 최소 온도)를 종래보다도 낮출 수 있는 동시에, 다이본드용 땜납 재료와의 고상선 온도차를 크게 할 수 있다. 그 결과, 실장된 모든 표면 실장 부품의 땜납 재료 접합부에 있어서의 솔더링성이 양호해지므로, 회로 기판 내 온도 분포가 커져도 다이본드용 땜납 재료가 용해되는 일이 없어지고, 표면 실장 부품의 접합 강도가 높아져 기계적 신뢰성을 높일 수 있다.

발명을 실시하기 위한 구체적인 내용

이어서, 본 발명을 실시하기 위한 형태를, 도면을 참조하면서 설명한다. 이하에 나타내는 실시예에서는, 회로소자로서 웨이퍼로부터 잘라내어진 반도체 소자(IC 칩)를 표면 실장하는 경우에 대해 설명한다. 따라서 회로 기판으로서는 프린트 기판이 사용되고 있다.

[제1 실시예]

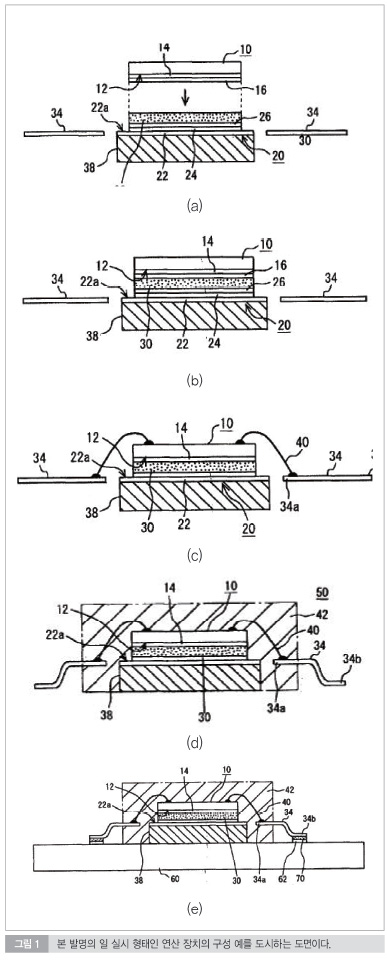

우선, 표면 실장 부품의 솔더링 방법에 대해 그림 1을 참조하여 설명하지만, 이 솔더링 공정 자체는 주지의 공정이므로, 그 개략을 설명한다.

그림 1의 (a)에 도시하는 바와 같이, 이 발명에서는 반도체 소자(IC 칩)(10) 중 다이본딩면으로 되는 전극면(12)에는 Ni 도금층(14)이 형성된다. Ni 도금층(14)은, 다이본딩되는 면의 모든 영역(모든 전극면)에 형성된다. Ni 도금층(14)의 표층에는 Sn 도금층 또는 Au 도금층(16)이 더 형성된다. Au 도금층(16)은 필요에 따라서 형성된다. 이들 Sn 도금층 또는 Au 도금층(16)은, 이 상태에 있어서, 다이본드용 땜납 재료(30)에 위치하는 솔더링면측(최표면)에 Sn 도금층 또는 Au 도금층(16)이 형성되어 있으면 되는 것이며, IC 칩(10)과 Ni 도금층(14) 사이에 예를 들어 Cu, Ti 등 Ni 도금층 이외의 층이 개재되어도 된다. 그림 1의 (a)와 같이, 리드 프레임(20)의 아일랜드부로 되는 다이패드 전극부(다이본드 접합부)(22)가 회로 소자 고정부이고, 그 하면에는 방열판(38)이 장착되고, 그 상면(22a)이 다이패드 전극면으로 된다. 따라서 다이패드 전극면(22a)은 회로 소자 고정용 전극면으로서 기능한다.

IC 칩(10)의 전극면(12)과 대향하는 이 다이패드 전극면(22a)에는 Ni 도금층(24)이 실시된다. Ni 도금층(24)의 표층에 Au 도금층(26)이 더 형성된다. Au 도금층(26)은 필요에 따라서 설치된다. 그리고 이 다이패드 전극면(22a)의 표층에 다이본드용 땜납 재료(30)이 공급된다. 이 예에서는 표층에 Au 도금층(26)이 형성되어 있으므로, 이 Au 도금층(26)의 상층에 다이본드용 땜납 재료(30)가 도포된다(솔더 페이스트 처리). 다이본드용 땜납 재료(30)로서는, 후술하는 고융점 땜납 재료가 사용된다. 여기서, 리드 프레임(20)은 Cu를 주성분으로 하는 것이므로, 이 발명에서는 Ni 도금층(24)에 의해 리드 프레임(20)의 다이패드 전극면(22a)을 피복한다.

Ni 도금층(24)을 피복하면, IC 칩(10)의 솔더링 공정 중에 리드 프레임(20)이 가열되어, Cu가 용출되려고 해도, Cu가 용출되기 어려워지는 동시에, 용출되었다고 해도 다이본드용 땜납 재료(30) 중에는 혼입되지 않는다. 다이본드용 땜납 재료(30) 중에 용출된 Cu가 혼입되면, 이 다이본드용 땜납 재료(30) 자체의 고상선 온도(후술하는 바와 같이 본 예에서는 245℃)를 저하시켜 버린다. 실험에 따르면 229 내지 236℃ 정도까지 저하되어 버린다. Ni 도금층(24)을 사용함으로써 다이본드용 땜납 재료(30) 그 자신의 고상선 온도를 245℃로 유지할 수 있다.

그림 1의 (b)에 도시하는 바와 같이, 도포된 고융점의 다이본드용 땜납 재료(30)의 면에 IC 칩(10)의 전극면(12)이 대치하도록 적재되어 가고정된다. 그 후, 오븐 리플로우 노 내에 반송되어 가열 처리된다. 이 가열 처리에 의해 그림 1의 (c)와 같이 Au 도금층(16과 26)은 용해된다.

다이패드 전극면(22a)에 다이본드용 땜납 재료(30)를 사용하여 솔더링함으로써 그림 1의 (c)와 같은 회로 소자로 된다. 실제로는, 이 회로 소자를 구성하는 리드(34) 중 내부 단자부(내부 전극부)(34a)와 IC 칩(10)이 전극 와이어(40)에 의해 결선(와이어 본딩)된 후, 와이어 본딩된 IC 칩(10)과 리드 프레임(20)이 수지(42)에 의해 몰드 처리되어, 그림 1의 (d)에 도시하는 주지의 표면 실장 부품(50)이 얻어진다.

표면 실장 부품(50)으로서는, 주지와 같이 SOP(Small Outline Package), QFN(Quad Flat Non-Lead)이나, QFP(Quad Flat Package) 등이 생각된다. 표면 실장 부품(50)은, 그림 1의 (e)에 도시하는 바와 같이 회로 기판으로서 기능하는 프린트 기판(60)에 실장된다. 그로 인해, 프린트 기판(60)에 형성된 기판 단자부(랜드)(62)와 리드(34)의 외부 단자부(34b)가 Pb 프리의 실장용 땜납 재료(70)에 의해 솔더링되어, 실장 처리가 완성된다. 또한, 리드 프레임(20)을 구성하는 리드(34)는 미리 그 전체에 걸쳐 Sn 도금이나, Sn-Bi 도금, Sn-Cu 도금, Sn-Ag 도금 등에 의한 도금 가공이 실시되어 있다.

상술한 실장 처리는, 오븐 리플로우 노 내에서 행해진다. 실장용 땜납 재료(70)로서는, 후술하는 바와 같이 종래부터 사용되고 있는 (Sn-Ag-Cu)계 땜납 재료보다도 그 고상선 온도 및 액상선 온도가 낮은 것이 사용된다. 계속해서, 본 발명에 있어서 사용한 다이본드용 땜납 재료(30)와 실장용 땜납 재료(70)에 대해 설명한다.

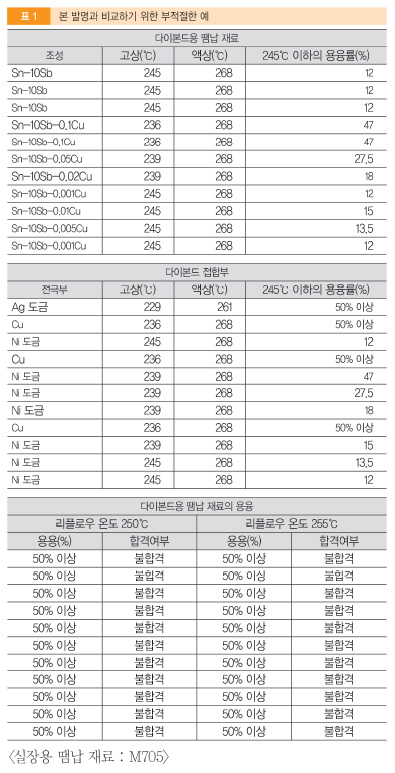

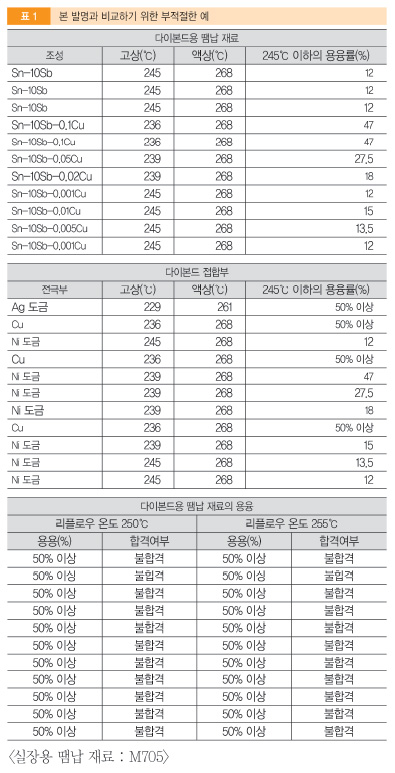

본 발명에 있어서는, 다이본드용 땜납 재료(30)로서는, 고상선 온도를 저하시키는 성분을 가능한 한 포함하지 않거나, 포함하였다고 해도 기정 값 이하로 되는 땜납 재료를 사용하는 동시에, 땜납 재료 접합 공정 중에 고상선 온도를 저하시키는 성분이 용출되지 않도록 한 것이다. 또한, 다이본드용 땜납 재료(30)와 실장용 땜납 재료(70)의 고상선 온도차가 커지는 다이본드용 땜납 재료(30)와 실장용 땜납 재료(70)를 사용하여 표면 실장 부품을 솔더링하도록 한 것이다. 표 1를 참조하여 설명한다.

표 1은 본 발명과 비교하기 위한 부적절한 예를 나타낸다. 실장용 땜납 재료(70)로서는 종래부터 사용되고 있는 M705 규격의 합금 땜납 재료(Sn-3Ag-0.5Cu)를 예시한다. 그 고상선 온도는 217℃이고, 액상선 온도는 220℃ 이다. 이에 대해 다이본드용 땜납 재료(30)로서는, 표 1에 나타내는 바와 같이 Sn을 주성분으로 하는 (Sn-Sb)계 땜납 재료이다.

표 1에는, (Sn-Sb)계 땜납 재료로서, Cu를 함유하는 것과, 그렇지 않은 2종류의 땜납 재료를 나타낸다. (Sn-10Sb)계 땜납 재료는, 0.1질량% 이하의 불순물을 포함한다. 또한, (Sn-10Sb)계 땜납 재료 그 자신의 고상선 온도는 245℃이고, 액상선 온도는 268℃이다. 표 1에는 다이본드용 땜납 재료(30)의 조성비, 그 조성비에서의 고상선 온도, 액상선 온도 및 다이본드용 땜납 재료(30) 자체의 245℃ 이하에서의 용융률을 나타낸다. 또한, 접합부인 다이패드 전극부(22)에 있어서의 고상선 온도, 액상선 온도 및 그곳에서의 245℃ 이하에서의 용융률은, 다이패드 전극부(22)에 있어서의 무도금인 경우와, 도금 가공을 실시한 경우를 나누어 실험한 값을 나타낸다. 그리고 리플로우 노의 가열 온도를 바꾸었을 때에, 다이패드 전극부(22)에 있어서의 용융 상태가 어떻게 변화되는지를 합격 여부(적합 여부)로 나타냈다. 여기에, 다이패드 전극부(22)에 있어서의 다이본드용 땜납 재료(30)의 용융에 의한 합격 여부는, 1질량%라도 용융된 경우에는 불합격으로 하였다.

리플로우 노의 최소 가열 온도(리플로우 가능 최소 온도)는, 실장용 땜납 재료(70)의 액상선 온도를 기준으로, 이것보다도 10℃ 정도 높은 온도를 설정하고, 이 리플로우 가능 최소 온도를 기준으로 하여 20℃ 및 25℃ 높은 가열 온도에서의 합격 여부도 실험에 의해 확인하였다.

표 1과 같이, (Sn-10Sb)계 땜납 재료인 경우에는, 다이본드용 땜납 재료(30) 그 자체의 245℃ 이하에서의 용융률은 12%로 되었다. 또한, Sb가 10질량% 이하에서는, 표 1에 나타내는 바와 같이 다이패드 전극부(22)에 있어서의 고상선 온도는 245℃ 이하로 저하된다. 이 값은, 다이패드 전극부(22)에 있어서의 도금층에 따라 다르지만, 다이본드용 땜납 재료(30) 자체의 고상선 온도보다도 낮다. 결론적으로는, 다이본드용 땜납 재료(30)에 함유하는 Cu의 함유량을 가감 조정해도 다이패드 전극부(22)에 있어서의 용융이 일어나는 것을 확인할 수 있었다. 따라서 표 1에 나타내는 땜납 재료는, 적절한 조합이라고는 할 수 없다.

표 2는 본 발명의 설명에 제공하는 실험예를 나타낸다. 표 2에서는, 다이본드용 땜납 재료(30)로서 (Sn-10Sb)계의 땜납 재료를 사용하고, 실장용 땜납 재료(70)로서 (Sn-Ag-Cu-Bi)계의 땜납 재료를 사용한 경우이다. 다이본드용 땜납 재료(30)에 있어서, Sb가 10질량% 이하에서는, 고상선 온도로서 245℃를 만족시킬 수 없어, 245℃ 이하로 되어 버린다. 이에 대해, Sb가 13질량% 이상이면 다음에는 땜납 재료가 단단해져 크랙이 형성되기 쉬워져, 땜납 재료 고형 후의 기계적 신뢰성이 저하되어 버린다. 따라서, Sb는 10% 내지 13질량%가 바람직하고, 크랙의 발생을 억지하고, 기계적 신뢰성을 확보하기 위해서는, 10% 내지 11질량%의 Sn이 보다 바람직하다. 또한, 땜납 재료의 주성분인 Sn의 순도는, 99.9질량% 이상인 것이 바람직하고, 그 중에서도 0.1질량% 이하의 불순물 중에 함유하는 Cu의 함유량은, 0.01질량% 이하가 바람직하고, 0.005질량% 이하가 더욱 바람직하다. Cu의 함유율이 높아지면, 그만큼 본래의 고상선 온도(245℃)를 저하시키게 되기 때문이다.

실장용 땜납 재료로서 사용되는 (Sn-Ag-Cu-Bi)계 땜납 재료로서는, Ag가 3% 내지 3.4질량%, Cu가 0.5% 내지 1.1질량%, Bi가 3% 내지 7질량%, 나머지가 Sn으로 이루어지는 땜납 재료를 나타낸다. Ag의 첨가량이 많아지면 고상선 온도가 높아질 우려가 있다. 따라서 바람직하게는 3.0질량% 정도가 좋다. Cu도, 고상선 온도를 높이게 되므로, (0.55 내지 0.85)질량%의 범위 내에서 첨가하는 것이 바람직하다. Bi도 Cu와 마찬가지로 고상선 온도를 높이게 되거나, 기계적 강도가 떨어지게 되므로, 바람직하게는 (3 내지 5)질량%의 범위 내에서 첨가한다. 이 예에서는, (Sn-3Ag-0.8Cu-3Bi)계 땜납 재료를 사용하였다.

Bi를 첨가한 (Sn-Ag-Cu-Bi)계의 실장용 땜납 재료(70)를 사용하면, 그 고상선 온도는 205℃로 되고, 액상선 온도는 215℃로 되므로, M705 규격의 땜납 재료보다도 고상선 온도, 액상선 온도 모두 낮게 할 수 있다.

한편 표 2와 같이, Cu를 함유하는 것에 의해서는, 다이본드용 땜납 재료(30) 그 자신의 고상선 온도와 액상선 온도는 각각 변화되지 않고, 또한 다이패드 전극부(22)에 있어서의 도금 재료가 Ni재일 때에는, 다이패드 전극부(22)에 있어서의 245℃ 이하에서의 용융률은 12% 내지 15% 정도로 되지만, 리플로우 노 온도가 220℃ 내지 240℃의 범위 내일 때에는, 다이패드 전극부(22)에 있어서의 245℃ 이하에서의 용융률은 0%로 된다. 여기서, 최소의 리플로우 노 온도를 220℃로 설정한 것은, 상술한 조성비의 실장용 땜납 재료(70)를 사용하였을 때의 액상선 온도가, 215℃로 낮기 때문이다. 또한, 리플로우 노 온도를 245℃까지 승온하면, 다이패드 전극부(22)에 있어서의 245℃ 이하에서의 용융률은 12% 내지 15%로 된다.

그 결과, 다이패드 전극면(22a)에 Ni 도금층이 실시된 리드 프레임(20)을 사용하는 동시에, 실장용 땜납 재료(70)로서 (Sn-Ag-Cu-Bi)계의 땜납 재료를 사용하고, 다이본드용 땜납 재료(30)로서 (Sn-10Sb)계의 땜납 재료이며, 0.1질량% 이하의 불순물에 포함되는 Cu의 함유량이 0.01질량% 이하로 억제된 땜납 재료를 사용한 경우에는, 리플로우 노의 가열 온도가 240℃까지일 때에는 양호한 결과가 얻어지는 것을 알 수 있다. 여기에, 다이패드 전극부(22)에 있어서의 다이본드용 땜납 재료(30)는, 1%라도 용융된 경우에는 불합격으로서 판정하고 있는 것은, 표 1의 경우와 동일하다. 또한, 만약을 위해 표 2에는 종래부터 사용되고 있는 (Sn-10Cu)계 땜납 재료도 예시되어 있다. 또한 Cu가 0.02질량% 이상 포함되는 경우의 조합에 대해서도 비교예로서 열거되어 있다.

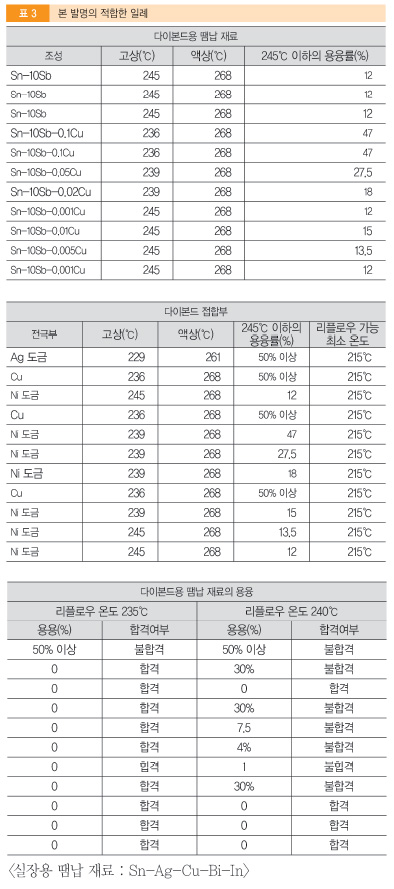

표 3은 본 발명의 적합한 일례를 나타낸다. 표 3의 예는, 실장용 땜납 재료(70)로서 표 2에 나타낸 성분 외에 In을 첨가한 (Sn-Ag-Cu-Bi-In)계의 땜납 재료를 사용한 경우이다. Bi가 (2 내지 5)질량%일 때, In은 (3 내지 5)질량% 첨가된다. 바람직한 첨가량은 Bi가 3질량%일 때, In은 3% 내지 4질량%이고, Bi가 4질량%일 때에는, In은 3질량%가 적합하다. In은 액상선 온도를 낮추는 작용이 있다. 이 예에서는, (Sn-3Ag-0.8Cu-2Bi-5In)계 땜납 재료를 사용하였다.

실장용 땜납 재료(70)로서 In을 더 첨가한 (Sn-3Ag-0.5Cu-3Bi-3In)의 땜납 재료를 사용하면, 그 고상선 온도는 189℃이고, 액상선 온도는 210℃로 되어, Bi를 첨가한 경우보다도 더욱 낮게 할 수 있다. 물론, M705 규격의 땜납 재료보다도 그 고상선 온도, 액상선 온도를 모두 낮게 할 수 있다.

다이본드용 땜납 재료(30)로서는 표 2와 마찬가지로 (Sn-10Sb)계의 땜납 재료이며, 0.1질량% 이하의 불순물에 포함되는 Cu의 함유량이 0.01질량% 이하로 억제된 땜납 재료이다. 만약을 위해, 표 2와 마찬가지로, 0.02질량% 이상 Cu를 함유하는 다이본드용 땜납 재료(30)에 대해서도 그 데이터를 열거하고 있다. Cu를 함유하는 것에 의해서는, 표 2의 경우와 마찬가지로 다이본드용 땜납 재료(30) 그 자신의 고상선 온도와 액상선 온도는 변화되지 않아, 245℃와 268℃이다. 또한 Cu재로 구성되는 다이패드 전극부(22)의 도금 재료는 Ni재가 가장 바람직하고, Cu의 함유량이 0.01질량% 이하에 있어서의 다이패드 전극부(22)에서의 고상선 온도는 239℃ 내지 245℃로, 다이본드용 땜납 재료(30) 자체의 고상선 온도(245℃)와 동일하거나, 극히 가까운 값으로 되었다. 다이패드 전극부(22)에 있어서의 액상선 온도는 변화되지 않고 268℃ 그대로이다. 다이본드용 땜납 재료(30) 자체의 245℃ 이하에서의 용융률은, 0.01질량% 이하의 Cu 함유량일 때에는 12% 내지 27.5% 정도의 범위이다. 덧붙여 말하면, 종래 다이본드용 땜납 재료(30)(Cu가 0.02질량% 이상 함유되는 경우를 포함함)를 사용한 경우에는, 50% 이상의 용융률로 된다.

한편, 실장용 땜납 재료(70)로서 (Sn-Ag-Cu-Bi-In)계의 땜납 재료인 경우에는, 상술한 바와 같이 그 액상선 온도가 210℃로 낮아지기 때문에, 리플로우 노에 있어서의 최소 온도(최소 가열 온도)도 낮아지므로, 215℃ 정도로 리플로우 가능 최소 온도를 설정할 수 있다. 따라서 리플로우 노 온도가 230 내지 235℃까지 승온(가열)되었다고 해도, 표 3에 나타내는 바와 같이 모두 다이패드 전극부(22)에 있어서의 다이본드용 땜납 재료(30)는 용융되지 않는 것이 실험에 의해 확인되었다.

계속해서, 실장용 땜납 재료(70)의 조성비를 바꾸었을 때의 실시예(실험예)를 표 4 및 표 5에 나타낸다. 다이본드용 땜납 재료(30)는 (Sn-10Sb)계 땜납 재료를 사용한 경우이다.

표 4는 (Sn-Ag-Cu-Bi)계 땜납 재료를 사용하였을 때의 실시예이다. 제1 실시예 내지 제6 실시예까지는, (Sn-Ag-Cu-Bi)계 땜납 재료이고, 제7 실시예 내지 제9 실시예까지는 특정 금속[(Ni, Fe, Co) 중 1종]을 더 첨가하였을 때의 실시예이다. 또한, 제10 내지 제11 실시예는 Cu를 포함하지 않는 땜납 재료를 사용하였을 때의 실시예이고, 제12 내지 제16 실시예는 특정 금속(Ni, Co 중 어느 하나 또는 모두)을 첨가하였을 때의 실시예이다. 제1 비교예는, M705 규격의 땜납 재료를 사용하였을 때의 데이터이다. 이것을 기준 데이터로서 사용하고 있다.

표 4는 땜납 재료의 조성비, 융점으로서 고상선 온도, 액상선 온도 외에 최대 흡열 반응점에 있어서의 융점을 나타낸다. 또한, 이 밖에 기계적 접합 강도와, 땜납 재료 표면 상태의 양부를 나타낸다. 리플로우 노의 가열 온도로서는, 제1 내지 제9 실시예에서는 220℃, 제1 비교예에서는 230℃, 그리고 제2 비교예 내지 제6 비교예에서는 220℃를 각각 예시한다.

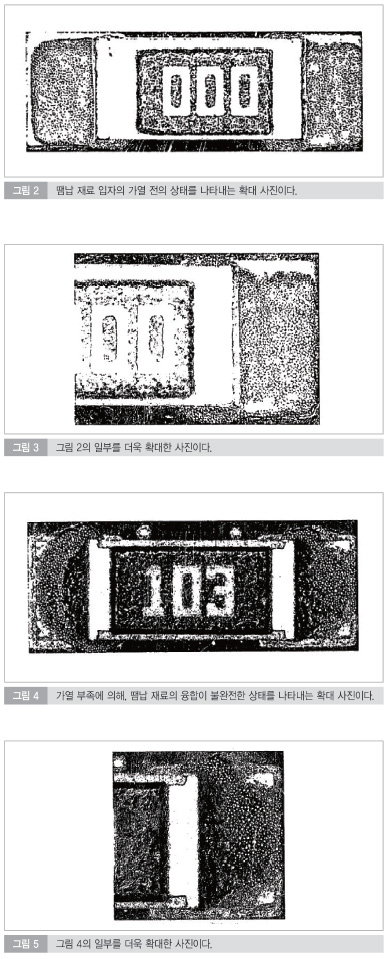

땜납 재료 표면 상태는, 그림 2에 나타내는 바와 같은 땜납 재료 입자(땜납 재료립)를 사용하였다. 그림 2는 가열 처리되기 전의 도면이며, 칩 부품(시료 번호 「000」)을 예시하였다. 그림 3과 같이 그 일부를 확대함으로써, 땜납 재료의 입자가 전극 전체면에 걸쳐 혼재되어 있는 것을 알 수 있다. 소정량의 땜납 재료 입자를 융기시킨 상태에서 리플로우 노의 온도에서 가열한다. 그러한 경우, 리플로우 노의 가열 온도에서도 아직 충분히 땜납 재료 입자가 용해되어 있지 않은 상태가 그림 4(시료 번호는 「103」)이고, 그 일부 확대도가 그림 5이다. 땜납 재료의 일부의 입자가 아직 충분히 용해되어 있지 않은 것을 알 수 있다.

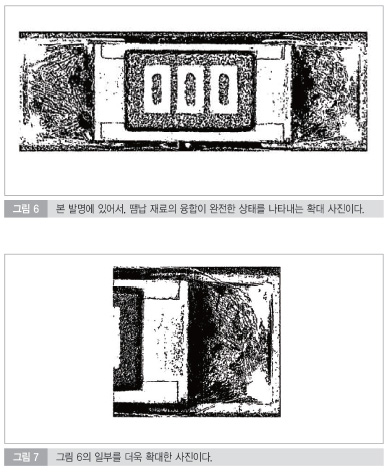

땜납 재료의 입자가 완전히 용해된 상태가 그림 6이고, 그 확대도가 그림 7이다. 그림 4와 같이 표면에 땜납 재료 입자가 남는 용해 상태는 바람직하지 않다. 그림 6 및 그림 7의 상태가 구하려고 하는 이상적인 용해 상태이다.

접합 강도는, 열사이클 시험에 의해 행한다. 이 예에서는, 칩 저항 부품을 예시한다. 프린트 기판의 솔더링 패턴(1.6㎜×1.2㎜)에 (Sn-Ag-Cu-Bi)계 땜납 재료의 솔더 페이스트를 150㎛의 두께로 인쇄 도포한다. 그 후, (3.2㎜×1.6㎜×0.6㎜)의 칩 저항 부품을 얹고, 가열 온도가 220℃인 리플로우 노에서 솔더링한 후, 칩 저항 부품이 실장된 프린트 기판을 -55℃ 내지 +125℃로 각각 30분씩 유지하는 조작을 1사이클로 하여, 1000사이클 행하였을 때의 접합 강도(N)를 나타낸다.

접합 강도는, 평균값이 높고, 최소값이 20℃ 이상이 바람직하고, 그 중에서도 그 절대값이 작은 것이 더욱 바람 직하다.

제1 실시예 내지 제9 실시예로부터 명백한 바와 같이, 고상선 온도는 210℃ 이하이다. 액상선 온도도 약 215℃ 이하이다. 땜납 재료 표면 상태는 모두 양호(그림 6의 완전 용해 상태)하므로, 접합 강도도 만족시키는 값으로 되어 있다. 일부, 액상선 온도가 220℃를 초과하고 있는 실시예도 있지만, 땜납 재료 표면 상태 및 접합 강도는 충분히 만족시킨 값을 나타내고 있다.

제2 비교예 내지 제6 비교예까지는, 제1 비교예를 초과하는 내용의 것도 있지만, 제1 실시예 내지 제9 실시예와 같이 땜납 재료 표면 상태(일부 불용해 상태)와 접합 강도의 점에서 떨어진다. 따라서 (Sn-Ag-Cu-Bi)계 땜납 재료로서는, 상술한 바와 같은 범위 내로 제한하는 조성비가 바람직하다고 할 수 있다.

표 5는 (Sn-Ag-Cu-Bi-In)계 땜납 재료를 사용하였을 때의 실험예(실시예)이다. 제1 비교예는, M705 규격의 땜납 재료를 사용하였을 때의 데이터로, 이것을 기준 데이터로서 사용하고 있다. 표 5도 표 4와 마찬가지로, 땜납 재료의 조성비, 융점으로서 고상선 온도, 액상선 온도 외에 최대 흡열 반응점에 있어서의 융점을 나타내고, 또한 기계적 접합 강도와, 땜납 재료 표면 상태의 양부를 나타낸다. 땜납 재료 표면 상태는, 그림 3 내지 그림 6과 마찬가지이다. 접합 강도의 시험도 표 4와 동일하다. 단, 리플로우 노의 가열 온도는 215℃로 변경하여 실험하였다.

기준이 되는 땜납 재료로서는, 표 4의 경우와 마찬가지로 M705 규격의 합금 땜납 재료이며, 이 땜납 재료의 여러 특성을 기준 데이터로서 사용하고 있다.

제17 실시예 내지 제24 실시예로부터 명백한 바와 같이, 고상선 온도는 200℃ 이하이다. 액상선 온도도 약 215℃이다. 땜납 재료 표면 상태는 모두 양호(그림 6 및 그림 7의 완전 용해 상태)하므로, 접합 강도도 만족시킨 값으로 되어 있다. 일부, 액상선 온도가 215℃를 초과하고 있는 실시예도 있지만, 땜납 재료 표면 상태 및 접합 강도는 충분히 만족시킨 값을 나타내고 있다. 제7 비교예 내지 제14 비교예에 있어서는 제1 비교예를 초과하는 내용의 것도 있지만, 제17 실시예 내지 제24 실시예에 비해 땜납 재료 표면 상태(일부 불용해 상태)와 접합 강도의 점에서 떨어지는 것을 알 수 있다. 따라서 (Sn-Ag-Cu-Bi-In)계 땜납 재료로서는, 상술한 바와 같은 범위 내로 제한하는 조성비가 바람직하다고 할 수 있다. 따라서 표 1 내지 표 5까지의 실험 결과로부터 명백한 바와 같이, 이 발명에 있어서는, (1) 실장용 땜납 재료(70)로서는, 표 2 이하에 나타내는 조성비로 이루어진 (Sn-Ag-Cu-Bi)계의 땜납 재료 혹은 이것에 In을 첨가한 표 3 이하에 나타내는 조성비로 이루어진 (Sn-Ag-Cu-Bi-In)계의 땜납 재료가 적합하다. (2) 다이본드용 땜납 재료(30)로서는, (Sn-10Sb)계의 땜납 재료이며, 0.1질량% 이하의 불순물에 포함되는 Cu의 함유량이 0.01질량% 이하로 억제된 땜납 재료가 적합하다. 특히 Cu의 함유량이 0.005질량% 이하, 바람직하게는 0.001질량% 이하인 것이 바람직하다. 이 경우 사용하는 다이패드 전극부(22)에 있어서의 도금재로서는 Ni재가 적합하고, 리플로우 노의 가열 온도는 245℃ 이하, 바람직하게는 240℃ 이하로 설정되는 것이 바람직한 것이 판명되었다. (3) 또한, 상술한 (Sn-Sb)계 땜납 재료를 다이본드용 땜납 재료(30)로서 사용할 때, 이것에 P를 첨가할 수도 있다. 상술한 (Sn-Sb)계 땜납 재료에 P를 미량으로 더 첨가하면, 젖음성과 함께 보이드의 개선으로 이어진다. (4) 상술한 (3)의 (Sn-Sb)계 땜납 재료에, (Ni, Fe, Co) 중 1종 이상의 성분을 더 첨가할 수도 있다. P 대신에 (Ni, Fe, Co) 중 1종 이상의 성분을 첨가해도 된다.

(Ni, Fe, Co) 중 1종 이상의 성분을 첨가하는 것은, 땜납 재료 접합 공정 중에서, Ni 도금층(14, 24)이 용해되는 것을 억제하는 동시에, 땜납 재료 접합 중에 생성되는 Ni 도금의 반응량의 성장을 억제하기 위함이다. (Ni, Fe, Co) 중 1종 이상의 성분은, 총량이 0.01 내지 0.1질량%로 되는 범위 내에서 첨가된다. 단독(1종류)으로 첨가할 때에는, Ni로는 0.1질량%, Fe로는 0.05질량%, Co로는 0.05질량%가 바람직하다. 이들 성분의 조합으로서는, (Ni+Co), (Ni+Fe+Co)가 생각된다. 그 후, 본건 출원인이 예의 검토를 행한 결과, 본원 발명의 다이본드용 땜납 재료와 실장용 땜납 재료의 고상선 온도차가 커지는 다이본드용 땜납 재료와 실장용 땜납 재료를 사용하여 표면 실장 부품을 솔더링함으로써 다이본드용 땜납 재료의 용해를 방지할 수 있도록 하기 위한 과제 달성을 위해서는, Cu 성분이 없어도 달성할 수 있는 것이 판명되었다. 그 결과를 표 4의 제10 실시예 내지 제16 실시예 및 표 5의 제25 내지 제27 실시예에 나타낸다.

표 4의 제15 실시예 및 제16 실시예는 외관상 문제가 없는 것처럼 보이지만, 보이드가 많았기 때문에, 결과로서 불합격으로 하였다. 결과적으로, (Sn-(4~5)Bi-3Ag)계 땜납 재료 또는 (Sn-(4~5)Bi-3Ag)계 땜납 재료에, (0.02~0.1)중량%의 Ni나, (01~0.1)중량%의 Co 중 어느 하나를 첨가하거나, 또는 Ni와 Co 모두를 첨가함으로써, 제1 실시예 내지 제9 실시예와 동등한 결과가 얻어졌다. 또한, 표 5의 제25 실시예 내지 제27 실시예에 나타내는 바와 같이, (Sn-(3~5)In-(2~4)Bi-3Ag)계 땜납 재료인 경우라도, 제10 실시예 내지 제16 실시예와 동등하다고 하는 결과가 얻어졌다. Ag의 첨가량은, 2.8질량% 내지 3.3질량%의 범위 내이면 된다.