응력 제거 위한 범프 상호연결 전도층 상의 절연 물질

부분적인 마이크로 비아 형성

반도체 디바이스는 반도체 다이와 상기 반도체 다이 상에 형성된 제1 절연층을 갖는다. 복수의 제1 마이크로 비아는 상기 제1 절연층상에 형성된다. 전도층은 제1 마이크로 개구와 제1 절연층상에 형성된다. 제2 절연층은 제1 절연층과 전도층상에 형성된다. 제2 절연층의 일부는 전도층을 노출시키도록 제거되고, 전도층상의 제2 절연층 내에 복수의 제2 마이크로 개구를 형성한다. 제2 마이크로 개구는 마이크로 비아, 마이크로비아 링 또는 마이크로비아 슬롯일 수 있다. 제2 절연층의 일부를 제거하면 전도층상에 제2 절연층의 아일랜드를 만든다. 범프는 전도층상에 형성된다. 제3 절연층은 범프 상의 제2 마이크로 개구에 형성된다. 제2 마이크로 개구는 응력 제거를 제공한다.

배경 기술

반도체 디바이스는 일반적으로 현대의 전자 제품에서 발견된다. 반도체 디바이스는 전기 부품의 수와 밀도에 따라 다양하다. 개별 반도체 디바이스는 일반적으로 전기 부품, 예를 들어, 발광 다이오드(LED), 작은 신호 트랜지스터, 레지스터, 커패시터, 인덕터 및 전력 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)중 한 종류가 포함된다. 집적 반도체 디바이스는 일반적으로 수백에서 수백만의 전기 부품이 포함된다. 집적 반도체 디바이스의 예로는 마이크로 컨트롤러, 마이크로프로세서, 부하 연결 장치(CCD), 태양 전지 및 디지털 마이크로-미러 장치(DMDs)가 포함된다.

반도체 디바이스는 신호 처리, 고속 계산, 전자기 신호 송신 및 수신, 전자 장치 제어, 태양 빛을 전기로 변환, 텔레비전 디스플레이를 위한 영상 프로젝션 생성과 같은 다양한 기능을 수행한다. 반도체 디바이스는 엔터테인먼트, 통신, 전력 변환, 네트워크, 컴퓨터 및 소비자 제품 분야에서 발견된다. 반도체 디바이스는 또한 군사 응용 프로그램, 항공, 자동차, 산업 컨트롤러 및 사무 장비에서 찾아 볼 수 있다.

반도체 디바이스는 반도체 재료의 전기적 특성을 이용한다. 반도체 재료의 원자 구조는 그 전기 전도성이 전기장 또는 베이스 전류를 적용하거나 또는 도핑 과정을 통해 조작될 수 있게 한다. 도핑은 반도체 재료에 불순물을 도입하여 반도체 디바이스의 전도성을 조절하거나 제어한다.

반도체 디바이스는 능동(active) 및 수동(passive) 전기 구조물을 포함하고 있다. 양극성 및 전계 효과 트랜지스터를 포함하는 능동 구조물은 전기 전류의 흐름을 제어한다. 전기장 또는 베이스 전류의 도핑 및 적용 레벨을 변화시킴으로써, 트랜지스터는 전기 전류의 흐름을 증진하거나 제한한다. 레지스터, 커패시터 및 인덕터 등을 포함하는 수동 구조물은 다양한 전기적 기능을 수행하기에 필요한 전류와 전압 사이의 관계를 형성한다. 수동 및 능동 구조물은 전기적으로 연결되어 회로를 형성하고, 이 회로는 반도체 디바이스가 고속 계산 및 기타 유용한 기능을 수행할 수 있도록 한다.

반도체 디바이스는 일반적으로 두 개의 복잡한 제조 공정, 즉 프런트 엔드 제조공정(front-end manufacturing) 및 백 엔드 제조공정(back-end manufacturing)을 사용하여 제조되며, 각 공정은 잠재적으로 수백 개의 공정을 포함한다. 프런트 엔드 제조공정은 반도체 웨이퍼의 표면에 복수의 다이를 형성하는 것을 포함한다. 각 반도체 다이는 일반적으로 동일하며, 전기적으로 연결되는 능동 및 수동 부품에 의해 형성된 회로가 포함된다. 백 엔드 제조공정은 구조적 지지와 주변 절연을 제공하기 위해 완성된 웨이퍼로부터 개별 반도체 다이를 분리하고 패키징한다.

발명의 내용

발명을 실시하기 위한 구체적인 내용

반도체 제조의 하나의 목표는 더 작은 반도체 디바이스를 생산하는 것이다. 더 작은 장치는 일반적으로 적은 전력을 소모하고, 높은 성능이 있고, 보다 효율적으로 생산될 수 있다. 또한, 더 작은 반도체 디바이스는 더 작은 최종 제품에 대해 바람직한 더 작은 풋 프린트(smaller footprint)를 갖추고 있다. 더 작은 반도체 다이 크기는 프런트 엔드 공정의 개선에 의해 작고, 높은 밀도의 능동 및 수동 부품을 갖는 반도체 다이를 성취할 수 있게 한다. 백 엔드 공정은 전기적 상호연결 및 패키징 재료의 개선에 의해 더 작은 풋 프린트를 갖는 반도체 디바이스 패키지가 될 수 있게 한다.

반도체 웨이퍼는 일반적으로 웨이퍼의 활성 표면상에 형성된 복수의 접촉 패드를 포함한다. 절연층이 이 활성표면과 접촉 패드 상에 형성된다. 절연층의 일부는 접촉 층을 노출하도록 제거된다. 복수의 범프가 전기적 상호연결을 위하여 노출된 접촉 패드 상에 형성된다. 접촉 패드 주변의 절연층은 특히 범프에 의해 발생된 응력에 기인하여, 접촉 패드의 에지 주변에 크랙이 형성되는 것이 알려져 있다. 이 절연층의 크랙킹(cracking)은 결점 및 기타 신뢰성 문제를 일으킨다.

접촉 패드 상에 있는 절연층상의 범프 유발 응력을 감소시킬 필요가 있다. 따라서 일 실시예에 있어서, 본 발명은 반도체 다이를 제공하는 단계, 상기 반도체 다이 상에 제1 절연층을 형성하는 단계, 상기 제1 절연층 상에 전도층을 형성하는 단계, 상기 제1 절연층과 전도층 상에 제2 절연층을 형성하는 단계, 상기 전도층을 노출시키고, 상기 전도층 상의 제2 절연층에 복수의 마이크로 비아를 형성하기 위해, 상기 제2 절연층의 일부를 제거하는 단계, 상기 전도층상에 범프를 형성하는 단계를 포함하는 반도체 디바이스의 제조 방법이다.

다른 실시예에 있어서, 본 발명은 기판을 제공하는 단계, 상기 기판상에 전도층을 형성하는 단계, 상기 기판과 상기 전도층상에 제1 전도층을 형성하는 단계, 상기 전도층을 노출시키고, 상기 전도층 상의 제1 절연층에 복수의 제1 마이크로 개구를 형성하기 위해, 상기 제1 절연층의 일부를 제거하는 단계, 상기 전도층상에 상호연결 구조물을 형성하는 단계를 포함하는 반도체 디바이스의 제조 방법이다. 다른 실시예에 있어서, 본 발명은 기판을 제공하는 단계, 상기 기판 상에 전도층을 형성하는 단계, 상기 기판과 상기 전도층상에 복수의 제1 마이크로 개구를 갖는 제1 전도층을 형성하는 단계, 상기 전도층상에 상호연결 구조물을 형성하는 단계를 포함하는 반도체 디바이스의 제조 방법이다. 다른 실시예에 있어서, 본 발명은 기판과 상기 기판상에 형성된 전도층을 포함하는 반도체 디바이스이다. 제1 절연층은 상기 기판과 상기 전도층상에 복수의 제1 마이크로 개구를 갖는다. 상호연결 구조물은 상기 전도층상에 형성된다.

본 발명은 응력 제거를 위한 범프 상호연결 전도층상의 절연 물질을 통해 부분적인 마이크로 비아를 형성하는 반도체 디바이스 및 방법을 제공하여, 접촉 패드 상에 있는 절연층상의 범프 유발 응력을 감소시킨다.

수동 및 능동 부품은 도핑, 증착, 포토리소그래피(photolitho graphy), 에칭 그리고 평탄화(planarization) 등의 일련의 공정 단계에 의해 반도체 웨이퍼의 표면 위에 형성된다. 도핑은 이온 주입 또는 열 확산 등의 기술에 의해 반도체 물질 내에 불순물을 유입시킨다. 이 도핑 공정은 능동 장치에서 반도체 물질의 전기 전도성을 수정하여 반도체 물질을 절연체, 전도체로 변경시키거나 또는 전기장 또는 베이스 전류에 응답하여 반도체 물질의 전도성을 다이내믹하게 변경시킨다. 트랜지스터는 전기장 또는 베이스 전류의 적용에 따라 트랜지스터가 전기 전류의 흐름을 향상시키거나 제한하는데 필요하도록 배열된 도핑의 다양한 형태 및 정도의 영역을 포함한다.

능동 및 수동 부품은 서로 다른 전기적 특성을 갖는 재료의 층으로 형성된다. 이 층들은 증착되는 물질의 종류에 따라 일부 결정된 다양한 증착 기술에 의해 형성될 수 있다. 예를 들어, 박막 증착은 화학 기상 증착(CVD), 물리 기상 증착(PVD), 전해 도금(electrolytic plating), 무전해 도금 공정(electroless plating processes)을 포함할 수 있다. 각 층은 일반적으로 능동 부품, 수동 부품 또는 부품들 사이의 전기적 연결의 일 부분을 형성하도록 패턴화된다.

층들은 패턴화될 층 상에 빛에 민감한 소재를 증착하는, 예를 들면 포토레지스트를 포함하는 포토리소그래피를 사용하여 패턴화될 수 있다. 패턴은 빛을 사용하여 포토마스크(photomask)로부터 포토레지스트(photoresist)로 변경된다. 일 실시예에서, 빛에 노출된 포토레지스트 패턴의 부분은 용매를 사용하여 제거되고 하부 층의 노출 부분은 패턴화된다. 또 다른 실시예에서, 빛에 노출되지 않은 포토레지스트 패턴의 부분인 네거티브 포토레지스트는 용매를 사용하여 제거되고 하부 층의 노출 부분은 패턴화된다. 포토레지스트의 나머지 부분은 제거되고 패턴화된 층의 뒤가 남게 된다. 대안적으로, 재료의 일부 유형은 무전해 및 전해 도금과 같은 기술을 사용하여 이전의 증착/에칭 공정에 의해 형성된 지역이나 공극에 재료를 직접 증착시켜 패턴화된다.

패터닝은 반도체 웨이퍼 표면상에서 상부 층의 일부가 제거되는 기본적인 작업이다. 반도체 웨이퍼의 부분들은 포토리소그라피(photolithography), 포토마스킹(photomasking) 마스킹(masking), 산화 또는 금속 제거, 포토그라피(photography) 및 스텐실(stenciling) 그리고 마이크로리소그라피(microlithography)를 사용하여 제거될 수 있다. 포토리소그라피는 래티클(reticles)에 패턴 또는 포토마스크를 형성하고, 이 패턴을 반도체 웨이퍼의 표면층에 전송하는 단계를 포함한다. 포토리소그라피는 두 단계 공정으로 반도체 웨이퍼의 표면에 능동 및 수동 구성부품의 수평 크기를 형성한다. 먼저, 래티클 또는 마스크의 패턴은 포토레지스트의 층으로 전송된다. 포토레지스트는 빛에 노출되면 그 구조와 성질이 변화하는 빛에 민감한 소재이다. 포토레지스트의 구조와 성질의 변화 공정은 수동-작용 포토레지스트 또는 긍정-작용 포토레지스트 중 하나로 발생한다. 다음, 포토레지스트 층이 웨이퍼 표면에 전송된다. 에칭이 포토레지스트에 의해 덮여지지 않은 반도체 웨이퍼의 상단 층의 일부분을 제거할 때, 변환이 발생한다. 포토레지스트(photoresists)의 화학은, 포토레지스트에 의해 덮이지 않은 반도체 웨이퍼의 상단 층의 부분이 제거되는 동안 포토레지스트가 화학적 에칭 용액의 제거에 대해 실질적으로 그대로 남아 저항하는 방식이다. 포토레지스트를 형성하고, 노출하고, 제거하는 공정뿐만 아니라 반도체 웨이퍼의 일부를 제거하는 공정은 사용되는 특정 저항과 원하는 결과에 따라 수정될 수 있다.

수동-작용 포토레지스트에서, 포토레지스트는 빛에 노출되어, 중합화(polymerization)로 알려진 공정에서 용해 상태에서 불용성 상태로 변화된다. 중합화에서, 중합되지 않은 소재는 빛 또는 에너지 소스에 노출되고 폴리머는 에칭 저항성인 교차 결합된 물질을 형성한다. 대부분의 수동 저항에서, 폴리머는 폴리이소프랜(polyisoprenes)이다. 화학 용제나 현상액(developers)으로 수용성 부분(즉, 빛에 노출되지 않은 부분)을 제거하여 래티클에 있는 불투명 패턴에 해당하는 저항 층에 구멍을 남겨둔다. 그 패턴이 불투명 영역에 존재하는 마스크는 소위 클리어-필드 마스크(clear-field mask) 라고 한다.

능동-작용 포토레지스트에서, 포토레지스트는 빛에 노출되어, 광가용성화(photosolubilization)로 알려진 공정에서 비교적 용해되지 않는 상태에서 훨씬 더 잘 용해되는 상태로 변경된다. 광가용성화에서, 비교적 불용성 저항은 적절한 빛 에너지에 노출되어 더욱 용해가능한 상태로 변환된다. 저항의 광가용성화된 부분은 개발 공정에서 용매에 의해 제거될 수 있다. 기본적인 능동 포토레지스트 중합체는 페놀-포름 알데히드 노보락(novolak) 수지라 불리는, 페놀-포름 알데히드 폴리머이다. 화학 용제나 현상액(developers)으로 수용성 부분(즉, 빛에 노출된 부분)을 제거하여 래티클에 있는 투명 패턴에 해당하는 저항 층에 구멍을 남겨둔다. 그 패턴이 투명 영역에 존재하는 마스크는 소위 다크-필드 마스크(dark-field mask)라고 한다.

포토레지스트에 의해 덮여지지 않은 반도체 웨이퍼의 상단 부분을 제거한 후, 포토레지스트의 나머지가 제거되고 그 뒤에 패턴 층을 남긴다. 대안적으로, 일부 유형의 재료가 무전해 및 전해 도금과 같은 기술을 사용하여 이전에 증착/에칭 공정에 의해 형성된 영역이나 공극에 재료를 직접 증착하여 패턴화된다.

기존의 패턴 상에 박막의 물질을 증착하는 것은 하부 패턴을 과장시켜(exaggerate) 불균일한 평면 표면을 만들 수 있다. 균일한 평면 표면은 더 작고 더 밀도가 높게 다져진 능동 및 수동 부품을 생산하기 위해 필요하다. 평탄화는 웨이퍼의 표면에서 물질을 제거하고, 균일한 평면 표면을 생성하는 데 사용될 수 있다. 평탄화는 폴리싱 패드로 웨이퍼의 표면을 폴리싱하는 것을 포함한다. 마찰 물질과 화학적 부식이 폴리싱 중에 웨이퍼의 표면에 추가된다. 마찰의 기계적 작업과 부식성의 화학적 작업의 결합은 임의의 불규칙한 지형(topography)을 제거하여 균일한 평면 표면을 형성한다.

백 엔드 제조는 완성된 웨이퍼를 개별 다이로 절단 또는 분리하고, 구조적 지지와 외부 절연을 위한 다이로 패키징되는 것을 의미한다. 반도체 다이를 분리하려면, 웨이퍼가 쏘우 스트리트 또는 스크라이브로 불리는 웨이퍼의 비기능적 지역을 따라 계산되어 절단된다. 웨이퍼는 레이저 절단 도구 또는 쏘우 블레이드를 사용하여 분리된다. 분리 후, 개별 반도체 다이는 다른 시스템 부품과 상호연결되기 위한 핀이나 접촉 패드를 포함하는 패키지 기판에 장착된다. 그리고 반도체 다이 상에 형성된 접촉 패드는 패키지 내의 접촉 패드에 연결된다. 전기적 연결은 납땜 범프, 스터드 범프, 전도성 페이스트 또는 와이어본드(wirebond)로 만들 수 있다. 밀봉제 또는 다른 몰딩 재료는 물리적 지지와 전기 절연을 제공하기 위해 패키지 위에 증착된다. 완성된 패키지는 전기적 시스템에 삽입되고 반도체 디바이스의 기능이 다른 시스템 부품에 사용할 수 있게 제조된다.

.jpg)

그림 1은 전자 장치(50)를 도시하며, 이 전자 장치는 그 표면에 장착된 복수의 반도체 패키지를 갖는 칩 캐리어 기판 또는 인쇄 회로 기판 (PCB)(52)을 갖는다. 전자 장치(50)는 적용에 따라, 한 형태의 반도체 패키지 또는 여러 형태의 반도체 패키지를 가질 수 있다. 다른 형태의 반도체 패키지가 설명을 목적으로 그림 1에 도시된다.

전자 장치(50)는 하나 이상의 전기적 기능을 수행하기 위해 반도체 패키지를 사용하는 독립형 시스템(standalone system)이 될 수 있다. 대안적으로, 전자 장치(50)는 더 큰 시스템의 하위 부품이 될 수 있다. 예를 들어, 전자 장치(50)는 휴대전화, 개인 디지털 보조장치(PDA), 디지털 비디오카메라(DVC) 또는 기타 전자 통신 장치의 일부가 될 수 있다. 대안적으로, 전자 장치(50)는 그래픽 카드, 네트워크 인터페이스 카드 또는 컴퓨터에 삽입될 수 있는 다른 신호 처리 카드가 될 수 있다. 반도체 패키지는 마이크로프로세서, 메모리, 응용 프로그램 특정 집적 회로(ASIC), 논리 회로, 아날로그 회로, RF 회로, 개별 장치 또는 기타 반도체 다이 또는 전기 부품을 포함할 수 있다. 소형화 및 중량 감소는 시장에서 인정 될 제품에 대하여 필수적이다. 반도체 디바이스들 사이의 거리는 더 높은 밀도를 달성하기 위해 감소되어야만 한다.

그림 1에서, PCB(52)는 PCB에 장착된 반도체 패키지의 구조적 지지와 전기적 상호연결을 위한 일반적인 기판을 제공한다. 전도성 신호 트레이스(54)는 증발, 전해 도금, 무전해 도금, 스크린 인쇄 또는 다른 적절한 금속 증착 프로세스를 사용하여 PCB(52)의 표면상에 또는 층 내에 형성된다. 신호 트레이스(54)는 각각의 반도체 패키지, 장착 부품 및 다른 외부 시스템 부품 간의 전기적 통신을 위하여 제공된다. 트레이스(54)는 또한 각각의 반도체 패키지에 전력 및 접지 연결을 제공한다.

일부 실시예에서, 반도체 디바이스는 두 개의 패키지 레벨(packaging levels)을 갖는다. 제 1 패키지 레벨은 반도체 다이를 중간 캐리어에 기계적 및 전기적으로 부착하기 위한 기술이다. 제 2 패키지 레벨은 중간 캐리어를 PCB에 기계적 및 전기적으로 부착하기 위한 기술을 포함한다. 다른 실시예들에서, 반도체 디바이스는 다이가 PCB에 기계적 및 전기적으로 직접 장착되는 제 1 패키지 레벨만을 가질 수 있다.

설명을 위해, 본드 와이어 패키지(56) 및 플립칩(58)을 포함하는 제 1 레벨 패키지의 여러 형태가 PCB(52) 상에 도시된다. 또한, 볼 그리드 어레이(BGA)(60), 범프 칩 캐리어(BCC)(62), 듀얼 인-라인 패키지(DIP)(64), 랜드 그리드 어레이(LGA)(66), 멀티 칩 모듈(MCM)(68), 쿼드 플랫 무연 패키지(QFN)(70) 및 쿼드 플랫 패키지(72)를 포함하는, 제 2 레벨 패키지의 여러 형태가 PCB(52) 상에 장착되어 도시된다. 시스템의 요구 사항에 따라, 제 1 및 제 2 레벨의 패키지 형태의 임의의 조합뿐만 아니라 다른 전자 부품의 조합으로 구성된 반도체 패키지의 조합이 PCB(52)에 연결될 수 있다. 다른 실시예에서, 전자 장치(50)는 여러 상호연결된 패키지를 포함할 수 있으나, 일부 실시예에서는, 하나의 연결된 반도체 패키지를 포함한다. 하나의 기판 위에 하나 이상의 반도체 패키지를 결합하여, 제조업자는 미리 만든 부품을 전자 장치 및 시스템에 통합할 수 있다.

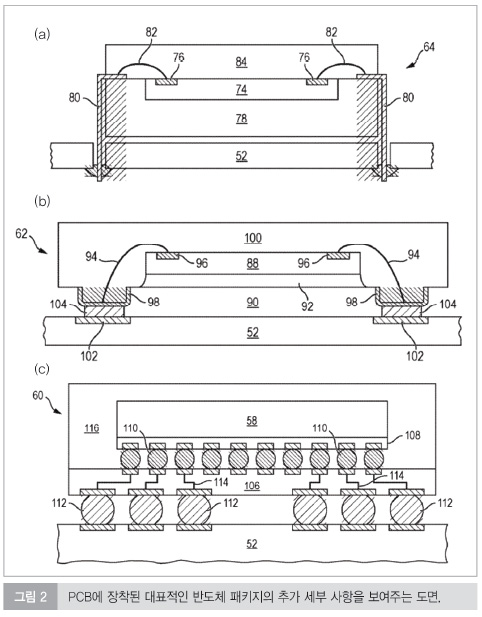

그림 2는 예시적인 반도체 패키지를 보여준다. 그림 2의 (a)는 PCB(52)에 장착된 DIP(64)를 더 자세히 보여준다.

반도체 다이(74)는 다이 내에 형성되어 다이의 전기적 설계에 따라 전기적으로 상호연결되는, 능동 장치, 수동 장치, 전도층 및 유전체 층으로 구현된 아날로그 또는 디지털 회로를 포함하는 능동 영역을 포함한다. 예를 들어, 회로는 반도체 다이(74)의 능동 영역 내에 형성된 하나 이상의 트랜지스터, 다이오드, 인덕터, 커패시터, 레지스터 및 다른 회로 요소를 포함할 수 있다. 접촉 패드(76)는 알루미늄(Al), 구리(Cu), 주석(Sn), 니켈(Ni), 금(Au) 또는 은(Ag)과 같은 전도성 물질의 하나 이상의 층이고, 반도체 다이(74) 내에 형성된 회로 요소에 전기적으로 연결된다. DIP(64)의 조립 동안, 반도체 다이(74)는 금 - 실리콘 공정 층 또는 열 에폭시 또는 에폭시 수지와 같은 접착 물질을 사용하여 중간 캐리어(78)에 장착된다. 패키지 몸체는 중합체나 세라믹 등의 절연성의 패키지 물질을 포함한다. 컨덕터 리드(80)와 본드 와이어(82)는 반도체 다이(74)와 PCB(52) 사이의 전기적 상호연결을 제공한다. 밀봉제(84)는 수분과 입자가 패키지에 들어가는 것을 방지하고 반도체 다이(74) 또는 본드 와이어(82)가 오염되는 것을 방지하는 주위 환경 보호를 위해 패키지 위에 증착된다.

그림 2의 (b)는 PCB(52)에 장착된 BCC(62)를 더 자세히 보여준다. 반도체 다이(88)는 언더필(underfill) 또는 에폭시-수지 접착 물질(92)을 사용하여 캐리어(90)에 장착된다. 본드 와이어(94)는 접촉 패드(96 와 98) 사이의 제 1 레벨 패키지 상호연결을 제공한다. 몰드 화합물 또는 밀봉제(100)는 장치에 대한 물리적 지지와 전기 절연을 제공하기 위해 반도체 다이(88)와 본드 와이어(94) 위에 증착된다. 접촉 패드(102)는 산화를 방지하기 위해 전해 도금 또는 무전해 도금과 같은 적합한 금속 증착 프로세스를 사용하여 PCB(52)의 표면상에 형성된다. 접촉 패드(102)는 PCB(52)에서 하나 이상의 전도성 신호 트레이스(54)에 전기적으로 연결된다. 범프(104)는 BCC (62)의 접촉 패드(98)와 PCB(52)의 접촉 패드(102) 사이에 형성된다.

그림 2의 (c)에서, 반도체 다이(58)는 플립 칩 형태의 제 1 레벨 패키지를 갖는 중간 캐리어(106)를 향해 아래로 장착된다. 반도체 다이(58)의 능동 영역(108)은 다이의 전기적 설계에 따라 형성된 능동 장치, 수동 장치, 전도층 및 유전체 층으로 구현된 아날로그 또는 디지털 회로를 포함한다. 예를 들어, 회로는 능동 영역 (108) 내에 하나 이상의 트랜지스터, 다이오드, 인덕터, 커패시터, 레지스터 및 다른 회로 요소를 포함할 수 있다. 반도체 다이(58)는 범프(110)를 통해 전기적 및 기계적으로 캐리어(106)에 연결된다.

BGA(60)는 범프(112)를 사용하여 BGA 형태의 제 2 레벨 패키지를 갖는 PCB(52)에 전기적 및 기계적으로 연결된다. 반도체 다이(58)는 범프(110), 신호 라인(114) 및 범프(112)를 통해 PCB(52)에서 전도성 신호 트레이스에 전기적으로 연결된다. 몰딩 화합물 또는 밀봉제(116)는 장치에 대한 물리적 지지와 전기 절연을 제공하기 위에 반도체 다이(58)와 캐리어(106) 상에 증착된다. 플립칩 반도체 디바이스는 신호 전파 거리를 줄이고, 낮은 커패시턴스 및 전체 회로 성능을 향상시키기 위해, 반도체 다이(58) 상의 능동 장치로부터 PCB(52) 상의 전도성 트랙을 향해 짧은 전기 전도성의 통로를 제공한다. 다른 실시예에서, 반도체 다이(58)는 중간 캐리어(106) 없는 플립칩 형태의 제 1 레벨 패키지를 사용하여 PCB(52)에 기계적 및 전기적으로 직접 연결될 수 있다.

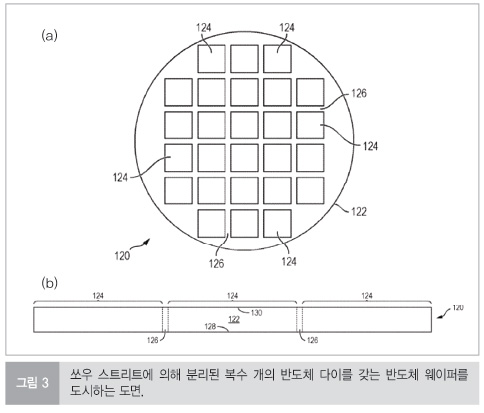

그림 3의 (a)는 구조적 지지를 위한, 실리콘, 게르마늄, 갈륨 비소, 인듐 인화물 또는 탄화 규소 등의 베이스 기판 물질(122)을 갖는 반도체 웨이퍼(120)를 보여준다. 복수의 반도체 다이 또는 부품(124)은 비-능동, 다이 사이의 웨이퍼 지역(inter-die wafer area) 또는 상술한 쏘우 스트리트(126)에 의해 분리된 웨이퍼 (120) 상에 형성된다. 쏘우 스트리트(126)는 반도체 웨이퍼(120)를 개별 반도체 다이(124)로 분리하는 커팅 영역을 제공한다. 그림 3의 (b)는 반도체 웨이퍼(120)의 일부 단면도를 보여준다. 각 반도체 다이(124)는, 다이 내에 형성되어 다이의 전기적 설계 및 기능에 따라 전기적으로 상호연결된 능동 장치, 수동 장치, 전도층 및 유전체 층으로 구현된 아날로그 또는 디지털 회로를 포함하는 후방 표면(128) 및 능동 표면(130)을 포함한다. 예를 들어, 회로는 디지털 신호 프로세서(DSP), ASIC, 메모리 또는 기타 신호 처리 회로 등의 아날로그 회로 또는 디지털 회로를 구현하기 위해 능동 표면(130) 내에 형성된 하나 이상의 트랜지스터, 다이오드 및 기타 회로 요소를 포함할 수 있다. 반도체 다이(124)는 RF 신호 처리를 위한, 인덕터, 커패시터 및 레지스터 등의 직접 수동 장치(IPDs)를 포함할 수 있다.

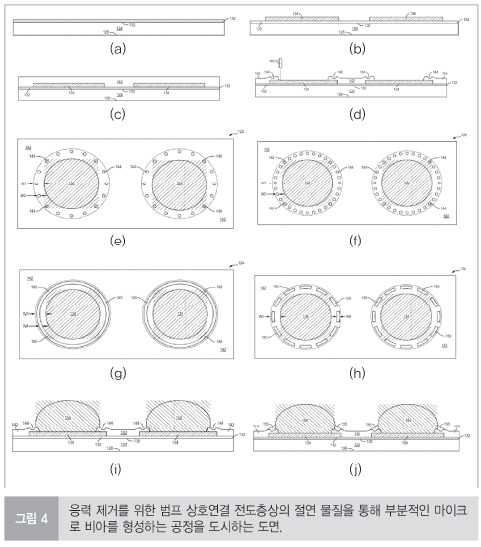

그림 4는 그림 1과 그림 2의 (a) 내지 그림 2의 (c)와 관련하여, 응력 제거를 위하여 범프 상호연결 전도층상의 절연 물질을 통해 부분적인 마이크로 비아를 형성하는 공정을 도시한다. 그림 4의 (a)는 반도체 웨이퍼(120)의 하나의 반도체 다이(124)의 일부분을 도시한다. 전도층 또는 보호 층(132)이 PVD, CVD, 인쇄, 스핀 코팅, 스프레이 코팅, 신터링(sintering) 또는 열적 산화(thermal oxidation)를 사용하여 반도체 다이(124)의 활성 표면상에 형성된다. 절연층(132)은 실리콘 디옥사이드(dioxide)(SiO₂), 실리콘 질화물 (nitride)(Si₃N₄), 실리콘 옥시니트라이트(oxynitride)(SiON), 탄탈 펜톡시드(tantalum pentoxide)(Ta₂O5), 알루미늄 산화물(Al₂O₃), 하프늄 산화물(hafnium oxide)(HfO₂), 벤조시클로부테인(benzocyclobutene)(BCB), 폴리이미드(polyimide)(PI), 폴리벤조사졸레(polybenzoxazoles)(PBO) 또는 기타 적당한 절연 물질 중 하나 이상의 층을 포함한다.

그림 4의 (b)에서, 전기 전도층(134)은 PVD, CVD, 전해 도금, 무전해 도금 공정 또는 다른 적당한 금속 증착 공정을 사용하여 절연층(132)에 형성된다. 전도층(134)은 Al, Cu, Sn, Ni, Au, Ag 또는 다른 적절한 전기 전도성 물질 중 하나 이상의 층이 될 수 있다. 전도층(134)은 활성 표면(130)상의 회로에 전기적으로 연결된 접촉 패드로서 작동한다. 접촉 패드(134)는 그림 4의 (b)에 도시된 바와 같이, 반도체 다이(124)의 에지로부터의 제1 거리에 나란하게 배치될 수 있다. 대안적으로, 접촉 패드(134)는, 접촉 패드의 제1 열이 다이의 에지로부터의 제1 거리에 배치되고 제1 열과 교대로 있는 접촉 패드의 제2열이 다이의 에지로부터의 제2 거리에 배치되도록, 다중으로 옵셋될 수 있다.

그림 4의 (c)에서, 절연층 또는 보호 층(142)이 PVD, CVD, 인쇄, 스핀 코팅, 스프레이 코팅, 신터링 또는 열적 산화를 사용하여 절연층(132)과 전도층(134) 상에 형성된다. 절연층(142)은 SiO₂, Si₃N₄, SiON, Ta₂O5, Al₂O₃, HfO₂, BCB, PI, PBO 또는 기타 적당한 절연 물질 중 하나 이상의 층을 포함한다. 절연층(142)은 3~70마이크로미터(㎛)의 두께를 갖는다.

그림 4의 (d)에서, 절연층(142)의 일 부분은 전도층(134)을 노출시키기 위해 패턴화된 포토레지스트 층을 통한 에칭 공정에 의해 제거된다. 대안적으로, 절연층(142)의 일 부분은 레이저(143)를 사용하는 레이저 직접 연마(LDA)에 의해 제거된다. 에칭 또는 LDA 공정은 전도층(134) 상의 절연층(142)을 통해 부분적으로 확장하는 마이크로 비아 또는 마이크로 개구(144)를 또한 형성한다. 마이크로 비아(144)는 전도층(134)을 노출시키지 않고 부분적으로 향상된 패턴을 얻기 위해 포토레지스트 해상도(photoresist resolution capability) 보다 작다.

그림 4의 (e)는 전도층(134)과 상기 전도층(134) 상의 절연층(142)을 통해 부분적으로 형성된 마이크로 비아(144)를 갖는 반도체 다이(124)의 평면도를 도시한다. 일 실시예에 있어서, 16개의 마이크로 비아(144)가 전도층(134) 상의 절연층(142)을 통해 부분적으로 형성된다. 절연층(142)과 전도층(134) 사이의 중첩부분은 20-50㎛의 폭(W1)을 갖는다. 마이크로 비아(144)는 0.5-10㎛의 폭(W2)을 갖고, 전도층(134)의 노출을 방지하기 위해 절연층(142)의 두께보다 작은 깊이를 갖는다. 그림 4의 (f)는, 32개의 마이크로 비아(144)가 전도층(134) 상의 절연층(142)을 통해 부분적으로 형성된 반도체 다이(124)의 평면도를 도시한다.

다른 실시예에 있어서, 그림 4의 (g)는 전도층(134)과 상기 전도층(134) 상의 절연층(142)을 통해 부분적으로 형성된 마이크로 비아 링(146)을 갖는 반도체 다이(124)의 평면도를 도시한다. 절연층(142)과 전도층(134) 사이의 중첩 부분은 20-50㎛의 폭(W3)을 갖고, 마이크로 비아 링(146)은 0.5-10㎛의 폭(W4)을 갖고, 전도층(134)의 노출을 방지하기 위해 절연층(142)의 두께보다 작은 깊이를 갖는다.

그림 4의 (h)는 전도층(134)과 상기 전도층(134) 상의 절연층(142)을 통해 부분적으로 형성된 마이크로 비아 슬롯(150)을 갖는 반도체 다이(124)의 평면도를 도시한다. 절연층(142)과 전도층(134) 사이의 중첩부분은 20-50㎛의 폭(W5)을 갖고, 마이크로 비아 슬롯(150)은 0.5-10㎛의 폭(W6)을 갖고, 전도층(134)의 노출을 방지하기 위해 절연층(142)의 두께보다 작은 깊이를 갖는다. 그림 4의 (i)에서, 전기 전도성 범프 물질은 증발(evaporation), 전해 도금, 무전해 도금, 볼 드롭(ball drop) 또는 스크린 인쇄 공정을 사용하여 전도층(134)과 절연층(142) 상에 증착된다. 범프 물질은 Al, Sn, Ni, Au, Ag, Pb, Bi, Cu, 솔더 및 그 조합일 수 있다. 예를 들어, 범프 물질은 공정 Sn/Pb, 고연 솔더(high-lead solder), 무연 솔더(lead-free solder)일 수 있다. 범프 물질은 적당한 접착 또는 본딩 공정을 사용하여 전도층(134)에 부착될 수 있다. 일 실시예에서, 범프 물질은 볼 또는 범프(154)를 형성하기 위해 그 용융점 이상에서 물질을 가열하여 재유동된다. 몇몇 적용에 있어서, 범프(154)는 전도층(134)에 대한 전기적 접촉을 향상시키기 위해 2차로 재유동된다. 범프(154)는 또한 전도층(134)에 압축 부착될 수 있다. 범프(154)는 전도층(134) 상에 형성될 수 있는 상호연결 구조물의 한 형태를 나타낸다. 상호연결 구조물은 또한 스터드 범프, 마이크로 범프 또는 다른 전기적 상호연결을 사용할 수 있다. 그림 4의 (j)에서, 절연층(156)은 마이크로 비아(144) 상에 그리고 그 안에 형성될 수 있고, 범프의 추가적인 구조적 지지를 위하여 범프(154) 상에 형성될 수 있다. 일 실시예에 있어서, 절연층(156)은 플럭스 잔사 폴리머(flux residue polymer)이다. 범프(154)는 반도체 다이(124)의 활성 표면(130) 상에 형성된 전도층(134)에 전기적으로 연결된다. 마이크로 비아(144)에 형성된 절연층(142)은 크랙킹과 다른 상호연결 결함을 감소시키기 위해 응력 프로파일을 재분배하여 범프(154)에 대한 응력 제거를 제공한다. 유사하게, 그림 4의 (h)~(i)에서 마이크로 비아 링(146) 또는 마이크로 비아 슬롯(150)은 전도층(134) 상의 절연층(142)의 크랙킹 및 다른 상호연결 결함을 감소시키기 위해 응력 프로파일을 재분배하여 범프(154)에 대한 응력 제거를 제공한다.

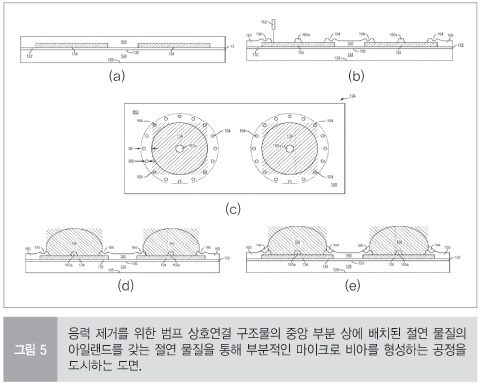

그림 5는 범프 상호연결 전도층 상의 절연 물질을 통해 부분적으로 마이크로 비아를 형성하는 다른 실시예를 도시하며, 범프 상호연결 전도층은 응력 제거를 위하여 범프 상호연결 구조물의 중앙 부분에 절연 물질이 배치된 아일랜드(Island)를 갖는다. 그림 4의 (b)로부터 계속하여, 절연 또는 보호 층(160)은 그림 5의 (a)에 도시된 바와 같이, PVD, CVD, 인쇄, 스핀 코팅, 스프레이 코팅, 신터링 또는 열적 산화를 사용하여 절연층(132)과 전도층(134) 상에 형성된다. 그림 5의 (b)에서, 절연층(160)의 일 부분은 전도층(134)을 노출시키기 위해 패턴화된 포토레지스트 층을 통한 에칭 공정에 의해 제거된다. 대안적으로, 절연층(160)의 일 부분은 레이저(162)를 사용하는 레이저 직접 연마(LDA)에 의해 제거된다. 에칭 또는 LDA 공정은 전도층(134) 상의 절연층(142)을 통해 부분적으로 확장하는 마이크로 비아 또는 마이크로 개구(164)를 또한 형성한다. 마이크로 비아(164)는 전도층(134)을 노출시키지 않고 부분적으로 향상된 패턴을 얻기 위해 포토레지스트 해상도 보다 작다. 그림 5의 (c)는 전도층(134)과 상기 전도층(134) 상의 절연층(160)을 통해 부분적으로 형성된 마이크로 비아(164)를 갖는 반도체 다이(124)의 평면도를 도시한다. 일 실시예에 있어서, 16개의 마이크로 비아(164)가 전도층(134) 상의 절연층(160)을 통해 부분적으로 형성된다. 절연층(160)과 전도층(134) 사이의 중첩부분은 20-50㎛의 폭(W1)을 갖는다. 마이크로 비아(164)는 0.5-10㎛의 폭(W2)을 갖고, 전도층(134)의 노출을 방지하기 위해 절연층(160)의 두께보다 작은 깊이를 갖는다. 추가적인 마이크로 비아(164)가 그림 4의 (f)와 유사하게, 전도층(134) 상의 절연층(160)을 통해 부분적으로 형성될 수 있다. 마이크로 비아 링 또는 마이크로 비아 슬롯은 그림 4의 (g)~(h)와 유사하게, 전도층(134) 상의 절연층(160)을 통해 부분적으로 형성될 수 있다.

그림 5의 (d)에서, 전기 전도성 범프 물질은 증발, 전해 도금, 무전해 도금, 볼 드롭 또는 스크린 인쇄 공정을 사용하여 전도층(134)과 절연층(160) 상에 증착된다. 범프 물질은 Al, Sn, Ni, Au, Ag, Pb, Bi, Cu, 솔더 및 그 조합일 수 있다. 예를 들어, 범프 물질은 공정 Sn/Pb, 고연 솔더(high-lead solder), 무연 솔더(lead-free solder)일 수 있다. 범프 물질은 적당한 접착 또는 본딩 공정을 사용하여 전도층(134)에 부착될 수 있다. 일 실시예에서, 범프 물질은 볼 또는 범프(166)를 형성하기 위해 그 용융점 이상에서 물질을 가열하여 재유동된다.

그림 5의 (e)에서, 절연층(168)은 마이크로 비아(164) 상에 그리고 그 안에 형성될 수 있고, 범프의 추가적인 구조적 지지를 위하여 범프(166) 상에 형성될 수 있다. 일 실시예에 있어서, 절연층(168)은 플럭스 잔사 폴리머이다. 범프(166)는 반도체 다이(124)의 활성 표면(130) 상에 형성된 전도층(134)에 전기적으로 연결된다. 마이크로 비아(164)에 형성된 절연층(160)은, 전도층(134)의 중앙 영역 위에 배치된 절연층(160)의 아일랜드(160a) 뿐만 아니라, 크랙킹 및 다른 상호연결 결함을 감소시키기 위해 응력 프로파일을 재분배하여 범프(166)에 대한 응력 제거를 제공한다.

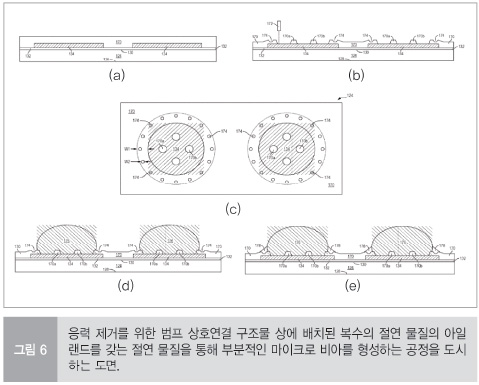

그림 6은 범프 상호연결 전도층 상의 절연 물질을 통해 부분적으로 마이크로 비아를 형성하는 다른 실시예를 도시하고 있으며, 범프 상호연결 전도층은 응력 제거를 위하여 범프 상호연결 구조물에 배치된 복수의 아일랜드를 갖는다. 그림 4의 (b)로부터 계속하여, 절연 또는 보호 층(170)은 그림 6의 (a)에 도시된 바와 같이, PVD, CVD, 인쇄, 스핀 코팅, 스프레이 코팅, 신터링 또는 열적 산화를 사용하여 절연층(132)과 전도층(134) 상에 형성된다. 절연층(170)은 3-70㎛의 두께를 갖는다. 그림 6의 (b)에서, 절연층(170)의 일 부분은 전도층(134)을 노출시키기 위해 패턴화된 포토레지스트 층을 통한 에칭 공정에 의해 제거된다. 대안적으로, 절연층(170)의 일 부분은 레이저(162)를 사용하는 레이저 직접 연마(LDA)에 의해 제거된다. 특히, 에칭 또는 LDA 공정은 전도층(134) 상에 배치된 절연층(170)의 복수의 아일랜드(170a-170b)를 남겨둔다. 에칭 또는 LDA 공정은 전도층(134) 상의 절연층(170)을 통해 부분적으로 확장하는 마이크로 비아 또는 마이크로 개구(174)를 또한 형성한다. 마이크로 비아(174)는 전도층(134)을 노출시키지 않고 부분적으로 향상된 패턴을 얻기 위해 포토레지스트 해상도 보다 작다.

그림 6의 (c)는 전도층(134)과 상기 전도층(134) 상의 절연층(170)을 통해 부분적으로 형성된 마이크로 비아(174)를 갖는 반도체 다이(124)의 평면도를 도시한다. 일 실시예에 있어서, 16개의 마이크로 비아(174)가 전도층(134) 상의 절연층(170)을 통해 부분적으로 형성된다. 절연층(170)과 전도층(134) 사이의 중첩부분은 20-50㎛의 폭(W1)을 갖는다. 마이크로 비아(174)는 0.5-10㎛의 폭(W2)을 갖고, 전도층(134)의 노출을 방지하기 위해 절연층(170)의 두께보다 작은 깊이를 갖는다. 추가적인 마이크로 비아(174)는 그림 4의 (f)와 유사하게, 전도층(134) 상의 절연층(170)을 통해 부분적으로 형성될 수 있다. 마이크로 비아 링 또는 마이크로 비아 슬롯은 그림 4의 (g)~(h)와 유사하게, 전도층(134) 상의 절연층(170)을 통해 부분적으로 형성될 수 있다.

그림 6의 (d)에서, 전기 전도성 범프 물질은 증발, 전해 도금, 무전해 도금, 볼 드롭 또는 스크린 인쇄 공정을 사용하여 전도층(134)과 절연층(170) 상에 증착된다. 범프 물질은 Al, Sn, Ni, Au, Ag, Pb, Bi, Cu, 솔더 및 그 조합일 수 있다. 예를 들어, 범프 물질은 공정 Sn/Pb, 고연 솔더, 무연 솔더 일 수 있다. 범프 물질은 적당한 접착 또는 본딩 공정을 사용하여 전도층(134)에 부착될 수 있다.

그림 6의 (e)에서, 절연층(178)은 마이크로 비아(174) 상에 그리고 그 안에 형성될 수 있고, 범프의 추가적인 구조적 지지를 위하여 범프(176) 상에 형성될 수 있다. 일 실시예에 있어서, 절연층(178)은 플럭스 잔사 폴리머이다. 범프(176)는 반도체 다이(124)의 활성 표면(130) 상에 형성된 전도층(134)에 전기적으로 연결된다.

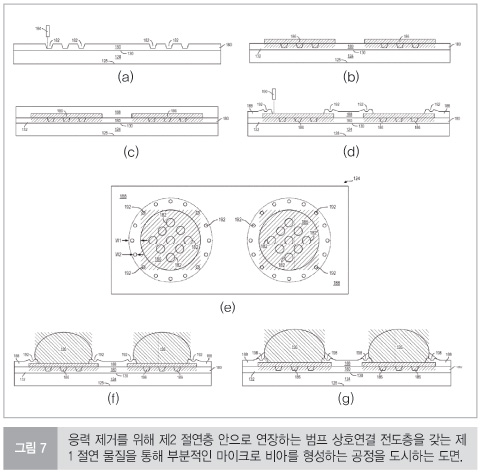

그림 7은 응력 제거를 위하여 제2 절연층 안으로 확장하는 범프 상호연결 전도층을 갖는 제1 절연 물질을 통해 부분적으로 마이크로 비아를 형성하는 다른 실시예를 도시한다. 그림 4의 (a)로부터 계속하여, 절연 또는 보호 층(180)은 그림 7의 (a)에 도시된 바와 같이, PVD, CVD, 인쇄, 스핀 코팅, 스프레이 코팅, 신터링 또는 열적 산화를 사용하여 반도체 다이(124)의 활성 표면(130) 상에 형성된다. 절연층(180)은 SiO₂, Si₃N₄, SiON, Ta₂O5, Al₂O₃, HfO₂, BCB, PI, PBO 또는 기타 적당한 절연 물질 중 하나 이상의 층을 포함한다. 절연층(180)은 3-70㎛의 두께를 갖는다. 절연층(180)의 일 부분은 절연층의 마이크로 비아 또는 마이크로 개구(182)를 형성하기 위해 에칭 공정에 의해 제거된다. 마이크로 비아(182)는 활성 표면(130)을 노출시키지 않고 부분적으로 향상된 패턴을 얻기 위해 포토레지스트 해상도 보다 작다. 일 실시예에 있어서, 마이크로 비아(182)는 5㎛의 폭과 10㎛의 피치를 갖는 지그재그식 배열(Staggered Layout)로 형성된다. 대안적으로, 절연층(180)의 일 부분은 절연층에 마이크로 비아 또는 마이크로 개구(182)를 형성하기 위해 레이저(184)를 사용하는 LDA에 의해 제거된다.

그림 7의 (b)에서, 전기 전도층(186)은 PVD, CVD, 전해 도금, 무전해 도금 공정 또는 다른 적당한 금속 증착 공정을 사용하여 절연층(180)상에 그리고 마이크로 비아(183) 내에 형성된다. 전도층(186)은 Al, Cu, Sn, Ni, Au, Ag 또는 다른 적절한 전기 전도성 물질 중 하나 이상의 층이 될 수 있다. 전도층(186)은 활성 표면(130)상의 회로에 전기적으로 연결된 접촉 패드로서 작동한다. 접촉 패드(186)는 반도체 다이(124)의 에지로부터의 제1 거리에 나란하게 배치될 수 있다. 대안적으로, 접촉 패드(186)는, 접촉 패드의 제1 열이 다이의 에지로부터의 제1 거리에 배치되고 제1 열과 교대로 있는 접촉 패드의 제2열이 다이의 에지로부터의 제2 거리에 배치되도록, 다중으로 옵셋될 수 있다.

그림 7의 (c)에서, 절연층 또는 보호 층(188)이 PVD, CVD, 인쇄, 스핀 코팅, 스프레이 코팅, 신터링 또는 열적 산화를 사용하여 절연층(180)과 전도층(186) 상에 형성된다. 절연층(188)은 SiO₂, Si₃N₄, SiON, Ta₂O5, Al₂O₃, HfO₂, BCB, PI, PBO 또는 기타 적당한 절연 물질 중 하나 이상의 층을 포함한다. 절연층(188)은 3-70㎛의 두께를 갖는다. 그림 7의 (d)에서, 절연층(188)의 일 부분은 전도층(186)을 노출시키기 위해 패턴화된 포토레지스트 층을 통한 에칭 공정에 의해 제거된다. 마이크로 비아(192)는 전도층(186)을 노출시키지 않고 부분적으로 향상된 패턴을 얻기 위해 포토레지스트 해상도 보다 작다. 대안적으로, 절연층(188)의 일 부분은 레이저(190)를 사용하는 LDA에 의해 제거된다. 에칭 또는 LDA 공정은 전도층(186) 상의 절연층(188)을 통해 부분적으로 확장하는 마이크로 비아 또는 마이크로 개구(192)를 또한 형성한다. 그림 7의 (e)는 전도층(134)과 전도층(186) 상의 절연층(188)을 통해 부분적으로 형성된 마이크로 비아(192)를 갖는 반도체 다이(124)의 평면도를 도시한다. 일 실시예에 있어서, 16개의 마이크로 비아(192)가 전도층(186) 상의 절연층(188)을 통해 부분적으로 형성된다. 절연층(188)과 전도층(186) 사이의 중첩부분은 20-50㎛의 폭(W1)을 갖는다. 마이크로 비아(192)는 0.5-10㎛의 폭(W2)을 갖고, 전도층(186)의 노출을 방지하기 위해 절연층의 두께보다 작은 깊이를 갖는다.

그림 7의 (f)에서, 전기 전도성 범프 물질은 증발, 전해 도금, 무전해 도금, 볼 드롭 또는 스크린 인쇄 공정을 사용하여 전도층(186)과 절연층(188) 상에 증착된다. 범프 물질은 Al, Sn, Ni, Au, Ag, Pb, Bi, Cu, 솔더 및 선택적인 플럭스 용제를 갖는 조합일 수 있다. 예를 들어, 범프 물질은 공정 Sn/Pb, 고연 솔더 또는 무연 솔더일 수 있다. 범프 물질은 적당한 접착 또는 본딩 공정을 사용하여 전도층(186)에 부착될 수 있다.

그림 7의 (g)에서, 절연층(198)은 마이크로 비아(192) 상에 그리고 그 안에 형성될 수 있고, 범프의 추가적인 구조적 지지를 위하여 범프(196) 상에 형성될 수 있다. 일 실시예에 있어서, 절연층(198)은 플럭스 잔사 폴리머이다. 범프(196)는 반도체 다이(124)의 활성 표면(130) 상에 형성된 전도층(186)에 전기적으로 연결된다. 마이크로 비아(182)는 높은 신뢰성을 위하여 범프(196) 아래의 전도층(186)의 두께를 증가시킨다. 마이크로 비아(164)에 형성된 절연층(188)은 크랙킹 및 다른 상호연결 결함을 감소시키기 위해 응력 프로파일을 재분배하여 범프(196)에 대한 응력 제거를 제공한다.

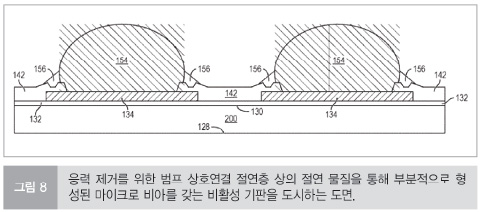

그림 8은 그림 4의 (a)~(i)와 유사한, 전도층(134), 절연층(142) 및 PCB와 같은, 비활성 기판(22)상에 형성된 범프(154)를 갖는 실시예를 도시한다. 전도층(134)은 전기적 상호연결을 위하여 기판(200) 내의 전도성 트레이스에 전기적으로 연결된다.