범프 접합 시의 휨 억제 목적

범프와 전극 단자의 간극 발생 억제를 통해 실현

종래의 반도체 소자의 실장 방법에서는 포름산을 범프에 도입할 때에 반도체 소자 상에 가압 장치가 올려놓아져 있기 때문에 포름산이 가압 장치를 돌아 들어가 범프에 공급되고 있었다. 그 때문에 포름산이 범프까지 충분히 도입되지 않아 범프 표면의 산화막 제거가 불충분해져 범프의 접합 강도가 충분히 확보되지 않는다는 문제가 발생하고 있었다. 본 발명은 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제하는 것을 목적으로 한다.

배경 기술

반도체 장치의 고기능화 소형화의 요청에 따라 반도체 소자를 복수개 늘어놓아 실장하여 하나로 패키지화하는 SiP(System in Package) 등의 반도체 장치가 이용되고 있다. 반도체 소자의 실장은 범프를 통하여 전극 단자 간을 땜납 접합함으로써 행해지지만 땜납 용융 시의 가열에 의해 반도체 소자가 휘어져 전극 단자 간의 접속 불량 등이 발생하는 경우가 있어 반도체 소자의 실장을 생산성 높게 행하는 것이 곤란했다. 휨의 원인은 반도체 소자 표면에 형성되는 회로에 이용되는 Al나 Cu 혹은 SiN, 폴리이미드 등의 절연막의 재료와 반도체 이면 재료의 선팽창 계수차에 의한 것이다. 특히, 반도체 장치의 소형화를 위해서 반도체 소자를 얇게 할수록 휨의 발생이 현저해지고 있다. 그 때문에 종래의 반도체 소자의 실장 방법에서는 땜납을 용융하고 나서 땜납이 응고되어 전극 단자간 접합이 완료될 때까지의 동안 반도체 소자의 휨을 규제하도록 반도체 소자를 가압하고 있었다.

상기 가압은 1개의 반도체 소자를 실장할 때마다 가압 부재를 이용하여 1개의 반도체 소자에 하중을 부가하여 행해지고 있었다. 또한, 반도체 소자의 실장 공정을 단축하기 위해서 복수의 반도체 소자를 1개의 가압 부재에 의해 가압하여 실장하는 경우도 있었다.

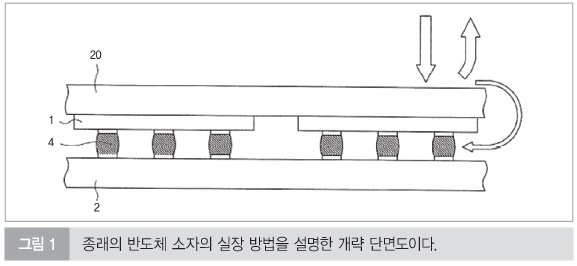

그림 1을 참조하여 종래의 반도체 소자의 실장 방법에 대해서 설명한다. 우선, 범프(4)를 통하여 서로의 전극 단자가 접속되도록 기판(2) 상에 복수의 반도체 소자(1)를 올려놓는다. 다음에, 반도체 소자(1) 상면을 가압한 상태로 범프를 가열, 냉각함으로써 범프를 통하여 전극 단자 간을 접합한다. 여기서, 반도체 소자(1)의 가압은 반도체 소자(1) 상면과 평행하게 모든 반도체 소자(1)를 덮는 크기 예를 들면, 기판(2)과 동일한 정도의 크기의 판형상의 가압 장치(20)를 이용하여 기판에 탑재된 다수 혹은 모든 반도체 소자(1) 상면 전체면에 접하도록 가압 장치(20)를 반도체 소자(1) 상면에 가압함으로써 행한다. 이와 같이, 범프(4)의 용융 시부터 응고할 때까지의 기간 가압을 행함으로써 반도체 소자(1)의 실장 시에 반도체 소자(1)가 휘는 것을 방지하고 있다. 여기서, 범프(4)와 전극 단자의 접합 시에 범프(4) 표면에 산화막이 형성되어 있으면, 범프(4)를 구성하는 땜납의 젖음성이 저하되고, 범프(4)와 전극 단자 간에 간극이 발생하여 접합 강도가 저하되는 문제가 발생하고 있었다. 그 때문에 종래의 반도체 소자의 실장 방법에서는 범프(4)에 포름산을 도입하면서 가열, 가압을 행하여 산화막을 환원하여 제거하면서 실장을 행하고 있었다.

발명의 내용

해결하려는 과제

종래의 반도체 소자의 실장 방법에서는 포름산을 범프(4)에 도입할 때에 반도체 소자(1) 상에 가압 장치(20)가 올려놓아져 있기 때문에 포름산이 가압 장치(20)를 돌아 들어가 범프(4)에 공급되고 있었다. 그 때문에 포름산이 범프(4)까지 충분히 도입되지 않아 범프(4) 표면의 산화막 제거가 불충분해져 범프(4)의 접합 강도가 충분히 확보되지 않는다는 문제가 발생하고 있었다.

본 발명은 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제하는 것을 목적으로 한다.

과제의 해결 수단

상기 목적을 달성하기 위해서 본 발명의 반도체 소자의 실장 방법은 기판 또는 제1 반도체 소자의 표면에 범프를 통하여 제2 반도체 소자를 접합하는 반도체 소자의 실장 방법에 있어서 기판 또는 복수의 제1 반도체 소자의 표면의 범프에 가접합한 복수의 제2 반도체 소자를 환원 가스 분위기 중에서 가압 수단에 의해 상기 기판 또는 복수의 제1 반도체 소자와 복수의 상기 제2 반도체 소자가 가까워지는 방향으로 가압하여 상기 범프를 가열하는 가압 가열 공정과 상기 가압 수단에 의한 상기 가압을 계속하면서 상기 범프를 냉각하는 가압 냉각 공정을 가지고, 상기 가압 수단에는 상기 환원 가스가 통과 가능한 환원 가스 유입 경로가 설치되어 있으며, 상기 가압 가열 공정과 상기 가압 냉각 공정에 의해 상기 기판 또는 복수의 제1 반도체 소자에 가접합된 상기 제2 반도체 소자를 본접합하여 실장하는 것을 특징으로 한다.

또, 상기 가압 부재가 각각 1개의 상기 제2 반도체 소자 또는 상기 제3 반도체 소자 상에 올려놓아져도 된다. 또, 상기 가접합한 복수의 제2 반도체 소자의 휨을 상기 본접합에서 억제하는 것이 바람직하다. 또, 상기 가접합한 상기 제2 반도체 소자의 적어도 일부에는 또한 다른 반도체 소자 또는 상기 제2 반도체 소자가 가접합되어 적층되어도 된다. 또, 상기 가압 수단은 복수의 상기 제2 반도체 소자를 개별적으로 가압하는 것이 바람직하다. 또, 상기 가압 단은 복수의 가압 부재와 상기 복수의 가압 부재를 서로 연결하는 접속부에 의해 구성해도 된다. 또, 상기 접속부가 메쉬형상 또는 격자형상이어도 된다.

또, 상기 접속부가 상기 가압 부재의 변위에 따라 변형 가능한 탄성을 가져도 된다. 또, 상기 가압 수단을 자성을 가지는 복수의 가압 부재로 구성하고 전자석을 이용하여 복수의 상기 가압 부재의 재치(載置) 및 인상을 제어해도 된다. 또, 상기 가압 수단을 상기 기판 또는 복수의 제1 반도체 소자와 복수의 상기 제2 반도체 소자가 가까워지는 방향으로 가압하는 복수의 핀으로 구성해도 된다. 또, 상기 가압 부재가 추여도 된다. 또, 상기 가압 수단을 복수의 상기 제2 반도체 소자를 둘러싸는 가이드와 상기 가이드로 둘러싸인 영역 내에 배치하는 입상물로 구성해도 된다. 또, 상기 기판 또는 하단이 되는 제1 반도체 소자가 웨이퍼에 형성된 복수의 반도체 소자여도 된다. 또, 상기 환원 가스가 포름산 가스 또는 수소 가스여도 된다.

발명을 실시하기 위한 구체적인 내용

기판이나 하단이 되는 반도체 소자의 표면에 복수의 반도체 소자를 늘어놓고, 각각의 전극 단자를 대응하는 기판이나 하단이 되는 반도체 소자의 표면에 형성된 전극 단자와 범프를 통하여 접합함으로써 개개의 반도체 소자를 기판이나 하단이 되는 반도체 소자의 표면에 실장한다. 이 때, 탑재하는 반도체 소자가 휘지 않도록 각 반도체 소자 상으로부터 가압 장치를 이용하여 가압한 상태로 범프 표면의 산화막을 제거하기 위해서 환원 가스를 범프에 도입하면서 범프를 일괄적으로 가열, 냉각하여 전극 단자 간을 땜납 접합한다. 그리고 가압 장치 내 적어도 반도체 소자와 접촉하는 가압 부재를 복수로 분할하고, 분할된 각 가압 부재로 가압함으로써 하나 또는 복수의 반도체 소자를 가압하는 것이 본 발명의 특징이다. 이와 같이 가압 부재를 분할하여 가압 부재와 가압 부재 간의 공간을 환원 가스의 유입 경로로서 확보함으로써 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 특히, 가압 부재로서 인가에 필요한 하중에 대응하는 무게의 추의 자중을 이용한 경우는 반도체 소자 상에 추를 올려놓은 후 추의 이동에 이용하는 가압 장치 본체를 반도체 소자로부터 이격할 수 있기 때문에 추의 상부 공간으로부터도 환원 가스의 유입 경로를 확보할 수 있어 보다 효율적으로 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 또, 반도체 소자를 하나씩 가압하여 실장하는 경우에도 1개의 반도체 소자 상에 추를 올려놓아 가압함으로써 반도체 소자 상부를 가압 장치가 덮는 일이 없어지기 때문에 환원 가스의 유입을 촉진할 수 있어 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 또, 자중에 의존하지 않고 반도체 소자를 가압하도록 가압 부재를 비접촉으로 제어함으로써도 가압 장치 본체가 환원 가스의 유통의 방해가 되지 않고 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 또, 실장 시간을 단축하기 위해서 실장 공정을 가접합 공정과 본접합 공정으로 나누어도 된다. 가접합 공정은 반도체 소자를 탑재할 때마다 행하여 가열 기간만 가압하는 것이다.

가접합에서는 적어도 위치 맞춤한 전극 단자 간을 반송 공정 등에 있어서 벗어나지 않을 정도로 고정할 수 있으면 된다. 본접합은 가접합을 복수의 반도체 소자에 대해서 행한 후에 일괄적으로 행하는 것이며, 가열부터 냉각 기간에 걸쳐 가압을 행한다. 그리고 적어도 본접합 공정에 있어서 가압을 복수로 분할한 가압 부재를 이용하여 가압 부재의 간극을 유로로 하여 환원 가스를 도입한다. 이와 같이 가압 부재를 분할하여 환원 가스의 유입 경로를 확보하면서 가압을 행함으로써 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있어 실장 시간의 대부분을 차지하는 공정인 냉각과 동시에 가압하는 공정을 모든 반도체 소자를 일괄적으로 행하는 본 공정만으로 행함으로써 실장 시간을 단축하여 생산성의 향상을 도모할 수 있다.

이하, 그림들을 이용하여 각 실시의 형태로서 구체적인 가압 방법을 설명한다. 여기에서는 가접합과 본접합에 의해 실장하는 방법을 이용하여 기판에 복수의 반도체 소자를 늘어놓아 실장하는 경우를 예로서 설명한다. 또, 가압 부재로서 추를 이용하는 경우를 예로 설명한다.

실시의 형태 1

그림 2는 실시의 형태 1에 있어서의 반도체 소자의 실장 방법의 가접합 공정을 순서대로 설명한 개략 단면도이다. 그림 2에 나타낸 바와 같이 실시의 형태 1에서는 가접합으로서 기판(2) 상에 반도체 소자를 실장하고, 또한, 반도체 소자에 인접하여 다른 반도체 소자(1)를 실장하며 이러한 실장을 반복하여 기판 표면에 복수의 반도체 소자를 병렬시켜 실장한다.

우선, 그림 2의 (a)에 나타낸 바와 같이 기판(2)의 전극 단자(7) 또는 반도체 소자(1)의 전극 단자(8) 중 어느 하나에 범프(4)를 형성한다. 다음에, 그림 2의 (b)에 나타낸 바와 같이 전극 단자(7, 8)의 위치를 맞추어 기판(2) 상에 반도체 소자(1)를 올려놓고, 가접합으로서 가열하면서 반도체 소자(1)를 가압하고, 가열을 종료함과 함께 가압도 종료한다. 또, 가열 대신에 초음파를 인가해도 된다. 이러한 가접합에 의해 그림 2의 (c)에 나타낸 바와 같이 범프(4)와 전극 단자(7, 8)의 계면 영역 만을 합금화하여 합금 영역(4b)을 형성함으로써 기판(2)과 반도체 소자(1)를 가접합한다. 이러한 부분적인 합금화는 가압, 가열 시간에 의해 제어된다. 이 때, 가압, 가열을 해제한 순간은 범프(4)의 합금화되어 있지 않은 영역인 비합금층(4a)은 용융 상태이다. 또, 가압을 해제함으로써 반도체 소자(1)는 표리의 선팽창 계수차에 의해 휨을 일으키기 시작한다. 이 상태에서 비합금층(4a)은 응고하기 시작하며, 반도체 소자(1)가 완전하게 휘기 전에 응고가 완료됨으로써 반도체 소자(1)의 휨을 억제하면서 반도체 소자(1)의 가접합을 행할 수 있다. 이와 같이 휨에 의한 응력이 범프(4)에 인가될 때에 비합금층(4a)은 합금화되지 않고 용융되어 있기 때문에 휨에 의해 범프(4)가 절단되는 것을 방지할 수 있다. 여기서, 가압, 가열을 해제한 후 냉각 가스 등으로 범프(4)를 냉각함으로써 응고가 촉진되어 보다 휨을 억제하면서 반도체 소자(1)를 가접합할 수 있다. 또한, 범프(4)의 형성부터 가접합을 행하여 반도체 소자(1)와 인접하여 기판(2) 상에 반도체 소자(3)를 실장한다. 이러한 반도체 소자의 실장을 반복하여 그림 2의 (d)에 나타낸 바와 같이 기판(2) 상에 복수의 반도체 소자를 병렬로 실장한다.

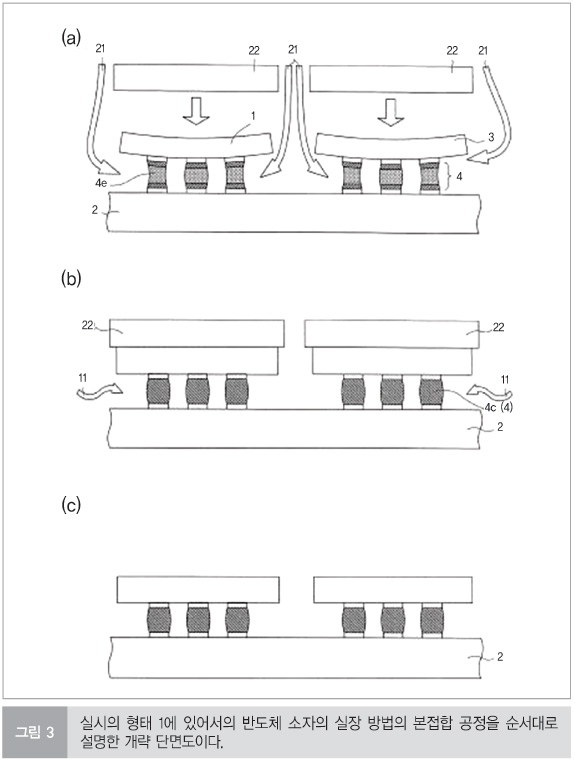

다음에, 그림 3에 나타낸 바와 같이 실시의 형태 1에서는 본접합으로서 가접합을 반복하여 실장한 반도체 소자(1, 3)의 범프(4)의 비합금층(4a)(그림 2 참조)을 일괄적으로 합금화한다.

우선, 그림 3의 (a)에 나타낸 바와 같이 기판(2) 상에 실장된 복수의 반도체 소자(1, 3)를 일괄적으로 가압한 상태로 가열한다. 이 때, 범프(4) 표면의 산화막을 환원 제거하기 위해서 범프(4)에 환원 가스(21)를 도입하면서 행한다. 이러한 가열에 의해 비합금층(4a)이 재용융되고, 이 상태에서 가압됨으로써 반도체 소자(1, 3)의 휨이 제거된다. 즉, 가열, 가압에 의해 반도체 소자(1, 3)의 휨이 복원되는 방향으로 작용하지만 범프(4)가 완전하게 합금화되지 않고 비합금층(4a)이 용융되기 때문에 반도체 소자(1, 3)의 복원을 저해하지 않고 용융된 비합금층(4a)이 휨의 복원을 흡수하여 반도체 소자의 휨을 제거할 수 있다. 본 실시의 형태에서는 복수의 추(22)를 이용하여 가압을 행하여 각 추(22)가 하나 또는 복수의 반도체 소자(1, 3)를 가압하는 것이 특징이다. 동시에 환원 가스(21)가 추(22)의 간극으로부터 범프(4)까지 유입될 수 있다.

다음에, 그림 3의 (b)에 나타낸 바와 같이 가열을 정지하고 가압 상태를 유지한 채로 냉각 가스(11)를 도입하여 범프(4)를 냉각한다. 이와 같이 가압 상태에서 범프(4)를 냉각함으로써 범프 전체가 응고되어 합금층(4c)이 되고, 반도체 소자가 휨이 없는 상태로 기판(2)에 실장 고정된다. 마지막으로 냉각 가스(11)의 도입 및 가압을 정지하면 그림 3의 (c)에 나타낸 바와 같이 기판(2) 상에 복수의 휨이 없는 반도체 소자가 실장된다.

이상과 같이, 본접합 시에 복수로 분할된 추(22)를 이용하여 기판 상에 병렬시켜 실장된 복수의 반도체 소자를 일괄적으로 가압할 수 있기 때문에 환원 가스(21)가 충분히 도입되어 범프(4)와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다.

또한, 요즈음의 반도체 장치의 소형화, 고기능화에 수반하여 실장되는 반도체 소자가 박형화, 단자가 협피치화되는 경향이 있다. 예를 들면, 반도체 소자 두께가 50μm, 전극 단자간 피치가 50μm 정도인 반도체 소자를 실장하는 경우가 있다. 반도체 소자를 박형화하는데 수반하여 반도체 소자의 휨이 촉진되고 협단자 피치화에 수반하여 환원 가스의 유통이 보다 곤란해진다. 그 때문에 박형화, 단자가 협피치화 된 반도체 소자의 실장 시에는 이상의 실장 방법에 의해 생산성을 높이면서 반도체 소자의 휨을 억제할 수 있으며, 추의 간극으로부터 환원 가스를 유입시킬 수 있으므로 보다 효과적으로 범프 접합의 강도를 유지할 수 있다.

또, 기판이나 하단의 반도체 소자 상에 높이가 상이한 반도체 소자를 실장하는 경우도 있다. 이 경우, 모든 반도체 소자를 1개의 추를 이용하여 가압하는 경우 반도체 소자의 높이의 차이에 기인하여 추가 기울어지는 경우가 있다. 기울어진 추로 반도체 소자를 가압하면 반도체 소자도 기울어져 실장되어 실장 불량이 발생하는 경우가 있었다. 이 경우에도 반도체 소자마다 추를 올려놓음으로써 반도체 소자의 높이의 차이에 기인하여 추가 기울어지는 일이 없어져 실장 불량의 발생을 저감시킬 수 있다.

또한, 땜납 재료로서는, SnAg, SnAgCu, SnZn, SnZnBi, SnPb, SnBi, SnAgBiIn, SnIn, In, Sn 등을 이용할 수 있다. 전극 단자로서는 예를 들면, AlCu, AlSiCu, AlSi, Cu, Al 등을 이용할 수 있다. 또한, 범프(4)로서 Cu를 내포한 Sn 등의 땜납 혹은 Cu의 표면에 Sn 등의 땜납을 설치한 Cu 필러 범프나 무전해 Ni도금 범프 등을 이용해도 된다. 또, 실장 조건은 범프(4)가 Sn2.3Ag인 경우 융점 T0는 220℃이며, 가접합의 가열 온도를 260~300℃로 설정하고, 가접합의 실장 시간은 0.25~2.0sec, 가접합의 가압 하중은 10~200N이 된다. 또, 본접합은 가열 온도를 245~260℃로 설정하고, 실장 시간은 30~300sec, 가압 하중은 0.1~0.5N이 된다.

또, 그림 2, 그림 3의 설명에서는 반도체 소자가 아래로 볼록한 방향으로 휘는 경우를 예시하고 있지만, 휨의 방향은 반도체 소자마다에서 임의이며 반도체 소자에 따라 휨의 방향이 상이한 경우에도 동일한 방법으로 실장이 가능하다.

실시의 형태 2

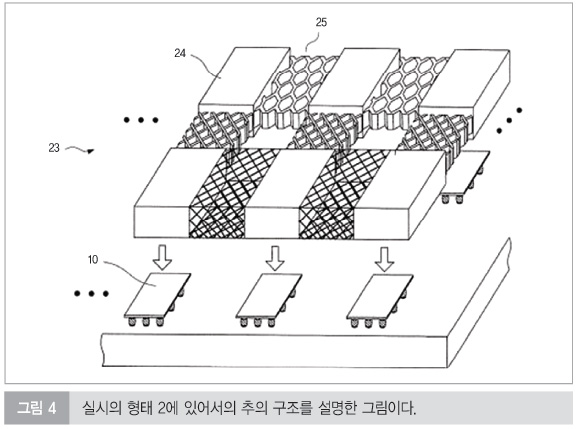

다음에, 그림 4를 이용하여 실시의 형태 2로서 추의 형태의 실시예를 설명한다. 그림 4는 실시의 형태 2에 있어서의 추의 구조를 설명한 그림이다.

그림 4에 나타낸 바와 같이 실시의 형태 2에 있어서의 추(23)는 반도체 소자(10)에 하중을 인가하는 복수의 가압부(24)와 가압부(24)를 연결하는 접속부(25)로 이루어지며 접속부(25)에 환원 가스의 유통이 가능하도록 메쉬형상 혹은 격자형상 등의 구멍을 구비하는 것을 특징으로 한다. 이러한 복수의 가압부(24)를 접속부(25)로 접속된 구조의 추(23)를 이용하여 실시의 형태 1에 있어서의 본접합 시의 가압을 행함으로써 가압부(24) 각각이 하나 또는 복수의 반도체 소자(10)를 가압하면서 접속부(25)로부터 환원 가스를 공급할 수 있다. 그 때문에 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 또, 가압부(24)가 접속부(25)로 접속되어 있기 때문에 가압의 인가 및 해제 공정을 용이하게 행할 수 있다.

또, 접속부(25)를 탄성을 가지는 유연한 재질로 형성함으로써 실장하는 반도체 소자의 높이가 불균일한 경우에도 가압부(24)의 높이의 변위에 따라 접속부(25)가 변형되어 높이의 차이를 흡수하여 가압부(24)가 기울어져 접속 불량이 발생하는 것을 억제할 수 있다.

접속부(25)의 재질은 예를 들면, 글라스 화이버 등의 섬유를 이용할 수 있다. 또, SUS, Al, Cu를 에칭하여 형성해도 된다.

상기 접속부(25)는 격자형상이나 메쉬형상 등의 환원 가스를 유통시킬 수 있는 구멍을 구비하고 있으면 되며, 다양한 구멍을 구비하는 형상이 혼재되어 있어도 된다. 그림 4에서는 격자형상과 메쉬 형상의 구멍 및 가압부(24) 사이에 망을 설치한 형상을 예시하고 있다. 추의 형상 이외의 가접합 공정 및 본접합 공정은 실시의 형태 1과 동일하므로 설명을 생략한다.

실시의 형태 3

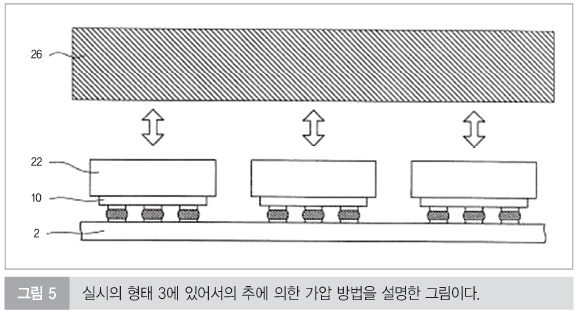

다음에, 그림 5를 이용하여 실시의 형태 3으로서 실시의 형태 1 및 실시의 형태 2의 추를 이용하여 하중을 인가 및 해제하는 방법의 실시예를 설명한다. 그림 5는 실시의 형태 3에 있어서의 추에 의한 가압 방법을 설명한 그림이다.

본 실시의 형태에 의한 가압 방법은 실시의 형태 1에 있어서의 추(22) 및 실시의 형태 2에 있어서의 추(23)(그림 4 참조)를 자성을 가지는 재질로 형성하여 전자석(26)에 의해 제어하는 것을 특징으로 한다. 즉, 가압 시에 우선, 전자석(26)을 도전하여 전자석(26)에 자성을 가지는 복수의 추(22) 혹은 가압부(24)(그림 4 참조)를 흡착한다. 또한, 추(22) 혹은 가압부(24)(그림 4 참조)는 기판(2)에 탑재된 반도체 소자(10)의 위치에 대응하여 흡착된다. 다음에 각각의 추(22) 혹은 가압부(24)(그림 4 참조)가 대응하는 반도체 소자(10) 상에 배치되도록 전자석(26)을 이동시킨다. 다음에, 전자석(26)에 공급되는 전류를 제어하여 각각의 반도체 소자(10) 상에 추(22) 혹은 가압부(24)(그림 4 참조)를 올려놓는다. 이후, 실시의 형태 1 및 실시의 형태 2에 있어서의 가접합 또는 본접합을 행한다. 마지막으로, 다시 전자석(26)을 도전하여 전자석(26)에 복수의 추(22) 혹은 가압부(24)(그림 4 참조)를 흡착하고, 반도체 소자(10)에 대한 가압을 해제한다. 이상의 설명 이외의 공정은 실시의 형태 1 혹은 실시의 형태 2와 동일하므로 설명을 생략한다.

이와 같이, 전자석(26)을 이용하여 추(22) 또는 추(23)(그림 4 참조)의 동작을 제어함으로써 용이하게 복수의 추(22) 또는 가압부(24)(그림 4 참조)에 의한 가압을 제어할 수 있어 가압에 의해 휨을 억제하면서 환원 가스를 범프에 도입하는 것이 용이해져 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 또, 반도체 소자가 휘어져 있는 경우 범프가 응고되어 있는 상태에서 가압을 더하면 반도체 소자가 깨지는 경우가 있었지만, 전자석(26)을 이용하여 추(22, 23)의 재치를 용이하게 제어할 수 있으므로 범프가 응고되어 있는 상태에서는 추(22, 23)를 올려놓지 않고, 용융되어 있는 상태에서 올려놓도록 추(22, 23)의 재치 타이밍을 용이하게 제어할 수 있다.

실시의 형태 4

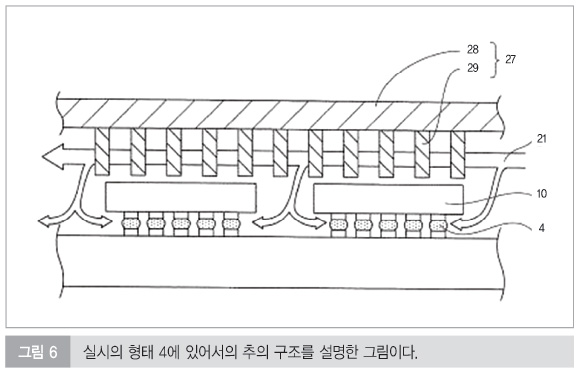

다음에, 그림 6을 이용하여 실시의 형태 4로서 추의 형태의 실시예를 설명한다. 그림 6은 실시의 형태 4에 있어서의 추의 구조를 설명한 그림이다. 그림 6에 나타낸 바와 같이 추(27)에 핀 형상을 설치함으로써 핀과 핀 사이로부터 환원 가스(21)를 유입시키는 것을 특징으로 한다. 즉, 추(27)는 기재(28)의 반도체 소자(10)와 서로 마주 보는 면에 복수의 길이가 동등한 핀(29)을 접속하는 구성이며 핀(29)이 반도체 소자(10) 표면을 누름으로써 가압하는 것을 특징으로 한다. 또한 가압 이외의 공정은 실시의 형태 1 혹은 실시의 형태 2와 동일하므로 설명을 생략한다.

이와 같이, 서로 간격을 둔 핀(27)에 의해 가압을 행함으로써 가압 중에 핀(27)의 간격으로부터 환원 가스(21)를 유입시켜 각 반도체 소자(10)의 범프(4)에 환원 가스(21)를 도입시킬 수 있으므로 가압에 의해 휨을 억제하면서 환원 가스(21)를 범프(4)에 도입하는 것이 용이해져 범프(4)와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 또, 핀(29)을 기재(28)에 전체적으로 설치한 경우 반도체 소자 사이즈나 반도체 소자간 피치에 제약되지 않고, 위치 맞춤도 불필요해지므로 용이하게 가압을 행하는 것이 가능하다.

또, 핀(29)은 신축 가능한 핀을 이용할 수도 있다. 또, 자중이나 비접촉에 의해 가압을 행하는 것에 한정되지 않고, 가압 장치로 기재(28)에 하중을 걸음으로서도 가압 장치 본체가 방해가 되지 않고, 핀(29) 사이를 환원 가스(21)가 유통할 수 있다. 또, 추(27)의 동작을 전자석으로 행할 수도 있다. 이 경우 기재(28)를 자성을 구비하는 재료로 형성한다. 또, 실장된 반도체 소자마다 추(27)를 올려놓을 수 있도록 분할하는 것도 가능하다.

실시의 형태 5

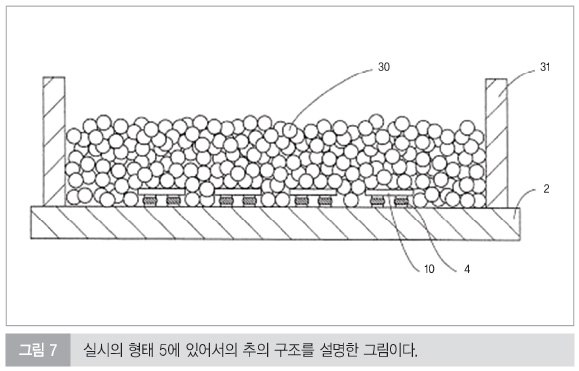

다음에, 그림 7을 이용하여 실시의 형태 5로서 추의 형태의 실시예를 설명한다. 그림 7은 실시의 형태 5에 있어서의 추의 구조를 설명한 그림이다. 그림 7에 나타낸 바와 같이 실시의 형태 5에 있어서의 추로서 다수의 입상물(30)을 이용하는 것을 특징으로 한다.

가압 시에는 우선, 복수의 반도체 소자(10)가 늘어서 접합된 기판(2) 상에 모든 반도체 소자(10)를 둘러싸는 가이드(31)를 설치한다. 다음에, 가이드(31) 내에 다수의 입상물(30)을 유입시킨다. 입상물(30)의 자중에 의해 각 반도체 소자(1)를 가압한다. 가압하는 압력은 입상물(30)의 무게와 개수로 조정한다. 하중을 해제할 때에는 가이드(31)를 떼어 입상물을 유출시킨다. 여기서, 입상물(30)은 구형인 것이 바람직하지만, 어느 정도의 유동성을 확보할 수 있으면 형상은 임의이다. 또, 크기는 입상물(30)의 최단 직경이 기판(2)과 반도체 소자(10)의 간격보다 크면 기판(2)과 반도체 소자(10) 사이에 유입되는 것이 없음으로 바람직하며, 반도체 소자(10) 표면에 균일하게 하중이 인가되도록 반도체 소자(10) 표면의 단변의 예를 들면 1/5보다 최단 직경이 작은 것이 바람직하다.

또, 입상물(30)의 재질을 철 등의 자성을 가지는 것으로 함으로써 입상물(30)의 유입 및 유출을 용이하고 또한 편리하게 행할 수 있다. 즉 가압 시에 가이드(31)를 기판(2) 상에 설치한 후, 입상물(30)을 흡착한 전자석을 가이드(31) 내에 이동시킨다. 다음에, 전자석의 전원을 차단하고, 입상물(30)을 가이드(31) 내에 유입시킨다. 제압 시에는 다시 전자석에 전원을 공급함과 함께 전자석을 반도체 소자(10)에 가까이하여 가이드(31) 내의 입상물(30)을 전자석에 흡착시킨다.

이상과 같이 입상물(31)을 이용하여 가압함으로써 입상물(31)의 간극을 통과하여 환원 가스가 공급되기 때문에 가압에 의해 휨을 억제하면서 환원 가스를 범프(4)에 도입하는 것이 용이해져 범프(4)와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 또, 반도체 소자 사이즈나 반도체 소자간 피치에 제약되지 않으며, 위치 맞춤도 불필요해지므로 용이하게 가압을 행하는 것이 가능하다.

실시의 형태 6

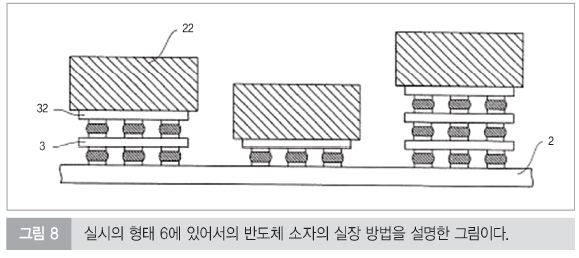

다음에, 그림 8을 이용하여 실시의 형태 6의 반도체 소자의 실장 방법을 설명한다. 그림 8은 실시의 형태 6에 있어서의 반도체 소자의 실장 방법을 설명한 그림이다.

그림 8에 나타낸 바와 같이 본 실시의 형태의 특징은 기판(2)에 형성되는 반도체 소자(3)의 적어도 일부에 또한 반도체 소자(32)가 적층되는 것이다. 기판(2) 상에 탑재되는 반도체 소자의 단수가 상이함으로써 탑재된 반도체 소자를 합한 높이가 상이한 경우여도 본접합 시에 추(22) 등의 실시의 형태 1~3에서 예시한 추를 반도체 소자마다 올려놓음으로써 추가 기울어지는 일 없이 접합 정밀도를 확보할 수 있음과 함께 가압에 의해 휨을 억제하면서 환원 가스를 범프에 도입하는 것이 용이해져 범프와 전극 단자 간에 간극이 발생하는 것을 억제하면서 범프 접합 시의 휨을 억제할 수 있다. 또, 실시의 형태 5와 같이 본접합 시에 입상물(30)(그림 7 참조)을 이용하여 가압을 해도 탑재된 반도체 소자를 합한 높이의 차를 유동하는 입상물(30)(그림 7 참조)로 흡수할 수 있으므로 반도체 소자의 접합 정밀도를 유지할 수 있다.

여기서, 가접합은 1개의 반도체 소자(3) 또는 반도체 소자(32)를 탑재할 때마다 행하고, 본접합은 모든 반도체 소자의 가접합이 종료된 후에 기판(2)마다 일괄적으로 행한다. 그 이외의 공정은 상기 각 실시의 형태와 동일하므로 설명을 생략한다.

실시의 형태 7

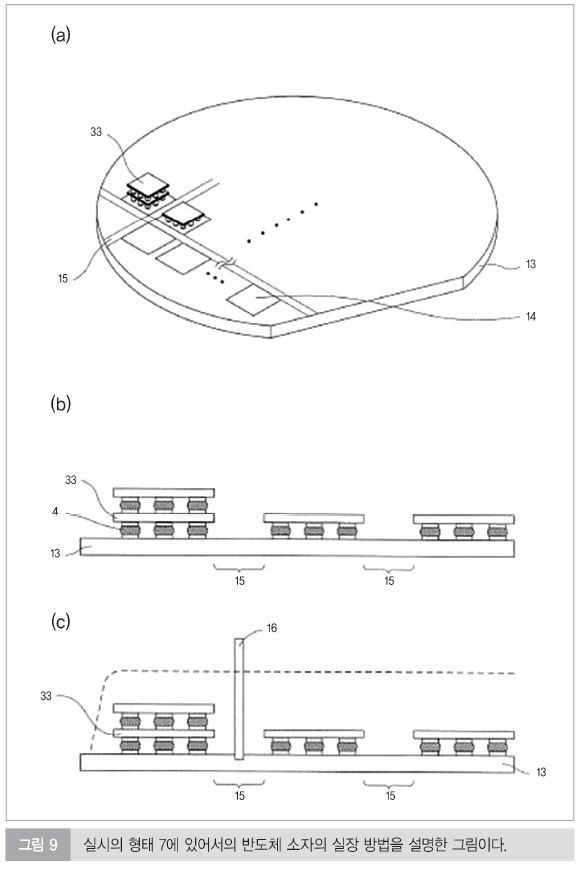

다음에, 그림 9를 이용하여 실시의 형태 7에 있어서의 반도체 소자의 실장 방법에 대해서 설명한다. 그림 9는 실시의 형태 7에 있어서의 반도체 소자의 실장 방법을 설명한 그림이며, 그림 9의 (a)는 반도체 소자를 실장한 웨이퍼의 구성을 나타낸 사시도, 그림 9의 (b)는 반도체 소자를 실장한 웨이퍼의 구성을 나타낸 단면도, 그림 9의 (c)는 적층한 반도체 소자를 개편화하는 공정을 설명한 단면도이다.

이상의 각 실시의 형태에서는 기판 혹은 반도체 소자 상에 복수단의 반도체 소자를 실장하는 방법에 대해서 설명했지만, 실시의 형태 7에 있어서의 반도체 소자의 실장 방법의 특징은 기판 대신에 복수의 반도체 소자가 형성된 웨이퍼의 각 반도체 소자 상에 하나 또는 복수단의 반도체 소자를 실장하는 것이다.

그림 9에 나타낸 바와 같이 웨이퍼(13)의 표면에는 복수의 반도체 소자(14)가 서로 스크라이브 영역(15)을 통하여 매트릭스형상으로 형성되어 있다. 본 실시의 형태에서는 우선, 웨이퍼 상태로 반도체 소자(14) 상에 하나 또는 복수의 반도체 소자(33)를 탑재한다. 이 때, 반도체 소자(33)를 탑재할 때마다 가접합하고, 모든 반도체 소자(33)의 가접합을 행하고 나서 웨이퍼(13) 단위로 일괄적으로 모든 반도체 소자의 범프(4)에 대해 환원 가스를 공급하면서 상기 각 실시의 형태에서 나타낸 반도체 소자마다 가압 부재를 올려놓는 가압을 행하여 본접합을 행한다(그림 9의 (a), 그림 9의 (b)).

이와 같이 하여 웨이퍼(13) 상의 반도체 소자(14) 상에 하나 또는 복수의 반도체 소자를 탑재한 상태로 각 반도체 소자를 일괄 몰드하고, 그 후, 스크라이브 영역(15)을 따라 다이싱 블레이드(16) 등을 이용하여 다이싱함으로써 반도체 소자가 적층된 반도체 소자(14)가 탑재된 반도체 장치를 개편화한다(그림 9의 (c)).

이상과 같이 웨이퍼 상태로 반도체 소자(14) 상에 반도체 소자(33)를 실장할 때마다 가접합하고, 모든 반도체 소자(33)의 가접합을 행한 후 웨이퍼 일괄로 본접합을 행함으로써 박형화, 단자가 협피치화된 반도체 소자여도 반도체 소자의 탑재마다 휨을 억제하여 접합하는 경우와 비교하면 생산성을 향상시키면서 범프(4)와 전극 단자 간에 간극이 발생하는 것을 억제함과 함께 범프 접합 시의 휨을 억제할 수 있다. 또한, 상기 각 실시의 형태에 있어서 환원 가스로서는 포름산 등의 카르본산 또는 H2가스 등을 이용할 수 있다. 또, 가접합 전에 Ar 플라즈마 세정을 행함으로써 범프 표면의 땜납 산화막을 제거해도 된다. 범프 표면의 산화물을 제거함으로써 접합부의 공극의 발생을 더 억제하고 접합 강도를 향상시킴과 함께 접합을 단시간에 행할 수 있다. 또한, Ar 플라즈마 세정 후 H2가스 분위기 중에서 유지함으로써 그 후의 산화를 억제할 수도 있다.