여러 가지 패키지 및 패키지를 형성하는 방법이 개시된다. 실시형태에 따르면, 패키지는 밀봉재에 의해 적어도 측방에서 밀봉되는 프로세서 다이와, 밀봉재에 의해 적어도 측방에서 밀봉되는 메모리 다이와, 밀봉재 상의 재분배(redistribution) 구조물을 포함한다. 프로세서 다이는, 재분배 구조물을 통하여 상기 메모리 다이에 소통 가능하게 결합된다. 추가적인 실시형태에 따르면, 메모리 다이는 프로세서 다이의 캐시인 메모리를 포함할 수 있고, 메모리 다이는 동적 랜덤 액세스 메모리(dynamic random access memory; DRAM)을 포함할 수 있다.

발명의 설명

배경 기술

종래의 프로세서 아키텍처에 있어서, 중앙 처리 장치(CPU) 또는 가속 프로세서 유닛(Accelerated Processor Unit; APU)의 캐시는, 통상 시스템 온 칩(System on Chip; SoC) 디바이스 내의 내장된 정적 랜덤 액세스 메모리(SRAM), 또는 일반적으로 시스템 인 패키지(System in Package; SiP) 디바이스를 위한 외부 SRAM이다. SRAM 아키텍처는 칩 영역의 관점에서 덜 효율적일 수 있고, 일반적으로 다른 메모리 아키텍처보다 더 고가이다.

해결하려는 과제

진보된 기술 노드[예컨대, 16 nm 핀 전계 효과 트랜지스터(fin field effect transistor; FinFET) 노드 등과 같은 20nm 미만의 노드]는, 이러한 노드 내에 내장된 SRAM을 제조하는 것에 대한 어려움 등으로 인해 SoC 디바이스를 위한 내장된 SRAM을 제공하지 못할 수도 있다.

과제의 해결 수단

실시형태는 이점을 달성할 수도 있다. 일부 실시형태에서, 메모리는 프로세서 다이로부터 제거될 수도 있고, 여전히 프로세서 다이에 매우 근접할 수도 있다. 이상의 실시형태에서 논의된 바와 같이, 제1 집적 회로 다이(20)는 CPU 또는 APU일 수 있고, 제2 집적 회로 다이(22)는 DRAM일 수 있다. 실시예에 도시된 바와 같이, CPU/APU는 패키지 외부의 어떤 접속 없이 패키지의 재분배 구조물을 통하여 DRAM에 소통가능하게 결합될 수도 있다. 전술한 바와 같이 패키지는 DRAM으로 하여금 CPU/APU에 대한 캐시가 되도록 허용할 수도 있다. 또한, DRAM을 이용하는 것은, 정적 랜덤 액세스 메모리(SRAM)와 같은 다른 메모리보다 더 영역 효율적일 수도 있으며, 이러한 SRAM은 캐시로서 사용될 수도 있다. DRAM은 또한 JEDEC Wide I/O에 대한 51 기가바이트/초(GB/s) 또는 Wide I/O 2 또는 JEDEC LPDDR4 표준에 대하여 25.6 GB/s와 같은 높은 대역폭을 가질 수 있다. 이러한 이점은 또한 프로세서 제품을 상품화하는데 도움을 준다.

실시형태는 패키지이다. 이 패키지는 밀봉재(encapsulant)에 의해 적어도 측방에서 밀봉되는 프로세서 다이와, 상기 밀봉재에 의해 적어도 측방에서 밀봉되는 메모리 다이와, 상기 밀봉재 상의 재분배(redistribution) 구조물을 포함한다. 상기 프로세서 다이는, 상기 재분배 구조물을 통하여 상기 메모리 다이에 소통 가능하게(communicatively) 결합된다.

다른 실시형태는 패키지이다. 패키지는 밀봉재와, 상기 밀봉재 내에 매립된 제1 다이와, 상기 밀봉재 내에 매립된 제2 다이를 포함한다. 상기 제1 다이는 프로세서 집적 회로부를 포함한다. 상기 제1 다이의 활성 측부 상에 제1 패드가 존재하며, 상기 제1 패드 상에 제1 다이 커넥터가 존재한다. 상기 제2 다이는 메모리 집적 회로부를 포함한다. 상기 제2 다이의 활성 측부 상에 제2 패드가 존재하며, 상기 제2 패드 상에 제2 다이 커넥터가 존재한다. 상기 제1 다이 커넥터의 표면, 상기 제2 다이 커넥터의 표면, 및 상기 밀봉재의 표면은 동일 평면상의 표면이다. 상기 패키지는 상기 동일 평면상의 표면에 있는 재분배 구조물을 더 포함한다. 상기 제1 다이는 상기 제1 다이 커넥터, 상기 재분배 구조물, 및 상기 제2 다이 커넥터를 통하여 상기 제2 다이에 소통가능하게 결합된다.

추가적인 실시형태는 방법이다. 이 방법은 제1 다이 및 제2 다이를 밀봉재 내에 밀봉하는 단계와, 이 밀봉재 상에 재분배 구조물을 형성하는 단계를 포함한다. 제1 다이는 프로세서를 포함하며, 제2 다이는 메모리를 포함한다. 재분배 구조물은 제1 다이를 제2 다이에 전기적으로 결합한다.

본 개시의 양태들은 첨부된 도면들과 함께 읽혀질 때 이하의 상세한 설명으로부터 가장 잘 이해된다. 산업 표준 관행에 따라, 다양한 특징부들이 축척비율대로 그려지는 것은 아니라는 점에 유의해야 한다. 사실상, 다양한 특징부들의 치수는 논의의 명료성을 위해 임의로 증가되거나 축소될 수 있다.

발명을 실시하기 위한 구체적인 내용

본 개시는 이러한 개시 상이한 특징들을 구현하기 위한 많은 상이한 실시형태들, 또는 예들을 제공한다. 본 개시를 간소화하기 위해 구성요소 및 장치의 특정 예가 이하에서 설명된다. 물론, 이들은 예일 뿐이며, 제한적인 것으로 의도되지는 않는다. 예를 들어, 후속하는 설명에서 제2 특징부 상의 또는 그 위의 제1 특징부는, 제1 특징부와 제2 특징부가 직접 접촉하여 형성되는 실시형태들을 포함할 수 있으며, 제1 특징부와 제2 특징부가 직접 접촉하지 않도록 제1 특징부와 제2 특징부 사이에 추가의 특징부들이 형성될 수 있는 실시형태들도 또한 포함할 수 있다. 또한, 본 개시는 다양한 예에서 참조 번호 및/또는 문자들을 반복할 수도 있다. 이러한 반복은 간소화와 명료화를 위한 것이며, 그 자체로 논의되는 다양한 실시형태들 및/또는 구성들 사이의 관계에 영향을 주는 것은 아니다.

또한, ‘아래의’, ‘아래쪽의’, ‘낮은’, ‘위의’, ‘상부의’ 등과 같은 공간적으로 상대적인 용어들이, 도면에 나타낸 하나의 요소 또는 특징부에 대한 또 다른 요소(들) 또는 특징부(들)의 관계를 논의하기 위해 설명의 편의상 여기에 사용될 수 있다. 공간적으로 상대적인 용어들은 도면들에 도시된 배향 외에도 사용 중이거나 동작 중인 장치의 상이한 배향들을 포괄하도록 의도된 것이다. 장치는 다른 방식으로 배향될 수도 있고(90도 회전되거나 기타의 배향) 여기서 사용된 공간적으로 상대적인 기술어(descrtiptor)는 그에 따라 유사하게 해석될 수 있다. 여기서 논의된 실시형태는, 특정 콘텍스트 즉, 팬-아웃 또는 팬-인 웨이퍼-레벨 패키지에서 논의될 수도 있다.

보다 상세하게는, 일부 실시형태는 패키지 내의 재분배 구조물에 의해 서로 연결되는 제1 집적 회로 다이 및 제2 집적 회로 다이에 관한 것이다. 일부 실시형태에서의 이러한 방식에 있어서, 제2 집적 회로 다이는, 중앙 처리 장치(Central Processing Unit) 또는 가속 프로세서 유닛(Accelerated Processor Unit; APU)과 같은 프로세서일 수도 있는 제1 집적 회로 다이에, 동적 랜덤 액세스 메모리(Dynamic Random Access Memory; DRAM)와 같은 캐시를 제공할 수도 있다. 다른 실시형태는, 본 개시를 읽을 때 당업자에게 쉽게 명백하게 되는 다른 패키지 타입 또는 다른 구성과 같은 다른 애플리케이션을 고려한다. 여기서 논의된 실시형태는 구조물에 존재할 수도 있는 모두 구성요소 또는 특징부(feature)를 반드시 예시할 필요는 없음을 주목해야 한다. 예컨대, 복수의 구성요소는, 구성요소들 중 하나에 대한 설명이 실시형태의 양태를 전달하기에 충분하게 될 때 등에 있어서, 도면으로부터 생략될 수도 있다. 또한, 여기서 논의된 방법 실시형태는, 특정 순서로 수행되는 것으로서 논의될 수도 있지만, 다른 방법 실시형태는 임의의 논리적 순서로 수행될 수도 있다.

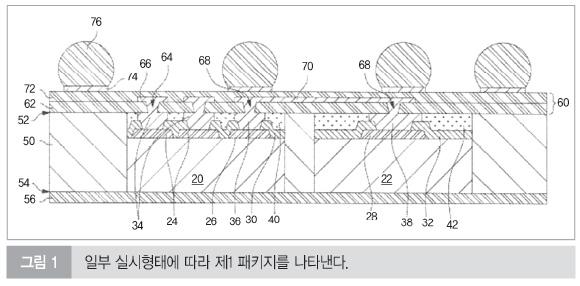

그림 1은 일부 실시형태에 따른 패키지를 나타낸다. 패키지는 밀봉재(encapsulant)(50)에 의해 밀봉되는 제1 집적회로 다이(20) 및 제2 집적 회로 다이(22)를 포함한다. 일부 실시형태에 따르면, 제1 집적 회로 다이(20)는 CPU, APU 등과 같은 프로세서의 집적 회로를 포함하며, 제2 집적 회로 다이(22)는 DRAM 등과 같은 메모리의 집적 회로를 포함한다. 이러한 예에 있어서, 제2 집적 회로 다이(22)는 JEDEC(Joint Electron Devices Engineering Council) Wide Input/Output(I/O) 또는 Wide I/O 2 표준 명세서에 따른다.

제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)는 집적 회로를 형성하기 위하여 적용 가능한 제조 프로세스에 따라서 처리될 수도 있다. 예컨대, 집적 회로 다이(20 및 22)는 각각 벌크 반도체 기판, 반도체-온-인슐레이터(semiconductor-on-insulator; SOI) 기판, 다층 또는 그레이디언트(gradient) 기판 등을 포함할 수도 있다.

일반적으로, SOI 기판은, 기판 상에 BOX(buried oxide), 실리콘 옥사이드 등과 같은, 절연체 층 상에 형성된 반도체 재료의 층을 포함한다. 기판의 반도체 재료는, 실리콘, 게르마늄 등과 같은 기본적인 반도체; 실리콘 게르마늄, 실리콘 카바이드, 갈륨 비소, 인듐 비소, 인화 인듐, 실리콘 게르마늄 카바이드, 인화 갈륨 비소, 인화갈륨 인듐, 이들의 조합 등과 같은 화합물 재료 등일 수 있다. 트랜지스터, 다이오드, 캐패시터, 저항 등과 같은 디바이스는, 반도체 기판 내에 및/또는 이 반도체 기판 상에 형성될 수도 있고, 예컨대 집적 회로를 형성하기 위하여 반도체 기판 상의 하나 이상의 유전체 층 내에 금속화 패턴에 의해 형성되는 상호접속 구조에 의해 상호 접속될 수도 있다.

제1 집적 회로 다이(20)는, 외부 접속이 행해지는 알루미늄 패드와 같은 패드(24 및 26)를 더 포함하며, 제2 집적 회로 다이(22)는, 외부 접속이 행해지는 알루미늄 패드와 같은 패드(28)를 더 포함한다. 패드(24, 26 및 28)는 각각의 집적 회로 다이(20 및 22)의 활성 측부로서 참조될 수도 있는 것 위에 있다. 패시베이션 필름(30)은 제1 집적 회로 다이(20) 상에 그리고 패드(24 및 26)의 일부 위에 존재하고, 패시베이션 필름(32)은 제2 집적 회로 다이(22) 상에 그리고 패드(28)의 일부 위에 존재한다. 개구는 패시베이션 필름(30 및 32)을 관통하여 각각의 패드(24, 26 및 28)에 이어져 있다.

도전성 필러와 같은 다이 커넥터(34, 36, 38)[예컨대, 구리와 같은 금속을 포함함]는 패시베이션 필름(30 및 32)을 관통하는 개구 내에 존재하며, 각각의 패드(24, 26 및 28)에 기계적 및 전기적으로 결합된다. 다이 커넥터(34, 36 및 38)는, 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)의 각각의 집적 회로를 전기적으로 결합한다. 감소된 개수의 다이 커넥터는, 명료화 및 단순화를 위하여 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)의 각각에 도시되며, 당업자는 더 많은 다이 커넥터가 존재할 수도 있음을 쉽게 이해한다. 또한, 다이 커넥터의 상대적인 크기 및/또는 피치는 다양한 개념을 더욱 명료하게 전달하기 위하여 예시에 있어서 과장될 수도 있다. 다이 커넥터(34, 36 및 38)의 더욱 상세한 내용을 그림 2를 참조하여 설명한다.

유전체 재료(40)는 패시베이션 필름(30) 및 다이 커넥터(34 및 36) 위와 같은 제1 집적 회로 다이(20)의 활성측부 상에 존재하고, 유전체 재료(42)는 패시베이션 필름(32) 및 다이 커넥터(38) 위와 같은 제2 집적 회로 다이(22)의 활성 측부 상에 존재한다. 유전체 재료(40)는 측방에서 다이 커넥터(34 및 36)를 밀봉하며, 유전체 재료(40)는 측방에서 제1 접적 회로 다이(20)에 대한 공동 종점(co-terminus)이다. 이와 유사하게, 유전체 재료(42)는 다이 커넥터(380)를 측방에서 밀봉하고, 유전체 재료(42)는 측방에서 제2 집적 회로(22)에 대한 공동 종점이다. 유전체 재료(40 및 42)는, PBO(polybenzoxazole), 폴리이미드, BCB(benzocyclobutene) 등과 같은 폴리머; 실리콘 니트라이드 등과 같은 질화물; 실리콘 옥사이드, PSG(PhosphoSilicate Glass), BSG(Borosilicate Glass), BPSG(Boron-doped PhosphoSilicate Glass) 등과 같은 산화물; 또는 이들의 조합일 수도 있다.

밀봉재(50)는 측방에서 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)를 밀봉한다. 밀봉재(50)는 몰딩 화합물, 에폭시 등일 수도 있다. 밀봉재(50)의 제1 표면(52)은 유전체 재료(40 및 42)의 표면 및 다이 커넥터(34, 36 및 38)의 표면과 동일 평면상에 존재한다. 제1 표면(52)과 대향하는 밀봉재(50)의 제2 표면(54)은, 제1 집적회로 다이(200) 및 제2 집적 회로 다이(22)의(예컨대, 활성 측부와 대향하는) 이면의 표면과 동일 평면상에 존재한다. 다른 실시형태에서, 여러 가지 표면은 동일 평면상에 존재하지 않을 수도 있다. 예시된 바와 같이, 접착 필름일 수도 있는 DAF(die-attach-film)(56)는, 밀봉재의 제2 표면(54) 그리고 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)의 이면의 표면 상에 존재한다. 일부 실시형태에서, DAF(56)은 생략될 수도 있다.

재분배 구조물(60)은, 밀봉재(50)의 제1 표면(52) 상에 그리고 유전체 재료(40 및 42) 및 다이 커넥터(34, 36 및 38)의 표면 상에 존재한다. 재분배 구조물(60)은, 제1 유전체 층(62), 제2 유전체 층(72) 및 여러 가지 금속화 패턴 및 비아를 포함한다. 제1 유전체 층(62)은 밀봉재(50)의 제1 표면(52) 상에 그리고 유전체 재료(40 및 42)의 표면 상에 존재한다. 비아(64 및 68)와 같은 비아는 제1 유전체 층(62)을 관통하여 존재하며, 각각의 다이 커넥터(34, 36 및 38)에 직접 결합된다. 금속화 패턴(66)은 제1 유전체 층(62) 상에 존재한다. 제2 유전체 층(72)은 금속화 패턴(66) 및 제1 유전체 층(62) 상에 존재한다. 개구(도시되지 않음)는 제2 유전체 층(72)을 관통하며, 금속화 패턴은 개구 내에 형성되고 제2 유전체 층(72) 상에 본드 패드(74)를 형성하기 위하여 존재한다. 제1 유전체 층(62) 및 제2 유전체 층(72)은, PBO, 폴리이미드, BCB 등과 같은 폴리머; 실리콘 니트라이드와 같은 질화물; 실리콘 옥사이드, PSG, BSG, BPSG와 같은 산화물 등일 수도 있다. 여러 가지 금속화 패턴, 비아 및 본드 패드는, 구리, 티타늄, 텅스텐, 알루미늄 등과 같은 금속 또는 이들의 조합을 포함할 수도 있다. 재분배 구조물(60)은 임의의 개수의 유전체 층 및 금속화 패턴을 포함할 수도 있다. 외부 전기 커넥터(76)는 본드 패드(74) 상에 존재한다. 외부 전기 커넥터(76)는 땜납과 같은 저온 리플로우 가능한 재료를 포함할 수도 있고, 이는 납이 없는 것 또는 납을 포함하는 것일 수도 있다. 외부 전기 커넥터(76)는 볼 그리드 어레이(ball grid array; BGA)일 수도 있다.

금속화 패턴(66) 내의 비아(68) 및 라인(70)은 재분배 구조물 내에 다이 대 다이 접속을 형성한다. 제1 집적 회로 다이(20) 상의 다이 커넥터(36)는 비아(68)에 직접 결합되며, 이 비아(68)는 라인에 집적 결합된다. 라인(70)은 다른 비아(68)에 직접 결합되며, 이는 제2 직접 회로 다이(22) 상의 다이 커넥터(38)에 직접 결합된다. 그러므로 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)는, 패키지 외부의 임의의 접속에 대한 필요성 없이, 예컨대, 재분배 구조물(60)을 통하여 패키지 내에 소통가능하게 결합된다. 그림 1의 예시된 다이 대 다이 접속은 예로서 도시되며, 재분배 구조물 내의 다이 대 다이 접속에 대한 다른 구성이 사용될 수도 있다.

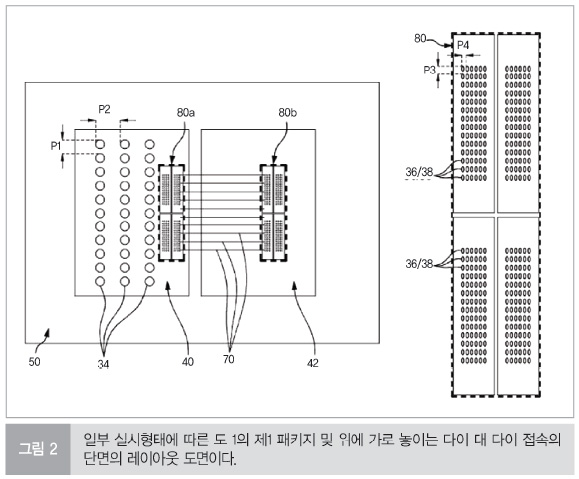

그림 2의 (a)는 일부 실시형태에 따르면, 위에 가로 놓이는 다이 대 다이 접속 상태에서, 밀봉재(50)의 제1 표면(52), 유전체 재료(40 및 42)의 표면, 다이 커넥터(34, 86 및 88)의 표면의 레이아웃 도면이다. 다이 커넥터(34)는 일반적으로 제1 집적 회로 다이(20) 상의 어레이로서 배치된다. 다이 커넥터(34)는 다이 커넥터(34)의 각각의 이웃하는 쌍 사이에 (예컨대, y-방향으로의) 제1 피치(P1), 및 (예컨대, x-방향으로의) 제2 피치(P2)를 가질 수 있다. 다이 커넥터(34)의 제1 피치(P1) 및 제2 피치(P2)의 각각은, 약 80㎛와 같은, 약 20㎛ 내지 약 150㎛일 수도 있다. 다이 커넥터(36)는 제1 집적 회로 다이(20) 상의 영역(80a) 내에 배치되며, 다이 커넥터(38)는 제2 집적 회로 다이(22) 상의 영역(80b) 내에 배치된다. 제2 집적 회로 다이(22) 상의 영역(80b)은 일반적으로 제2 집적 회로 다이(22) 상의 중앙에 위치된다. 라인(70)은 제1 집적 회로 다이(20)의 다이 커넥터(36)와 제2 집적 회로 다이(22)의 다이 커넥터(38) 사이의 다이 대 다이 접속을 나타내기 위하여 영역(80a)와 영역(80b) 사이에 나타내어진다. 영역(80a 및 80b)은 일반적으로 그림 2의 (b)에서 영역(80)으로서 더욱 더 상세하게 도시된다. 각각이 다이 커넥터(36/38)[제1 집적 회로 다이(20)에 대한 다이 커넥터(36) 및 제2 집적 회로 다이(22)에 대한 다이 커텍터(38)]의 어레이를 포함하는 4 개의 4분면이 영역(80) 내에 존재한다. 다이 커넥터(36/38)는 영역(80)의 4분면 내의 다이 커넥터(36/380의 각각의 이웃하는 쌍 사이에 (예컨대, y-방향으로의) 제1 피치(P3) 및 (예컨대, x-방향으로의) 제2 피치(P4)를 가질 수 있다. 다이 커넥터(36/38)의 제1 피치(P3) 및 제2 피치(P4)의 각각은, 약 40㎛와 같은 약 20㎛ 내지 약 60㎛일 수도 있다. 제1 피치(P1)는 제1 피치(P3)보다 더 크고, 제2 피치(P2)는 제2 피치(P4) 보다 더 크다.

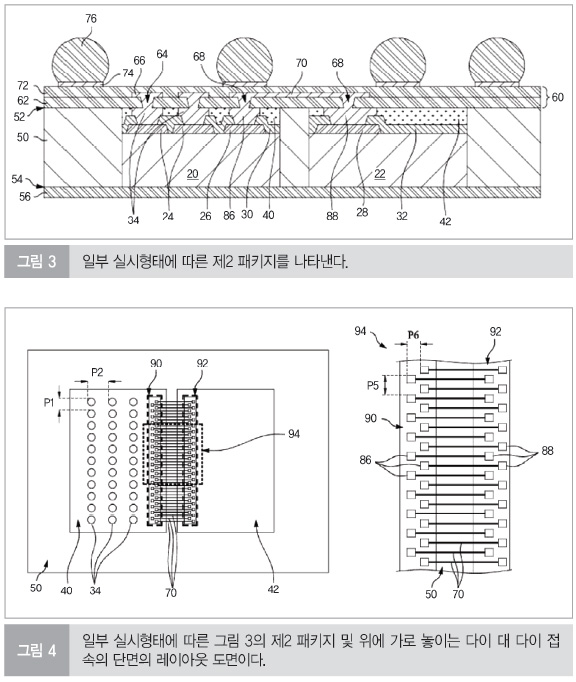

그림 3은 일부 실시형태에 따른 다른 패키지를 나타낸다. 그림 3의 패키지는 일반적으로 그림 1의 패키지와 유사하므로, 그림 3 및 그림 1에 도시된 공통적인 구성요소는 간결성을 위하여 여기서는 논의되지 않는다. 이러한 예에 있어서, 제2 집적 회로 다이(22)는, JEDEC DDR(Double Data Rate) 또는 LPDDDR(Low Power DDR) 표준 명세서에 따른다. 그림 1의 패키지 내의 다이 커넥터(36 및 38)는 그림 3의 패키지 내의 다이 커넥터(86 및 88)로 대체된다. 이러한 다이 커넥터(86 및 88)의 부가적인 세부사항은 그림 4에 도시된다.

그림 4의 (a)는 일부 실시형태에 따르면, 위에 가로 놓이는 다이 대 다이 접속 상태에서, 밀봉재(50)의 제1 표면(52), 유전체 재료(40 및 42)의 표면, 다이 커넥터(34, 86 및 88)의 표면의 레이아웃 도면이다. 다이 커넥터(34)는 일반적으로 그림 2의 (a)에 논의된 바와 같이 배치된다. 다이 커넥터(86)는 일반적으로 제1 집적 회로 다이(20) 상의 영역(80) 내에 배치되며, 다이 커넥터(88)는 일반적으로 제2 집적 회로 다이(22) 상의 영역(92) 내에 배치된다.

영역(90 및 92)은 일반적으로 각각의 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)의 측방 에지에 대응하여 근접한 영역을 따라 그리고 그 영역 내에 위치된다. 라인(70)은 제1 집적 회로 다이(20)의 다이 커넥터(86)와 제2 집적 회로 다이(22)의 다이 커넥터(88) 사이의 다이 대 다이 접속을 나타내기 위하여 영역(90)과 영역(92) 사이에 나타내어진다. 영역(90 및 92)의 일부(94)는 일반적으로 그림 4의 (b)에 더욱 상세하게 도시된다. 제1 집적 회로 다이(20) 상의 영역(90) 내의 다이 커넥터(86)는 일반적으로 예컨대, y-방향을 따라, 영역(90)이 근접하는 제1 집적 회로 다이(20)의 측방 에지에 평행한 2개의 열에 배치된다. 다이 커넥터(86)는 영역(90)이 근접하는 제1 집적 회로 다이(20)의 측방 에지에 수직한 방향 예컨대 x-방향에 대하여 오프셋된다. 이와 유사하게, 제2 집적회로 다이(22) 상의 영역(92) 내의 다이 커넥터(88)는 일반적으로 영역(82)이 근접해 있는 제2 집적 회로 다이(22)의 측방 에지에 평행한 2 개의 열에 배치된다. 다이 커넥터(88)는 영역(92)이 근접해 있는 제2 집적 회로 다이(22)의 측방 에지에 수직한 방향에 대하여 오프셋된다. 다이 커넥터(86 및 88)는, 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22) 중 각각의 하나 위의 다이 커넥터(86 및 88)의 각각의 이웃하는 쌍 사이에(예컨대, y-방향의) 제1 피치(P5) 및 (예컨대, x-방향의) 제2 피치(P6)를 가질 수 있다. 다이 커넥터(86 및 88)의 제1 피치(P5) 및 제2 피치(P6)의 각각은 약 80㎛와 같은, 약 40㎛ 내지 약 200㎛일 수 있다. 제1 피치 (P1)는 제1 피치(P5)보다 더 크고, 제2 피치(P2)는 제2 피치(P6) 보다 더 크다.

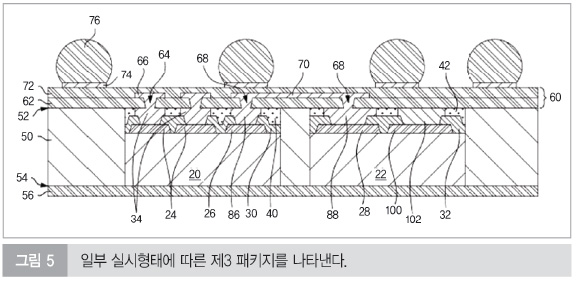

그림 5는 일부 실시형태에 따른 다른 패키지를 나타낸다. 그림 5의 패키지는 일반적으로 그림 3의 패키지와 유사하므로, 그림 5 및 그림 3에 도시된 공통적인 구성요소는 간결성을 위하여 여기서는 논의되지 않는다. 제2 집적 회로 다이(22)는, 제2 집적 회로 다이(22)의 활성 측부 상에, 알루미늄 패드와 같은 더미 패드(100)를 더 포함한다. 패시베이션 필름(32)은 더미 패드(100)의 일부 위에 존재한다. 개구는 패시베이션 필름(32)을 관통하여 더미 패드(100)에 이어져 있다. 도전성 필러(예컨대, 구리와 같은 금속을 포함함)와 같은 더미 다이 커넥터(102)는 패시베이션 필름(32)을 관통하는 개구 내에 존재하며, 더미 패드(100)에 기계적으로 결합된다. 더미 다이 커넥터(102) 및 더미 패드(100)는 다른 디바이스 또는 도전성 특징부에 전기적으로 결합되지 않을 수도 있다. 감소된 개수의 더미 다이 커넥터(102)는 명료화 및 단순화를 위하여 제2 집적 회로 다이(22) 상에 도시되며, 당업자는 더 많은 더미 다이 커넥터가 존재할 수도 있음을 쉽게 이해한다. 또한, 더미 다이 커넥터의 상대적인 크기 및/또는 피치는 다양한 개념을 더욱 명료하게 전달하기 위하여 예시에 있어서 과장될 수도 있다. 더미 다이 커넥터(102)의 더욱 상세한 내용을 그림 6을 참조하여 설명한다.

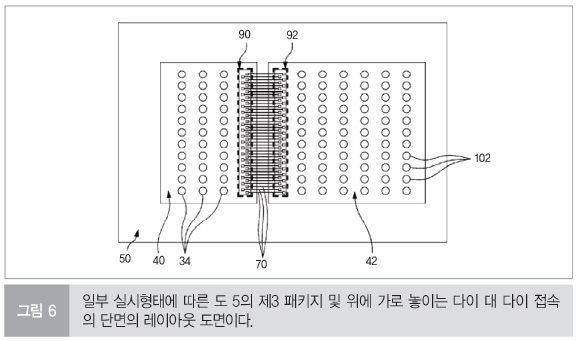

그림 6은 일부 실시형태에 따르면, 위에 가로 놓이는 다이 대 다이 접속 상태에서, 밀봉재(50)의 제1 표면(52), 유전체 재료(40 및 42)의 표면, 다이 커넥터(34, 86 및 88)의 표면의 레이아웃 도면이다. 그림 6의 레이아웃 도면은, 그림 4의 (b)에 도시된 부가적인 세부사항을 포함하여, 일반적으로 그림 4의 (a)의 레이아웃 도면과 동일하다. 더미 다이 커넥터(102)는 영역(92) 외부의 제2 집적 회로 다이(22) 상의 어레이로서 배치된다. 임의의 개수의 더미 다이 커넥터(102)가 사용될 수도 있으며, 더미 다이 커넥터(102)는 임의의 크기를 가진 임의의 구성 내에 존재할 수도 있다. 더미 다이 커넥터(102)는, 포토리소그래피, 도금 및/또는 에칭 프로세스 동안에 패키지를 형성하는데 사용되는 일부 프로세스에서 프로세싱 균일성을 증가시킬 수도 있고, 이는 이후에 논의될 것이다. 그림 5 및 그림 6은 그림 3, 그림 4에서 논의된 영역(90 및 92)의 콘택스트에서 논의되었지만, 당업자는 더미 다이 커넥터(102) 및 더미 패드(100)가 그림 1, 그림 2의 패키지에 통합될 수도 있음을 쉽게 이해할 것이다.

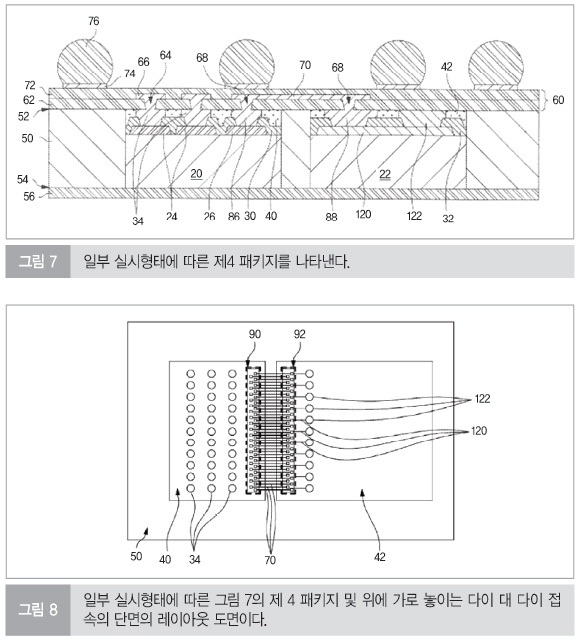

그림 7은 일부 실시형태에 따른 다른 패키지를 나타낸다. 그림 7의 패키지는 일반적으로 그림 3의 패키지와 유사하므로, 그림 7 및 그림 3에 도시된 공통적인 구성요소는 간결성을 위하여 여기서는 논의되지 않는다. 제2 집적 회로 다이(22) 상의 패드(28)는, 제2 집적 회로 다이(22) 상에 알루미늄 패드와 같은 패드(120)로 대체된다. 패드(120)의 각각은 가늘고 긴 패드일 수도 있고, 2개의 패드로서, 이러한 2개의 패드를 연결하는 라인을 가진 2개의 패드 등을 구비할 수도 있다. 패시베이션 필름(32)은 패드(120)의 일부 위에 존재한다. 개구는 패시베이션 필름(32)을 관통하여 패드(120)에 이어져 있다. 2개의 개구는 패시베이션 필름(32)을 관통하여 각각의 패드(120)에 이어져 있다. 도전성 필러(예컨대, 구리와 같은 금속을 포함함)와 같은 다이 커넥터(88) 및 프로브 다이 커넥터(122)는 패시베이션 필름(32)을 관통하는 개구 내에 존재하며, 패드(120)에 전기적으로 및 기계적으로 결합된다. 각 패드(120)에 대하여, 하나의 다이 커넥터(88)는 패드(120)에 대한 하나의 개구 내에 존재할 수도 있고, 하나의 프로브 다이 커넥터(122)는 패드(120)에 대한 다른 하나의 개구 내에 존재할 수도 있다. 감소된 개수의 프로브 다이 커넥터(122)는 명료화 및 단순화를 위하여 제2 집적 회로 다이(22) 상에 도시되며, 당업자는 더 많은 프로브 다이 커넥터가 존재할 수도 있음을 쉽게 이해한다. 또한, 프로브 다이 커넥터의 상대적인 크기 및/또는 피치는 다양한 개념을 더욱 명료하게 전달하기 위하여 예시에 있어서 과장될 수도 있다. 프로브 다이 커넥터(122)의 더욱 상세한 내용을 그림 8을 참조하여 설명한다.

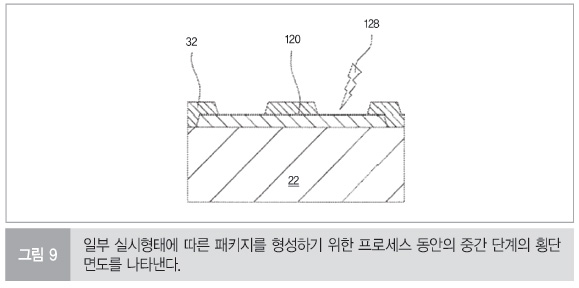

그림 8은 일부 실시형태에 따르면, 위에 가로 놓이는 다이 대 다이 접속 상태에서, 밀봉재(50)의 제1 표면(52), 유전체 재료(40 및 42)의 표면, 다이 커넥터(34, 86 및 88)의 표면, 프로브 다이 커넥터(122)의 표면의 레이아웃 도면이다. 그림 8의 레이아웃 도면은, 그림 4의 (b)에 도시된 부가적인 세부사항을 포함하여, 일반적으로 그림 4의 (a)의 레이아웃 도면과 동일하다. 프로브 다이 커넥터(102)는 일반적으로 제2 집적 회로 다이(22) 상의 영역(92)에 따라 그리고 이 영역(92)에 평행하게 배치된다. 임의의 개수의 프로브 다이 커넥터(122)가 사용될 수도 있으며, 프로브 다이 커넥터(122)는 임의의 크기를 가진 임의의 구성 내에 존재할 수도 있다. 라인과 같이, 영역(92) 내의 다이 커넥터(88) 및 프로브 다이 커넥터(122) 중 각각의 하나를 전기적으로 결합하는 패드(120)가 도시된다. 프로브 다이 커넥터(122) 및/또는 상기 프로브 다이 커넥터(122)가 접속되는 패드(120)의 하부 부분은 다이 검사를 돕기 위하여 사용될 수도 있다. 프로브 다이 커넥터(122) 및/또는 패드(120)의 하부 부분은 일반적으로 영역(92) 내의 다이 커넥터(88)보다 더 큰 크기 및 피치를 가질 수도 있다. 그러므로 프로브 다이 커넥터(122) 및/또는 패드(120)의 하부 부분을 프로빙하는 것은, 다이 커넥터(88) 및/또는 패드(28)를 프로빙하는 것보다 더 쉬울 수도 있다. 그림 7 및 그림 8은 그림 3, 그림 4에서 논의된 영역(90 및 92)의 콘택스트에서 논의되었지만, 당업자는 패드(120) 및 프로브 다이 커넥터(122)가 그림 1, 그림 2의 패키지에 통합될 수도 있고, 또한 더미 패드 및/또는 더미 다이 커넥터가 또한 어느 하나의 패키지에 통합될 수도 있음을 쉽게 이해할 것이다.

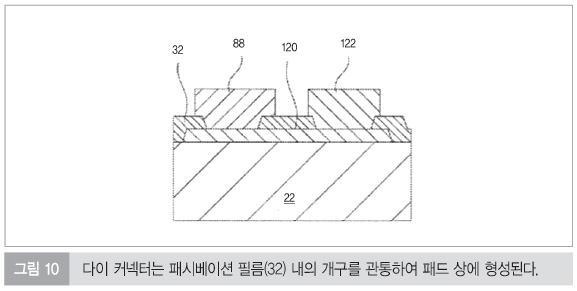

그림 9는 일부 실시형태에 따라 패키지를 형성하기 위한 프로세스 동안의 중간 단계의 횡단면도를 나타낸다. 그림 9는 제2 집적 회로 다이(22)의 프로세싱 동안의 횡단면도이며, 당업자는 제1 집적 회로 다이(20)가 유사한 프로세싱을 겪을 수도 있음을 쉽게 이해할 수 있다.

그림 9에서, 패드는 제2 집적 회로 다이(22) 상에 형성된다. 그림 9에서의 프로세싱 이전에, 제2 집적 회로 다이(22)는 다른 BEOL(Back-End-Of-the-Line) 프로세스에 의해 처리되었을 수도 있다. 예컨대, 여러 가지 금속화 층은, 제2 집적 회로 다이(22)의 반도체 기판 상에 형성되었을 수도 있고, 이는 집적 회로를 형성하기 위하여 반도체 기판에 및/또는 그 위에 형성된 여러 가지 디바이스를 서로 연결할 수도 있다. 패드는 상부 금속화 층 위에 가로 놓이는 유전체 층 상에 형성될 수도 있고, 상부 금속화 층 내의 금속화 패턴에 결합될 수도 있다. 그림 7 및 그림 8의 패드는 그림 9의 실시형태에 도시된다. 다른 실시형태에 있어서, 패드(28, 100 및/또는 122)는 다른 그림으로 형성될 수도 있다. 패드는, 화학적 기상 증착(chemical vapor deposition; CVD), 물리적 기상 증착(physical vapor deposition) 등과 같은 수용 가능한 증착 프로세스에 의해 기판 상에 알루미늄, 구리, 금속 합금 등의 금속과 같은 도전성 재료를 증착함으로써 형성될 수도 있다. 도전성 재료는 예컨대 수용 가능한 포토리소그래피 및 에칭 프로세스를 이용하여 패드에 패터닝될 수도 있다. 이후에, 패드(120) 및 기판 위에 패시베이션 필름(32)이 형성된다. 패시베이션 필름(32)은 CVD 등에 의해 증착된, 실리콘 니트라이드, 실리콘 옥사이드 등과 같은 유전체 층일 수도 있다. 패드(120)를 노출시키는 개구는, 예컨대 수용 가능한 포토리소그래피 및 에칭 프로세스를 이용하여 패시베이션 필름(32)을 관통하여 형성될 수도 있다.

그 후, 그림 9에 도시된 바와 같이, 제2 집적 회로 다이(22)는 칩 검사를 겪을 수도 있다. 검사는 프로브(128)를 제2 집적 회로 다이(22) 상의 하나 이상의 패드(120)에 적용하는 단계와, 제2 집적 회로 다이(22) 내의 여러 가지 구성요소들을 검사하기 위하여 프로브(128)로부터의 신호를 패드(120) 전반에 걸쳐서 적용하는 단계를 포함할 수도 있다. 도시된 바와 같이, 패드(120)가 사용되는 실시형태에 있어서, 프로브(128)는 프로브 다이 커넥터(122)의 위치에 대응하여 패시베이션 필름(32) 내의 개구를 통하여 패드(120)를 접촉시킬 수도 있다. 다른 실시 형태에 있어서, 프로브(128)는 다이 커넥터(38 또는 88)의 위치에 대응하는 패시베이션 필름(32) 내의 개구를 통하여 패드를 접촉시킬 수도 있다. 또 다른 실시형태에 있어서, 검사가 생략될 수도 있다.

그림 10에 있어서, 다이 커넥터는 패시베이션 필름(32) 내의 개구를 관통하여 패드 상에 형성된다. 다이 커넥터는, 그림 7 및 그림 8의 다이 커넥터(88) 및 프로브 다이 커넥터(122)가 그림 9의 실시형태에 도시되어 있지만, 다른 도면의 다이 커넥터(38, 88, 102 및/또는 122) 중 임의의 것일 수도 있다. 다이 커넥터(88 및 122)를 형성하기 위한 예로서, 시드 층(도시되지 않음)은 패시베이션 필름(32) 위에 그리고 패시베이션 필름(32)을 관통한 개구의 표면 내 및 그 표면을 따라 형성된다. 일부 실시형태에서, 시드 층은 금속 층이며, 이는 단일 층 또는 상이한 재료로 형성된 복수의 서브층을 구비하는 복합 층일 수도 있다. 일부 실시형태에 있어서, 시드 층은 티타늄 층 및 상기 티타늄 층 위의 구리 층을 포함한다. 시드 층은 예컨대 PVD 등을 이용하여 형성될 수도 있다. 그 후, 포토 레지스트는 시드 층 상에 형성되어 패터닝된다. 포토 레지스트는 스핀 코팅 등에 의해 형성될 수도 있고, 패터닝을 위하여 광에 노출될 수도 있다. 포토 레지스트의 패턴은 다이 커넥터(88 및 122)에 대응한다. 패터닝은 시드 층을 노출시키는 포토 레지스트를 통하여 개구를 형성한다. 도전성 재료는 포토 레지스트의 개구 내에 그리고 시드 층의 노출된 부분 상에 형성된다. 도전성 재료는, 전기 도금 또는 무전해 도금 등과 같은 도금에 의해 형성될 수도 있다. 도전성 재료는, 구리, 티타늄, 텅스텐, 알루미늄 등과 같은 금속을 포함할 수도 있다. 그 후, 포토 레지스트 및 도전성 재료가 형성되지 않는 시드 층의 일부가 제거된다. 포토 레지스트는 산소 플라즈마 등을 이용하는 것과 같은 수용 가능한 애싱 또는 스트리핑 프로세스에 의해 제거될 수도 있다. 일단 포토 레지스트가 제거되면, 습식 또는 건식 에칭과 같은 수용 가능한 에칭 프로세스를 이용함으로써 시드 층의 노출된 부분이 제거된다. 시드 층 및 도전성 재료의 나머지 부분은, 다이 커넥터(88 및 122)를 형성한다.

그림 11에 있어서, 유전체 재료(42)는 다이 커넥터(88 및 122) 상에 그리고 패시베이션 필름(32) 상에 형성된다.

유전체 재료(42)는 다이 커넥터(88 및 122)의 노출된 표면을 덮기에 충분한 두께를 가진다. 유전체 재료(42)는, 스핀 코팅, 라미네이팅 등과 같은 임의의 수용 가능한 증착 프로세스에 의해 형성되는 PBO, 폴리이미드, BCB 등 일 수도 있다. 당업자는 그림 11을 포함하여 그림 11까지의 프로세싱이 웨이퍼와 같은 단일 기판 상에 복수의 제2 집적 회로 다이(22) 상에 동시에 발생할 수도 있음을 이해할 수 있다. 유전체 재료(42)가 형성된 이후에, 제2 집적 회로 다이(22)는, 다이싱 또는 쏘잉에 의해 싱귤레이트될 수도 있다.

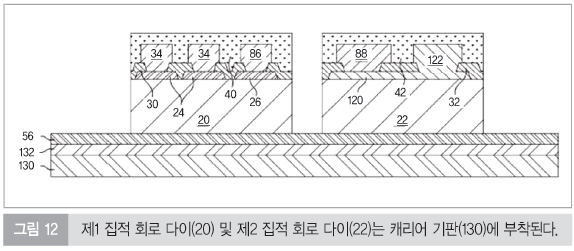

그림 12에서, 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)는 캐리어 기판(130)에 부착된다. 캐리어 기판(130)은, 유리 캐리어 기판, 세라믹 캐리어 기판 등일 수도 있다. 캐리어 기판(130)은 웨이퍼일 수도 있다. 릴리즈 층(132)은 캐리어 기판(130) 상에 존재하며, DAF(56)는 릴리즈 층(132) 상에 존재한다. 릴리즈 층(132)은 폴리머 기반 재료로 형성될 수도 있으며, 이는 후속 단계에서 형성되는 오버레이 구조물로부터 캐리어 기판(130)과 함께 제거될 수도 있다. 일부 실시형태에 있어서, 릴리즈 층(132)은 에폭시 기반 서멀-릴리즈 재료이며, 이는 KTHC(Light-to-Heat-Conversion) 릴리즈 코팅과 같이, 가열될 때 접착 특성을 잃어버린다. 다른 실시형태에서, 릴리즈 층(132)은 UV(ultra-violet) 접착제(glue)일 수도 있으며, 이는 UV 광에 노출될 때 접착 특성을 잃어버린다. 릴리즈 층(132)은 액체로서 제공되어 경화될 수도 있고, 캐리어 기판(130) 위에 라미네이트된 라미네이트 필름일 수 있고, 또는 다른 방식으로 처리될 수도 있다. DAF(56)는 캐리어 기판(130)에 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)를 부착하는 릴리즈 층 상에 인가되는 접착제일 수도 있다.

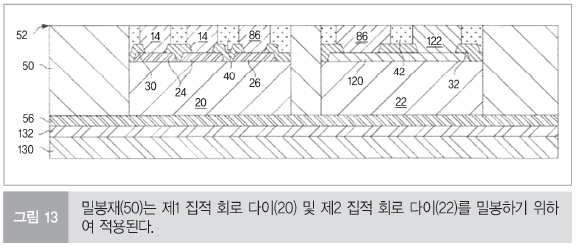

그림 13에 있어서, 밀봉재(50)는 제1 집적 회로 다이(20) 및 제2 집적 회로 다이(22)를 밀봉하기 위하여 적용된다. 밀봉재(50)는 몰딩 화합물, 에폭시 등일 수도 있고, 압축 몰딩, 트랜스퍼 몰딩 등에 의해 적용될 수도 있다. 경화 이후에, 밀봉재(50)는 다이 커넥터(34, 86, 88 및 122)를 노출시키기 위하여 그라인딩 프로세스를 겪을 수도 있다. 다이 커넥터(34, 86, 88 및 122), 유전체 재료(40 및 42) 및 밀봉재(50)의 상부 표면은 그라인딩 프로세스 이후에 동일 평면상에 존재한다. 일부 실시형태에 있어서, 그라인딩은 예컨대, 다이 커넥터(34, 86, 88 및 122)가 밀봉 프로세스 이후에 이미 노출되어 있으면, 생략될 수도 있다.

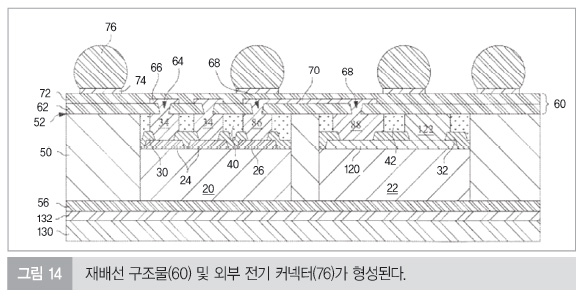

그림 14에 있어서, 재배선 구조물(60) 및 외부 전기 커넥터(76)가 형성된다. 재배선 구조물(60)은 임의의 개수의 유전체 층, 금속화 패턴 및 비아를 포함할 수도 있다. 예시된 바와 같이, 재배선 구조물(60)은 제1 유전체 층(62), 제2 유전체 층(72), 금속화 패턴(66) 및 다양한 비아를 포함한다.

제1 유전체 층(62)은 밀봉재(50), 유전체 재료(40 및 42) 및 다이 커넥터(34, 86, 88 및 122) 상에 형성된다. 일부 실시형태에서, 제1 유전체 층(62)은 폴리머로 형성되며, 이러한 폴리머는 PBO, 폴리이미드, BCB 등과 같은 광감지 재료일 수도 있고, 이는 리소그래피 마스크를 이용하여 쉽게 패터닝될 수도 있다. 다른 실시형태에서, 제1 유전체 층(62)은 실리콘 니트라이드와 같은 질화물; 실리콘 옥사이드, PSG, BSG, BPSG와 같은 산화물 등으로 형성된다. 제1 유전체 층(62)은 스핀 코팅, 라미네이션, CVD 등 또는 이들의 조합에 의해 형성될 수도 있다.

비아를 가진 금속화 패턴(66)은 제1 유전체 층(62) 상에 먼저 형성된다. 금속화 패턴(66)을 형성하기 위한 예로서, 시드 층(도시되지 않음)은 제1 유전체 층(62) 위에 형성된다. 일부 실시형태에서, 시드 층은 금속 층이며, 이는 단일 층 또는 상이한 재료로 형성된 복수의 서브층을 구비하는 복합 층일 수도 있다. 일부 실시형태에서, 시드 층은 티타늄 층 및 상기 티타늄 층 위의 구리 층을 포함한다. 시드 층은 예컨대 PVD 등을 이용하여 형성될 수도 있다. 그 후, 포토 레지스트가 시드 층 상에 형성되어 패터닝된다. 포토 레지스트는 스핀 코팅 등에 의해 형성될 수도 있고, 패터닝을 위하여 광에 노출될 수도 있다. 포토 레지스트의 패턴은 금속화 패턴(66) 및 비아에 대응한다. 패터닝은 시드 층을 노출시키는 포토 레지스트를 통하여 개구를 형성한다. 도전성 재료는 포토 레지스트의 개구 내에 그리고 시드 층의 노출된 부분 상에 형성된다. 도전성 재료는, 전기 도금 또는 무전해 도금 등과 같은 도금에 의해 형성될 수도 있다. 도전성 재료는, 구리, 티타늄, 텅스텐, 알루미늄 등과 같은 금속을 포함할 수도 있다. 그 후, 포토 레지스트 및 도전성 재료가 형성되지 않는 시드 층의 일부가 제거된다. 포토 레지스트는 산소 플라즈마 등을 이용하는 것과 같은 수용 가능한 애싱 또는 스트리핑 프로세스에 의해 제거될 수도 있다. 일단 포토 레지스트가 제거되면, 습식 또는 건식 에칭과 같은 수용 가능한 에칭 프로세스를 이용함으로써 시드 층의 노출된 부분이 제거된다. 시드 층의 나머지 부분 및 도전성 재료는, 제1 유전체 층(62) 전반에 걸쳐서 금속화 패턴(66) 및 비아를 형성한다. 비아는 금속화 패턴(66)을 다이 커넥터(34)에 직접 결합시키는 비아(64) 그리고 다이 커넥터(86 및 88)를 금속화 패턴(66)의 라인(70)에 직접 결합시키는 비아(68)를 포함한다.

제2 유전체 층(72)은 금속화 패턴(66) 및 제1 유전체 층(62) 상에 형성된다. 일부 실시형태에서, 제2 유전체 층(72)은 폴리머로 형성되며, 이러한 폴리머는 PBO, 폴리이미드, BCB 등과 같은 광감지 재료일 수도 있으며, 이는 포토리소그래피 마스크를 이용하여 쉽게 패터닝될 수도 있다. 다른 실시형태에서, 제2 유전체 층(72)은 실리콘 니트라이드와 같은 질화물; 실리콘 옥사이드, PSG, BSG, BPSG와 같은 산화물 등으로 형성된다. 제2 유전체 층(72)은 스핀 코팅, 라미네이션, CVD 등 또는 이들의 조합에 의해 형성될 수도 있다. 그 후, 제2 유전체 층(72)은 금속화 패턴(66)의 일부를 노출시키는 개구를 형성하기 위하여 패터닝된다. 패터닝은, 유전체 층이 광감지재료일 때 제2 유전체 층(72)을 광에 노출시키는 것 또는 예컨대 이방성 에칭을 이용하여 에칭시키는 것과 같은 수용 가능한 프로세스에 의한 것일 수도 있다.

하나 이상의 부가적인 금속화 패턴 및 유전체 층은, 금속화 패턴 및 유전체 층을 형성하기 위한 프로세스를 반복함으로써 재분배 구조물(60) 내에 형성될 수도 있다. 비아는 시드 층을 형성함으로써 금속화 패턴을 형성하는 동안에 형성될 수 있고 그리고 제2 유전체 층의 개구 내에 금속화 패턴의 도전성 재료가 형성될 수 있다. 그러므로 비아는 상호접속부일 수도 있고, 여러 가지 금속화 패턴을 전기적으로 결합할 수도 있다.

본드 패드(74)는 재분배 구조물(60)의 외부 표면 상에 형성된다. 예시된 실시형태에서, 본드 패드(74)는 제2 유전체 층(72) 내의 개구를 관통하는 비아(도시되지 않음)를 포함한다. 본드 패드(74)를 형성하기 위한 예로서, 시드 층(도시되지 않음)는 제2 유전체 층(72) 위에 형성된다. 일부 실시형태에서, 시드 층은 금속 층이며, 이는 단일 층 또는 상이한 재료로 형성된 복수의 서브층을 구비하는 복합 층일 수도 있다. 일부 실시형태에 있어서, 시드 층은 티타늄 층 및 상기 티타늄 층 위의 구리 층을 포함한다. 시드 층은 예컨대 PVD 등을 이용하여 형성될 수도 있다. 그 후, 포토 레지스트는 시드 층 상에 형성되어 패터닝된다. 포토 레지스트는 스핀 코팅 등에 의해 형성될 수도 있고, 패터닝을 위하여 광에 노출될 수도 있다. 포토 레지스트의 패턴은 본드 패드(74)에 대응한다. 패터닝은 시드 층을 노출시키는 포토 레지스트를 통하여 개구를 형성한다. 도전성 재료는 포토 레지스트의 개구 내에 그리고 시드 층의 노출된 부분 상에 형성된다. 도전성 재료는, 전기 도금 또는 무전해 도금 등과 같은 도금에 의해 형성될 수도 있다. 도전성 재료는, 구리, 티타늄, 텅스텐, 알루미늄 등과 같은 금속을 포함할 수도 있다. 그 후, 포토 레지스트 및 도전성 재료가 형성되지 않는 시드 층의 일부가 제거된다. 포토 레지스트는 산소 플라즈마 등을 이용하는 것과 같은 수용 가능한 애싱 또는 스트리핑 프로세스에 의해 제거될 수도 있다. 일단 포토 레지스트가 제거되면, 습식 또는 건식 에칭과 같은 수용 가능한 에칭 프로세스를 이용함으로써 시드 층의 노출된 부분이 제거된다. 시드 층 및 도전성 재료의 나머지 부분은, 본드 패드(74)를 형성하며, 이는 라인 및 비아를 포함할 수 있으며, 여기서 라인 및 비아는 본드 패드(74)를 금속화 패턴(66)에 전기적으로 결합한다. 비아는 제2 유전체 층(72) 내의 개구에 형성된다.

외부 전기 커넥터(76)은 패드(116) 상에 형성된다. 외부 전기 커넥터(76)는 땜납과 같은 저온 리플로우 가능한 재료를 포함할 수도 있고, 이는 납이 없는 것 또는 납을 포함하는 것일 수 있다. 외부 전기 커넥터(76)는 적절한 볼 드롭 프로세스를 이용함으로써 형성될 수도 있다. 패드(116)가 생략되는 다른 실시형태에 있어서, 외부 전기 커넥터는 제2 유전체 층(72) 내의 여러 가지 개구를 통하여 금속화 패턴(66) 상에 직접 형성된다.

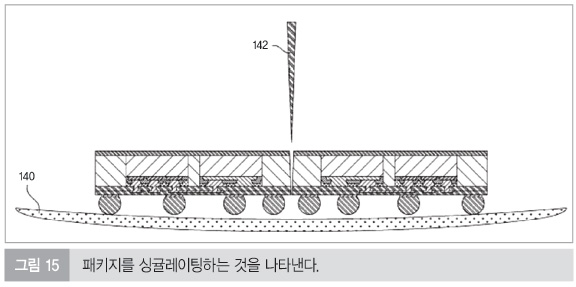

당업자는 그림 14를 통한 프로세싱이 전술한 바와 같이 웨이퍼인 캐리어 기판(130) 상에 수행될 수 있으므로, 복수의 패키지 구조물은 단일 캐리어 기판(130) 상에 형성될 수도 있음을 쉽게 알 수 있다. 그림 15는 패키지를 싱귤레이팅하는 것을 나타낸다. 싱귤레이션 이전에, 캐리어 기판(130)은 패키지 구조물로부터 접합 해제(또는 분리)된다. 일부 실시형태에 따르면, 접합 해제는 릴리즈 층(132)이 광의 열을 받아 분해되고, 캐리어 기판(130)이 제거될 수 있도록 릴리즈 층(132) 상에 레이저 광 또는 UV 광과 같은 광을 투사하는 것을 포함한다. 클리닝 및/또는 그라인딩 프로세스는 릴리즈 층(132) 및/또는 DAF(56)의 잔여 부분을 제거하기 위하여 수행될 수도 있다. 그 후, 패키지 구조물은 플립 오버되고, 테이프(140) 상에 배치되다. 패키지는 예컨대 톱(142)을 사용하여 패키지 사이를 쏘잉함으로써 싱귤레이트된다.