기판 지지체 및 이송 디바이스로 구성

3D 칩 적층 기술 향상 기대

기판 상에 칩을 적층하기 위한 칩 적층 장치 기술이다. 칩 적층 장치는 기판을 반송하도록 구성된 기판 지지체 및 칩을 기판에 배치하도록 구성된 이송 디바이스를 포함한다. 이송 디바이스는 본드 헤드를 포함하고, 본드 헤드는 본드 베이스 및 본드 베이스 상에 배치되고 그 위에 칩이 부착될 수 있도록 구성된 부착 엘리먼트를 포함한다. 본드 베이스에 대하여 부착 엘리먼트의 중심 영역은 부착 엘리먼트의 가장자리 영역보다 높다.

발명의 설명

배경 기술

반도체 디바이스는 개인용 컴퓨터, 셀 폰, 디지털 카메라 및 다른 전자 기기와 같은 다양한 전자 응용물에서 이용된다. 반도체 디바이스는 일반적으로 웨이퍼 상부에 절연층들 또는 유전체층들, 도전층들 및 반도체 재료 층들을 순차적으로 성막하고, 리소그래피를 이용하여 다양한 재료층들을 패터닝하여 웨이퍼 상에 회로 컴포넌트들 및 엘리먼트들을 형성함으로써 제조된다. 많은 집적 회로들은 일반적으로 단일 웨이퍼 상에 제조되고, 웨이퍼 상의 개별의 다이들은 스크라이브 라인을 따라 집적 회로들 사이를 쏘잉함으로써 싱귤레이팅된다. 개별의 다이는 일반적으로 다중-칩 모듈에서, 예를 들어, 또는 다른 유형의 패키지에서 개별적으로 패키징된다.

최근, 3D 칩 적층 기술이 개발되어 왔다. 3D 칩 적층 기술에서, 3D 적층 칩은 다수의 칩들을 적층함으로써 형성된다. 3D 칩 적층 기술을 위한 기존의 디바이스 및 방법들은 그들의 의도된 목적에 대해서는 대체적으로 충분하였지만, 모든 측면에서 완전히 만족스럽지는 않았다. 따라서 3D 칩 적층 기술을 향상시키기 위한 해결책을 제공하는 것이 바람직할 것이다.

발명을 실시하기 위한 구체적인 내용

다음의 발명개시는 제공되는 본 발명내용의 상이한 피처들을 구현하기 위한 많은 상이한 실시예들 또는 예시들을 제공한다. 본 발명개시를 간략화하기 위해서 컴포넌트 및 배치의 구체적인 예들이 이하에 설명된다. 물론, 이들은 단지 예시를 위한 것이며 한정을 의도하는 것은 아니다. 예를 들어, 다음의 설명에서 제 2 피처 상부 또는 위에 제 1 피처를 형성하는 것은 제 1 피처와 제 2 피처가 직접 접촉하여 형성된 실시예를 포함할 수 있고, 또한 제 1 피처와 제 2 피처가 직접 접촉하지 않도록 제 1 피처와 제 2 피처 사이에 추가의 피처가 형성될 수 있는 실시예도 포함할 수 있다. 또한, 본 발명개시는 다양한 예시들에서 참조 부호들 및/또는 문자들을 반복할 수 있다. 이러한 반복은 간략화 및 명료화를 위한 것이고, 그 자체가 개시된 다양한 실시예들 및/또는 구성들 사이의 관계를 설명하는 것은 아니다.

또한, 도면들에서 도시된 하나의 엘리먼트 또는 피처에 대한 다른 엘리먼트(들) 또는 피처(들)의 관계를 설명하기 위해서 ‘아래’, ‘밑’, ‘하부’, ‘위’, ‘상부’ 등과 같은 공간 상대적 용어들이 설명의 용이성을 위해 여기서 이용될 수 있다. 공간 상대적인 용어는 도면에서 예시된 배향에 더하여 이용 또는 동작에서의 디바이스의 상이한 배향을 포함하도록 의도된다. 장치는 이와 다르게 배향될 수 있고(90° 회전되거나 또는 다른 배향에 있음), 여기서 이용되는 공간 상대적 기술어들이 그에 따라 해석될 수 있다.

본 실시예들의 몇몇의 변형들이 설명된다. 다양한 도면들과 예시적인 실시예들 전반에 걸쳐, 동일한 엘리먼트들을 지정하기 위해 동일한 참조 번호들이 이용된다. 방법 이전, 동안, 그리고 이후에 추가의 동작들이 제공될 수 있고, 설명된 동작들의 일부는 방법의 다른 실시예를 위해 대체 또는 제거될 수 있다는 것을 이해하여야 한다.

칩 적층 장치 및 적층 방법이 제공된다. 칩 적층 장치는 3D 적층 칩을 형성하기 위해 기판 상에 칩을 적층하도록 구성된다. 칩을 기판 상에 적층할 때 칩과 기판 사이에 기체 기포 및 오염물이 최소화된다. 또한, 기판 상에 적층된 칩의 정렬(alignment)향상된다.

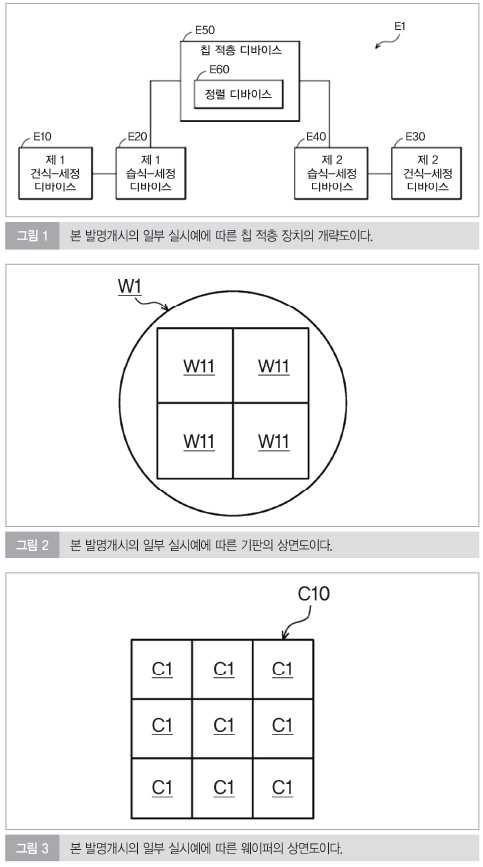

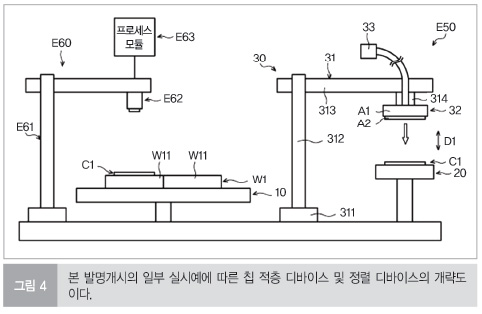

그림 1은 본 발명개시의 일부 실시예에 따른 칩 적층 장치(E1)의 개략도이다. 그림 2는 본 발명개시의 일부 실시예에 따른 기판(W1)의 상면도이다. 그림 3은 본 발명개시의 일부 실시예에 따른 웨이퍼(W2)의 상면도이다. 칩 적층 장치(E1)는 제 1 건식-세정(dry-cleaning) 디바이스(E10), 제 1 습식-세정(wet-cleaning) 디바이스(E20), 제 2건식-세정 디바이스(E30), 제 2 습식-세정 디바이스(E40), 칩 적층 디바이스(E50) 및 정렬 디바이스(E60)를 포함한다.

제 1 건식-세정 디바이스(E10)는, 그림 2에 나타낸 바와 같이, 기체 또는 플라즈마를 이용하여 기판(W1)을 세정하도록 구성된다. 일부 실시예에 있어서, 기체는 N2와 같은 불활성(inert) 기체이다. 일부 실시예에 있어서, 기판(W1)은 웨이퍼이다. 기판(W1)은 다수의 바텀 칩(bottom chip)(W11)을 포함한다. 일부 실시예에 있어서, 기판(W1)은 바텀 칩이다.

일부 실시예에 있어서, 제 1 건식-세정 디바이스(E10)는 플라즈마 디바이스를 포함한다. 플라즈마 디바이스는 기판(W1) 상에 플라즈마 공정을 수행하도록 구성된다. 예를 들어, 제 1 건식-세정 디바이스(E10)는 기판(W1)의 표면 상의 오염물을 세정하기 위해 기판(W1)의 표면에 분사(dispense)하는 플라즈마를 생성한다. 일부 실시예에 있어서, 오염물은 입자(예를 들어, 먼지), 유지 잔존물, 또는 무기 잔존물(예를 들어, 금속 이온)이다. 일부 실시예에 있어서, 오염물은 약 0.1㎛ 내지 약 50㎛ 범위 내의 직경을 가진다. 일부 실시예에 있어서, 제 1 건식-세정 디바이스(E10)는 저기압 하에, 또는 대기압 상태에서 플라즈마 공정을 수행한다.

기판(W1)이 제 1 건식-세정 디바이스(E10)에 의해 세정된 후에, 기판(W1)은 제 1 습식-세정 디바이스(E20)로 이송된다. 제 1 습식-세정 디바이스(E20)는 액체를 사용하여 기판(W1)을 세정하도록 구성된다. 일부 실시예에 있어서, 제 1 습식-세정 디바이스(E20)는 기판(W1)의 표면 상의 오염물을 세정하기 위해 기판(W1)의 표면에 액체를 분사한다. 일부 실시예에 있어서, 액체는 탈이온수(deionized water)와 같은 물이다. 일부 실시예에 있어서, 액체는 산성액 또는 알칼리액이다.

일부 실시예에 있어서, 기판(W1)은 먼저 제 1 습식-세정 디바이스(E20)에 의해 세정되고, 이후 제 1 건식-세정 디바이스(E10)에 의해 세정된다. 일부 실시예에 있어서, 제 1 건식-세정 디바이스(E10)는 기판(W1) 상에 부착된 오염물을 또는 큰 사이즈를 갖는 오염물을 세정하도록 구성된다. 제 1 습식-세정 디바이스(E20)는 기판(W1) 상에 떨어진, 먼지와 같은, 오염물을 세정하도록 구성된다. 그러므로 거의 모든 오염물이 제 1 건식-세정 디바이스(E10) 및 제 1 습식-세정 디바이스(E20)에 의해 기판(W1)으로부터 제거될 수 있다.

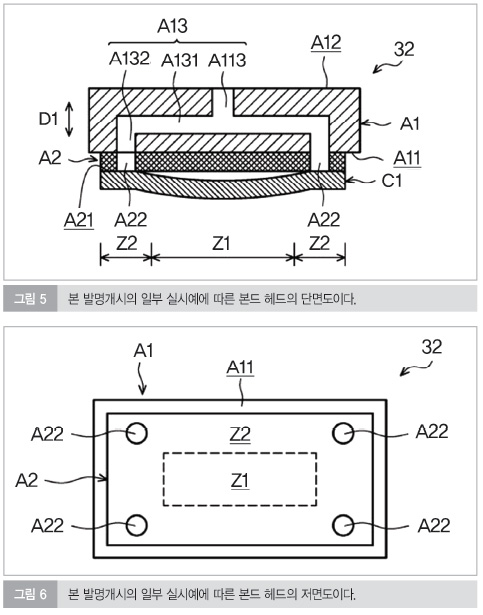

제 2 건식-세정 디바이스(E30)는, 그림 3에 나타낸 바와 같이, 기체 또는 플라즈마를 이용하여 칩 어레이(C10)를 세정하도록 구성된다. 칩 어레이(C10)는 어레이 내에 배열된 다수의 칩(C1)을 포함한다. 일부 실시예에 있어서, 칩(C1)은 박막에 부착된다.

일부 실시예에 있어서, 제 2 건식-세정 디바이스(E30)는 플라즈마 디바이스일 수 있다. 제 2 건식-세정 디바이스(E30)는 칩 어레이(10)의 칩(C1) 상에 플라즈마 공정을 수행하도록 구성된다. 제 2 건식-세정 디바이스(E30)는 칩(C1)의 표면 상의 오염물을 세정하기 위해 칩(C1)의 표면에 분사하는 플라즈마를 생성한다.

칩(C1)이 제 2 건식-세정 디바이스(E30)에 의해 세정된 후에, 칩(C1)은 제 2 습식-세정 디바이스(E40)로 이송된다. 제 2 습식-세정 디바이스(E40)는 액체를 이용하여 칩(C1)을 세정하도 구성된다. 일부 실시예에 있어서, 제 2 습식-세정 디바이스(E40)는 칩(C1)의 표면 상의 오염물을 세정하기 위해 칩(C1)에 액체를 분사한다. 일부 실시예에 있어서, 칩(C1)은 먼저 제 2 습식-세정 디바이스(E40)에 의해 세정되고, 그 후에 제 2 건식-세정 디바이스(E30)에 의해 세정된다. 일부 실시예에 있어서, 제 2 건식-세정 디바이스(E30)는 칩(C1) 상에 부착된 오염물 또는 큰 사이즈를 갖는 오염물을 세정하도록 구성된다. 제 2 습식-세정 디바이스(E40)는 칩(C1) 상에 떨어진, 먼지와 같은, 오염물을 세정하도록 구성된다. 그러므로 거의 모든 오염물이 제 2 건식-세정 디바이스(E30) 및 제 2 습식-세정 디바이스(E40)에 의해 기판(W1)으로부터 제거될 수 있다.

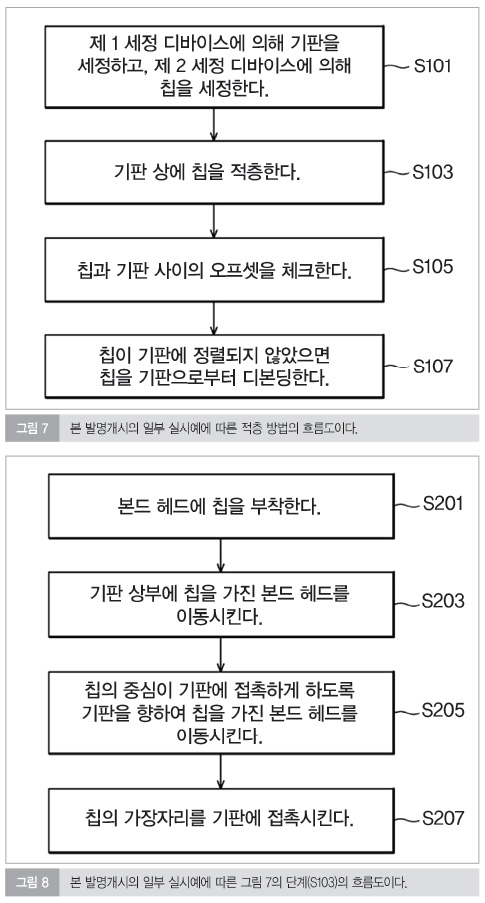

그림 4는 본 발명개시의 일부 실시예에 따른 칩 적층 디바이스(E50) 및 정렬 디바이스(E60)의 개략도이다. 칩 적층 디바이스(E50)는 기판(W1)에 칩(C1)을 적층하도록 구성된다. 일부 실시예에 있어서, 바텀 칩(W11)은 중앙 처리 장치(central processing unit; CPU)이고, 칩(C1)은 디스플레이 장치이다. 칩(C1)은 칩(C1)이 바텀 칩(W11) 상에 적층될 때 바텀 칩(W11)에 전기적으로 접속된다. 일부 실시예에 있어서, 다수의 칩(C1)이 하나의 바텀 칩(W11)에 적층된다.

칩 적층 디바이스(E50)는 기판 지지체(10), 칩 지지체(20) 및 이송 디바이스(30)를 포함한다. 기판 지지체(10)는 기판(W1)을 지지하도록 구성된다. 일부 실시예에 있어서, 기판 지지체(10)는 웨이퍼 척과 같은 척이다. 기판(W1)은 제 1 습식-세정 디바이스(E20)에 의해 세정된 후에, 기판(W1)은 기판 지지체(10) 상으로 이송된다.

칩 지지체(20)는 칩(C1)을 지지하도록 구성된다. 칩(C1)이 제 2 습식-세정 디바이스(E40)에 의해 세정된 후에, 칩(C1) 중 하나는 칩 지지체(20) 상으로 이송된다. 일부 실시예에 있어서, 칩 지지체(20)는 칩 이송 디바이스이다. 칩 이송 디바이스는 칩(C1)을 전송하고 칩(C1)을 플립(flip)하도록 구성된다. 일부 실시예에 있어서, 칩 이송 디바이스는 칩(C1)을 회전시키도록 구성된다.

이송 디바이스(30)는 칩(C1)을 기판(W1) 상으로 배치하도록 구성된다. 이송 디바이스(30)는 이송 메커니즘(31), 본드 헤드(32) 및 진공 펌프(33)를 포함한다. 이송 메커니즘(31)은 본드 헤드(32)를 이동시키도록 구성된다. 예를 들어, 이송 메커니즘(31)은 칩(C1)을 향하여 본드 헤드(32)를 이동시키거나, 또는 기판(W1)을 향하여 칩(C1)을 구비한 본드 헤드(32)를 이동시키도록 구성된다.

일부 실시예에 있어서, 이송 메커니즘(31)은 트랙(311), 스탠드(312), 아암(313) 및 유지 엘리먼트(314)를 포함한다. 스탠드(312)는 트랙(311)을 따라 이동될 수 있다. 일부 실시예에 있어서, 아암(313)은 스탠드(312)로부터 연장되어 스탠드(312)에 실직적으로 직각을 이룬다. 아암(313)은 스탠드(312) 상에 이동가능하게 그리고 회전 가능하게 배치된다. 예를 들어, 아암(313)은 방향(D1)을 따라 이동될 수 있다. 예를 들어, 아암(313)은 그 자체가 스탠드(312)를 따라 이동할 수 있고, 스탠드(312) 주위를 회전할 수 있다.

유지 엘리먼트(314)는 본드 헤드(32)를 유지하도록 구성된 아암(313)의 단부에 배치된다. 일부 실시예에 있어서, 본드 헤드(32)는 이송 메커니즘(31)의 유지 엘리먼트(314) 상에 착탈가능하게 배치된다. 본드 헤드(32)는 칩(C1)을 유지하도록 구성된다. 본드 헤드(32)는 다양한 사이즈를 칩들을 만족시키기 위해 대체 가능하다.

진공 펌프(33)는 본드 헤드(32)와 커플링되어 본드 헤드(32)를 통하여 공기를 빨아들인다. 그에 따라, 본드 헤드(32)는 칩(C1)이 본드 헤드(32)에 부착될 때 진공 펌프(33)에 의해 칩(C1) 상에 흡입력을 발생시킬 수 있다.

그림 5는 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 단면도이다. 그림 6은 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 저면도이다.

본드 헤드(32)는 본드 베이스(A1) 및 부착 엘리먼트(A2)를 포함한다. 본드 베이스(A1)는 도 3에 나타낸 바와 같이 이송 메커니즘(31)의 유지 엘리먼트(314) 상에 배치된다. 일부 실시예에 있어서, 본드 베이스(A1)는 플레이트 구조물이다. 본드 베이스(A1)는 스테인리스 스틸과 같은 금속으로 이루어진다. 본드 베이스(A1)는 방향(D1)에 실질적으로 직각을 이루는 수평면으로 연장된다.

본드 베이스(A1)는 저면(A11), 상면(A12) 및 채널(A13)을 포함한다. 저면(A11)은 상면(A12)에 대향한다. 채널(A13)은 본드 베이스(A1) 내에 형성되고, 저면(A11) 및 상면(A12)에 접속된다. 채널(A13)은 상면(A12)을 통하여 진공 펌프(33)와 커플링된다.

일부 실시예에 있어서, 채널(A13)은 메인 채널(A131), 다수의 저부 개구부(A132) 및 상부 개구부(A133)를 포함한다. 메인 채널(A131)은 본드 베이스(A1) 내에 내장된다. 저부 개구부(A132)는 저면(A11)의 가장자리 영역에 위치되고, 메인 채널(A131)에 접속된다. 일부 실시예에 있어서, 저부 개구부(A132)는 저면(A11)의 코너에 위치된다. 상부 개구부(A133)는 상면(A12)의 코너 영역에 위치되고, 메인 채널(A131)에 접속된다. 상부 개구부(A133)는 진공 펌프(33)와 커플링된다.

부착 엘리먼트(A2)는 본드 베이스(A1)의 저면(A11) 상에 배치된다. 부착 엘리먼트(A2)는 칩(C1)이 부착 엘리먼트(A2) 상에 부착될 수 있도록 구성된다. 일부 실시예에 있어서, 부착 엘리먼트(A2)는 플레이트 구조물이다. 부착 엘리먼트(A2)는 본드 베이스(A1)에 평행한다. 일부 실시예에 있어서, 부착 엘리먼트(A2)는 본드 베이스(A1)의 저면(A11)에 고정된다. 일부 실시예에 있어서, 부착 엘리먼트(A2)는 플라스틱과 같은 플렉서블 재료로 제조된다. 일부 실시예에 있어서, 플렉서블 재료는 열경화성 플라스틱 또는 열가소성이다.

부착 엘리먼트(A2)는 부착 엘리먼트(A2)를 통과하여 채널(A13)의 저부 개구부(A132)로 접속되는 다수의 진공 홀(A22)을 포함한다. 다르게 말하면, 진공 펌프(33)는 채널(A13)을 통하여 진공 홀(A22)과 커플링된다. 그러므로 부착 엘리먼트(A2)는 진공 홀(A22)을 통하여 공기를 빨아들이는 진공 펌프(33)에 의해 칩(C1)을 끌어당기도록 흡입력을 발생시킬 수 있다. 본드 헤드(32)는 진공 홀(A22)을 총하여 흡입력을 이용하여 칩(C1)을 끌어당긴다.

일부 실시예에 있어서, 진공 홀(A22)은 방향(D1)을 따라 연장된다. 진공 홀(A22)은 부착 엘리먼트(A2)의 가장자리 영역(Z2)에 위치된다. 가장자리 영역(Z2)은 중심 영역(Z1) 둘레에 있다. 예를 들어, 가장자리 영역(Z2)은 중심 영역(Z1)의 대향하는 두 측면에 위치된다. 일부 실시예에 있어서, 진공 홀(A22)은 부착 엘리먼트(A2)의 측벽 둘레에 위치된다. 일부 실시예에 있어서, 진공 홀(A22)은 그림 5에 나타낸 바와 같이 부착 엘리먼트(A2)의 코너에 위치된다.

일부 실시예에 있어서, 부착 엘리먼트(A2)는, 평편한 표면이고, 칩(C1)을 부착하도록 구성된, 부착면(A21)을 가진다. 진공 펌프(33)가 인에이블되면, 진공 홀(A22)은 진공 펌프(33)에 의해 진공 상태가 된다. 그림 5에 나타낸 바와 같이, 흡입력은 부착 엘리먼트(A2)의 가장자리 영역(Z2)에서 진공 홀(A22)을 통하여 발생되어, 칩(C1)의 가장자리를 끌어당긴다. 본드 헤드(32)는 중심 영역(Z1)보다 가장자리 영역(Z2)에서 더 큰 흡입력을 가진다.

일부 실시예에 있어서, 칩(C1)은 본드 헤드(32) 상에 부착될 때, 플렉시블 막 형상의 구조물이다. 일부 실시예에 있어서, 칩(C1)은 예를 들어, 약 10㎛ 내지 300㎛의 범위 내의 두께를 가진다. 그러므로 칩(C1)의 중심은, 칩(C1)의 가장자리가 부착면(A21)의 가장자리 영역(Z2)에 부착될 때, 그림 5에 나타낸 바와 같이, 중력에 의해 하향하여 휘어진다. 다르게 말하면, 칩(C1)의 중심은 부착면(A21)의 중심 영역(Z1)으로부터 분리된다.

그림 4에 나타낸 바와 같이, 정렬 디바이스(E60)는 칩(C1)과 기판(W1) 사이의 오프셋을 체크하도록 구성된다. 정렬 디바이스(E60)는 이송 디바이스(E61), 이미지 센서(E62) 및 프로세스 모듈(E63)을 포함한다. 이송 디바이스(E61)는 이미지 센서(E62)를 이동시키도록 구성된다. 이미지 센서(E62)는 이송 디바이스(E61) 상에 배치된다.

이미지 센서(E62)는 칩(C1)이 기판(W1) 상에 적층될 때, 칩(C1) 및 기판(W1)의 이미지를 캡쳐하도록 구성된다. 이미지 센서(E62)는 또한 그 이미지에 따라 이미지 신호를 발생한다. 프로세스 모듈(E63)은 이미지 센서(E62)와 커플링된다. 프로세스 모듈(E63)은 이미지 신호를 수신하고, 이미지 신호를 분석하도록 구성된다. 프로세스 모듈(E63)은 또한 이미지 신호 및 칩(C1)과 기판(W1) 사이의 오프셋에 응답하여 보정 신호를 발생하도록 구성된다. 그 후, 이송 디바이스(30)는 보정 신호에 따라 기판(W1)에 후속 칩을 이송한다.

그림 7은 본 발명개시의 일부 실시예에 따른 적층 방법의 흐름도이다. 그림 8은 본 발명개시의 일부 실시예에 따른 그림 7의 단계(S103)의 흐름도이다.

단계(S101)에서, 기판(W1)은 제 1 세정 디바이스에 의해 세정된다. 일부 실시예에 있어서, 제 1 세정 디바이스는 제 1 건식-세정 디바이스(E10) 및 제 1 습식-세정 디바이스(E20)를 포함한다. 기판(W1)은 제 1 건식-세정 디바이스(E10)에 의해 세정된다. 그 후, 기판(W1)은 제 1 습식-세정 디바이스(E20)에 의해 세정된다. 또한, 칩(C1)은 제 2 세정 디바이스에 의해 세정된다. 일부 실시예에 있어서, 제 2 세정 디바이스는 제 2 건식-세정 디바이스(E30) 및 제 2 습식-세정 디바이스(E40)를 포함한다. 칩(C1)은 제 2 건식-세정 디바이스(E30)에 의해 세정된다. 그 후, 칩(C1)은 제 2 습식-세정 디바이스(E40)에 의해 세정된다.

세정 디바이스(E10~E40)에 의해, 칩(C1)은, 칩(C1)이 기판(W1)에 부착되기 전에, 더 세정 된다. 칩(C1) 및 기판(W1)은, 칩(C1)이 기판(W1) 상에 적층되기 전에, 세정된다. 그러므로 칩(C1)과 기판(W1) 사이의 오염물은 감소된다. 기판(W1)을 가진 칩(C1)의 제품의 수율이 증가된다.

단계(S103)에서, 칩(C1) 중 하나가 기판(W1) 상에 적층된다. 일부 실시예에 있어서, 칩(C1)은, 그림 8의 단계들에 따라, 기판(W1) 상에 적층된다. 그림 8에 나타낸 바와 같이, 단계(S201)에서, 칩(C1)은 칩 지지체(20) 상에 배치된다. 이송 메커니즘(31)은, 그림 4에 나타낸 바와 같이, 칩(C1)에 접촉하도록 본드 헤드(32)를 하향하여 이동시킨다. 진공 펌프(33)가 인에이블되면, 부착 엘리먼트(A2)는 칩(C1) 상에 흡입력을 발생한다. 그에 따라, 칩(C1)은 본드 헤드(32)의 부착면(A21)을 끌어당긴다.

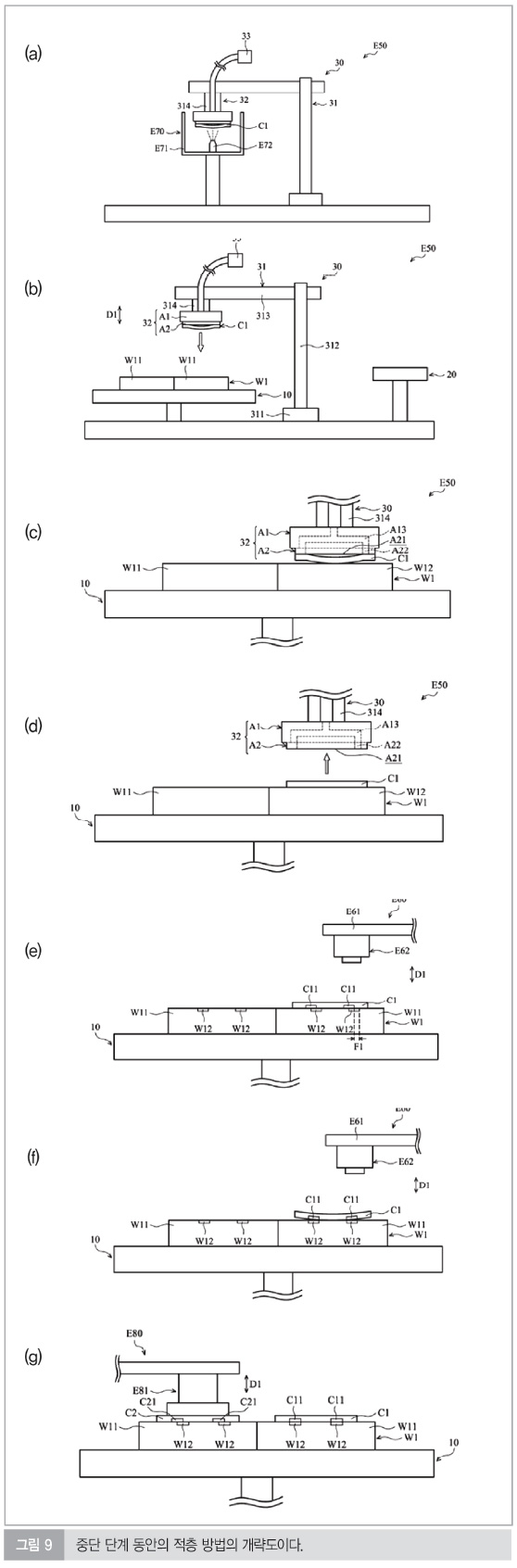

그림 9는 중단 단계 동안의 적층 방법의 개략도이다. 일부 실시예에 있어서, 칩 적층 디바이스(E50)는 그림 9의 (a)에 나타낸 바와 같이 칩 세정 디바이스(E70)를 더 포함한다. 칩 세정 디바이스(E70)는 칩(C1)이 본드 헤드(32)에 부착될 때 칩(C1)을 세정하도록 구성된다. 칩 세정 디바이스(E70)는 커버(E71) 및 노즐(E72)을 포함한다. 노즐(E72)은 커버(E71) 내에 배치된다. 노즐(E72)은 칩(C1) 상으로 액체 또는 기체를 분사하도록 구성된다. 일부 실시예에 있어서, 액체는 물 또는 탈이온수이다. 일부 실시예에 있어서, 액체는 산성액 또는 알칼리액이다. 일부 실시예에 있어서, 기체는 N2와 같은 불활성 기체이다. 커버(E71)는 다른 디바이스 상에 액체가 분사되는 것을 방지하도록 구성된다.

이송 메커니즘(31)은 노즐(E72) 상부로 칩(C1)을 가진 본드 헤드(32)를 이동시킨다. 그 후, 노즐(E72)은 칩(C1)의 저면에 액체 또는 기체를 분사한다. 칩 세정 디바이스(E70)에 의해, 칩(C1)은, 칩(C1)이 기판(W1)에 부착되기 전에 더 세정된다.

단계(S203)에서, 이송 메커니즘(31)은 그림 9의 (b)에 나타낸 바와 같이 기판(W1) 상부로 칩(C1)을 가진 본드 헤드(32)를 이동시킨다.

단계(S205)에서, 부착 공정이 기판(W1) 상에 개시된다. 이송 메커니즘(31)은 칩(C1)의 중심이 기판(W1)에 접촉하게 하도록 방향(D1)을 따라 기판(W1)을 향하여 칩(C1)을 가진 본드 헤드(32)를 이동시킨다. 그림 9의 (c)에 나타낸 바와 같이, 일부 실시예에 있어서, 칩(C1)의 가장자리는, 칩(C1)의 중심이 기판(W11)의 바텀 칩(W11) 중 하나에 접촉하기 시작할 때, 기판의 바텀 칩(W11)으로부터 분리된다.

단계(S207)에서, 흡입력은 진공 펌프(33)의 제어를 통하여 점차적으로 감소된다. 일부 실시예에 있어서, 진공펌프(33)는 칩(C1)의 중심이 기판(W1)에 접촉할 때 디스에이블된다. 그 후, 칩(C1)의 가장자리는, 흡입력이 감소되거나 소실되기 때문에 부착 엘리먼트(A2)로부터 분리된다. 칩(C1)은 그림 9의 (d)에 나타낸 바와 같이 칩(C1)의 중심으로부터 가장자리까지 점차적으로 기판(W1)에 접촉한다. 다르게 말하면, 칩(C1)의 중심은, 부착 공정 동안에 칩(C1)이 부착면(A21)에 부착될 때, 칩(C1)의 가장자리보다 이전에 기판(W1)에 접촉한다.

칩(C1)은 칩(C1)의 중심으로부터 가장자리까지 점차적으로 기판(W1)에 접촉하기 때문에, 칩(C1)이 기판(W1)에 부착된 후에, 칩(C1)과 기판(W1) 사이에 기체 기포가 형성되지 않는다. 그러므로 칩(C1)과 기판(W1) 사이의 전기적 접속이 기체 기포에 의해 방해되지 않는다. 기판(W1)을 가진 칩(C1)의 제품의 수율이 증가된다.

단계(S105)에서, 정렬 디바이스(E60)는 칩(C1)과 기판(W1) 사이의 오프셋을 체크한다. 일부 실시예에 있어서, 그림 9의 (e)에 나타낸 바와 같이, 칩(C1)은 마크(C11)를 더 포함하고, 기판(W1)은 마크(W12)를 더 포함한다. 이미지 센서(E62)는 기판(W1) 상에 적층된 마크(W12) 및 마크(C11)의 이미지를 캡쳐한다. 그 후, 이미지 센서(E62)는 프로세스 모듈(E63)에 이미지 신호를 송신한다.

프로세스 모듈(E63)은 이미지 신호를 분석하고, 마크(C11)와 마크(W12) 사이의 오프셋(F1)에 따라 보정 신호를 발생한다. 후속 칩이 기판(W1) 상에 적층될 때, 기판(W1)에 대한 후속 칩의 위치는 보정 신호 및 오프셋(F1)에 따라 수정된다. 그러므로 후속 칩의 마크는 기판(W1)의 마크(W12)와 정렬된다. 후속 칩은 기판(W1) 상으로 정확하게 적층될 수 있다.

그림 9의 (f)에 나타낸 바와 같이, 칩(C1)은, 칩(C1)이 기판(W1) 상에 적층될 때 변형(deform)될 수 있다. 일부 실시예에 있어서, 칩(C1)의 가장자리가 변형되기 때문에 마크(C11)의 형상이 변형된다. 프로세스 모듈(E63)은 또한 이미지 신호를 분석하고, 마크(C11)의 형상의 변형에 응답하여 보정 신호를 발생한다. 마크(C11)의 형상이 변형되면, 프로세스 모듈(E63)은 후속 칩의 가장자리 상의 압력을 증가시킨다. 그러므로 후속 칩의 가장자리는 기판(W1)에 완전히 접촉할 수 있다.

단계(S107)에서, 디본딩(debonding) 디바이스(E80)는, 칩(C1)이 기판(W1)에 바르게 정렬되지 않거나 완전히 접촉하지 않을 때, 칩(C1)을 기판(W1)으로부터 분리시킨다. 그림 9의 (g)에 나타낸 바와 같이, 칩(C2)의 마크(C21)는 기판(W1)의 마크(C12)와 바르게 정렬되지 않는다. 디본딩 디바이스(E80)는 디본딩 헤드(E81)를 포함한다. 디본딩 헤드(E81)는 칩(C2) 상에 흡입력을 발생시키고, 칩(C2)이 배치되었던 위치에 다른 칩이 적층될 수 있도록, 기판(W1)으로부터 칩(C2)을 분리시킨다.

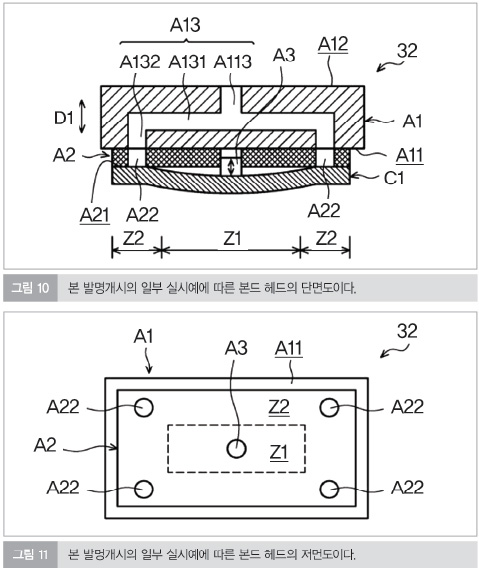

그림 10은 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 단면도이다. 그림 11은 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 저면도이다.본드 헤드(32)는 부착 엘리먼트(A2) 상에 배치되고 중심 영역(Z1)에서 위치되는 푸싱(pushing) 엘리먼트(A3)를 더 포함한다. 푸싱 엘리먼트(A3)는 부착면(A21) 위로 돌출된다. 칩(C1)은 칩(C1)이 부착면(A21)을 끌어당길 때, 푸싱 엘리먼트(A3)에 의해 휘어진다. 일부 실시예에 있어서, 푸싱 엘리먼트(A3)는 로드(rod) 구조물이다. 푸싱 엘리먼트(A3)는 약 0.05mm 내지 약 5mm의 범위 내의 폭을 가진다. 일부 실시예에 있어서, 푸싱 엘리먼트(A3)는 부착 엘리먼트(A2) 내에 이동가능하게 배치된다. 적층 방법의 단계(S201 및 S203)에서, 푸싱 엘리먼트(A3)는 부착 엘리먼트(A2) 내에 내장되고, 부착면(A21) 위로 돌출되지 않는다. 칩(C1)의 흡입력은 그림 5 및 그림 6의 실시예보다 클 수 있다. 따라서 이송 메커니즘(31)을 이용하여 칩(C1)을 전송하는 동안 칩(C1)이 부착면(A21)에 안정적으로 부착된다.

적층 방법의 단계(S205 및 S207)에서, 푸싱 엘리먼트(A3)는 부착면(A21) 위로 돌출하고 칩(C1)의 중심 부분을 푸시하며, 그림 10에 나타낸 바와 같이, 칩(C1)은 푸싱 엘리먼트(A3)에 의해 휘어진다. 일부 실시예에 있어서, 푸싱 엘리먼트(A3)는 약 0.5 N 내지 200 N의 범위 내의 가압력에 의해 칩(C1)을 푸시한다.

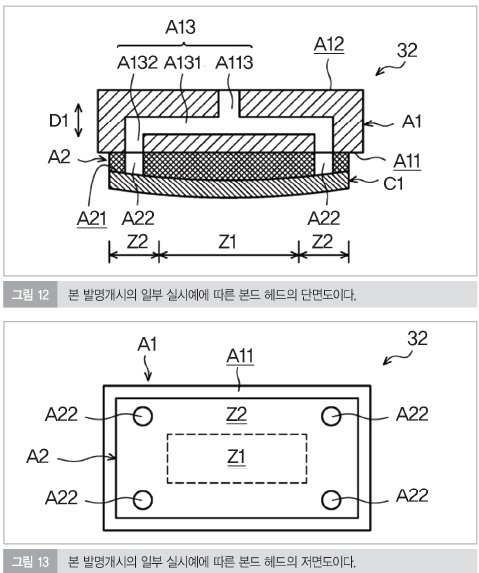

그림 12는 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 단면도이다. 그림 13은 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 저면도이다. 저면(A11)은 상면(A12)에 대향한다. 채널(A13)은 본드 베이스(A1) 내에 형성되고, 저면(A11) 및 상면(A12)에 접속된다. 채널(A13)은 상면(A12)을 통하여 진공 펌프(33)와 커플링된다.

부착 엘리먼트(A2)는 본드 베이스(A1)의 저면(A11) 상에 배치된다. 진공 홀(A22)은 부착 엘리먼트(A2)를 통과하여 채널(A13)에 접속된다. 진공 홀(A22)은 부착면(A21)의 가장자리 영역(Z2)에 위치된다. 일부 실시예에 있어서, 부착면(A21)은 휘어진 표면이다. 예를 들어, 본드 베이스(A1)에 대하여 부착 엘리먼트(A2)의 중심 영역(Z1)은 부착 엘리먼트(A2)의 가장자리 영역(Z2)보다 높다. 칩(C1)은 중심 영역(Z1) 및 가장자리 영역(Z2) 상에 부착되도록 구성된다.

진공 펌프(33)가 인에이블되면, 진공 홀(A22)은 진공 펌프(33)에 의해 진공 상태가 된다. 그림 12에 나타낸 바와 같이, 흡입력은 부착면(A21)의 가장자리 영역(Z2)에서 진공 홀(A22)을 통하여 발생된다. 진공 홀(A22)이 부착면(A21)의 가장자리 영역(Z2)에 위치되기 때문에, 칩(C1)의 가장자리는 진공 홀(A22)에 의해 부착 엘리먼트(A2)의 가장자리 영역(Z2)에 부착된다. 게다가, 부착면(A21)이 휘어진 표면이기 때문에, 일부 실시예에 있어서, 칩(C1)의 표면은, 칩(C1)이 본드 헤드(32)에 부착될 때, 부착면(A21)을 따라 휘어질 수 있다. 예를 들어, 칩(C1)의 중심이 또한 부착면(A21)에 부착될 수 있다.

적층 방법의 단계(S207)에서, 칩(C1)의 중심은 부착 공정 동안에 칩(C1)의 가장자리보다 이전에 기판(W1)에 접촉한다.

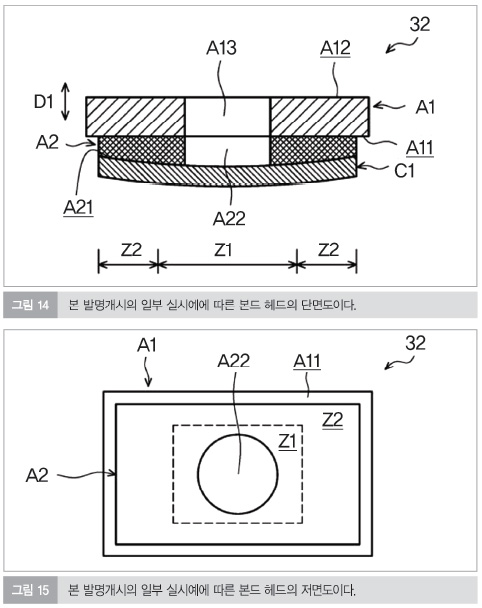

그림 14는 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 단면도이다. 그림 15는 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 저면도이다. 일부 실시예에 있어서, 채널(A13)은 방향(D1)을 따라 연장된다. 부착 엘리먼트(A2)는 채널(A13)에 접속된 하나의 진공 홀(A22)을 포함한다. 진공 홀(A22)은 부착면(A21)의 중심 영역(Z1)에 위치된다.

일부 실시예에 있어서, 부착면(A21)은 휘어진 표면이다. 칩(C1)은 휘어진 표면 상에 부착되도록 구성된다. 진공 홀(A22)이 부착면(A21)의 중심 영역(Z1)에 위치되기 때문에, 칩(C1)의 중심은 진공 홀(A22)을 통하여 부착 엘리먼트(A2)의 중심 영역(Z1)에 부착된다. 또한, 부착면(A21)이 휘어진 표면이기 때문에, 칩(C1)의 가장자리가 또한 부착면(A21)에 부착된다. 다르게 말하면, 칩(C1)이 부착 엘리먼트(A2)에 부착될 때, 칩(C1)은 부착면(A21)을 따라 휘어진다.

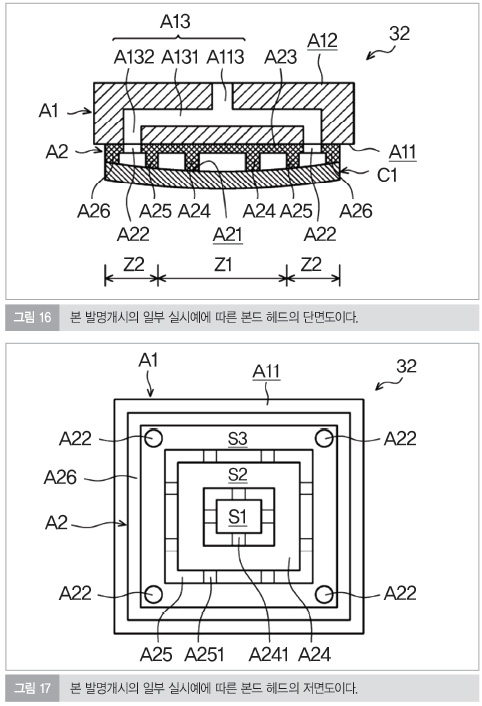

그림 16은 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 단면도이다. 그림 17은 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 저면도이다. 메인 채널(A131)은 본드 베이스(A1) 내에 내장된다. 저부 개구부(A132)는 저면(A11)의 가장자리 영역에 위치되고, 메인 채널(A131)에 접속된다. 상부 개구부(A133)는 상면(A12)의 중심 영역에 위치되고, 메인 채널(A131)에 접속된다. 상부 개구부(A133)는 진공 펌프(33)와 커플링된다.

부착 엘리먼트(A2)는 본드 베이스(A1)의 저면(A11) 상에 배치된다. 부착 엘리먼트(A2)는 저부 부분(A23), 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)을 포함한다. 저부 부분(A23)은 부착면(A21) 상에 배치된다. 저부 부분(A23)은 다수의 진공 홀(A22)을 포함한다. 진공 홀(A22)은 저부 부분(A23)을 통과하여 채널(A13)의 저부 개구부(A132)에 접속된다. 진공 홀(A22)은 부착면(A21)의 가장자리 영역(Z2)에 위치된다.

일부 실시예에 있어서, 저부 부분(A23)은 플레이트 구조물이다. 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)은 저부 부분(A23) 상에 배치된다. 일부 실시예에 있어서, 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)은 저부 부분(A23)과 직각을 이룬다. 중심 벽(A24), 중간 벽(A25), 가장자리 벽(A26) 및 저부 부분(A23)은 단일 피스로 형성된다.

일부 실시예에 있어서, 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)은 링(ring) 형상의 구조물이다. 중심 벽(A24)은 부착 엘리먼트(A2)의 중심 영역(Z1) 내에 위치된다. 중간 벽(A25) 및 가장자리 벽(A26)은 부착 엘리먼트(A2)의 가장자리 영역(Z2) 내에 위치된다. 중간 벽(A25)은 중심 벽(A24)과 가장자리 벽(A26) 사이에 위치된다. 다르게 말하면, 중간 벽(A25)은 중심 벽(A24) 둘레에 있다. 가장자리 벽(A26)은 중간 벽(A25) 둘레에 있다. 일부 실시예에 있어서, 중간 벽(A25)은 생략될 수 있다. 일부 실시예에 있어서, 부착 엘리먼트(A2)는 다수의 중간 벽(A25)을 포함한다. 일부 실시예에 있어서, 중심 벽(A24)은 다수의 쓰루 홀(A241)을 포함한다. 중간 벽(A25)은 다수의 쓰루 홀(A251)을 포함한다. 중심 벽(A24) 내의 공간(S1)은, 쓰루 홀(A241)을 통하여, 중심 벽(A24)과 중간 벽(A25) 사이에 있는, 공간(S2)과 연통한다. 중간 벽(A25)과 가장자리 벽(A26) 사이의 공간(S3)은 쓰루 홀(A251)을 통하여 공간(S2)와 연통한다.

진공 홀(A22)은 저부 부분(A23)의 가장자리 영역(Z2)에 위치된다. 그러므로 진공 펌프(33)가 인에이블되면, 공간(S3) 내의 공기는 진공 홀(A22)을 통하여 끌어당겨지고, 칩(C1) 상의 흡입력이 공간(S3)에 의해 발생된다. 또한, 공간(S2) 내의 공기가 또한 쓰루 홀(A251) 및 공간(S3)을 통하여 진공 펌프(33)에 의해 끌어당겨진다. 공간(S1) 내의 공기는 쓰루 홀(A241) 및 공간(S2) 통하여 진공 펌프(33)에 의해 끌어당겨진다. 그러므로 칩(C1)은 공간(S1 및 S2)을 통한 흡입력에 의해 끌어당겨진다. 칩(C1)은 진공 펌프(33)가 인에이블될 때, 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)의 단부에 부착된다.

일부 실시예에 있어서, 저부 부분(A23)에 대한 중심 벽(A24)의 높이는 저부 부분(A23)에 대한 중간 벽(A25)의 높이보다 높다. 저부 부분(A23)에 대한 중간 벽(A25)의 높이는 저부 부분(A23)에 대한 가장자리 벽(A26)의 높이 보다 높다. 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)의 단부는 부착면(A21)을 형성한다. 벽(A24-A26)의 각 상면은 휘어진 표면을 형성한다. 따라서, 칩(C1)이 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)의 단부에 부착될 때, 칩(C1)은 휘어진다.

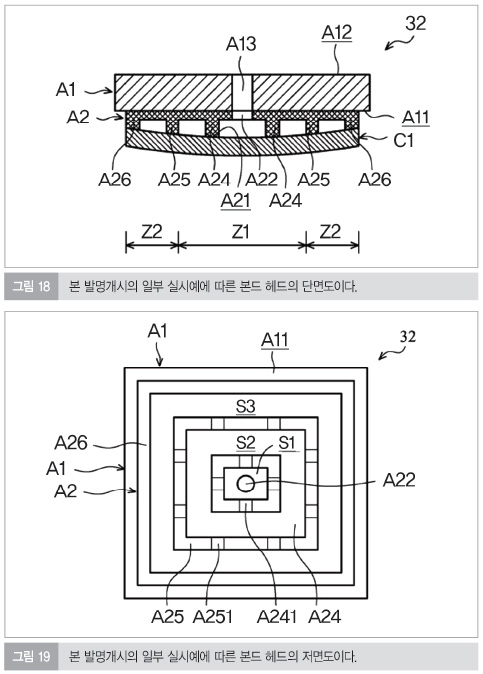

그림 18은 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 단면도이다. 그림 19는 본 발명개시의 일부 실시예에 따른 본드 헤드(32)의 저면도이다. 일부 실시예에 있어서, 채널(A13)은 방향(D1)을 따라 연장된다. 저부 부분(A23)은 채널(A13)에 접속된 하나의 진공 홀(A22)을 포함한다. 진공 홀(A22)은 저부 부분(A23)의 중심 영역(Z1)에 위치된다.

진공 홀(A22)은 부착면(A21)의 중심 영역(Z1)에 위치된다. 진공 펌프(33)가 인에이블되면, 공간(S1) 내의 공기는 진공 홀(A22)을 통하여 끌어당겨지고, 칩(C1) 상의 흡입력이 공간(S1)을 통하여 발생된다. 또한, 공간(S2) 내의 공기는 쓰루 홀(A241) 및 공간(S1)을 통하여 진공 펌프(33)에 의해 끌어당겨진다. 공간(S3) 내의 공기는 쓰루 홀(A251) 및 공간(S2)을 통하여 진공 펌프(33)에 의해 또한 끌어당겨진다. 따라서 칩(C1)에 대한 흡입력이 공간(S2 및 S3)을 통하여 발생된다. 진공 펌프(33)가 인에이블될 때, 칩(C1)이 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)의 단부에 부착된다. 일부 실시예에 있어서, 저부 부분(A23)에 대한 중심 벽(A24)의 높이는 저부 부분(A23)에 대한 중간 벽(A25)의 높이보다 높다. 저부 부분(A23)에 대한 중간 벽(A25)의 높이는 저부 부분(A23)에 대한 가장자리 벽(A26)의 높이보다 높다. 따라서 칩(C1)이 중심 벽(A24), 중간 벽(A25) 및 가장자리 벽(A26)의 단부에 부착될 때, 칩(C1)은 휘어진다.

칩 적층 장치(E1) 및 적층 방법의 실시예가 제공된다. 칩(C1) 및 기판(W1)은, 칩(C1)이 기판(W1) 상에 적층되기 전에 세정된다. 그러므로 칩(C1)과 기판(W1) 사이의 오염물은 감소된다. 또한, 후속 칩이 기판 상에 적층된 이전 칩의 위치에 따라 기판(W1) 상에 적층된다. 따라서 후속 칩은 기판(W1) 상에 정확하게 적층될 수 있다. 기판(W1)을 가진 칩(C1)의 제품의 수율이 증가된다. 또한, 부착 동정 동안에 칩(C1)이 부착면(A21)에 부착될 때 칩(C1)의 중심은 칩(C1)의 가장자리보다 이전에 기판(W1)에 접촉한다. 칩(C1)은 칩(C1)의 중심부터 가장자리까지 점차적으로 기판(W1)에 접촉하기 때문에, 칩 적층 디바이스(E50) 및 적층 방법에 의해 칩(C1)이 기판(W1) 상에 적층될 때 칩(C1)과 기판(W1) 사이의 기체 기포는 감소된다. 따라서 기판(W1)을 가진 칩(C1)의 제품의 수율이 또한 증가된다.

일부 실시예에 있어서, 기판 상에 칩을 적층하기 위한 칩 적층 장치가 제공된다. 칩 적층 장치는 기판을 반송하도록 구성된 기판 지지체 및 칩을 기판에 배치하도록 구성된 이송 디바이스를 포함한다. 이송 디바이스는 본드 헤드를 포함하고, 본드 헤드는 본드 베이스 및 본드 베이스 상에 배치되고 그 위에 칩이 부착될 수 있도록 구성된 부착 엘리먼트를 포함한다. 본드 베이스에 대하여 부착 엘리먼트의 중심 영역은 부착 엘리먼트의 가장자리 영역보다 높다.

일부 실시예에 있어서, 기판 상에 칩을 적층하기 위한 칩 적층 장치가 제공된다. 칩 적층 장치는 기판을 반송하도록 구성된 기판 지지체 및 기판 상으로 칩을 배치하도록 구성된 이송 디바이스를 포함한다. 이송 디바이스는 본드 헤드를 포함하고, 본드 헤드는 본드 베이스 및 중심 영역을 둘러싸는 가장자리 영역 및 가장자리 영역에 위치된 복수의 진공 홀을 포함하는 부착엘리먼트를 포함한다. 부착 엘리먼트는 본드 베이스 상에 배치되며, 그 위에 칩이 부착될 수 있도록 구성된다. 칩 적층 장치는 본드 헤드와 커플링되고 진공 홀을 통하여 본드 헤드가 흡입력을 갖게 하도록 구성된 진공 펌프를 또한 포함한다. 가장자리 영역에서의 본드 헤드의 흡입력은 중심 영역에서의 본드 헤드의 흡입력보다 강하다.