복수의 핀 포함한 핀

3D 디바이스용 커패시터

3D 커패시터 및 3D 커패시터를 제조하는 방법이 개시된다. 예시적인 3D 커패시터는 복수의 핀을 포함하는 핀 구조를 포함한 기판을 포함한다. 3D 커패시터는 기판 상의 복수의 핀들 각각 사이에 배치된 절연 물질을 더 포함한다. 3D 커패시터는 복수의 핀들 각각에 배치된 유전층을 더 포함한다. 3D 커패시터는 핀 구조의 제1 부분에 배치된 제1 전극을 더 포함한다. 제1 전극은 핀 구조의 표면과 직접 접촉한다. 3D 커패시터는 핀 구조의 제2 부분에 배치된 제2 전극을 더 포함한다. 제2 전극은 유전층 상에 직접 배치되고, 핀 구조의 제1 부분 및 제2 부분은 상이하다.

배경기술

반도체 집적 회로(IC) 산업은 급속한 성장을 이루었다. 집적 회로 진화 동안에, 기하학적 크기(즉, 제조 공정을 이용하여 생성될 수 있는 가장 작은 컴포넌트(또는 라인))는 감소한 반면, 기능 밀도(즉, 칩 영역당 상호접속된 장치의 수)는 일반적으로 증가하였다. 이러한 축소는 일반적으로 생산 효율성을 증가시키고 관련 비용을 낮춤으로써 이점을 제공한다. 또한, 이와 같은 축소는 IC 제조 및 처리의 복잡성을 증가시키고, 이러한 진보를 실현하기 위해, IC 제조에서 유사한 개발이 필요하다. 예를 들어, 반도체 산업이 높은 장치 밀도, 높은 성능 및 비용 절감을 추구하기 위해서 나노미터 기술 공정 노드로 진행함에 따라, 제조 및 설계 모두에서의 도전 과제는 3차원(3D) 장치의 개발을 야기시킨다. 3D 장치의 개발과 함께, 3D 장치를 위한 커패시터가 필요하다.

발명의 내용

발명을 실시하기 위한 구체적인 내용

다음의 개시는 본 발명의 상이한 피처(feature)들을 구현하는 다수의 상이한 실시예들, 또는 예들을 제공한다. 컴포넌트 및 배치의 특정한 예들은 본 개시를 단순화하기 위해 이하에 설명된다. 물론, 이러한 설명은 단지 예일 뿐 제한하기 위한 것이 아니다. 예를 들어, 이어지는 설명에서 제2 피처 위에 제1 피처의 형성은, 제1 피처 및 제2 피처가 직접 접촉하여 형성되는 실시예를 포함하고, 제1 피처 및 제2 피처가 직접 접촉하여 형성되지 않도록 제1 피처와 제2 피처 사이에 부가적인 피처들이 형성되는 실시예들을 또한 포함할 수 있다. 게다가, 본 개시는 다양한 예들에서 참조 번호 및/또는 문자를 반복할 수 있다. 이러한 반복은 단순함과 명료함을 위한 것으로, 그 자체가 논의된 다양한 실시예들 및/또는 구성들 사이의 관계를 지시하지 않는다. 또한, 본 명세서에 개시된 컴포넌트들은 본 개시의 범위를 벗어나지 않고 본 명세서에 도시된 예시적인 실시예들과는 상이한 방법으로 정렬, 조합, 또는 구성될 수 있다. 당업자는 본 명세서에는 명시적으로 기술되지 않았지만, 본 발명의 원리들을 포함하는 다양한 등가물을 고안할 수 있음을 이해한다.

본 발명의 하나 이상의 실시예들로부터 이익을 얻을 수 있는 장치의 예는, 반도체 장치이다. 이와 같은 장치는, 예를 들어, 3 차원(3D) 장치를 위한 커패시터이다. 커패시터는 금속 절연체 금속(metal insulator metal; MIM) 또는 금속 절연체 반도체(metal insulator semiconductor; MIS) 커패시터와 같은 3D 커패시터일 수 있다. 3D 커패시터는, 예를 들어, 핀 전계 효과 트랜지스터(fin-like field effect transistor; FinFET) 장치와 같은 3D 장치와 함께 이용될 수 있다. FinFET 장치는, 예를 들어, P형 금속 산화막 반도체(P-type metal-oxide-semiconductor; PMOS) FinFET 장치, 또는 N형 금속 산화막 반도체(NMOS) FinFET 장치일 수 있다.

다음 설명은 본 개시의 다양한 실시예들을 나타내기 위해 FinFET 장치를 위한 MIM 커패시터 예를 계속 이용할 것이다. 그러나 본 개시는 특별하게 특허청구 되는 것을 제외하고, 특정한 유형의 장치로 제한되어서는 안된다는 것을 이해해야 한다.

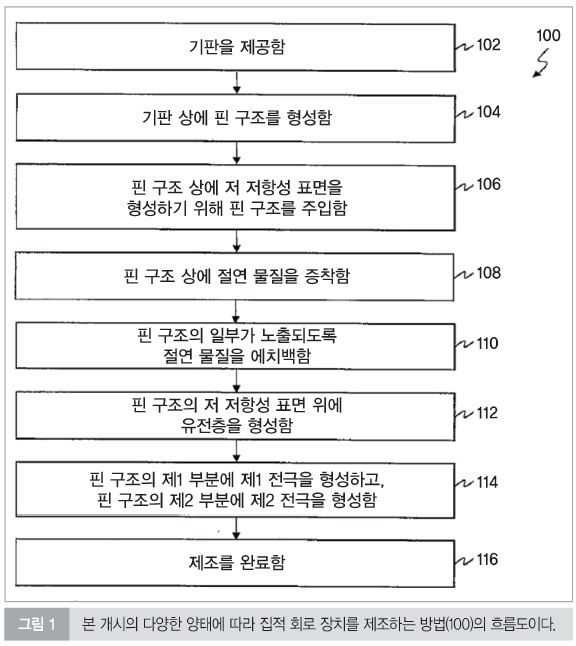

그림 1은 본 개시의 다양한 양태에 따라 집적 회로 장치를 제조하는 방법(100)의 흐름도이다. 본 실시 예에서, 방법(100)은 3D 커패시터를 포함하는 집적 회로 장치를 제조하는 것이다. 방법(100)은 기판이 제공되는 블록(102)에서 시작한다. 블록(104)에서, 핀 구조가 기판 위에 형성된다. 핀 구조의 형성은 마스크층을 패턴화하고, 마스크층을 이용하여 반도체 기판을 에칭하는 것을 포함할 수 있다. 블록(106)에서, 핀 구조는 핀 구조 상에 저 저항성 표면을 형성하기 위해 주입된다. 방법(100)은 블록(108)으로 계속 진행하고, 이 블록에서 절연 물질이 핀 구조 상에 증착된다. 절연 물질은, 핀 구조를 커버하고 실질적으로 핀 구조의 각각의 핀 사이의 영역을 충진하도록 증착될 수 있다. 유전층의 탑 표면을 평탄화하여 핀 구조의 탑 표면을 노출하도록 평탄화 공정이 그 뒤에 수행될 수 있다. 방법(100)은 블록(110)으로 계속 진행하고, 이 블록에서 핀 구조의 일부가 노출되도록 에칭 공정이 절연 물질 상에 수행된다. 블록(112)에서, 유전층이 핀 구조의 저 저항성 표면 위에 형성된다. 방법(100)은 블록(114)으로 진행하고, 이 블록에서 제1 전극이 핀 구조의 제1 부분에 형성되고, 제2 전극이 핀 구조의 제2 부분에 형성된다. 제1 부분 및 제2 부분은 상이하다. 방법(100)은 블록(116)으로 진행하고, 이 블록에서 집적 회로 장치의 제조가 완료된다. 부가적인 단계들이 상기 방법(100) 이전에, 방법 동안에, 그리고 방법 이후에 제공될 수 있고, 기술된 방법들의 일부는 상기 방법의 다른 실시예들을 위해 교체되거나 제거될 수 있다. 이어지는 설명은 그림 1의 방법(100)에 따라 제조될 수 있는 집적 회로 장치의 다양한 실시예들을 나타낸다.

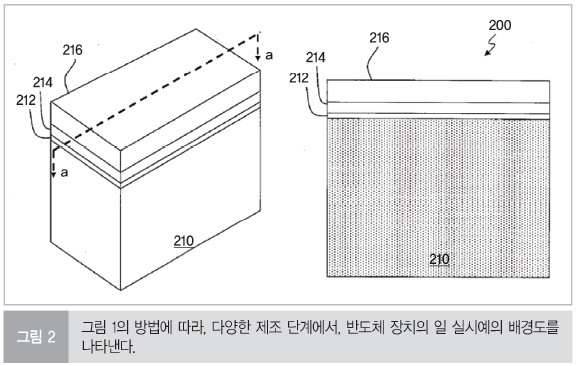

그림 2를 참조하면, 3D 커패시터(200)는 기판(예컨대, 웨이퍼)(210)을 포함한다. 기판(210)은 벌크 실리콘 기판이다. 대안적으로, 기판(210)은 결정 구조의 실리콘 또는 게르마늄과 같은 기본(elementary) 반도체; 실리콘 게르마늄, 탄화 규소, 비화 갈륨, 인화 갈륨, 인화 인듐, 비화 인듐 및/또는 안티몬화 인듐과 같은 화합물 반도체; 또는 이들의 조합을 포함한다. 대안적으로, 기판(210)은 실리콘 온 인슐레이터(silicon-oninsulator; SOI) 기판이다. SOI 기판은 산소의 주입에 의한 분리(separation by implantation of oxygen; SIMOX), 웨이퍼 본딩 및/또는 다른 적합한 방법을 이용하여 제조될 수 있다. 그림 2를 더욱 참조하면, 기판(210) 위에 유전층(212)이 형성된다. 유전층(212)은 임의의 적합한 공정에 의해 임의의 적합한 두께로 형성된다. 본 실시예에서, 유전층(212)은 실리콘 산화물을 포함하고, CVD 또는 열 산화 공정에 의해 형성된다. 열 산화 공정은 건식 공정 또는 습식 공정일 수 있다. 다양한 예에서, 실리콘 산화물은 물리적 기상 증착(physical vapor deposition; PVD), 원자층 증착(atomic layer deposition; ALD), 고밀도 플라즈마 CVD(high density plasma CVD; HDPCVD), 다른 적합한 방법 및/또는 이들의 조합에 의해 형성될 수 있다. CVD 공정은, 예를 들어, 헥사클로로디실란(HCD 또는 Si2Cl6), 디클로로실란(DCS 또는 SiH2Cl2), 비스(3차부틸아미노)실란(BTBAS 또는 C8H22N2Si) 및 디실란(DS 또는 Si2H6)을 포함하는 화학 물질을 이용할 수 있다.

마스크층(214)은 유전층(212) 위에 형성된다. 본 실시예에서, 마스크층(214)은 실리콘 질화물을 포함하고, CVD 공정에 의해 형성된다. 마스크층(214)은 정지층/하드 마스크층일 수 있다. 마스크층(214)은 임의의 적합한 공정에 의해 임의의 적합한 두께로 형성된다. 마스크층(214)은 실리콘 질화물, 실리콘 산화질화물, 실리콘 탄화물, 실리콘 탄화 질화물, 다른 적합한 물질, 또는 이들의 조합물과 같은 물질을 포함할 수 있다. 본 실시예에서, 마스크층(214)은 실리콘 질화물을 포함하고, 화학적 기상 증착(chemical vapor deposition; CVD) 공정에 의해 형성된다. 다양한 예에서, 실리콘 질화물은 물리적 기상 증착(physical vapor deposition; PVD), 원자층 증착(atomic layer deposition; ALD), 고밀도 플라즈마 CVD(high density plasma CVD; HDPCVD), 다른 적합한 방법 및/또는 이들의 조합에 의해 형성될 수 있다. CVD 공정은, 예를 들어, 헥사클로로디실란(HCD 또는 Si2Cl6), 디클로로실란(DCS 또는 SiH2Cl2), 비스(3차부틸아미노)실란(BTBAS 또는 C8H22N2Si) 및 디실란(DS 또는 Si2H6)을 포함하는 화학 물질을 이용할 수 있다. 포토레지스트층(216)은 마스크층(214) 위에 형성된다. 포토레지스트층(216)은 임의의 적합한 공정에 의해 임의의 적합한 두께로 형성된다.

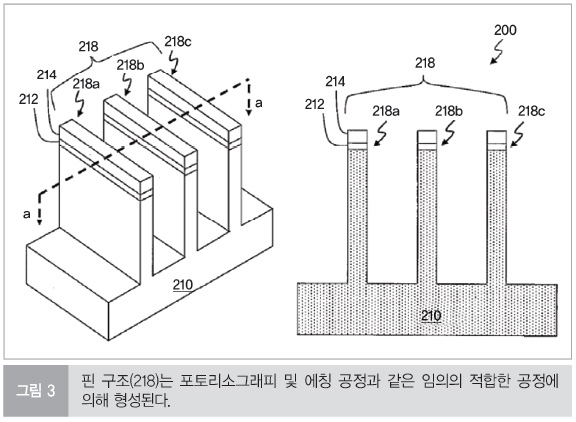

그림 3을 참조하면, 핀 구조(218)(복수의 핀들(218a, 218b 및 218c)을 포함함)는 포토리소그래피 및 에칭 공정과 같은 임의의 적합한 공정에 의해 형성된다. 예를 들어, 본 실시예에서, 핀 구조(218)는 포토레지스트층(216)을 패턴에 노출하고, 포스트 노출 베이크 공정을 수행하고, 포토레지스트층(216) 및 마스크층(214)을 포함하는 마스킹 요소를 형성하기 위해 포토레지스트층(216)을 현상함으로써 형성된다. 포토레지스트층(216)을 패턴화하는 것은, 포토레지스트 코팅, 소프트 베이킹, 마스크 정렬, 패턴 노출, 포트스 노출 베이킹, 포토레지스트 현상 및 하드 베이킹의 처리 단계들을 포함할 수 있다. 패턴화는 또한 마스크 없는 포토리소그래피, 전자 빔 기록, 이온 빔 기록 및 분자압인(molecular imprint)과 같은, 다른 적절한 방법에 의해 구현되거나 교체될 수 있다. 그 다음에, 마스킹 요소(포토레지스트층(216) 및 마스크층(214)을 포함함)는 에칭 공정에 이용되어 핀 구조(218)롤 기판(210)으로 에칭할 수 있다. 에칭 공정은 패턴화된 마스크층(214)을 이용하여 에칭될 영역을 정의하고 3D 커패시터(200)의 다른 영역을 보호한다. 에칭 공정은 습식 에칭 공정, 건식 에칭 공정, 또는 이들의 조합을 포함할 수 있다. 핀 구조(218)는 반응성 이온 에칭(reactive ion etch; RIE)을 이용하는 에칭 공정 및/또는 다른 적합한 공정에 의해 형성될 수 있다. 일례로, 플루오린화수소산(HF) 또는 버퍼링된 HF가 마스크층(214)에 의해 정의된 패턴에 따라 기판(210)을 노출하기 위해 유전층(212)을 에칭하는데 이용될 수 있다. 일례로, 기판(210)을 에칭하기 위해 이용되는 건식 에칭 공정은 플루오린 함유 기체를 포함하는 화학 물질을 포함한다. 이 예를 증진하기 위해서, 건식 에칭의 화학 물질은 CF4, SF6, 또는 NF3를 포함한다.

대안적으로, 핀 구조(218)는 더블 패턴닝 리소그래피(double-patterning lithography; DPL) 공정에 의해 형성된다. DPL은 패턴을 두 개의 인터리브 패턴으로 분할함으로써 기판 상에 패턴을 구성하는 방법이다. DPL은 향상된 피처(예컨대, 핀) 밀도를 허용한다. 이중 노출을 포함하는 다양한 DPL 방법이 이용될 수 있다.

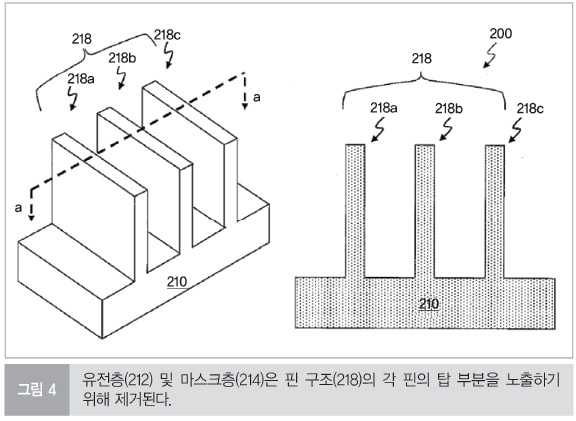

그림 4를 참조하면, 유전층(212) 및 마스크층(214)은 핀 구조(218)의 각 핀(218a, 218b, 218c)의 탑 부분을 노출하기 위해 제거된다. 유전층(212) 및 마스크층(214)은 임의의 적합한 공정에 의해 제거될 수 있다. 예를 들어, 유전층(212) 및 마스크층(214)의 제거는 습식 에칭 공정, 건식 에칭 공정, 또는 이들의 조합을 포함할 수 있다.

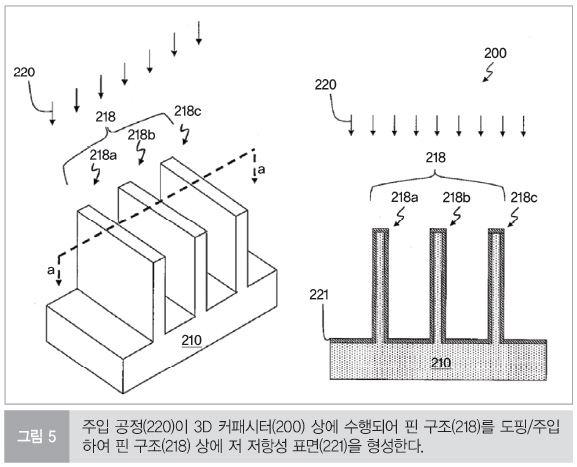

그림 5를 참조하면, 주입 공정(220)이 3D 커패시터(200) 상에 수행되어 핀 구조(218)를 도핑/주입하여 핀 구조(218) 상에 저 저항성 표면(221)을 형성한다. 주입 공정(220)은 붕소, BF2, 인, 비소 또는 저 저항성 표면(221)을 제공하기 위한 임의의 다른 적합한 주입 종과 같은 도펀트를 이용하는 것을 포함할 수 있다. 일부 실시예들에서, 이것은 대략 5 내지 150 KeV 사이의 에너지에서, 대략 1E15 내지 1E 16 atoms/cm2 사이의 도즈로 붕소 또는 인의 이온 주입을 통해 달성된다.

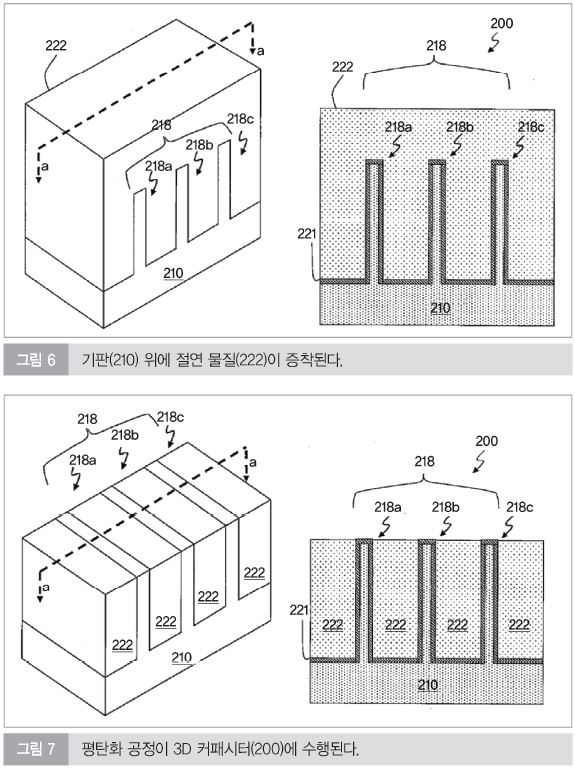

그림 6을 참조하면, 기판(210) 위에(그리고 핀 구조(218)의 저 저항성 표면(221) 위에) 절연 물질(222)이 증착된다. 절연 물질(222)은 핀 구조(218)의 각 핀(218a, 218b, 218c)을 서로 분리하고 각 핀을 둘러싸도록 증착된다. 절연 물질(222)은 실리콘 산화물, 실리콘 질화물, 실리콘 산화질화물, 저유전율 물질, 공극, 다른 적합한 물질, 또는 이들의 조합과 같은 절연 물질을 포함할 수 있다. 본 실시예에서, 절연 물질(222)은 실리콘 산화물을 포함한다. 실리콘 산화물은 CVD 공정에 의해 증착될 수 있다. 다양한 예에서, 실리콘 산화물은 물리적 기상 증착(physical vapor deposition; PVD), 원자층 증착(atomic layer deposition; ALD), 고밀도 플라즈마 CVD(high density plasma CVD; HDPCVD), 다른 적합한 방법 및/또는 이들의 조합에 의해 형성될 수 있다. 실리콘 산화물은 대안적으로 고세장비 공정(high aspect ratio process; HARP)에 의해 형성될 수 있다.

다양한 실시예들에서, 선택적인 열 산화 트렌치 라이너가 트렌치 인터페이스를 향상시키기 위해 성장될 수 있다. CVD 공정은, 예를 들어, 헥사클로로디실란(HCD 또는 Si2Cl6), 디클로로실란(DCS 또는 SiH2Cl2), 비스(3차부틸아미노)실란(BTBAS 또는 C8H22N2Si) 및 디실란(DS 또는 Si2H6)을 포함하는 화학 물질을 이용할 수 있다. 절연 물질(222)은 다층 구조(예를 들어, 라이너 위에 형성된 실리콘 질화물을 갖는 열 산화 라이너 층)를 가질 수 있다.

그림 7을 참조하면, 평탄화 공정이 3D 커패시터(200)에 수행된다. 일 실시예에서, 평탄화 공정은 절연 물질(222)의 과도한 부분을 제거하기 위해 3D 커패시터(200)에 적용된 화학적 기계적 연마(chemical mechanical polishing; CMP) 공정을 포함한다. 평탄화 공정은 절연 물질(222)을 제거하여 핀 구조(218)의 각 핀(218a, 218b, 218c)의 탑 부분을 노출하도록 수행될 수 있다.

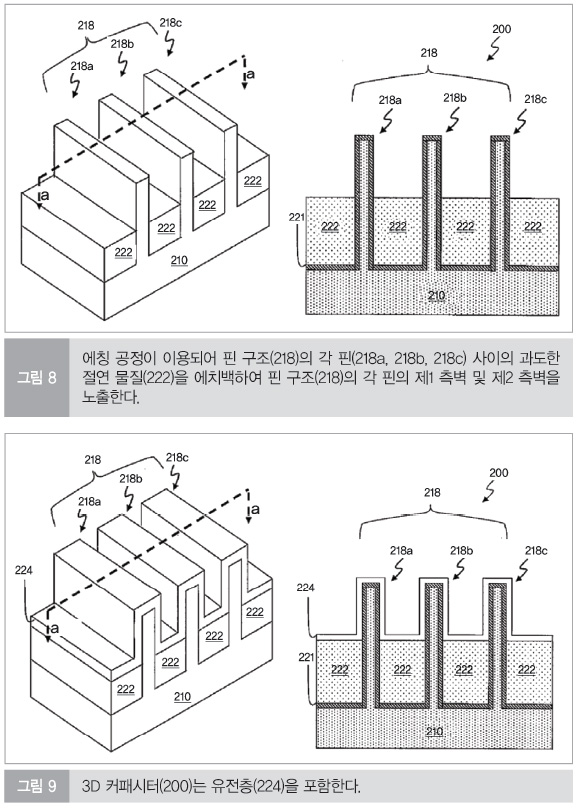

그림 8을 참조하면, 에칭 공정이 이용되어 핀 구조(218)의 각 핀(218a, 218b, 218c) 사이의 과도한 절연 물질(222)을 에치백하여 핀 구조(218)의 각 핀의 제1 측벽 및 제2 측벽을 노출한다. 에칭 공정은 습식 에칭 공정, 건식 에칭 공정, 또는 이들의 조합을 포함할 수 있다. 일례로, 절연 물질(222)을 에칭하기 위해 이용되는 건식 에칭 공정은 플루오린 함유 기체를 포함하는 화학 물질을 포함할 수 있다. 이 예를 증진하기 위해서, 건식 에칭의 화학 물질은 CF4, SF6, 또는 NF3를 포함한다.

그림 9를 참조하면, 3D 커패시터(200)는 유전층(224)을 포함한다. 유전층(224)은 핀 구조(218)를 횡단한다. 일부 실시예들에서, 유전층(224)은 실리콘 산화물, 실리콘 질화물, 실리콘 산화질화물, 또는 고유전율(high-k) 유전체를 포함할 수 있다. 고유전율 유전체는 특정 금속 산화물을 포함한다. 고유전율 유전체를 위해 이용되는 금속 산화물의 예는, Li, Be, Mg, Ca, Sr, Sc, Y, Zr, Hf, Al, La, Ce, Pr, Nd, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu 및 이들의 혼합물의 산화물을 포함한다. 본 실시예에서, 유전층(224)은 HfOx를 포함하는 고유전율 유전층이다. 게이트 유전층(224)은 원자층 증착(atomic layer deposition; ALD), 화학적 기상 증착(chemical vapor deposition; CVD), 물리적 기상 증착(physical vapor deposition; PVD), 열산화, UV-오존 산화 또는 이들의 조합과 같은 적합한 공정을 이용하여 형성될 수 있다. 유전층(224)은 유전층(224) 및 기판(210) 및/또는 핀 구조(218) 사이의 손상을 줄이기 위해 계면층(도시되지 않음)을 더 포함할 수 있다. 계면층은 실리콘 산화물을 포함할 수 있다.

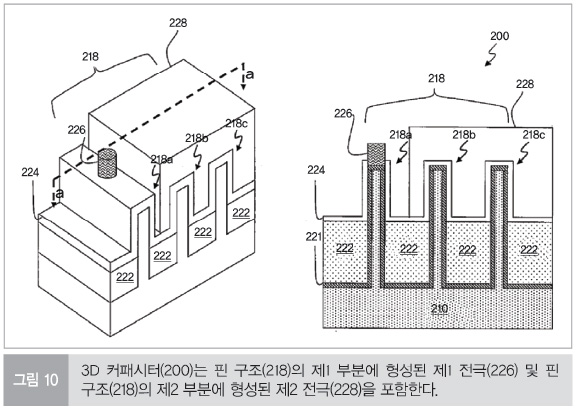

그림 10에서는, 3D 커패시터(200)는 핀 구조(218)의 제1 부분에 형성된 제1 전극(226) 및 핀 구조(218)의 제2 부분에 형성된 제2 전극(228)을 포함한다. 핀 구조(218)의 제1 부분 및 제2 부분은 상이하다. 예시된 실시예에서, 제1 부분은 핀(218a)의 일부를 포함하고, 제2 부분은 핀(218b, 218c)의 일부를 포함한다. 제1 전극(226) 및 제2 전극(228)은 임의의 적합한 도전 물질을 포함한다. 예를 들어, 제1 전극(226) 및 제2 전극(228)은 Al, Cu 및 W, 다른 도전 물질, 또는 이들의 조합을 포함한다.

제1 전극(226) 및 제2 전극(228)은 증착 공정, 리소그래피 패턴화 공정 및 에칭 공정을 포함하는 임의의 적합한 공정에 의해 형성될 수 있다. 증착 공정은 화학적 기상 증착(chemical vapor deposition; CVD), 물리적 기상 증착(physical vapor deposition; PVD), 원자층 증착(atomic layer deposition; ALD), 고밀도 플라즈마 CVD(high density plasma CVD; HDPCVD), 유기 금속 CVD(metal organic CVD; MOCVD), 원격 플라즈마 CVD(remote plasma CVD; RPCVD), 플라즈마 향상 CVD(plasma enhanced CVD; PECVD), 저압 CVD(low-pressure CVD; LPCVD), 원자층 CVD(atomic layer CVD; ALCVD), 대기압 CVD(atmospheric pressure CVD; APCVD), 도금, 다른 적합한 방법, 또는 이들의 조합을 포함한다. 리소그래피 패턴화 공정은 포토레지스트 코팅(예컨대, 스핀온 코팅), 소프트 베이킹, 마스크 정렬, 노출, 포스트 노출 베이킹, 포토레지스트 현상, 세정, 건조(예컨대, 하드 베이킹), 다른 적합한 공정, 또는 이들의 조합을 포함한다. 대안적으로, 리소그래피 노출 공정은 마스크 없는 포토리소그래피, 전자 빔 기록 및 이온 빔 기록과 같은 다른 방법에 의해 구현되거나 교체된다. 또 다른 대안으로, 리소그래피 패턴화 공정은 나노임프리트 기술을 구현할 수 있다. 에칭 공정은 건식 에칭, 습식 에칭 및/또는 다른 에칭 방법을 포함한다.

그림 10에 도시된 바와 같이, 3D 커패시터(200)는 복수의 핀들(218a, 218b, 218c)을 포함하는 핀 구조(218)를 포함하는 기판(210)을 포함한다. 현재 실시예가 3개의 핀들(218a, 218b, 218c)을 예시하지만, 더 많거나/더 적은 핀들이 고려된다. 기판(210) 및 핀 구조(218)는 저 저항성 표면(221)을 포함한다. 저 저항성 표면(221)은 기판(210) 및 핀 구조(218)의 탑 부분/층 상에 형성된다. 더욱이, 저 저항성 표면(221)은 핀 구조(218)의 각각의 핀(218a, 218b, 218c)의 측벽 상에 형성된다. 3D 커패시터(200)는 저 저항성 표면(221) 상에 그리고 핀 구조(218)의 각각의 핀(218a, 218b, 218c) 사이의 영역에 배치된 절연 물질(222)을 더 포함한다. 유전층(224)이 핀 구조(218) 및 저 저항성 표면(221) 위에 형성된다. 유전층(224)은 핀 구조(218)의 각각의 핀(218a, 218b, 218c)을 횡단한다. 제 1전극(226)이 유전층(224) 위에 형성된다. 제1 전극(226)은 핀 구조(218)의 적어도 하나의 핀(예컨대, 218a)의 중앙 영역에 형성된다. 예시된 실시예에서, 제1 전극(226)은 제1 전극(226)의 근간이 되는 제1 핀(예컨대, 218a)의 저 저항성 표면(221)과 직접 접촉하여, 전류가 저 저항성 표면(221)을 통해 제1 전극(226)과 핀 구조(218) 사이를 지나갈 수 있도록 한다. 제2 전극(228)이 핀 구조(218)의 제2 부분에 형성된다. 제2 전극(228)은 유전층(224)에 형성되어, 그로 인해 핀 구조(218)로부터 분리된다.

제2 전극(228)은 핀 구조(218)의 제2 부분 상에서 핀들(218a, 218b, 218c)의 길이를 따라 형성되고 핀 구조(218)를 횡단한다. 예시된 실시예에서, 제2 전극(228)은 또한 핀 구조(218)의 핀들(218a, 218b, 218c) 사이의 영역에서 유전층(224) 상에 형성된다. 예시된 실시예에서, 제1 전극(226) 및 제2 전극(228)은 핀 구조(218) 중 하나의 핀도 공동으로 갖지 않도록 형성된다. 제1 전극(226) 및 제2 전극(228)은 서로 분리된다.

그림 10의 실시예는 금속 절연막 반도체(metal insulator semiconductor; MIS) 커패시터를 제공한다. 예시된 바와 같이, 제1 전극(226)은 핀 구조(218)를 포함하는 기판(210)에 저 저항성 표면(221)을 통하여 연결을 제공한다. 제2 전극(228)으로부터 유전층(224)에 의해 분리되는 핀 구조(218)을 포함하는 기판(210)은 MIS 커패시터를 제공한다. 그림 10의 실시예에 예시된 3D 커패시터(200)가 오직 3개의 핀만을 포함하지만, 3D 커패시터(200)는 설계 요건에 따라, 하나 이상의 핀들을 포함할 수 있음을 이해한다. 더욱이, 예시된 실시예에서, 제1 전극은 오직 하나의 핀 상에 형성되지만, 제1 전극은 설계 요건에 따라 하나 보다 많은 핀 상에 형성될 수 있음을 이해한다.

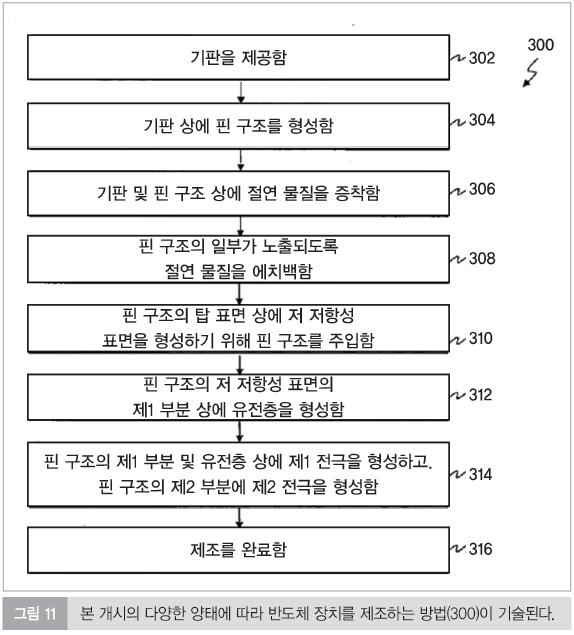

그림 11을 참조하면, 본 개시의 다양한 양태에 따라 반도체 장치를 제조하는 방법(300)이 기술된다. 방법(300)의 실시예는 앞서 논의된 방법(100)의 실시예와 유사한 공정 단계를 포함할 수 있다. 방법(300)의 실시예를 논의함에 있어서, 처리 및/또는 구조에 관한 일부 세부 사항들은, 방법(100)의 실시예에 기술된 것과 유사하다면, 간단함을 위해 스킵될 수 있다.

본 실시예에서, 방법(300)은 3D 커패시터를 포함하는 집적 회로 장치를 제조하는 것이다. 방법(300)은 기판이 제공되는 블록(302)에서 시작한다. 블록(304)에서, 핀 구조가 기판 위에 형성된다. 핀 구조의 형성은 마스크 층을 패턴화하고, 마스크층을 이용하여 반도체 기판을 에칭하는 것을 포함할 수 있다. 블록(306)에서, 절연 물질이 핀 구조 상에 증착된다. 절연 물질은, 핀 구조를 커버하고 실질적으로 핀 구조의 각각의 핀 사이의 영역을 충진하도록 증착될 수 있다. 유전층의 탑 표면을 평탄화하여 핀 구조의 탑 부분을 노출하도록 평탄화 공정이 그 뒤에 수행될 수 있다. 방법(100)은 블록(308)으로 계속 진행하고, 이 블록에서 핀 구조의 일부가 노출되도록 에칭 공정이 절연 물질 상에 수행된다. 블록(310)에서, 핀 구조는 핀 구조 상에 저 저항성 표면을 형성하기 위해 주입된다. 블록(312)에서, 유전층이 핀 구조의 저 저항성 표면 위에 형성된다. 방법(300)은 블록(314)으로 진행하고, 이 블록에서 제1 전극이 핀 구조의 제1 부분에 형성되고, 제2 전극이 핀 구조의 제2 부분에 형성된다. 제1 부분 및 제2 부분은 상이하다. 방법(300)은 블록(316)으로 진행하고, 이 블록에서 집적 회로 장치의 제조가 완료된다. 부가적인 단계들이 상기 방법(300) 이전에, 방법 동안에, 그리고 방법 이후에 제공될 수 있고, 기술된 방법들의 일부는 상기 방법의 다른 실시예들을 위해 교체되거나 제거될 수 있다. 이어지는 설명은 그림 11의 방법(300)에 따라 제조될 수 있는 집적 회로 장치의 다양한 실시예들을 나타낸다.

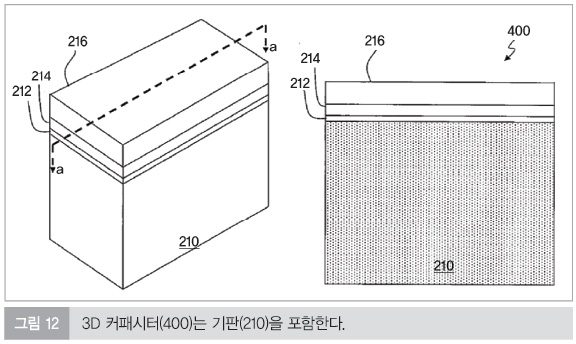

그림 12를 참조하면, 3D 커패시터(400)는 기판(210)을 포함한다. 본 실시예에서, 3D 커패시터(400)에 정의된 기판(210)은 조성, 형성 및 구성의 면에서 3D 커패시터(200)의 기판(210)과 실질적으로 유사하다. 대안적인 실시예에서, 이들은 상이하다. 그림 12를 참조하면, 3D 커패시터(400)는 또한 유전층(212), 마스크층(214) 및 포토레지스트층(216)을 포함한다. 본 실시예에서, 3D 커패시터(400)에 정의된 유전층(212), 마스크층(214) 및 포토레지스트층(216)은 조성, 형성 및 구성의 면에서 3D 커패시터(200)의 유전층(212), 마스크층(214) 및 포토레지스트층(216)과 실질적으로 유사하다. 대안적인 실시예에서, 이들은 상이하다.

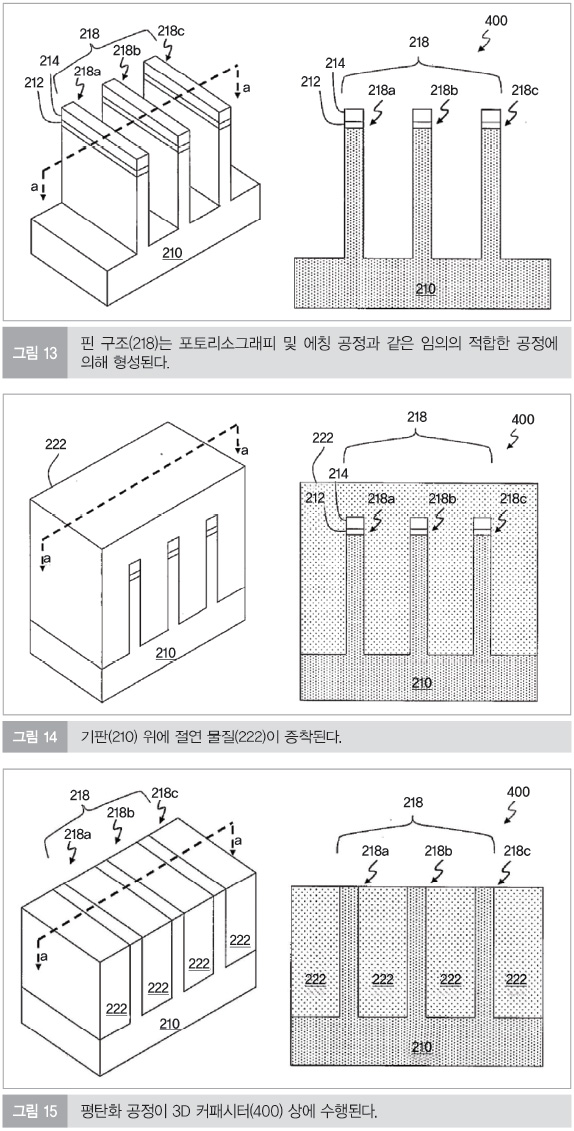

그림 13을 참조하면, 핀 구조(218)(복수의 핀들(218a, 218b 및 218c)을 포함함)는 포토리소그래피 및 에칭 공정과 같은 임의의 적합한 공정에 의해 형성된다. 본 실시예에서, 3D 커패시터(400)의 핀 구조(218)를 형성하는 공정은 3D 커패시터(200)의 핀 구조(218)를 형성하는 공정과 실질적으로 유사하다. 대안적인 실시예에서, 이들은 상이하다.

그림 14를 참조하면, 기판(210) 위에 절연 물질(222)이 증착된다. 본 실시예에서, 3D 커패시터(400)에 정의된 절연 물질(222)은 조성, 형성 및 구성의 면에서 3D 커패시터(200)의 절연 물질(222)과 실질적으로 유사하다. 대안적인 실시예에서, 이들은 상이하다.

그림 15를 참조하면, 평탄화 공정이 3D 커패시터(400) 상에 수행된다. 일 실시예에서, 평탄화 공정은 절연 물질(222)의 과도한 부분을 제거하기 위해 3D 커패시터(400)에 적용된 화학적 기계적 연마(chemical mechanical polishing; CMP) 공정을 포함한다. 평탄화 공정은 절연 물질(222), 유전층(212) 및 하드 마스크(214)를 제거하여 핀 구조(218)의 각 핀(218a, 218b, 218c)의 탑 표면을 노출하도록 수행될 수 있다.

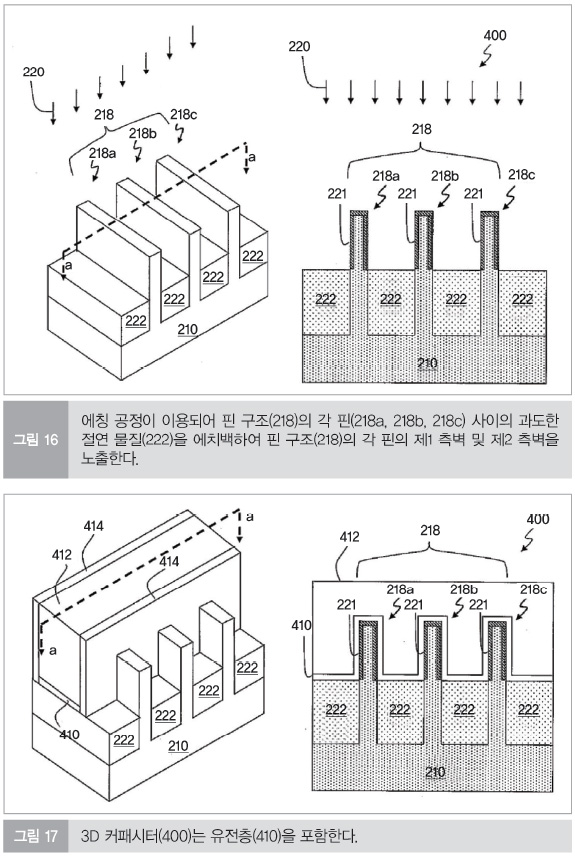

그림 16을 참조하면, 에칭 공정이 이용되어 핀 구조(218)의 각 핀(218a, 218b, 218c) 사이의 과도한 절연 물질(222)을 에치백하여 핀 구조(218)의 각 핀의 제1 측벽 및 제2 측벽을 노출한다. 본 실시예에서, 3D 커패시터(400)의 과도한 절연 물질(222)을 에치백하는데 이용되는 에칭 공정은 3D 커패시터(200)의 과도한 절연 물질(222)을 에치백하는데 이용되는 에칭 공정과 실질적으로 유사하다. 대안적인 실시예에서 이들은 상이하다.

그림 16을 참조하면, 주입 공정(220)이 3D 커패시터(400) 상에 수행되어 핀 구조(218)를 주입하여 핀 구조(218) 상에 저 저항성 표면(221)을 형성한다. 본 실시예에서, 3D 커패시터(400)의 핀 구조(218)를 주입하는데 이용되는 주입 공정(220)은 3D 커패시터(200)의 핀 구조(218)를 주입하는데 이용되는 주입 공정(220)과 실질적으로 유사하다. 대안적인 실시예에서, 이들은 상이하다.

그림 17을 참조하면, 3D 커패시터(400)는 유전층(410)을 포함한다. 유전층(410)은 핀 구조(218)를 횡단한다. 일부 실시예들에서, 유전층(410)은 실리콘 산화물, 실리콘 질화물, 실리콘 산화질화물, 또는 고유전율(high-k) 유전체를 포함할 수 있다. 고유전율 유전체는 특정 금속 산화물을 포함한다. 고유전율 유전체를 위해 이용되는 금속 산화물의 예는, Li, Be, Mg, Ca, Sr, Sc, Y, Zr, Hf, Al, La, Ce, Pr, Nd, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu 및 이들의 혼합물의 산화물을 포함한다. 본 실시예에서, 유전층(410)은 HfOx를 포함하는 고유전율 유전층이다. 유전층(410)은 원자층 증착(atomic layer deposition; ALD), 화학적 기상 증착(chemical vapor deposition; CVD), 물리적 기상 증착(physical vapor deposition; PVD), 열산화, UV-오존 산화 또는 이들의 조합과 같은 적합한 공정을 이용하여 형성될 수 있다. 유전층(410)은 유전층(410) 및 기판(210) 및/또는 핀 구조(218) 사이의 손상을 줄이기 위해 계면층(도시되지 않음)을 더 포함할 수 있다. 계면층은 실리콘 산화물을 포함할 수 있다.

그림 17을 계속 참조하면, 3D 커패시터(400)는 핀 구조(218)의 제1 부분에 형성된 제1 전극(412)을 더 포함한다. 예시된 실시예에서, 제1 부분은 핀들(218a, 218b, 218c)의 일부를 포함한다. 제1 전극(412)은 예를 들어, Al, Cu 및 W와 같은 도전 재료, 다른 적합한 도전 재료, 또는 이들의 조합을 포함한다. 제1 전극(214)은 증착 공정, 리소그래피 패턴화 공정 및 에칭 공정과 같은 임의의 적합한 공정에 의해 형성될 수 있다. 증착 공정은 화학적 기상 증착(chemical vapor deposition; CVD), 물리적 기상 증착(physical vapor deposition; PVD), 원자층 증착(atomic layer deposition; ALD), 고밀도 플라즈마 CVD(high density plasma CVD; HDPCVD), 유기 금속 CVD(metal organic CVD; MOCVD), 원격 플라즈마 CVD(remote plasma CVD; RPCVD), 플라즈마 향상 CVD(plasma enhanced CVD; PECVD), 저압 CVD(low-pressure CVD; LPCVD), 원자층 CVD(atomic layer CVD; ALCVD), 대기압 CVD(atmospheric pressure CVD; APCVD), 도금, 다른 적합한 방법 또는 이들의 조합을 포함한다. 리소그래피 패턴화 공정은 포토레지스트 코팅(예컨대, 스핀 온 코팅), 소프트 베이킹, 마스크 정렬, 노출, 포스트 노출 베이킹, 포토레지스트 현상, 세정, 건조(예컨대, 하드 베이킹), 다른 적합한 공정, 또는 이들의 조합을 포함한다. 대안적으로, 리소그래피 노출 공정은 마스크 없는 포토리소그래피, 전자 빔 기록 및 이온 빔 기록과 같은 다른 방법에 의해 구현되거나 교체된다. 또 다른 대안으로, 리소그래피 패턴화 공정은 나노임프리트 기술을 구현할 수 있다. 에칭 공정은 건식 에칭, 습식 에칭 및/또는 다른 에칭 방법을 포함한다.

그림 17을 계속 참조하면, 3D 커패시터(400)는 제1 전극(412)의 두 측벽 상에 형성된 스페이서(414)를 또한 포함한다. 스페이서(414)는 핀 구조(218)의 각각의 핀(218a, 218b, 218c)을 횡단한다. 스페이서(414)는 적합한 공정에 의해 적합한 두께로 형성된다. 예를 들어, 유전층(예를 들어, 실리콘 산화층)은 3D 커패시터(400) 위에 전반적 증착되고, 그리고 나서, 그림 17에 나타난 바와 같이 실리콘 산화층은 스페이서(414)를 형성하기 위해 실리콘 산화층을 제거하도록 에칭된다. 대안적으로, 스페이서(414)는 실리콘 질화물, 실리콘 산화질화물 또는 이들의 조합과 같은 다른 유전체를 포함한다.

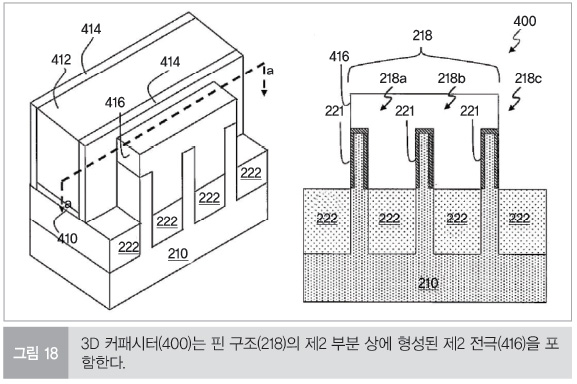

그림 18을 참조하면, 3D 커패시터(400)는 핀 구조(218)의 제2 부분 상에 형성된 제2 전극(416)을 포함한다. 예시된 바와 같이, 핀 구조(218)의 제1 부분(제1 전극(412)을 포함함) 및 제2 부분(제2 전극(416)을 포함함)은 상이하다. 예시된 실시예에서, 제2 부분은 핀들(218a, 218b, 218c)의 일부를 포함한다. 제2 전극(416)은 예를 들어, Al, Cu 및 W와 같은 도전 재료, 다른 적합한 도전 재료, 또는 이들의 조합을 포함한다. 제2 전극(416)은 증착 공정, 리소그래피 패턴화 공정 및 에칭 공정과 같은 임의의 적합한 공정에 의해 형성될 수 있다. 증착 공정은 화학적 기상 증착(chemical vapor deposition; CVD), 물리적 기상 증착(physical vapor deposition; PVD), 원자층 증착(atomic layer deposition; ALD), 고밀도 플라즈마 CVD(high density plasma CVD; HDPCVD), 유기 금속 CVD(metal organic CVD; MOCVD), 원격 플라즈마 CVD(remote plasma CVD; RPCVD), 플라즈마 향상 CVD(plasma enhanced CVD; PECVD), 저압 CVD(low-pressure CVD; LPCVD), 원자층 CVD(atomic layer CVD; ALCVD), 대기압 CVD(atmospheric pressure CVD; APCVD), 도금, 다른 적합한 방법, 또는 이들의 조합을 포함한다. 리소그래피 패턴화 공정은 포토레지스트 코팅(예컨대, 스핀 온 코팅), 소프트 베이킹, 마스크 정렬, 노출, 포스트 노출 베이킹, 포토레지스트 현상, 세정, 건조(예컨대, 하드 베이킹), 다른 적합한 공정 또는 이들의 조합을 포함한다. 대안적으로, 리소그래피 노출 공정은 마스크 없는 포토리소그래피, 전자 빔 기록 및 이온 빔 기록과 같은 다른 방법에 의해 구현되거나 교체된다. 또 다른 대안으로, 리소그래피 패턴화 공정은 나노임프리트 기술을 구현할 수 있다. 에칭 공정은 건식 에칭, 습식 에칭 및/또는 다른 에칭 방법을 포함한다.

그림 18에 도시된 바와 같이, 3D 커패시터(400)는 복수의 핀들(218a, 218b, 218c)을 포함하는 핀 구조(218)를 포함하는 기판(210)을 포함한다. 현재 실시예가 3개의 핀들(218a, 218b, 218c)을 예시하지만, 더 많거나/더 적은 핀들이 고려된다. 핀 구조(218)는 핀 구조(218)의 각 핀(218a, 218b, 218c)의 측벽의 일부 상에저 저항성 표면(221)을 포함한다. 저 저항성 표면(221)은 핀 구조(218)의 탑 부분/층 상에 형성된다. 3D 커패시터(400)는 기판(210) 상의 핀 구조(218)의 각각의 핀(218a, 218b, 218c) 사이의 영역에 배치된 절연 물질(222)을 더 포함한다. 유전층(410)이 저 저항성 표면(221)을 포함하는 핀 구조(218)의 제1 부분 위에 형성된다. 유전층(410)은 핀 구조(218)의 각각의 핀(218a, 218b, 218c)을 횡단한다. 제 1전극(412)이 유전층(410) 위에 형성된다. 제1 전극(412)은 핀 구조(218)의 각각의 핀(218a, 218b, 218c)을 횡단하고 유전층(410)에 의해 핀 구조(218)로부터 분리된다. 스페이서(414)가 핀 구조(218)의 각각의 핀(218a, 218b, 218c)의 일부 상에 그리고 제1 전극(412)의 측벽 상에 형성되고, 이 스페이서(414)는 스페이서(414) 중 하나의 스페이서의 대향면에 형성된 제2 전극(416)으로부터 제1 전극(412)를 분리하는데 기여한다. 제2 전극(416)은 핀 구조(218)의 일부 상에 형성되고 복수의 핀들(218a, 218b, 218c)을 횡단한다. 예시된 실시예에서, 제2 전극(416)은 핀 구조(218)의 복수의 핀들(218a, 218b, 218c)의 저 저항성 표면(221)상에 직접 형성되어, 전류가 저 저항성 표면(221)을 통해 제2 전극(416)과 핀 구조(218) 사이를 지나갈 수 있도록 한다. 제2 전극은 또한 핀 구조(218)의 각각의 핀(218a, 218b, 218c) 사이의 영역에서 절연 물질(222) 상에 형성된다. 제2 전극(416)은 스페이서(414)의 표면과 직접 접촉하는 표면을 포함한다. 제1 전극(412) 및 제2 전극(416)은, 이들이 서로 병렬로 있고 핀 구조(218)의 적어도 하나의 공통 핀(예컨대, 218a, 218b, 218c) 상에 있도록 형성된다. 제1 전극(412) 및 제2 전극(416)은 서로 분리된다.

그림 18의 실시예는 금속 절연막 금속(metal insulator metal; MIM) 커패시터 및 금속 절연막 반도체(metal insulator semiconductor; MIS) 커패시터를 제공한다. 예시된 바와 같이, 스페이서(414)에 의해 분리되는 제1 전극(412) 및 제2 전극(416)은 MIM 커패시터를 제공한다. 게다가, 유전층(410)에 의해 분리되는 핀 구조(218)를 포함하는 제1 전극(412) 및 기판(210)은 MIS 커패시터를 제공한다. 그림 18에서, 3D 커패시터(400)가 오직 3개의 핀만을 포함하는 것으로 예시되었지만, 3D 커패시터(400)는 설계 요건에 따라, 하나 이상의 핀들을 포함할 수 있음을 이해한다. 또한, 예시된 실시예에서, 제1 전극 및 제2 전극이 특정 실시예로 모든 핀들을 공통으로 가졌으나, 제1 전극 및 제2 전극은 설계 요건에 따라 공통으로 오직 일부의 핀만을 갖거나 공통으로 어떤 핀도 갖지 않을 수 있음을 이해한다.

3D 커패시터(200, 400)는 후속 처리에 의해 형성될 수 있는 추가적인 피처들을 포함할 수 있다. 예를 들어, 다양한 콘택/비아/라인 및 다층 상호접속 피처(예컨대, 금속 층, 층간 절연체)가 기판(210) 위에 형성되고, 3D 커패시터(200, 400)의 다양한 피처 또는 구조를 접속하도록 구성될 수 있다. 추가적인 피처들은 3D 커패시터(200, 400)에 전기적 상호접속을 제공할 수 있다. 예를 들어, 다층 상호접속은 종래의 비아 또는 콘택과 같은 수직 상호접속 및 금속 라인과 같은 수평 상호접속을 포함한다. 다양한 상호접속 피처들은 구리, 텅스텐 또는 실리사이드를 포함하는 다양한 도전 물질을 구현할 수 있다. 일례로, 다마신 공정(damascene process) 또는 듀얼 다마신 공정이 구리 관련 다층 상호접속 구조를 형성하는데 이용될 수 있다.

3D 커패시터(200, 400)는, 예를 들어 혼합 신호 애플리케이션에서의 디커플링(decoupling) 커패시턴스 및 고주파수 노이즈 필터, 마이크로프로세서 애플리케이션에서의 디커플링 커패시턴스, 메모리 애플리케이션에서의 저장 보유, 무선 주파수(RF) 애플리케이션에서의 오실레이터, 위상 시프트 네트워크, 바이패스 필터 및 커플링 커패시턴스와 같은, 다양한 기능을 위해 이용될 수 있다. 3D 커패시터(200, 400)는 트랜지스터, 인덕터, 보호막, 본딩 패드 및 패키징과 같은 다른 피처 및 구조를 포함하는 반도체 장치/집적 회로에 포함되지만, 예시된 실시예는 단순함과 명료함을 목적으로 단순화되었음을 이해한다. 따라서 3D 커패시터가 제공된다. 예시적인 3D 커패시터는 복수의 핀을 포함하는 핀 구조를 포함한 기판을 포함한다. 3D 커패시터(400)는 기판(210) 상의 복수의 핀들 각각 사이에 배치된 절연 물질을 더 포함한다. 3D 커패시터는 복수의 핀들 각각에 배치된 유전층을 더 포함한다. 3D 커패시터는 핀 구조의 제1 부분에 배치된 제1 전극을 더 포함한다. 제1 전극은 핀 구조의 표면과 직접 접촉한다. 3D 커패시터는 핀 구조의 제2 부분에 배치된 제2 전극을 더 포함한다. 제2 전극은 유전층 상에 직접 배치되고, 핀 구조의 제1 부분 및 제2 부분은 상이하다.