SMT 컴포넌트들이 기판 상에 실장되기 전에, 기판 패드들은 대응하는 솔더 퇴적(solder deposit)들로 선택적으로 코팅된다. 다음으로, 컴포넌트는 그의 전기적 단자들이 대응하는 기판 패드들과 정렬되도록 기판 위에 주의 깊게 위치되거나 ‘맞춰진다(registered)’. 마지막으로, ‘솔더링(soldering)’으로 알려진 동작에서, 컴포넌트 단자들과 PCB 패드들이 솔더 퇴적들의 응고(solidification)를 통해 전기적으로 및 기계적으로 서로 본딩된다.

자료출처 : 특허청

마이크로 전자 어셈블리, 표면 실장 컴포넌트 및 표면 실장 컴포넌트를 제공하는 방법이 개시된다. 어셈블리는 다음을 포함한다; 실장 표면 상에 배치되고, 강자성 재료를 포함하는 본딩 패드들을 갖는 기판, 그 본딩 패드들 상에 배치된 응고된 솔더; 및 응고된 솔더를 통하여 기판에 본딩된 표면 실장 컴포넌트 - 상기 표면 실장 컴포넌트는, 솔더링 전 및 솔더링 동안 기판 상에 표면 실장 컴포넌트를 유지하기에 충분한 크기의 자기력을 확립하기 위해 본딩 패드들 내의 강자성 재료와 협력하도록 적응된, 상기 표면 실장 컴포넌트의 기판측 상에 배치된 자성 층을 포함한다.

기술 분야

본 발명의 실시예들은 전자 어셈블리들에 관련되고, 더욱 자세하게는, 안티-뒤집힘(anti-flip)/안티-이동(anti-shift)/안티-비석화(anti-tombstoning) 구조들 및 연관된 제작 방법들에 관련된다.

배경 기술

기판 상에 컴포넌트들을 실장하는 종래의 방식들 중 하나는 표면 실장 기술(surface mount technology; SMT)이라고 불린다. SMT 컴포넌트들은 기판의 표면에 직접 솔더링되는 단자들 또는 리드들(일반적으로 ‘전기적 접촉점들’, ‘범프들’ 또는 ‘패드들’이라 불림)을 갖는다. SMT 컴포넌트들은 작은 크기와 실장의 단순성으로 인해 널리 사용된다. 컴포넌트와 기판 사이에 안전한 물리적 및 전기적 접속들을 확립하기 위해 SMT 컴포넌트의 전기적 접촉점들은 기판 표면 상의 전기적으로 도전성인 대응하는 실장 또는 본딩 패드들(‘랜드들’이라고도 불림)에 연결된다. PCB들을 높은 밀도로 제작하기 위해서, 커패시터들, 저항들 및 인덕터들과 같은 소정의 작은 수동 컴포넌트들을 표면 실장하는 것이 알려져 있다. 산출된 전자 시스템은 더 낮은 비용과 더 소형으로 제조될 수 있고, 그리하여 상업적으로 더 매력적일 수 있다.

SMT 컴포넌트들이 기판 상에 실장되기 전에, 기판 패드들은 대응하는 솔더 퇴적(solder deposit)들로 선택적으로 코팅된다. 다음으로, 컴포넌트는 그의 전기적 단자들이 대응하는 기판 패드들과 정렬되도록 기판 위에 주의 깊게 위치되거나 ‘맞춰진다(registered)’. 마지막으로, ‘솔더링(soldering)’으로 알려진 동작에서, 컴포넌트 단자들과 PCB 패드들이 솔더 퇴적들의 응고(solidification)를 통해 전기적으로 및 기계적으로 서로 본딩된다.

솔더링 방법의 하나의 예는 솔더 리플로우를 포함하는데, 솔더 리플로우 공정 동안, 컴포넌트 단자들과 PCB 패드들은 먼저 솔더 퇴적이 녹는 온도로 가열되고, 그 후 이들 조합이 냉각되도록 허용되어 솔더가 응고되고, 그리하여 단자들과 패드들이 적절한 전기적 및 물리적 접속들을 만든다.

.jpg)

그림 1A. DSC가 기판 패드들 중 하나 위로 이동된 종래기술에 따른 DSC와 기판 조합의 평면도이다.

그림 1B. DSC가 비석화된 종래기술에 따른 DSC와 기판 조합의 측입면도이다.

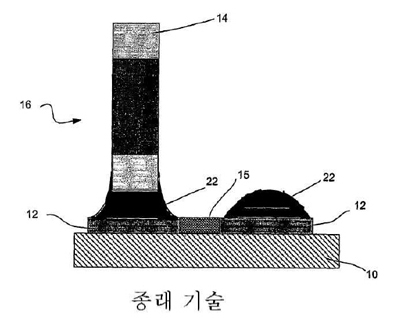

통상적으로, 예를 들면 그림 1A 및 그림 1B에서 보는 것과 같이, 기판(10)은 다이측 커패시터(die side capacitor) 또는 DSC(16)와 같은 SMT 컴포넌트들의 단자들(14)이 실장될 수 있는 패드들(12)의 쌍을 갖는다.

솔더 레지스트(15)가 두 개의 패드(12) 사이에 배치된다. 솔더링 동안 패드들(12) 상의 솔더 퇴적들(22)의 고르지 않은 표면 장력에 기인하는 비대칭적인 측면 표면 장력은 DSC(16)가 그림 1A에서 보는 것과 같이 이동되거나, 그림 1B에서 보는 것과 같이 비석화되게 할 수 있다. 그림 1A는 기판 패드들(12) 중 하나로부터 이동되어 인접한 기판 패드를 덮고 있는 DSC(16)의 상면도를 도시하는 한편, 그림 1B는 비석화된 DSC(16)의 측면도를 도시한다. SMT 컴포넌트들의 뒤집힘(flipping), 이동(shifting) 및 비석화는 본 고에서 SMT 컴포넌트 결함들(SMT component defects) 또는 SMTC 결함들(SMTC defects)이라고 불릴 것이다. 비석화 효과는 SMT 컴포넌트들의 실장에서 흔한 솔더링 결함으로 간주되고, 솔더의 표면 장력, SMT 컴포넌트의 무게 및 솔더링 조건들의 조합에 의해 야기된다. SMTC 결함들에 기여하는 다른 인자는 솔더링 동안 SMT 컴포넌트를 수송하는 컨베이어 벨트의 진동을 포함할 수 있다. 특히 최근에 치수 및 무게가 0805(8mm×5mil) 및 0402로부터 0201로 감소한 DSC에 대하여 SMTC 결함들이 조립 현장들에서 관찰되어 왔다. 0402 및 0201 컴포넌트들의 비교적 작은 치수 및 무게 때문에, 컴포넌트들의 솔더링성(solderability)의 변화 또는 컴포넌트의 각 단부에서 솔더 페이스트가 녹기 시작하는 시간차에 의해 표면 장력의 복잡한 균형이 더욱 쉽게 방해될 수 있다.

솔더 페이스트 인쇄 공정, 솔더 리플로우 공정 및 솔더 페이스트 포뮬레이션(formulation) 중 어느 하나를 조정함으로써, 종래 기술은 실장 공정 동안 야기된 SMTC 결함들을 해소하도록 시도해왔다. 솔더 페이스트 인쇄 공정을 조정하는 것은 통상적으로 솔더 패드들에 대한 인쇄 스텐실들을 재설계하여 리플로우에 대한 솔더 인쇄 파라미터들을 변경하는 것을 수반한다. 한편 리플로우 공정을 조정하는 것은 컴포넌트 단자들 상의 표면 장력들 사이의 원하는 균형을 달성하기 위해 통상적으로 예열 시간 및 담금 시간(soaking time)의 연장을 수반한다.

더욱 느린 예열 비율이 SMTC 결함 비율을 감소시키기 위해 제안되어 왔다. 페이스트 포뮬레이션을 조정하는 것은 더 넓은 응고 범위를 제공하고 작은, 리드 없는(leadless) 컴포넌트의 양 측의 표면 장력들 사이의 균형을 달성하기 위해 SnPbAg을 포함하는 솔더 합금을 사용하는 것을 수반한다. 확장된 응고 범위는 솔더 퇴적들 안의 솔더 페이스트의 매우 끈적끈적하고 반죽같은 단계를 늘이고, 그리하여 컴포넌트의 단자들 상의 표면 장력의 균형을 잡고, 또한 비석화 빈도를 감소시킨다.

SMTC 결함들의 발생을 감소시키기 위해 종래 기술에서 사용된 대안적인 수단은 도시된 바와 같이 실장 전 조합(1)의 솔더링 동안 캐패시터를 적소에 유지하기 위해 접착제를 사용하는 것을 고려한다. 그러한 방법에서, 위에서 기술된 그림 1A 및 그림 1B에 관하여 유사한 컴포넌트들이 비슷한 참조번호들을 사용하여 참조된 그림 2에서 보는 바와 같이, 접착제가 도시된 바의 두 개의 기판 패드(12) 사이의 솔더 레지스트(15) 상에 도포된다. 접착제는 SMTC 결함들을 감소시키려는 시도에서 솔더링 동안 커패시터를 적소에 유지하기 위한 것이다. 그러나 불리하게도, 앞에서 언급된 바와 같이, SMT 컴포넌트 크기가 축소됨에 따라, 접착 방법을 사용하는 것은 특히 접착제의 정확한 배치 및 정확한 도포를 필요로 하고, 이는 작은 공간/분량에 관련될 경우 더욱 어렵게 되고, 따라서 종종 접착제 도포기(dispensing machine)의 미세한 조정을 필요로 한다는 점에서 SMTC 결함들을 극복하는 데 적합하지 않게 된다. 전술한 이유들 때문에, 그리고 본 명세서를 읽고 이해할 때 본 기술분야의 당업자들에게 명확하게 될 후술하는 다른 이유들 때문에, 합리적인 생산 비용으로 상대적으로 높은 밀도 및 높은 품질의 상호 접속들을 제공하는 기판에 컴포넌트들을 실장하는 방법들에 대한 상당한 필요가 본 기술분야에 존재한다.

.jpg)

그림 2. 솔더링 동안 DSC를 적소에 유지하는데 접착제가 사용되고 있는 종래 기술에 따른 DSC와 기판 조합의 측입면도이다.

발명의 상세한 설명

자성층을 포함하는 표면 실장 컴포넌트, 표면 실장 컴포넌트의 형성 방법, 표면 실장 컴포넌트를 포함하는 전자 어셈블리 및 전자 어셈블리를 포함하는 전자 시스템이 본 명세서에 개시된다.

본 기술분야의 당업자들에 의해 본 기술분야의 다른 당업자들에게 작업 내용을 전달하기 위해 공통적으로 채용된 용어들을 사용하여 실시예들의 다양한 양상들이 기술될 것이다. 그러나 본 발명이 기술된 양상들 중 일부만을 이용하여 실시될 수 있다는 것이 본 기술 분야의 당업자들에게 명백할 것이다. 예시적인 실시예들의 철저한 이해를 제공하기 위해 특정한 숫자들, 재료들 및 구성들이 설명을 목적으로 개시된다. 그러나 본 기술 분야의 당업자에게 본 발명이 특정한 세부사항들 없이 실시될 수 있다는 것이 명백할 것이다. 다른 예들에서, 공지의 특징들이 예시적인 실시예들을 모호하게 하지 않기 위해 생략되거나 단순화되었다.

다양한 동작들이 본 발명을 이해하는데 가장 도움이 되도록 다수의 분리된 동작들로서 설명되지만, 설명의 순서가 이러한 동작들이 반드시 순서에 의존함을 암시한다고 해석되어서는 안 된다. 특히, 이러한 동작들은 제시된 순서대로 수행될 필요가 없다.

‘하나의 실시예’라는 표현이 반복적으로 사용된다. 그 표현은 일반적으로 동일한 실시예를 가리키지 않지만, 동일한 실시예를 가리킬 수도 있다. 문맥에서 달리 지시되지 않는다면 ‘포함하는’, ‘갖는’ 및 ‘구비하는’이라는 용어들은 같은 뜻이다.

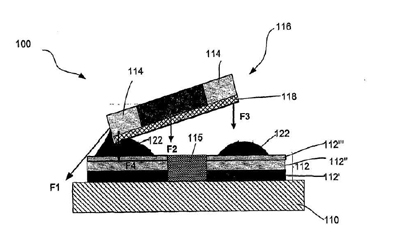

그림 3. 각각 리플로우 전 및 리플로우 동안 일 실시예에 따른 조립 전(pre-assembly) 조합의 측입면도이다.

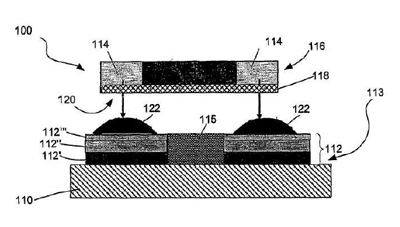

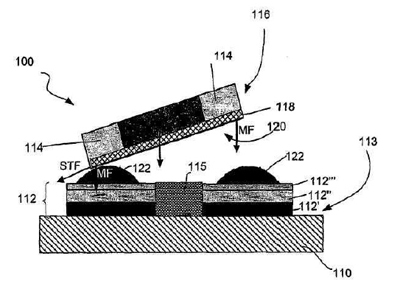

그림 3A 및 그림 3B를 참조하면, 실장 전 조합(100)이 각각 리플로우에 앞서 그리고 리플로우 동안 도시된다. 도시된 바와 같이 조합(100)은 본딩 표면(113) 상에 본딩 패드들(112)을 갖고, 솔더 레지스트(115)를 포함하는 기판(110)을 포함한다. 도시된 본딩 패드들(112)은 ENIG 본딩 패드들을 포함할 수 있다. ENIG 본딩 패드는 본 기술분야의 당업자에게 공지된 방법들을 사용하여 구리 패드들을 제공함으로써 만들어질 수 있다. 그 후 전기 화학적 수단에 의해 특정한 범위의 니켈 두께를 퇴적하기 위해 소정 길이의 시간 동안 구리 본딩 패드들이 적절한 니켈을 포함하는 배스(bath) 안에 넣어질 수 있다. 그 후 적절한 세정 후에, 본딩 패드들은 전체 니켈 표면 영역들이 금으로 덮일 때까지 금 원자들이 자발적으로(spontaneously) 표면의 니켈 원자들을 치환(replace)하는, 금을 포함하는 전기 화학 배스(electrochemical bath)에 넣어질 수 있다.

앞에서의 공정의 결과로 구리층(112´), 그 위의 니켈층(112´´), 및 니켈층을 덮는 금층(112´´´)을 포함하는 본딩 패드들(112)과 같은 본딩 패드들이 만들어진다. 금은 그의 낮은 전기 저항 및 부식성 물질들의 공격에 대한 그의 불활성(inertness) 때문에 접촉면을 위한 금속으로서 전자 산업에서 오랫동안 사용되어 왔다.

도시된 바와 같이 조합(100)은 단자들(114)을 갖는 DSC(116)와 같은 표면 실장 컴포넌트를 더 포함한다. DSC(116)는 다이측 표면(120) 상에 제공된 자성층(118)을 포함한다.

그림 3A에서와 같이, DSC(116)는 단자들(114)이 본딩 패드들(112) 상의 솔더 퇴적들(122)과 맞도록 기판(110) 위에 맞춰지는 공정에 있는 것으로서 도시된다. DSC가 기판 위에 맞춰진 때 리플로우 전에, 자성층(118)과 ENIG 본딩 패드들의 (강자성 성질을 갖는) 니켈층(112´´)이 상호작용하여 DSC(116)와 기판(110) 사이에 자기력 MF를 확립하고, 자기력 MF는 특히 유리하게도 기판 위에 DSC를 유지하여 리플로우 전에 기판 패드들 위에 DSC가 맞춰진 상태로 남아있도록 허용한다.

그림 3B에서와 같이, 조합(100)이 리플로우를 겪을 때, DSC의 각 측면 상의 본딩 패드들(112) 사이의 고르지 않은 표면 장력들 STF가 DSC(116) 상의 토크를 생성할 수 있고 그것은 ENIG 본딩 패드(112)에 존재하는 니켈층(112´´)과 자성층(118) 사이에서 작용하는 자기력들 MF에 의해 야기된 자기 토크에 의해 상쇄될(counteracted) 수 있다. 그러한 상쇄(counteraction)는 그림 1A 및 그림 1B에서 부분적으로 도시된 뒤집힘, 이동 및 비석화와 같은 SMTC 결함들을 실질적으로 방지하는 데 효과적이다. 자성층은 MF가 STF보다 크도록 선택되어, 예를 들면, 0402 또는 0201 DSC에 대해서와 같이, SMTC 결함들을 감소시키기 위해 리플로우 전 및 리플로우 동안 DSC와 아래에 놓인 기판 사이의 유지력을 증가시킬 수 있다.

본 실시예의 기술에서 사용된 바와 같이, ‘유지하다(hold)’ 또는 ‘유지하는(holding)’이 의미하는 것은 리플로우 전에 SMT 컴포넌트가 기판 상에 맞춰진 상태로 남아있고, 리플로우 동안, SMT 컴포넌트가 뒤집히거나 이동되거나 비석화되지 않도록 기판 상에 SMT 컴포넌트를 유지하는 것을 가리킨다는 것을 주의해야 한다.

하나의 실시 예에 따르면, 종래의 인쇄 방법을 사용하는 등의 DSC 제조 동안 자성층(118)은 DSC 상에 배치될 수 있다. 실시예들에 따르면, 두 솔더 퇴적(22)의 고르지 않은 표면 장력 STF(surface tension force)들에 의해 생성된 토크보다 큰 토크를 생성하는 자기력 MF를 제공하는 한편, 동시에 SMT 컴포넌트 상 또는 기판 상의 회로들의 성능에 미치는 영향은 최소화되도록 자성층이 선택된다. 바람직하게는, 리플로우를 겪을 솔더의 리플로우 피크 온도 범위보다 약간 높은 쿠리어 온도(Courier temperature)를 갖는 자성 재료가 선택된다. 예를 들면, 선택된 자성 재료의 쿠리어 온도는 솔더의 리플로우 피크 온도 범위보다 약 10℃ 높은 온도 내지 약 20℃ 높은 온도 사이일 수 있다. 그러한 경우에, 납을 포함하는 솔더가 사용되었을 때, 피크 리플로우 온도(peak reflow temperature) 범위는 약 210℃와 약 220℃ 사이일 수 있고, 그 경우 실시예들의 목적을 위해 수용 가능한 쿠리어 온도 범위는 약 220℃와 약 240℃ 사이일 수 있다. 게다가, 무연 솔더가 사용되었을 때, 피크 리플로우 온도 범위는 약 240℃와 약 250℃ 사이일 수 있고, 그 경우 실시예들의 목적을 위해 수용 가능한 쿠리어 온도 범위는 약 260℃와 약 270℃ 사이일 수 있다. 리플로우 피크 온도 범위 아래의 쿠리어 온도를 갖는 자성 재료는 리플로우 동안 그의 자기적 성질을 실질적으로 잃어버려서 불리하게도 DSC(116)와 같은 SMT 컴포넌트와 아래에 놓인 기판 사이의 상쇄 자기력 MF의 사실상의 소멸을 초래할 수 있다. 더욱 바람직하게는, SMT 컴포넌트 내 또는 기판 내의 회로들의 성능에 미치는 영향을 최소화하도록 적응된 잔류 자기(remanence)를 나타내는 자성 재료가 선택된다. 잔류 자기 및 회로 성능에 대한 그것의 영향에 기초한 자성 재료의 선택은 CPU의 경우에서와 같이, 약 2㎓ 이상의 주파수들과 같은 고 주파수들을 갖는 회로들의 경우에 특히 중요해진다. 한편, 실시예들에 따른 자성 재료는 기판 본딩 패드들 상의 솔더 퇴적들 사이의 같지 않은 표면 장력에 의해 SMT 컴포넌트에 대한 토크를 상쇄하기 위해 필요한 상쇄력(counteracting force)을 역시 제공하는 잔류 자기를 보여준다. 바람직한 실시예에 따른 자성층의 일부로서 사용될 수 있는 자성 재료들의 예들은 니켈 및 페로니켈(ferronickel) 합금들 중 임의의 하나를 포함할 수 있다. 페로니켈 합금들의 경우에, 그들의 혼합물들이 응용 필요에 따라 특정한 잔류 자기를 획득하기 위해 공지의 방식으로 만들어질 수 있다.

실질적으로 SMTC 결함들을 방지하기 위해, 솔더의 토크를 상쇄하기 위해 필요한 자기력 토크에 도달하기 위해서, 예를 들면 SMT 컴포넌트의 단자 치수들을 포함하는 치수들, SMT 컴포넌트의 무게, 게다가 솔더 퇴적들 중 하나로부터의, SMT 컴포넌트에 대한 표면 장력 토크를 고려하는 시뮬레이션과 같은 기법들을 사용하는 것이 본 기술분야의 당업자의 지식 내에 있을 것이다. 그리하여 발견된 자기력 토크에 기초하여, 리플로우 동안 그러한 자기 토크를 생성하도록 자성층이 선택될 수 있다. 일반적으로, 윗 단락에서 제공된 것과 같은 가이드라인들을 사용하여, DSC의 바람직한 평형상태를 실행하기 위해 필요한 최소의 자기력을 제공하는 자성층이 선택될 수 있다. 그러한 자성층은 검토되는 특정한 조합들에 대한 자기 토크 요건들에 기초하여 임의의 패턴을 규정할 수 있고 임의의 두께를 가질 수 있다. 예를 들면, 일 실시예에 따른 자성층은 ENIG 패드들의 니켈층의 두께와 동등한 범위의 두께, 즉 약 1㎛와 약 5㎛ 사이의 두께를 가질 수 있다.

그림 4. 본 발명에 따른 자성층(magnetic layer)의 세 개의 서로 다른 실시예의 평면도이다.

본 명세서에서 사용된 것과 같이, ‘자성층’은 연속적인 자성 재료의 층 및 불연속적인 자성 재료의 층을 가리킨다는 것을 주의해야 한다. 그리하여, 예로서 그림 4A, 그림 4B 및 그림 4C를 참조하면 실시예들에 따른 자성층은 그림 4A의 평면도에서 도시된 것과 같이 연속적인 층 또는 그림 4B 및 그림 4C의 평면도에서 도시된 바와 같이, 패턴을 규정하는 것과 같은 불연속적인 구성을 갖는 층을 포함할 수 있다. 일 실시예에 따르면, 자성층은 SMT 회로들에 대한, 자성층의 자기장으로부터의 영향이 최소화되도록 적응된 패턴을 규정하는 서브층(sublayer)들을 포함할 수 있다. 예를 들면, 그림 4B의 실시예에서 보여지는 바와 같이, 자성층은 기판 패드들의 패턴에 대응하는 평면도의 패턴을 규정하는 서브층들을 포함할 수 있다. 그리하여, 특히 그림 4B에서 보여지는 바와 같이, SMT 단자들이 예를 들면 그림 1A~그림 3B에서 도시된 바와 같이 패턴을 규정하는 경우, 자성층(218)은 각각이 기판 패드들 중 대응하는 패드 위에 놓이도록 구성된 두 개의 서브층(218´ 및 218´´)을 포함할 수 있다. 그림 4C의 실시예에서 예로서 보여진 바와 같이, 자성층(218)은 도시된 바와 같은 패턴 P를 각각 규정하는 서브층들(218´ 및 218´´)을 포함할 수 있다. 그림 4A~그림 4C는 단순히 자성층 구성들의 예들을 도시하는 것이고, 다른 구성들이 본 발명의 실시예들의 범위 내에 있다는 것을 주의해야 한다.

기판 패드들에 대해, 패드들이 ENIG 패드들인 실시예들을 반드시 따를 필요는 없다는 것을 주의해야 한다. 본 발명의 실시예들은 솔더 퇴적들의 같지 않은 표면 장력을 상쇄하기 위한 자기력을 확립하기 위해 전술된 것과 같이 자성층과 협력하도록 적응된 강자성 재료를 포함하는 기판 패드들이기만 하면 ENIG 패드가 아닌 기판 패드들을 그 범위 안에 포함한다.

그림 5A. DSC를 포함하는 표면 실장 컴포넌트의 사시도이다.

그림 5B. 기판 위에 표면 실장된 그림 5A의 DSC의 측입면도이다.

예

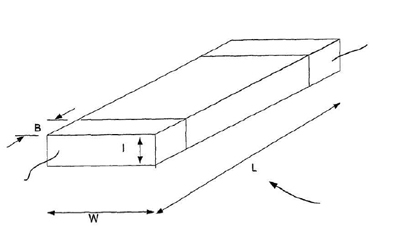

실시예들에 따른 적합한 자성층의 선택에 대해서, 그림 5A 및 그림 5B의 예시를 특히 참조하여 0402 DSC에 대한 예로서 다음의 계산들이 제공된다. 그리하여 일 실시예에 따르면, DSC(116)는 0402 DSC일 수 있고, 이 경우 그것의 치수들 및 특성들은 다음과 같다.

.jpg)

Eutectic SN63Pb37을 솔더로서 사용하면, 표면 장력은 (2)가 될 것이다. 결국, DSC의 단자측 상의 표면 장력은 (3)가 될 것이고, 표면 장력 토크는 (4)가 될 것이다. 한편, 중력 토크는 (5)가 될 것이다. 위에서 보여진 바와 같이, T1>>T2이면 DSC의 비석화가 야기될 수 있다. 막의 자기력이 캐패시터의 무게의 10배라고 가정하면, (6)이고, 자기 토크는 (7) 및 (8)이 될 것이다. 그리하여 DSC 상의 시계 반대 방향 총 토크는 (9)인 한편, DSC 상의 시계방향 총 토크는 (10)이다. (11)이므로, DSC는 비석화되지 않을 것이다.

유리하게도, 본 발명의 실시예들은 리플로우 전 및 리플로우 동안 기판 위에 SMT 컴포넌트들을 유지하기 위해서, 단순하고, 비용 효율이 높고, 효과적인 구성을 제공한다. 특히, 솔더 페이스트 포뮬레이션들을 만들고 검사하는 것 및 관련된 인쇄 및 리플로우 공정들에 의해, SMTC 결점들을 최소화하는 종래 방법들과 비교했을 때, 본 발명의 실시예들은, 리플로우 전 및 리플로우 동안 기판 위에 SMT 컴포넌트를 유지하기 위해 예를 들면 기판 상의 ENIG 패드의 니켈 층의 자연적인 강자성 성질들에 대한 것과 같은 기판 패드들의 강자성 성질들을 이용한다. 게다가, 유리하게도, 본 발명의 실시예들에 따르면, SMT 컴포넌트와 기판 사이의 고정력 및 유지력은 SMT 컴포넌트 상의 자성층의 자기장의 함수이고, 그것의 SMT 컴포넌트로의 제공은 위에서 언급된 바와 같은 SMTC 결함들을 최소화시키는 전통적인 방법들과 비교했을 때, 그리고 다른 SCAM 공정 파라미터들과 비교했을 때 제어하기에 더 쉬울 것이다. 게다가, 유리하게도, 본 발명의 실시예들은 SMT 컴포넌트들의 크기가 변함에 따라 재료들 또는 공정들을 분리하여 개발할 필요 없이 SMTC 결함들을 최소화하는 일반적인 방법을 제공한다.

이상은 0805 DSC로부터 훨씬 작은 0201 DSC로의 천이와 같은, SMT 컴포넌트들을 둘러싸고 있는 소형화 경향의 관점에서 더욱 더 유리하다. 부가적으로, 그리고 DSC에 대해서 특히, DSC의 주요 기능이 로직/저장소와는 대조적으로 DSC와 관련된 디바이스의 파워링 온(powering on)과 파워링 오프(powering off) 동안의 안정된 전압 제공이라는 점에서 실시예들에 따라 DSC 상에 자성층을 제공하는 것은 DSC의 기능에 실질적으로 영향을 미치지 않아 유리할 것이다. 부가적으로, SMTC를 기판 상에 실장하기 위해 사용된 실장/어셈블리 장비를 변경할 필요 없이 실시예들에 따르면 위의 모든 유리한 점들이 가능하다. 위의 유리한 점들은 안정되고 높은 커패시터 부착 수율을 허용하고 실질적으로 실장 장비에 영향을 미치지 않고 솔더링에 대한 공정 윈도우(process window)를 향상시킨다.

.jpg)

그림 6. 일 실시예에 따른 마이크로 전자 어셈블리의 측입면도이다.

다음으로 그림 6를 참조하면, 본 발명에 따른 마이크로 전자 어셈블리의 실시예가 어셈블리(200)로서 도시된다. 그림 6에서 도시된 바와 같이, 어셈블리(200)는 리플로우 및 후속의 DSC(116)의 기판(110)에 대한 부착 후의 그림 3A 및 그림 3B의 조합(100)을 나타낸다. 그림 6에서 보는 바와 같이, 어셈블리(200)는 응고된 솔더(123)를 통해 기판(110)의 ENIG 패드들(112)에 부착되거나 본딩된, 즉 전기적으로 및 기계적으로 본딩된 DSC(116)를 도시한다. DSC(116)는 그 위에 배치된 자성층(118)을 포함하고, 그것은 전술된 바와 같이, 리플로우 전 및 리플로우 동안 기판 위에 DSC를 고정시킨다.

.jpg)

그림 7. 일 실시예에 따른 그림 6의 어셈블리와 같은 마이크로 전자 어셈블리를 포함하는 시스템의 개략적인 표현이다.

그림 7을 참조하면, 본 발명의 실시예들이 사용될 수 있는 다수의 가능한 시스템(90) 중 하나가 예시된다. 마이크로 전자 어셈블리(1000)는 그림 6에서 위에서 도시된 마이크로 전자 어셈블리(200)와 각각 유사할 수 있다.

일 실시에에서, 전자 어셈블리(1000)는 마이크로프로세서를 포함할 수 있다. 대안적인 실시예에서, 전자 어셈블리(1000)는 ASIC(application specific IC)를 포함할 수 있다. 칩셋들(예를 들면 그래픽, 사운드 및 제어 칩셋들)에서 존재하는 집적 회로들은 본 발명의 실시예들에 따라 패키징될 수도 있다.

그림 7에서 도시된 실시예에 대해서, 도시된 바와 같이, 시스템(90)은 메인 메모리(1002), 그래픽 프로세서(1004), 대용량 저장 디바이스(1006) 또는 버스(1010)를 통하여 서로 연결된 입력/출력 모듈(1008)을 포함할 수도 있다. 메모리(1002)의 예들은 SRAM(static random access memory) 및 DRAM(dynamic random access memory)를 포함하지만 거기에 한정되지 않는다. 대용량 저장 디바이스(1006)의 예들은 하드 디스크 드라이브, CD(compact disk drive), DVD(digital versatile disk drive) 등을 포함하지만 거기에 한정되지 않는다. 입력/출력 모듈(1008)의 예들은 키보드, 커서 제어 장치. 디스플레이, 네트워크 인터페이스 등을 포함하지만 거기에 한정되지 않는다. 버스(1010)의 예들은 PCI(peripheral control interface) 버스, 및 ISA(Industry Standard Architecture) 버스 등을 포함하지만 거기에 한정되지 않는다. 다양한 실시예에서, 시스템(90)은 무선 이동 전화기, 개인 휴대 정보 단말기(personal digital assistant), 포켓 PC, 태블릿 PC, 데스크톱 컴퓨터, 셋톱박스, 미디어센터 PC(media-center PC), DVD 플레이어 및 서버일 수 있다.

바람직한 실시예를 기술하기 위해서 본 명세서에 특정한 실시예들이 예시되고 기술되었지만, 동일한 목적을 달성하기 위해 계산된 광범위하고 다양한 대안적인 구현 또는 동등한 구현들이 본 발명의 범위를 벗어나지 않고서 도시되고 기술된 특정한 실시예를 대체할 수 있다는 것이 본 기술 분야의 당업자들에 의해 이해될 것이다.

본 기술 분야의 당업자들은 본 발명이 매우 광범위하고 다양한 실시예들에서 구현될 수 있다는 것을 쉽게 이해할 것이다. 본 출원은 본 명세서에서 논의된 실시예들의 임의의 개작물 또는 변형물을 포괄하도록 의도된다. 그리하여, 본 발명이 청구범위들 및 그것의 동등물들에 의해서만 한정된다는 것이 명백히 의도된다.