하부 패키지에서 먼저 고장 나와

패드 크레터링은 잠재적인 안정성 문제

PoP는 One-pass 및 Two-pass 어셈블리 프로세스를 사용하여 조립할 수 있다. One-pass 기술에서, 프로세서는 먼저 보드에 마운팅되고 메모리는 프로세서에 마운트되며 그런 후에 최종 보드는 싱글 패스로 리플로우 오븐을 통과한다. Two-pass 기술에는 프로세서 위에 메모리가 최초로 마운트되는 중간 공정이 들어가 있다. 그런 다음에 이러한 두 개의 부품이 캐리어 트레이에 놓이고, 리플로우된다. 이들 결합 디바이스는 회로 보드 상에 장착되고 완성 보드는 두 번째로 리플로우된다. 본 연구에서는 이들 기술 기반의 PoP 신뢰성을 평가해 보았다.

.

초록

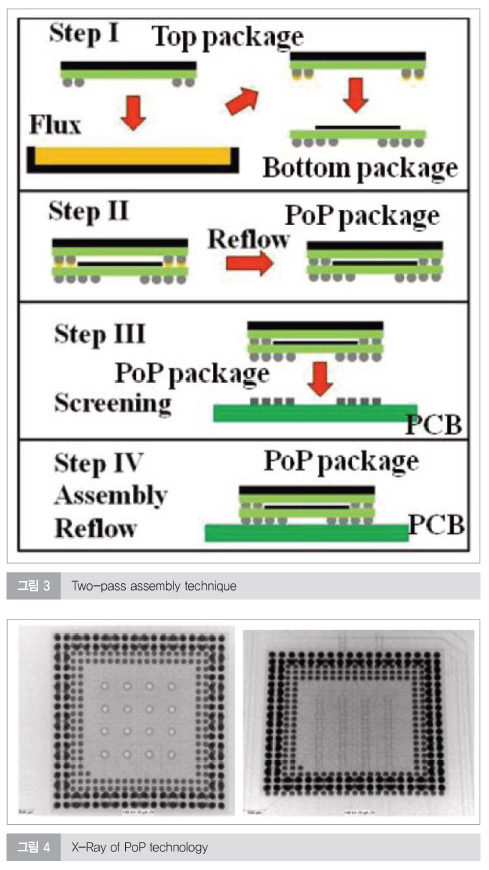

PoP(Package on Packages) 패키지는 메모리 밀도화가 필요한 고성능의 애플리케이션에서 주로 사용되고 있다. PoP 기술의 큰 이점 중 하나는 하부의 프로세서 칩에서 개별 패키지 메모리 칩까지 연결하는 고속 메모리 라인을 라우팅하는 비싸고 도전적인 작업을 제거할 수 있다는 것이다. 대신, 프로세서 상단에 메모리가 있으며, 어셈블리 중에 연결이 자동으로 이루어진다. 이러한 이유로 PoP 테크놀로지는 휴대전화 및 기타 모바일 애플리케이션에서 광범위하게 수용되기 시작했다. PoP는 One-pass 및 Two-pass 어셈블리 프로세스를 사용하여 조립할 수 있다. One-pass 기술에서, 프로세서는 먼저 보드에 마운팅되고 메모리는 프로세서에 마운트되며 그런 후에 최종 보드는 싱글 패스로 리플로우 오븐을 통과한다. Two-pass 기술에는 프로세서 위에 메모리가 최초로 마운트되는 중간 공정이 들어가 있다. 그런 다음에 이러한 두 개의 부품이 캐리어 트레이에 놓이고, 리플로우된다. 이들 결합 디바이스는 회로 보드 상에 장착되고 완성 보드는 두 번째로 리플로우된다.

Two-pass 기술은 비파괴 테스트 방법(예: X-Ray)을 사용하여 최종 어셈블리 전에 PoP의 결함을 확인할 수 있으므로 더 높은 수율을 기대할 수 있다는 확실한 이점이 있다. 본 연구에서는 하부 BGA와 상부 BGA에 각각 SAC105 및 SAC125 솔더를 이용해 동일한 테스트 보드에 8개의 PoP 패키지를 어셈블리하였다. One-pass 기법과 Two-pass 기법을 사용하여 각각 두 개의 테스트 보드를 어셈블리하였다. 사용된 조립 방법이 기계적 피로 내구성에 영향을 미치는지 확인하기 위해 이들 테스트 보드를 기계적 비틀림 하중 평가를 수행했다. 그런 다음에 불량 위치를 결정하기 위한 고장 분석 작업을 뒤따라 수행했다. Time-to-failure 데이터는 Weibull 2-매개변수 분포로 그래프화하였고, ANOVA 분석을 적용했다. 두 가지 다른 기술을 사용하여 조립된 패키지의 신뢰성에서 통계적으로 유의미한 차이가 발견되지 않았다.

서문

PoP(Package on package) 기술에는 더 나은 밀도가 가능하도록 두 개 이상의 패키지를 수직으로 쌓는 공정이 포함되어 있다. PoP 패키지는 일반적으로 적층형 메모리 칩 혹은 통합 메모리와 로직 칩으로 구성된다. 메모리 칩은 일반적으로 로직 칩과 비교할 때 더 적은 I/O를 필요로 한다. 이러한 이유로 표준 구성에는 하부에 저 피치(고밀도)의 프로세서가, 상부에 고 피치(저밀도)의 메모리 칩(적층형 혹은 다른 유형)이 사용된다. BGA 패키지는 높은 I/O 밀도와 신뢰성 때문에 일반적으로 PoP 애플리케이션에 이용된다. 기존 PoP 패키지의 개략도가 그림 1에 나와 있다.

PoP 기술의 확실한 이점 중 일부는 보드 공간의 효율적인 활용, 프로세서와 메모리 칩 사이의 라우팅 및 전송 시간 단축, 낮은 노이즈의 전기적 성능 향상을 꼽을 수 있다.[1] 그리고 이는 CSP와 달리 메모리와 로직 칩을 개별적으로 테스트한 다음 어셈블리할 수 있기 때문에 ‘정상적인’ 패키지만을 선택해서 사용할 수 있다는 것을 의미한다. PoP 기술은 휴대전화 및 모바일 컴퓨팅 시장에서 빠르게 받아들여지고 있다.[4]

PoP는 One-Pass와 Two-Pass의 두 가지 기법을 사용하여 어셈블리할 수 있다. One-Pass 기술은 인쇄 배선 어셈블리(PWA)를 스크린프린팅한 후 하부 BGA 패키지를 놓는다. 그런 다음 상부 BGA 패키지를 디핑하고 하부 BGA 패키지에 올린다. 그 후 싱글 리플로우를 사용하여 패키지를 어셈블리한다. 이 프로세스의 개략도는 그림 2에 나와 있다. 이 방법은 메모리와 로직 칩을 독립적으로 사용할 수 있고 더 많은 물류 유연성을 제공한다는 장점이 있다.[5]

Two-Pass 기술에는 상부 패키지를 플럭스에 디핑하고, 캐리어 트레이의 하부 패키지에 적층하는 작업이 포함되어 있다. 이 단계에서 패키지는 상부와 하부 패키지 사이의 솔더 연결을 만들기 위해 한 번 리플로우된다. 그 다음 PWA를 스크린프린팅하고 적층된 패키지를 패키지에 놓은 다음에 보드와 패키지 사이에 솔더 인터커넥트를 만들기 위한 두 번째 리플로우 프로세스가 이어진다. 이 프로세스의 개략도는 그림 3에 나와 있다.

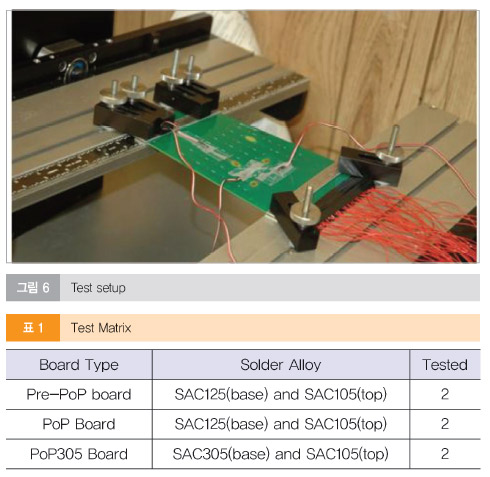

이 기술을 사용하면 패키지를 적층한 후 X-Ray와 같은 비파괴 테스트 방법을 사용하여 또 다른 품질 관리 검사를 도입할 수 있다. X-Ray를 사용한 비파괴 테스트의 예가 그림 4에 나와 있다. PWA에서 최종 어셈블리되기 전에 상단 및 하단 BGA 사이의 상호 연결 결함을 스크리닝할 수 있기 때문에 더 나은 보드 수율을 보장한다.[6]

JEDEC에 의해 설명된 바와 같이, 하부 패키지[7],[8]와 상부 패키지 핀아웃 구성에 패키지 아웃라인 도면을 개략적으로 그려서 패키지 표준화하였다. 그러나 신뢰성 관점에서 주로 낙하 테스트[9] 관련 문헌을 활용했고, 일부 연구에서는 열 신뢰성을 다뤘다.[2],[6],[11],[12],[13]. 또한, 리플로우 도중 warpage를 특정하였다.[14],[15],[16],[17]. 그러나 휴대전화와 모바일 컴퓨팅 업종의 PWA에서는 진동, 굽힘 및 비틀림과 같은 다른 유형의 기계적 부하와 종종 마주한다. 게다가, 두 가지 다른 기술을 사용하여 조립할 때 PoP 기술의 신뢰성 성능을 비교할 수 있는 문헌은 쉽게 찾기 어렵다.

기계적 비틀림 테스트에서는 횡방향 인접 하중이 2단계 상호연결의 전단 하중을 초래하는 곳의 PWA 하중 실험을 포함했다. 기계적 비틀림과 관련해 참고한 문헌은 PBGA(Plastic Ball Grid Array) 내의 보이드 신뢰성 평가[18], 무연 솔더 평가[19], 구리 표면 마감재 비교[20], 리볼링 및 솔더 페이스트 체적이 신뢰성에 미치는 영향 평가[21]였다. 비틀림 테스트는 또한 노트북용 회로보드[22]와 휴대전화[23]용에서 일반적으로 경험하는 부하를 시뮬레이션하는 데 사용하였다. 현재 MDS 또는 비틀림 기반 테스트를 위한 표준화 테스트 절차는 없다.

본 연구에서는 기계적 비틀림 하중 하에서 PoP 기술의 보드 수준 신뢰성에 대해 탐구했다. 사용된 어셈블리 기술의 영향과 신뢰성에 미치는 영향에 대해서 논의한다. 또한, 하부 패키지와 관련해 솔더 페이스트 선택의 영향을 조사했다. 또한, 불량 부위 및 불량 발생 메커니즘을 확인 및 결정하기 위해 불량 샘플에 대해 통계 분석을 수행했다. 불량 부위 분포에 대한 평가를 수행하여 성능 및 특성 불량 어셈블리 기술에 따라 어떻게 달라지는지 확인했다. 다음 섹션에는 테스트 보드에 대한 세부 정보가 포함되어 있다. 다음은 테스트 설정에 대한 설명하였고, 그런 다음 관련 오류 분석과 함께 결과를 보고하였다. 마지막으로 연구의 결론을 제시했다.

테스트 보드

본 연구에 사용된 테스트 보드는 8″ × 4.5″ × 62mils 사이즈의 제품이었다. PWA 카드는 OSP 보드 마감 처리된 Polyclad 370HR 보드 라미네이트를 사용하여 제작되었다. 8개의 PoP 패키지가 1/4의 보드 대칭으로 2개의 클러스터로 조립되었다. 12×12mm의 패키지 치수는 0.21mm의 패키지 라미네이트로 선택되었다. 구성의 상부 패키지는 18×18 볼 매트릭스에 128개의 패드가 있는 0.65mm 피치(peripheral)의 BGA 패키지로 구성되었다. 하부 패키지는 23×23 볼 매트릭스에 0.5mm 피치(peripheral)와 305개의 패드가 있는 BGA 패키지를 사용했다. 외부 클러스터의 패키지를 응력 Level I이라고 하고 내부 클러스터를 응력 Level Ⅱ라고 한다. 응력 Level Ⅱ에서 관찰된 변형률은 응력 Level I보다 약간 더 높으므로 응력 Level I에 실장된 부품이 응력 Level Ⅱ의 부품보다 오래 지속될 것으로 예상할 수 있다. 응력 Level이 표시된 테스트 보드는 그림 5에 나와 있다.

사용된 PoP 부품에는 테스트 중에 지속적인 저항 모니터링을 허용하는 3개의 데이지체인 네트가 있다. 상부 패키지의 가장자리에 있는 12개 솔더 볼은 첫 번째 데이지체인을 형성했고, 상부 패키지의 나머지 솔더 볼은 두 번째 데이지체인을 형성했다. 상부 패키지에는 두 개의 데이지체인이 사용되었고 하부 패키지의 솔더 볼에는 단일 데이지체인이 사용되었다. 이는 패키지에서 첫 번째 실패를 경험하기 위해 솔더 볼의 네트를 식별하기 위해 수행되었다.

앞서 언급한 2개의 어셈블리 기술을 사용하여 테스트 보드를 어셈블리했다. 상부 BGA 패키지를 어셈블리하는데 사용된 솔더 페이스트는 SAC105(98.5%Sn + 1.0%Ag + 0.5Cu)였다. 이는 상부 패키지가 낙하 하중에 민감하고 문헌에서 SAC105가 다른 높은 비중의 은(Ag) 솔더 타입과 비교했을 때 더 나은 충격 내구성을 갖는다고 강력히 시사하기 때문에 선택하였다. 하부 패키지는 더 많은 피로 하중을 받을 것이라고 예상되므로 하부 BGA 패키지는 SAC125(98.3%Sn + 1.2%Ag + 0.5%Cu) 또는 SAC305(96.5%Sn + 3.0%Ag + 0.5%Cu)를 사용하여 어셈블리하였다.

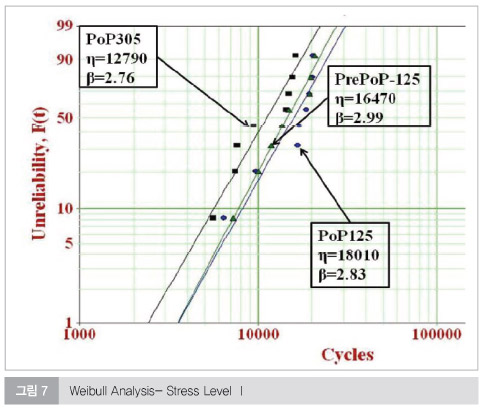

테스트 매트릭스에는 상부 및 하부 패키지에 SAC105 및 SAC125 솔더 페이스트 조합을 사용하여 One-pass 어셈블리 기술 및 Two-pass 기술을 사용하여 조립된 테스트 보드로 구성되었다(2개의 테스트 보드의 샘플 공간 포함). 또한 2개의 테스트 보드는 One-pass 방법을 사용하여 조립되었지만, 하부 패키지를 조립에는 SAC305 솔더 페이스트를 사용했다.

본 연구에서 One-pass로 어셈블리된 패키지는 ‘PoPxxx’라고 하고 Two-pass로 어셈블리된 패키지는 ‘PrePoPxxx’라고 했다. 여기서 xxx는 하부 패키지의 솔더 구성을 설명하는 데 사용된다. 예를 들어, PrePoP125는 상부 패키지에 SAC105 솔더, 하부 패키지에 SAC125 솔더가 사용된 Two-pass 어셈블리 패키지를 말하며, PoP305는 상부 패키지에 SAC105, 하부에 SAC305 솔더 페이스트가 적용된 One-pass 어셈블리 패키지를 의미한다.

테스트 설정

테스트 설정에는 정적 플랫폼과 회전식 플랫폼을 사용하여 PWA의 비틀림 하중 테스트를 도입하였다. 회전식 플랫폼은 각 변위, 각 속도 및 각 가속도를 피드백하는 기능을 통해 회전 변위를 제어했다. PWA의 두께도 고려되었으며 회전축이 PWA의 중심을 통과하도록 변경하였다. 이를 통해 피크-대-피크 보드 변형 및 평균 변형 속도를 제어할 수 있다. 1°/s의 각속도(angular velocity) 및 1°/s2의 각가속도(angular acceleration)에서 반복하중의 변형각(angular deflection) 4.5°를 선정하였다. 이것은 대략 50μstrain 단위/초의 평균 변형률 속도에서 1000μstrain 단위의 보드 전단 변형률로 해석된다. 테스트 설정에서 수행된 예비 유한 요소 분석 작업은 이전 작업[24]에서 설명되었다. 그러나 유효한 결과를 위해 테스트 변수는 동일한 응력 수준 내에서만 비교하였다. 또한, 본 연구에 사용된 실패 기준은 IPC-9701[25]을 기반으로 했다. 5회 연속 사이클 동안 공칭 저항이 20% 증가하면 고장으로 규정하였다. 또한, 패키지 구성의 특성을 고려하면 메모리 또는 로직 I/O의 오류와 상관없이 패키지의 기능은 영향을 받는다. 따라서 본 연구에서는 3개의 네트 중 어느 하나에서 첫 번째 불량이 나오면 모두 불량으로 규정하였다.

모든 테스트 보드는 100% 고장이 날 때까지 순환시켰다. 응력 Level I과 응력 Level Ⅱ에서 PoP 부품에 인접한 각 보드에 두 개의 스트레인 게이지를 붙여넣었다. 이는 변형 하중을 비교하고 향후 유한 요소 분석 작업(FEA)을 위한 참조 목적으로 수행하였다.

결과

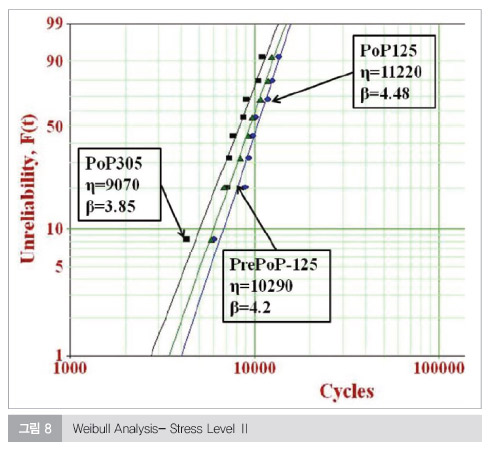

모든 데이지체인 네트의 저항을 모니터링하고 고장 데이터에 대한 주기를 확인했다. 그런 다음 Weibull 2 파라미터 분포를 가정하여 고장 데이터를 도표화하였다. 패키지의 배치(응력 Level)에 따라 데이터를 그룹화했다.

응력 Level I에서의 테스트 결과는 그림 7에 나와 있다. 테스트 결과에 대해 ANOVA 분석을 수행했으며 One-pass와 Two-pass 기술 간 통계적으로 유의미한 차이가 관찰되지 않았다. 또한, 하부 패키지용 SAC125 및 SAC305 솔더 페이스트로 조립된 PoP 부품 사이에서 성능 차이가 관찰되지 않았다. 이는 패키지 적층으로 인한 강성 증가로 인해 하부 패키지의 솔더 변형이 늘어났음을 의미한다. 유한 요소 분석(FEA)을 사용하여 확인할 수 있다. 그림 8에서 볼 수 있듯이 응력 Level Ⅱ에서도 일관된 모습이 나왔다.

또 다른 흥미로운 점은 패키지의 모든 첫 번째 오류가 하부 패키지의 데이지체인 네트에서 관찰되었다는 것이다. 이는 솔더 스트레인이 하부 패키지의 솔더 조인트에서 최대임을 나타낸다.

불량 분석

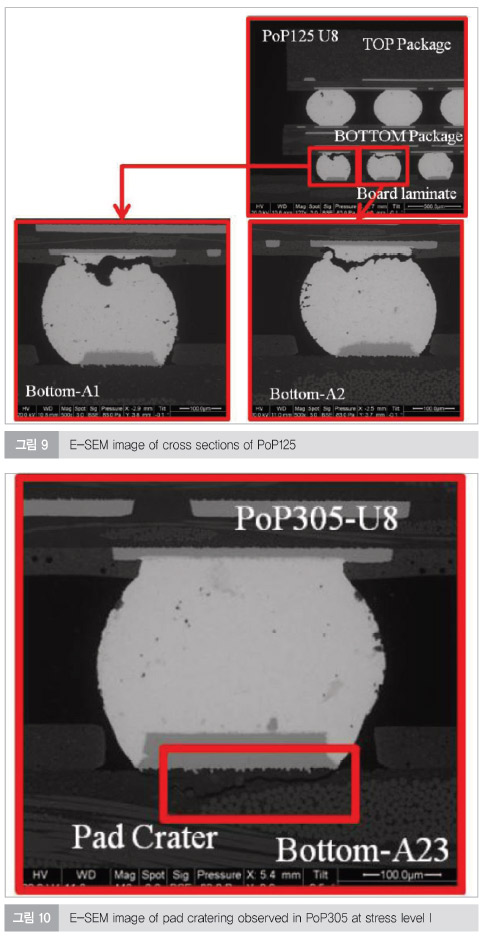

저항 모니터링에서는 첫 번째 오류가 하부 패키지에 있음을 보여주었다. 파손 부위를 결정하고 테스트 보드를 비교하기 위해 파괴적 파손 분석을 수행했다. 그림 9에서는 응력 Level I에서 PoP125 부품의 E-SEM 이미지를 보여주고 있다.

테스트 보드는 18200 사이클 동안 테스트되었으며 그림 10에 표시된 패키지는 6399 사이클에서 불량이 나왔다. 모든 인터커넥트 오류는 하부 패키지의 두 번째 레벨 인터커넥트에서 관찰되었다. 크랙은 패키지 솔더 인터페이스에 있었다. 또한, 패드 크레터링(pad cratering)의 여러 사례가 관찰되었다. 응력 Level I의 PoP305 패키지에서도 유사한 모습이 관찰되었다. E-SEM에서 관찰된 패드 분화구의 예가 그림 10에 나와 있다. PrePoP-125 패키지에서도 비슷했다.

패드 크레터링은 구리 패드와 트레이스 하부의 얇은 레진 내의 크랙으로 정의된다.[26] 문헌에서는 일반적으로 관찰되는 균열 메커니즘을 응집파괴와 접착파괴 두 가지 범주로 분류하고 있다.

레진 부위만을 따라 발생하는 파단을 응집파괴라고 하며, 레진과 유리섬유 번들 사이의 파단을 접착파괴라고 한다. 본 연구에서 패드 크레터링의 모든 사례는 응집파괴였다. 패드 크레터링 자체는 솔더 조인트의 전기적 결함이나 패키지의 기능 손실을 의미하지 않는다. 그러나 레진의 크랙으로 인해 PWA의 연결 트레이스에 오류가 발생하여 전기적 open이 발생할 수 있다. 그러나 트레이스가 절단되지 않았거나 패드가 작동하지 않은 경우에도 기본 라미네이트의 크랙은 신뢰성 문제의 원인이다.[27] 이러한 문제를 완화하는 기술로 언더필 사용이 제안되고 있다.[28]

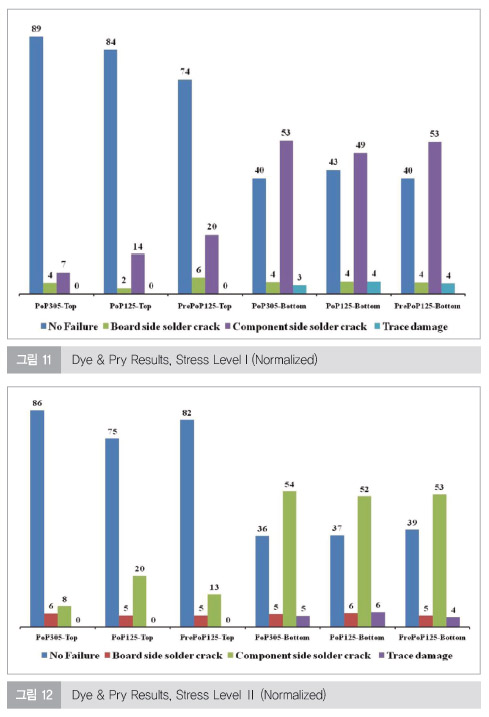

그러나 연구의 목적은 어셈블리 기술의 선택이 PoP 어셈블리의 신뢰성에 영향을 미치는지 비교하는 것이다. 따라서 불량 사이트 분포를 이해하고 어셈블리 기술과 솔더 선택을 비교하기 위해 부품의 Dye & Pry 분석(염료 침투 탐상 분석)을 수행하고, 다양한 불량 사이트 분포를 비교했다. 그 다음에 쉽게 비교할 수 있도록 각 불량 사이트의 인스턴스 수에 대한 문서화와 정규화를 이어서 했다. 이 연구의 결과는 그림 11과 그림 12에 나와 있다. 어셈블리 기술의 변화에 따라 통계적으로 유의미한 분포 변화가 발생하지 않는다는 점을 확인할 수 있었다. 또한, 솔더 페이스트의 변화도 불량 사이트에 영향을 미치지 않았다. 3개 네트의 첫 번째 불량에 대해 부품이 테스트되었으므로, 불량이 없는 PoP 어셈블리의 상부 패키지에 있는 볼의 숫자는 높은 편이다. 우리는 또한 중간 라미네이트에서 패드 크레터링 또는 트레이스 실패의 인스턴스를 관찰하지 않고 대신 PWA만 관찰했다. 부품-솔더의 인터페이스는 모든 샘플에서 관찰되는 가장 일반적인 불량 사이트이다.

결론

PoP 기술에 대한 다양한 어셈블리 기술을 비교하기 위해 기계적 비틀림 하중을 사용했으며 통계적으로 유의미한 차이는 관찰되지 않았다. 하부 패키지가 PoP 어셈블리에서 항상 먼저 불량이 되는 것으로 나타났다. PoP 기술의 경우, 기계적 비틀림을 받는 하부 패키지의 솔더 인터커넥트에 늘어난 Ag 함량이 내구성 측면에서 유의미한 차이가 관찰되지 않았다. PoP용 솔더 타입 혹은 어셈블리 기술 사이에서 불량 분포 경향의 차이도 관찰되지 않았다. 패드 크레터링은 잠재적인 안정성 문제로 확인되었다. 응력을 균일하게 재분배하고 추적 오류를 방지하려면 언더필을 사용하는 것이 좋다.