다양한 검증 테스트 실시

3D IC 구현에 중요한 데이터

본고에서는 다양한 3D 집적기술들을 리뷰했고, 3D IC의 주요 집적 과제를 설명하고, 3D IC 프로세스 준비를 검증하기 위해 다양한 광학 및 전기 테스트 구조를 제작해 이야기 하였다. 신뢰할 수 있는 레이어-투-레이어 정렬 정확성이 절실히 필요하다; 정렬 및 오버레이 측정에 대한 여러 기술들이 존재하고 있다. 3D IC에 있어서 가장 적극적인 정렬 허용오차(0.18㎛)는 투명한 기판, 고-품질 산화 퓨전 본딩 그리고 bow 보정 방법을 구현함으로써 이뤄질 수 있다. 더욱이 웨이퍼를 통과하는 정렬 프로세스 개선이 필요하다.

3D IC 테크놀로지 검증 테스트

디바이스 레이어 간 비아 형성 검증 테스트 구조

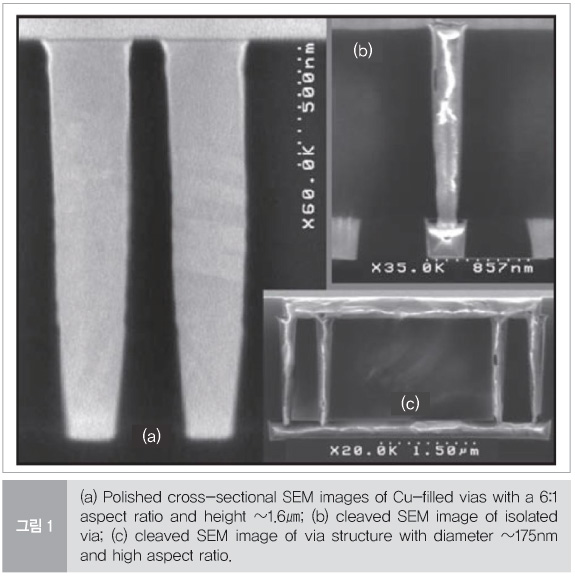

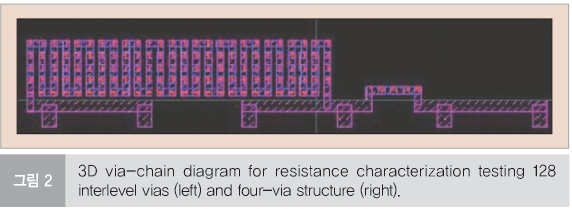

그림 1에서는 저항 측정을 위한 3D 비아-체인 구조의 예를 보여주고 있다. 비아 체인은 상부와 하부 웨이퍼의 첫 번째 금속 레벨 사이를 왕복하고 있다. 모든 테스트 패드는 상부 웨이퍼에 위치해 두었다. 4개 포인트의 저항을 측정하기 위해 비아 체인의 각 끝부분에 2개의 패드를 두었다. 이러한 간단한 테스트 구조는 사전 제작된 회로도와 호환되는 재료 및 프로세스를 사용한 접합 레이어 간에 낮은 기생 연결이 만들어졌는지의 여부를 보여줄 수 있다. 그림 2에서 보여주는 바와 같이, 싱글-다마신 프로세스는 상부와 하부 웨이퍼를 안정적으로 연결하는 서브미크론, Cu-충진 비아 등과 같은 제작에 사용될 수 있다.

본딩 검증 테스트 구조

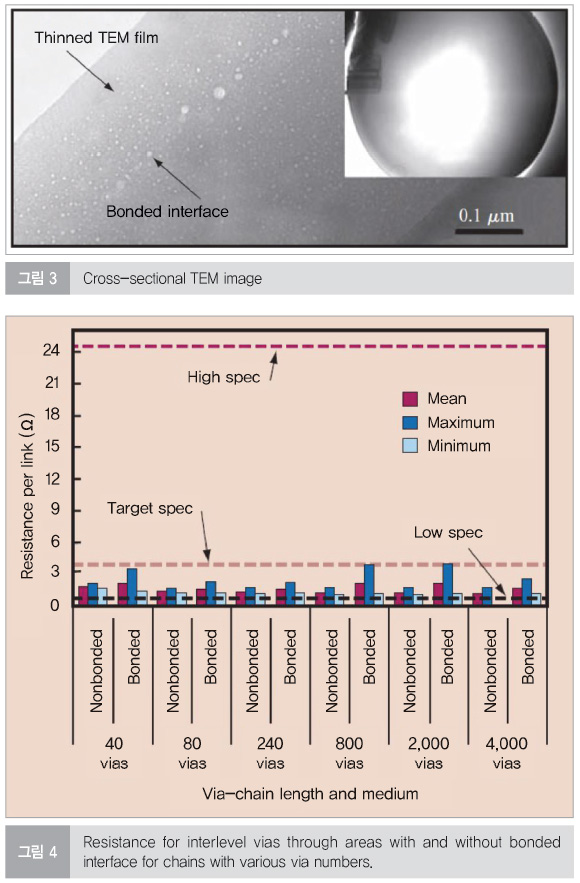

접합 강도 측정은 접합된 계면의 품질을 측정하기 위한 훌륭한 첫 번째 pass 방법이지만, 디바이스 신뢰성 관점에서 보면 충분하지 않다. 예를 들면, 그림 3의 산화물용융접합 계면(the oxide fusion-bonded interface)의 TEM 기반 측정에서는 2%의 기공 보이드 밀도가 존재하지만, 이는 ~2.2J/㎡의 높은 본드 강도를 양산한다.

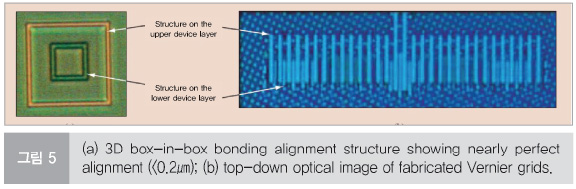

더 월등한 산화물용융접합 계면을 측정하기 위해, IBM에서는 약한 계면으로부터 초래되는 누설에 민감한 서브미르론 비아로 형성된 비아 체인 테스트 구조를 활용하였다. 그림 4에서 보여준 것 같은 비교는 다양한 너비의 레벨 간 비아 체인의 저항, 접합 계면을 갖거나 그러지 않은 패턴-관통 산화물을 평가하고 있다. 이를 통해 접합 계면을 통해 패턴화된 레벨 간 비아의 저항이 해당 종횡비율을 지닌 Cu 비아가 예상된 범위(<4 Ω per link) 내에 있음을 보여주고 있다.

본딩 정렬 정확도 검증 테스트 구조

광학적 및 전기적으로 3D 레이어를 정렬하고 동시에 그에 따른 오버레이의 오류를 측정할 수 있는 몇 가지 테크놀로지가 발전해 왔다. 2가지의 광학 정렬 테스트 구조는 그림 5의 (a)와 (b)에서 보여주고 있다. 이들 구조는 자동 혹은 수동 본딩 정렬 그리고 그에 따른 오버레이의 측정에 사용될 수 있다. 그림 5의 (a)에서는 표준 박스 속에 박스가 들어가 있는 구조의 이미지를 보여주고 있다. 그러나 3D IC 애플리케이션의 경우, 외측 박스는 상부 디바이스 레이어에서 생긴 것이고, 내측 박스는 하부 디바이스 레이어에서 생긴 것이다. 디자인을 통해, 더 작은 박스의 중앙은 더 큰 박스의 엣지로부터 13.0㎛ 떨어져 있어야만 한다. 따라서 2개의 박스 간의 서로 다른 거리를 간단하게 측정하여, X 및 Y 방향 모두의 정렬 정확도는 결정될 수 있다.

광학 정렬 테스트 구조의 또 다른 예인 버니어 타입 구조(Vernier-type structure)는 그림 5의 (b)에서 보여주고 있는데, 하부와 상부 웨이퍼의 금속 레벨 간 정렬이 측정되었다. 버니어 패턴은 X축과 Y축 방향 모두에 배치하여 0,18㎛ 낟알 모양에서 미스 정렬을 해결하기 위한 구조로 생성하였다. 웨이퍼의 한 특정 지점에서 X축과 Y축 방향 모두에서 거의 완벽한 <0.18㎛ 정렬을 볼 수 있었다. 이는 200mm 직경 웨이퍼의 잘 알려진 정렬 정밀도보다 훨씬 더 나은 결과였다. 그러나 반드시 고려해야 할 한 가지는 전체 웨이퍼에 걸친 정렬이 저하되고, 광학 측정에 의한 에어리어의 65%만이 <2.5㎛ 정렬 정밀도 내에서 요구된다는 점이다.

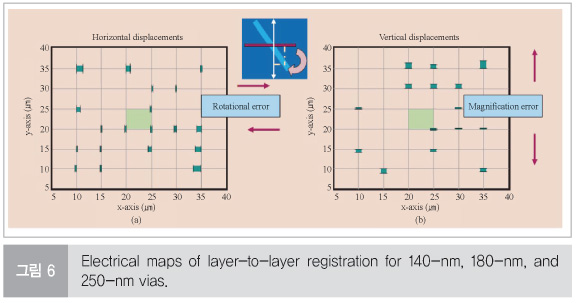

광학 테스트 구조 외에도, 3D 적층 회로에 있어서 본딩 정렬을 전기적으로 측정하기 위해 레지스터 체인 구조도 디자인하였다. 체인은 금속 체인 사이에서 poly-Si 레지스터를 지닌 하부 웨이퍼에서 제조되었다. 층간 비아를 이용하여, 하부 체인에서부터 중심부의 터미널은 상부 웨이퍼 트랙에 금속 다릿발로 연결하여 전압 분배 회로를 생성하였다.

웨이퍼에 대한 이러한 측정은 층간 위치맞춤(layer-to-layer registration)의 전기적 지도를 생성할 수 있다. 본딩에서 미스-정렬이 존재한다면, 층간 비아는 하부 웨이퍼의 예정되어 있던 금속 다릿발과 연결이 되지 않고, 잃어버리고, 다른 것과 연결될 것이다.

이 설계에서, 전압 판독에서의 불일치는 미스-정렬, 금속 체인 피치의 사이즈 그리고 웨이퍼간 비아 치수에 따라 다르다. 동일한 방법은 금속 체인(금속 체인 방법) 사이에서 추가된 poly-Si 저항 없이 패턴에 사용될 수도 있다. 그림 6에서는 140nm, 180nm 그리고 250nm 하부 임계치수의 비아 사이즈를 가지고 테스트한 정렬 측정의 전형적인 테스트 결과를 보여주고 있다. 결과는 매우 만족스러웠다. 웨이퍼 전체에 테스트된 모든 체인에서 요구하고 있는 0.5~2.5㎛ 정렬 오차 범주를 충족하였기 때문이다. 이들 대부분은 <1㎛을 나타냈다. 비아 체인 소자를 활용하는 많은 다른 테스트 구조가 정렬 평가를 위해 디자인될 수 있다.

회로 전력/열관리 테스트 구조 검증

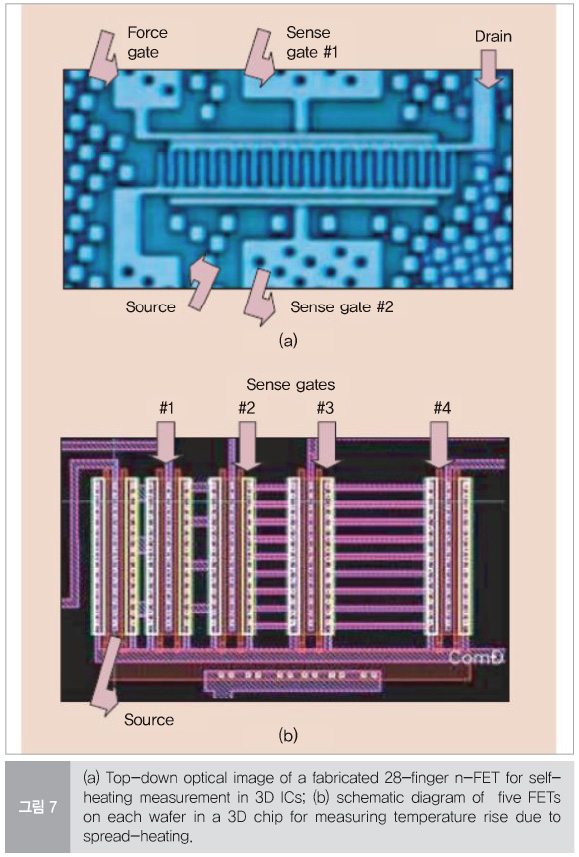

3D IC 내의 열 문제는 적층 다층 레이어의 전력 밀도와 열 저항이 증가함에 따라 심각해지기 시작했다. 3D vs 2D IC의 열적 측면을 측정하기 위해, subthreshold slope와 poly-Si 저항 측정 방식이 자가 및 확산 발열을 측정하기 위해서 3D 매크로에 이용되었다. 테스트에서는 단일 트랜지스터 내의 자가 발열을 정량화하는 것과 2-핑거(two-finger) 트랜지스터에서 공유된 Si 분리를 통한 확산 가열을 포함시켰다(그림 7 참조).

대부분의 연구가 디바이스 자체 발열에 초점을 두고 있는 반면, 우리는 확산 발열에 관심을 가졌다. 이는 수평 그리고 수직 방향에서 근처에 있는 디바이스의 전력 분산에 의한 트랜지스터의 온도 상승으로 규정하였다. 그림 7의 (a)에서는 4개 지점 저항 측정을 위해 중앙 핑거에 연결되어 있는 28-finger n-FET를 보여주고 있다. 나머지 finger는 하나의 게이트 단자로 트랜지스터를 구동하도록 연결되었다. 트랜지스터는 상부 혹은 하부 웨이퍼 내의 자체 발열 측정을 위해 3D 내에 설계되었다. 이 셀은 온도 상승이 ac와 dc 작동 모드 양쪽에서 온도 상승이 측정될 수 있도록 연결되어 있다. 이들 테스트 구조는 성공적으로 제조되어 왔으나, 최종 분석은 연구당시 완성되지 않았었다.

ANSYS 시뮬레이션 작업은 절연된 전기 ON 트랜지스터 주위의 얕은 트렌치 소자분리(STI, shallow-trench isolation)에서 온도가 매우 빠르게 떨어지는 것을 제안했다; 0.13㎛ SOI CMOS 기술에서 0.5㎛ 내로 80%. 따라서 그림 7의 (b)에서 보는 바와 같이 2개의 웨이퍼 3D 칩 내 각각의 웨이퍼에 다른 하나로부터 5개의 트랜지스터를 0.2㎛, 0.5㎛, 1㎛ 그리고 2.98㎛로 분리했다. 상호배선 레이어를 지닌 STI와 3D Box를 통해서 확산 발열 효과를 특성화하는 것을 목표로 하였다. 상부 및 하부 웨이퍼로부터 트랜지스터는 각 트랜지스터가 자체 소스 단자를 가지고 있으며, 모든 트랜지스터가 공통적으로 쇼트된 드레인과 게이트 단자를 공유하고 있는 방식으로 연결되었다. 실험이 진행되는 동안, 공통 드레인과 게이트 단자는 Vdd에 연결되어야만 한다. 그런 후 트랜지스터의 소스 단자에 Vdd를 적용하면 트랜지스터가 OFF로 바뀌고, 반면 소스 단자에 GND를 적용하면 ON으로 변한다. 그래서 하나는 트랜지스터의 ON/OFF 상태를 선택적으로 조절할 수 있다. ON 트랜지스터는 발열 생성을 위해 사용될 수 있는 반면, OFF 트랜지스터는 subthreshold slope로부터의 확산-발열에 의한 온도 상승 측정에 이용될 수 있다. 이들 구조에 대한 측정의 분석은 2006년 말에 마무리되었다.

회로 성능 무결성 검증 테스트 구조

디바이스 및 회로도의 전기적 무결성은 3D IC 제조 프로세스 동안 보존되어야만 한다. 한 가지 중요한 이슈는 3D IC 제조 동안 레이어 전이 프로세스에 의해 야기된 열 사이클링 및 기계적 응력의 효과이다. 다른 이슈는 적층 및 상호배선 다층 디바이스 레이어에 대한 정밀한 정렬과 낮은 기생 연결 요구와 관계가 있다. 최적의 회로 이점을 얻으려면, 정렬과 상호연결 치수는 중요 레이어에 일치되어야만 하고, 레이어 전이 프로세스는 3D 구조의 성능을 저하시키지 않는다. IBM 성능-무결성 테스트 구조에는 링 오실레이터(ring oscillator, RO), 싱글 트랜지스터(FET) 그리고 인버터 회로를 포함하고 있다. 레이어 전이가 요구되는 프로세스가 대상인 고성능 SOI FET와 RO 회로의 전기적 무결성 연구에 대한 체계적인 연구를 수행했다.

첫 번째 테스트 단계에서, 각 웨이퍼는 여러 단계의 레이어 전이 프로세스를 거쳤으며, 상호배선 프로세스 없이 다른 디바이스 레이어로 이송된 상부 디바이스 레이어의 각 단계 이후에 전기 테스트는 웨이퍼 당 25개 칩에서 수행되었다. 다른 측정 중에서, 다음과 같은 3 단계에서 특정 웨이퍼의 중앙 데이터를 조사하였다: a) 표준 CMOS 제조 이후, b) 글라스에 프로세스 된 웨이퍼를 접착하기 위해 요구되는 압력과 온도가 실제로 접착을 완료하지 않은 상태에서 부가적인 ‘모의 실험(simulated)’ 적층 프로세스 이후, c) 글라스에 완전히 부착한 이후, 두 번째 본딩 단계가 필요한 열 프로세싱을 시연하기 위한 어널링과 글라스 제거/접착제 제거. 장-채널(5-㎛) n-FET의 선형 드레인 전류인 Idlin 및 선형 임계 전압인 Vtlin은 두드러지게 바뀌지 않았고, 이는 이들 프로세스가 채널 이동성에 영향을 미치지 않는다는 것을 보여주는 것이다. 단-채널(65-nm) 디바이스는 Idlin와 Vtlin에서 약간의 저하를 보였으며, 소형 디바이스가 저항 변화에 더욱 민감하기 때문에 라인 저항의 증가가 나타났다고 여긴다.

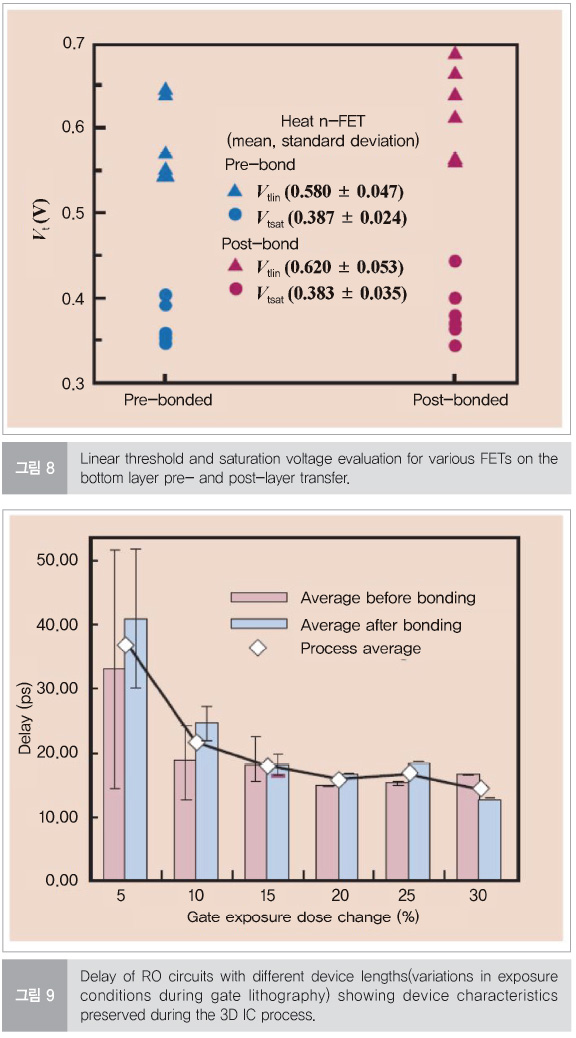

프로세스가 상부 회로의 저항 특성을 보존하는데 최적화시키기 위해, 레이어 전이 프로세스 이후 기능적인 상부와 하부 디바이스 레이어를 지닌 3D IC 회로를 형성할 수 있도록 특수 마스크가 디자인되었다. 우선, Vtlin와 포환 전압인 Vtsat는 2개 레이어로 적층된 IC의 바닥 레이어에 다양한 FET에 대해 측정하였다. 그림 8에서는 레이어 전이와 상호배선 프로세스 전후 동일한 로트로부터 웨이퍼에 동일한 6개 위치에 대한 Vt 플롯을 보여주고 있다. 데이터는 통계적 차이 안에서, 3D IC 레이어 전이 프로세스에 의한 어떠한 저하도 감지되지 않았다. 59개 혹은 41개 링 스테이지의 RO, 13-단계 분배기 그리고 5-단계 출력 버퍼가 디자인되고 제조되었다.

3D RO와 인버터를 지닌 7개의 매크로가 있다. 3D RO 레이아웃의 변화는 상부 혹은 하부 웨이퍼 상의 n-MOS 혹은 p-MOS 트랜지스터의 배치와 관계가 있다.

41-단계 RO는 웨이퍼 간 비아를 위한 거대한 landing zone의 사용으로 2㎛의 본딩 미스 배치를 가능하게 한다. 59-단계 RO는 엄격한 본딩 정렬(~0.5㎛)이 필요하다. 또한, 게이트의 패터닝 동안 프로세스 조건은 다양한 너비의 RO 디바이스 생성이 가능하도록 조정되었다. 그림 9에서 보여주고 있듯이, 리소그래피 노출은 게이트의 너비에 영향을 미치고 그래서 RO 딜레이가 변한다. 상부 선량은 더 많은 프로세스 변수를 산출하는 반면, 하부 선량은 더 우수한 프로세스 컨트롤을 제공하는 것을 보여주고 있다. 전반적으로, 하부 레이어 상의 RO의 성능은 레이어 전이 프로세스에 의한 영향을 받지 않는 것처럼 보인다.

결론

본고에서는 다양한 3D 집적기술들을 리뷰했고, 3D IC의 주요 집적 과제를 설명하고, 3D IC 프로세스 준비를 검증하기 위해 다양한 광학 및 전기 테스트 구조를 제작해 이야기 하였다. 신뢰할 수 있는 레이어-투-레이어 정렬 정확성이 절실히 필요하다; 정렬 및 오버레이 측정에 대한 여러 기술들이 존재하고 있다. 3D IC에 있어서 가장 적극적인 정렬 허용오차(0.18㎛)는 투명한 기판, 고-품질 산화 퓨전 본딩 그리고 bow 보정 방법을 구현함으로써 이뤄질 수 있다. 더욱이 웨이퍼를 통과하는 정렬 프로세스 개선이 필요하다.

우리는 3D IC에서 레이어 간 고밀도 접촉에 적합한 소형, 고-종횡비 비아의 제조와 관련된 이슈들을 설명했다. 0.13-㎛ MOSFET와 링 오실레이터 회로를 이용하여, BEOL CMOS 프로세스 기술이 동박-충진, 고-종횡비(>8:1) 트렌치 제조에 사용될 수 있다는 것을 보여주었다. 이 수준은 웨이퍼-투-웨이퍼 배선으로 가장 작은 비아를 생성할 수 있는 성능을 제공한다. 비아 배선과 계면 본딩의 신뢰성 테스트를 위한 전기 구조를 리뷰하였다. 3D IC에서의 자체 및 확산-방열 효과를 특성화하기 위한 테스트 구조도 역시 설명하였다. 고성능 CMOS 디바이스의 진정한 웨이퍼-레벨 3D 집적의 실현을 향한 중요한 발걸음이 되었다.