전자기기의 경박단소화, 충진 기술 발전의 원동력

IC-서브스트레이트 상의 적층 기술 연구 활발

본 고에서는 전해 구리도금 공정에 의해 구현된 마이크로비아 충진 및 쓰루홀 충진의 실제 상태를 제시하였다. 오늘날 전해 구리 공정에 의해 충진될 수 있는 마이크로비아 및 쓰루홀의 치수를 표시하였다. 또한 구리 충진 기술과 페이스트 플러깅을 비교하고 구리 충진 기술의 이점을 설명했다. 마이크로비아 충진 및 쓰루홀 충진 측면에서 향후 개발 범위를 다뤘다. 패널-레벨-패키징(PLP)과 같은 차세대 기술 부문과 새로운 전해 구리 도금 공정으로 실현된 IC 기판의 구리 필러 도금도 고려하였다.

요약

전자기기는 소형화, 고속화, 스마트화를 향한 진화를 거듭하고 있으며, 전자산업계에서는 이를 구현하기 위한 기술들을 진일보시키고 있다. 이러한 지속적인 발전 환경으로 인해 지난 수십 년 동안 여러 애플리케이션에서 적용 가능한 다양한 전해 구리 공정 기술들이 개발되었다.

지난 몇 년 동안 새로운 ‘충진’ 특성의 전해 구리 공정 도입을 본격화시키는 확실한 4가지 주요 동력이 있다.

첫 번째 요인은 전자기기의 지속적인 소형화이다. 최초의 블라인드 마이크로비아는 1980년대 후반과 1990년대 초반의 HDI 기술로 소개되었다. 1996년에 IC-기판 업종에서 마이크로 비아를 충진하기 시작했다. 공간을 줄이거나 ‘via in Pad’ 구조를 생성하기 위해 마이크로 비아를 적층하는 ‘플러깅’ 기술이 도입되었다. 전도성 페이스트를 사용하는 ‘플러깅’ 기술은 공정 스텝 추가가 필요하기에 많이 비용이 요구된다. 오늘날 구리 충진 마이크로 비아는 거의 모든 HDI PCB 제조업체의 표준이 되었다.

두 번째 동력은 기판의 열 관리이다. 전자기기의 수명 동안 발생하는 발화점(hot spots)을 최소화하기 위해서 한 면에서 다른 곳으로 기판의 열을 방출하도록 관리하는 높은 열 전도도 특성을 통합하는 솔루션이 필요해 졌다.

칩 성능이 우수할수록 국부적인 열점(heat-spots) 발생 현상이 많아지는 경향이 있어서 초기에 전자기기가 손상되기도 했다. 이러한 현상의 주된 이유는 국부적인 발화점에서의 다양한 재질들의 변성(變性) 때문이다.

한편, 완전한 구리 충진 쓰루홀은 2006년에 브리지 도금 또는 X-도금 기술로 실현되었다. 오늘날의 완벽한 구리 충진 쓰루홀 기판은 최첨단 PCB 제조 기술 중 하나이다. 구리가 도금되어있음에도 불구하고 최상위 수준의 열전도도를 가지고 있기 때문이다.

세 번째 동력은 신호 주파수와 관계가 있다. 전자 패키지 또는 PCB 내부의 전자 신호는 해마다 늘어나고 있으며, 이러한 확대는 지금도 계속 이어지고 있다. 적층형 마이크로 비아 및 팬 아웃 비아는 고주파에서 레지스턴스를 생성한다. 이 때문에 고주파 신호 전송이 점점 더 불리해지고 있다. 따라서, 고주파 애플리케이션의 적용 확대는 구리 충진 쓰루홀과 같은 기술에 대한 요구를 더욱 높이고 있다.

쓰루홀 충진의 4번째 동력은 특히, 품질 수율 측면이다. 전기도금 구리 충진 쓰루홀 기술을 대체하려면, 많은 공정 스텝들이 추가되거나 혹은 플러깅 페이스트와 같은 새로운 재료가 필요하다. 이러한 프로세스 스텝 추가 또는 신규 재료는 각각 다양한 리스크와 제조 문제를 일으켜 수율을 낮춘다. 따라서 PCB에 새로운 재료를 적용하지 않고 구리를 이용하여 쓰루홀을 충진하는 ‘원스텝’ 솔루션이 선호되고 있다. 본고에서는 PCB 상의 구리 충진 쓰루홀, 마이크로비아 및 기타 구리 도금 구조의 개발 이유와 치수 로드맵을 설명한다. 본고에는 오늘날의 마이크로비아의 대량 생산제조와 구리 전기도금을 이용한 쓰루홀 충진에 사용되는 도금 쓰루홀의 종횡비, 치수 및 결과를 포함하고 있다. 아울러, IC-서브스트레이트 상의 구리 필러 도금과 같은 첨단 애플리케이션을 위한 새로운 전기 도금 구조의 타당성 연구도 보여줄 것이다.

서문

전자 산업계는 더 작고, 더 빠르고, 더 스마트하고, 더 효율적인 전자 디바이스를 향해 발전을 거듭하고 있다. 지속적으로 진화하는 이러한 환경은 지난 수십 년 동안 여러 애플리케이션에 적합한 다양한 전해 구리 공정(electrolytic copper process)의 개발을 촉진하기에 충분했다. 지난 몇 년 동안 새로운 ‘충진’ 특성의 전해 구리 공정 도입을 본격화시키는 4가지 주요 동력이 있다.

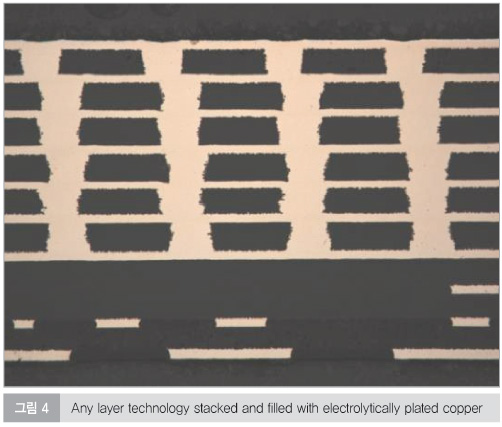

첫 번째 동력은 전자 디바이스의 지속적인 소형화이다. 최초의 블라인드 마이크로비아(blind microvias)는 1980년대 후반과 1990년대 초반에 소개되었다. 현장에서는 1996년에 마이크로비아를 충진하기 시작했다. 마이크로비아를 적층하여 공간을 줄이거나 혹은 ‘패드 내 비아’ 구조를 만들기 위해 ‘플러깅’ 기술이 소개되었다. 전도성 페이스트를 사용한 이 ‘플러깅’ 기술은 추가적인 공정 스텝이 필요하기에 투입되는 비용이 매우 높다. 또한 이 기술은 ‘blow out’, ‘outgasing’, ‘smear’ 그리고 기타 품질 문제와 같은 몇 가지 단점에 직면해 있다. 이러한 종류의 소형화 이점을 달성하기 위해 업계에서는 첨단 솔루션으로 플러그형 마이크로비아보다 완전히 구리로 충진되는 블라인드 마이크로비아를 선호하고 있다. 오늘날 구리 충진 마이크로비아는 거의 모든 HDI PCB 제조업체의 표준이 되었다.

두 번째 동력은 기판 상의 열 관리이다. ‘전자 부품의 전력 및 패키징 밀도가 증가함에 따라 좁은 공간에서 발생하는 폐열의 양도 심하게 늘어난다. 이로 인해 위험할 정도로 높은 온도가 발생하여 전자 디바이스의 고장 요인이 증가한다. 오늘날 전자부품 고장의 55%는 온도 상승으로만 발생한다’[1]는 보고서의 내용을 검토할 가치가 있다.

전자 디바이스 수명 동안 핫스팟을 최소화하기 위해 기판의 열을 한 면에서 다른 면으로 전달하는 관리가 가능한 높은 열 전도율 기능의 솔루션이 필요해 졌다. 고성능 칩은 국부적인 핫스팟을 생성하여 재료 성능 저하와 조기 고장의 원인이 되고 있다. 고성능 전자 디바이스에 열 비아(thermal vias)를 통합시키면, 핫스팟의 발생을 최소화할 수 있다는 점 때문에 업계에서 자체 활용도가 더욱 확대되기 시작했다. 초창기 열 비아는 표준 컨포멀 비아에 불과했으나 열 전도율은 충분하지 않았다. 이후 표준 쓰루홀의 열 전도율을 높이기 위해 플러깅 페이스트가 소개되었다. 그러나 이 경우, 플러깅 기술의 단점과 유사한 현상이 나타났다.

한편, 완전한 구리 충진 쓰루홀은 2006년에 처음으로 브리지 도금 또는 X-도금 기술에 의해 실현되었다. 오늘날, 완전한 구리 충진 쓰루홀 구조는 열 비아 구조에 있어서 최첨단 기술군에 속한다. 구리가 최고의 열전도율 중 하나임에도 불구하고 도금되어야 하기 때문이다.

세 번째 동력은 신호 주파수와 관계가 깊다. 전자 패키지 또는 PCB 내부의 전자 신호 주파수는 시간이 지남에 따라 늘어나고 있으며, 이러한 증가세는 더욱 가속화되고 있다. 팬-아웃 비아 구조에서는 고주파 신호 전송이 점점 더 어려워지기 시작했다. 고주파에서 저항을 생성한다는 점 때문이다. 따라서 고주파 애플리케이션의 확산에 따라 구리 충진 쓰루홀과 같은 기술 요구가 늘어날 것이다. 현재의 5G 인프라에서는 스마트폰 분야에서 이미 구리 충진 쓰루홀 기술을 적용하고 있다.

쓰루홀 충진의 4번째 동력은 품질 수율 측면에서 찾을 수 있다. 전기도금 구리 충진 쓰루홀을 대체하는 공정에는 많은 공정 스텝들이 추가되어야 하거나 혹은 플러깅 페이스트와 같은 새로운 재료가 필요하다. 이러한 공정 스텝 추가 또는 신규 재료 적용은 각각 다양한 위험과 제조 문제를 일으켜 수율을 낮출 소지가 있다. 따라서 PCB에 새로운 재료를 적용하지 않고 쓰루홀에 구리를 충진하는 ‘원-스텝’ 솔루션이 선호되는 솔루션이다.

본고에서는 구리 충진 쓰루홀, 마이크로비아의 개선사항과 치수 로드맵을 설명하고, PCB 상의 다른 구리 도금 구조의 측면을 보여준다. 또한, 전기도금된 구리의 마이크로비아와 쓰루홀 충진을 위해 오늘날 대량생산제조에 사용되고 있는 도금 쓰루홀의 종횡비, 치수 및 결과를 논의할 것이다. 더불어, IC-서브스트레이트 상의 구리 필러 도금과 같은 향후 애플리케이션을 겨냥한 새로운 전기 도금 구조의 타당성 연구도 보여줄 것이다.

구리 적용 마이크로비아 충진

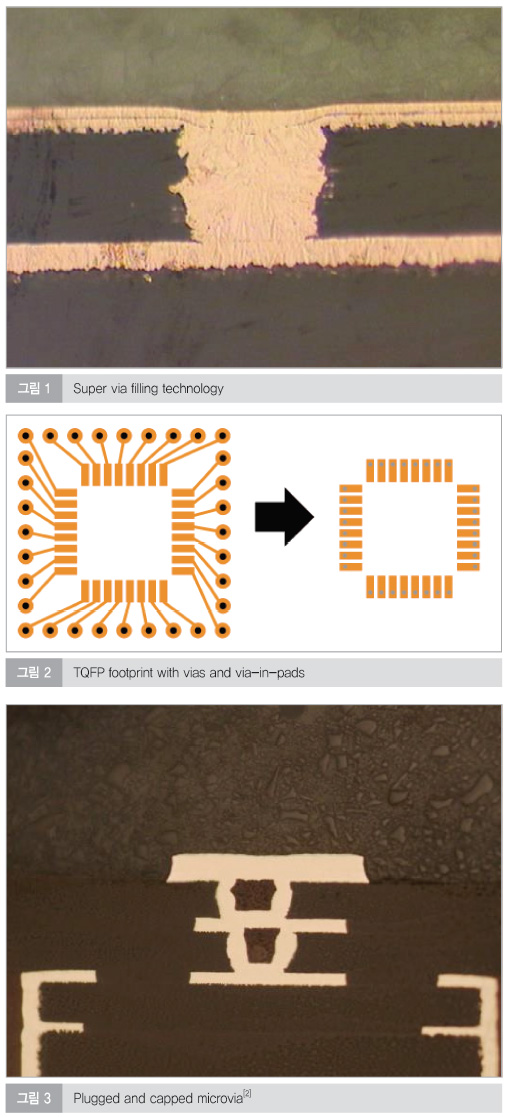

구리를 이용한 마이크로비아 충진 기술은 PCB HDI 생산현장에서 20여년 전에 이미 ‘표준’으로 정립되었다. 표면 상에 매우 얇은 두께로 구리를 도금한 수퍼 비아 충진 테크놀로지가 도입되었다(그림 1 참조).

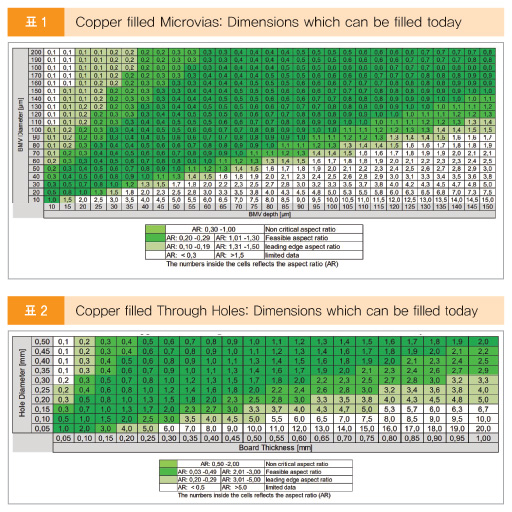

한편 마이크로비아의 구리 충진은 페이스트 프린팅 및 구리로 전체를 도금하여 구현된 플러깅 및 캡핑과 같은 다른 많은 충진 테크놀로지를 대체했다(그림 3 참조). 플러깅/캡핑과 구리 충진 마이크로비아 양쪽 기술은 모두 소위 ‘Via-in-Pad’로 불리는 구조를 가능하게 한다. 이러한 구조는 PCB 설계자에게 상당히 큰 도움을 준다.

게다가, 구리 충진 마이크로비아는 플러깅 기술에 비해 상당한 이점이 있다. 마이크로비아 내부의 재료가 구리라는 장점이 있지만, 다른 재료는 가스를 배출하거나 혹은 다른 CTE 값을 나타낼 잠재성을 가지고 있다.

또한, 구리 충진 마이크로비아의 보이드는 제어가 잘되지 않는 기존의 플러깅 기술에 비해 훨씬 덜하다.

구리 충진 마이크로비아의 개발과 도입은 그림 4에서 보여준 소위 ‘any layer HDI’ 테크놀로지를 도입할 수 있는 문을 열어주었다. Any layer HDI 테크놀로지는 구리 충진 마이크로비아를 적층함으로써 구리 충진 쓰루홀을 가능하게 한다. 이러한 종류의 특징을 통해 HDI 보드 설계자는 구리 충진 마이크로비아만을 사용하여 전체 PCB에 복잡한 신호 경로를 생성할 수 있다.

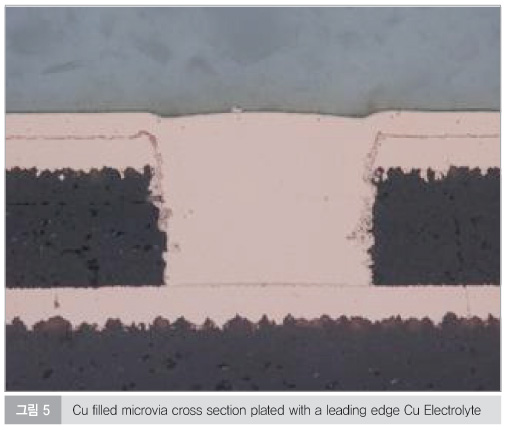

오늘날 마이크로비아의 거의 모든 중요한 치수는 함유물 없이 구리로 채워질 수 있다. 표 1에서는 오늘날 horizontal 및 vertical 도금 장비에서 충진할 수 있는 마이크로비아 치수를 보여주고 있다. 셀 내부의 숫자는 종횡비를 반영하고 있다. 표 1에서는 시장에 나와 있는 다양한 전해 구리 조성의 기능을 나타내고 있다. 각 전해 구리 레시피에는 종횡비와 관련하여 고유한 특성이 존재했다.

그림 5에서 보여주는 바와 같이, 마이크로비아 충전을 위한 최첨단 전해 조성은 다음과 같은 특성을 가지고 있다.

▶ 최대 2,5A의 전류 밀도로 도금

▶ 25%의 연성(延性) 생성

▶ 인장 강도 35kNm²

▶ 5μm 미만의 딤플; 도금 시간 <40분

▶ 표면의 13μm 구리 두께와 동 시간에 100 × 89μm 마이크 로비아를 완전히 충진

구리 쓰리홀 충진

대량 생산현장에서 구리를 적용한 쓰루홀 충진은 2005년에 시작되었다. X-도금 또는 브릿지 도금의 도입이 그 시작이었다. ‘브리징’ 기술은 인클루젼을 피하면서 쓰루홀을 완벽하게 구리도 충진시키기 위해 개발되었다. 이러한 완전한 충진 쓰루홀은 고주파 보드 PCB 설계에 있어서 열 전도성 및 신호무결성과 같은 많은 이점을 제공한다.

쓰루홀 충진은 페이스트로 메우거나 혹은 전해 구리 도금 공정으로 채움으로써 구현될 수 있다.

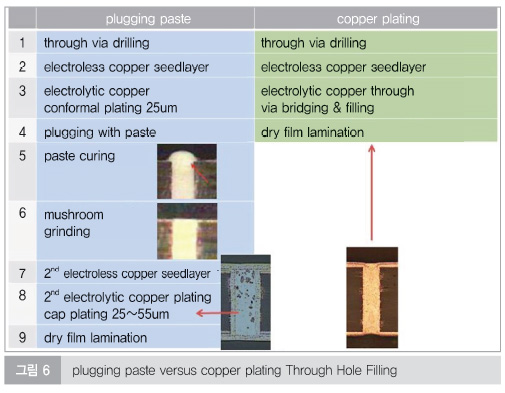

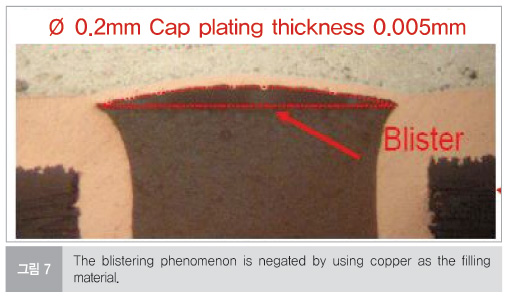

대형 홀(직경 > 500μm)의 경우, 열 전도성 페이스트를 이용한 플러깅 공법이 주로 사용되는 프로세스이다. 소형 홀(직경 < 500μm 및 가능한 종횡비 (AR > 0.5 및 < 5.0)의 경우, 브리지 도금 기술을 사용하는 구리 충전으로, 페이스트 플러깅에 비해 많은 이점이 있다. 우선 브리지 도금 기술은 페이스트 플러깅에 비해 제조 스텝이 더 적다(그림 6 참조). 생산 비용 측면에서 매우 유리하다.

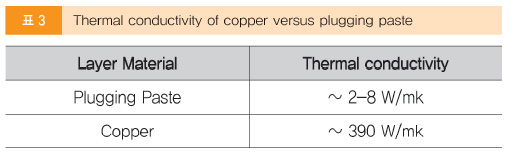

브리지 도금 기술은 충진제에 비해 열전도율 측면에서 또 하나의 이점을 제공한다. 구리는 시중에 나와 있는 낮은 열전도율 특성의 모든 플러깅 페이스트 중에서 최고의 열전도율 성질을 지닌 물질 중 하나이다(표 3 참조).

이러한 이점을 통해, PCB 설계자는 열 비아의 양을 약 70%까지 줄이는 동시에 핫스팟에서 열 전도 및 냉각 효율에 집중할 수 있다.

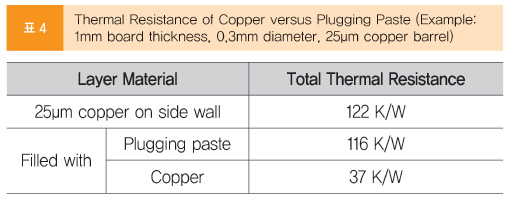

그림 6에서 볼 수 있듯이 구리 도금으로 무효화(negated)되었던 플러그된 비아에서 3가지의 신뢰성 문제가 나타났다. (1) 보이드 및 (2) 딤플은 공정 제어와 관련이 있는 반면(낮은 위험군), (3) 부풀음(blister)은 재료 및 치수와 밀접했다. 플러깅 페이스트(30~50ppm)에 비해 구리(16.5ppm)의 CTE 불일치로 인해 부풀음을 초래할 수도 있다. 플러그된 비아 상의 3가지 현상을 조사하였다[4].

페이스트로 메우면 3가지 현상이 모두 발생할 수 있지만, 구리를 충전제로 사용하면 부풀음 현상이 줄일 수 있다. 최신 구리 쓰루홀 충진 공정을 사용하여 (1) 보이드 형성을 완전히 피할 수 있었다. 이는 구리 브리징 및 충진 공정 중에 자동화되고 정교한 장비 제어를 사용하여 달성된다. 또한 구리 공정을 올바르게 설정하면 (2) 딤플을 5μm 미만으로 제어되었다. 이러한 회피 기술은 스크린 프린팅 방법을 사용하여 활성화된 고점도 플러깅 페이스트를 이용해 쓰루홀을 메우는 방식에서는 불가능하다.

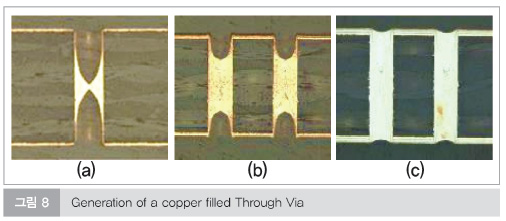

브리지 도금 기술은 다음과 같이 동작한다: 첫 번째 구리 전기 도금 공정 동안 구리 브리지가 형성된다(그림 8의 (a) 참조). 이 브리지 도금은 홀 충진의 핵심이다. 이 스텝 이후 상단과 하부 상의 2개의 마이크로비아만 남는다. 하나 이상의 후속 마이크로비아 충진 스텝을 거쳐 구리로 충진될 것이다(그림 8의 (b), (c) 참조).

구리 브리지 도금 공정은 horizontal 구리 도금 설비에서 잘 나왔는데, 이는 horizontal 시스템이 홀 내부의 유체 역학 측면에서 중요한 이점을 제공하기 때문이다. 이것은 보이드 없는 도금 결과의 생성, 표면의 매우 낮은 도금된 구리 두께, 훨씬 우수한 구리 균일성 및 vertical 도금 장치 대비 더 높은 처리량을 약속한다.

구리 충진으로 얻을 수 있는 쓰루홀의 치수는 표 4에 나와 있다. 표 4는 최신 세대의 horizontal 도금 장비에 사용되는 다양한 상용 구리 전해질을 기반으로 하고 있다.

구리 쓰루홀 충진과 관련된 현재 진행 중인 연구 및 개발에서는 다음의 주제를 다루고 있다:

▶ 빠른 처리 시간 (비용 동력)

▶ 소량의 표면 구리 도금 (비용 동력)

▶ 균일성 향상 (기술 동력)

▶ 더 우수한 충진성, 낮은 딤플 (기술 동력)

▶ 보이드 없는 수준 유지 (품질 동력)

▶ 더 높은 종횡비로 도금하기 위한 파라미터 선택

기타 새로운 전기 도금 구리 기술

마이크로비아 및 쓰루홀 충진 기술이 이미 정립되었고 양산 가동에 들어감에 따라, 전자 산업계에서는 IC-서브스트레이트 레벨 상에서 패널-레벨-패키징(PLP)이 가능하도록 IC-서브스트레이트 상의 필러 도금 혹은 소형 RDL(Redistribution Layer) 구조와 같은 새로운 특징을 요구하고 있다. 이미 상당한 기술 진전을 보이고 있다. 최근 개발된 구리 전해질을 사용한 새로운 장비 접근 방식은 이러한 기술을 가능하게 한다. 새로운 세대의 구리 도금 장비는 다음과 같은 장점을 제공한다.

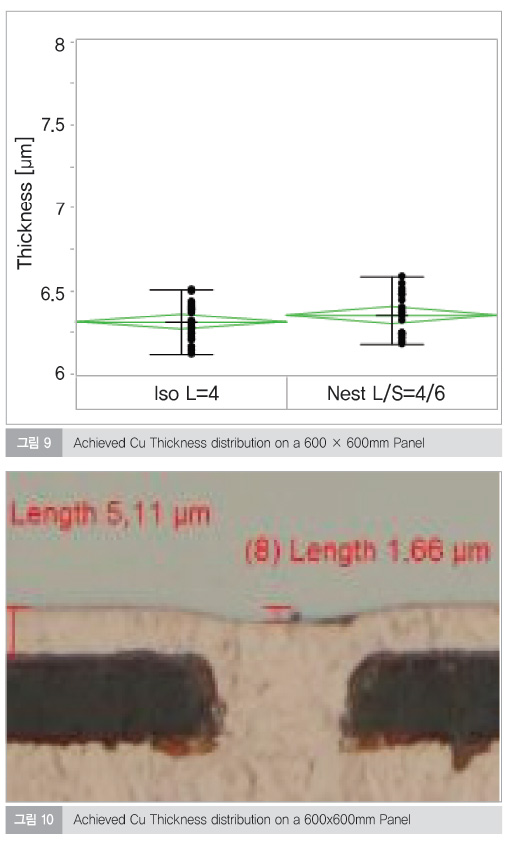

1. 구리 두께 분포가 5% 미만인 600 × 600mm 패널 상에 6 μm의 구리 두께 목표로 도금한다.

2. 표면에 5μm의 도금 두께와 2μm 미만의 딤플을 사용하여 15 × 10μm 크기의 마이크로 비아를 채울 수 있다.

또한, 이 도금 도구는 IC 기판 상에서 패널-레벨-패키징 기술을 가능하게 한다. 이를 통해 IC 기판 산업계에서는 반도체 웨이퍼 레벨 패키징 기술과의 경쟁이 가능하게 되었고, 구리 필러와 같은 새로운 기능으로 도금할 수 있게 되었다.

결론

본 고에서는 전해 구리도금 공정에 의해 구현된 마이크로비아 충진 및 쓰루홀 충진의 실제 상태를 제시하였다. 오늘날 전해 구리 공정에 의해 충진될 수 있는 마이크로비아 및 쓰루홀의 치수를 표시하였다. 또한 구리 충진 기술과 페이스트 플러깅을 비교하고 구리 충진 기술의 이점을 설명했다. 마이크로비아 충진 및 쓰루홀 충진 측면에서 향후 개발 범위를 다뤘다. 패널-레벨-패키징(PLP)과 같은 차세대 기술 부문과 새로운 전해 구리 도금 공정으로 실현된 IC 기판의 구리 필러 도금도 고려하였다.

REFERENCES

[1] Website Fraunhofer IZM: https://www.ipm.fraunhofer.de

[2] Picture from www.we-online.com. Wurthtechnologies.chapter micro via filling

[3] Picture from electronics.stackexchange.com. chapter via-in pad. technology

[4] S. Sano, Current state and future trends of PCBs in AVIO. Netherlands: 5th EMPPS workshop, ch. 3.1, pp. 11-14.(2014)

[5] S.Lamprecht, Plating a thermal runaway in PCBs - solid copper through via filling. IPC workshop, ch. 3.1, pp. 11-14. (2018)