웨이퍼 내 집적 회로와 외측 패드 연결 경로 감소효과

높은 메모리 밀도 및 낮은 비트당 가격 구현

3차원 적층 멀티칩 모듈은 W개의 집적 회로 다이의 스택을 포함한다. 각 다이는 전기적 도전체들과 일부 실시예들에 있어서는 기판 상부의 장치 회로를 갖는 전기적 콘택 영역을 포함하는 패터닝된 도전층을 구비한다. 적층 다이의 전기적 도전체들은 정렬된다. 전기적 커넥터들은 스택 내로 연장되어 전기적 도전체들 상의 랜딩 패드들에 접촉하여, 3차원 적층 멀티칩 모듈을 형성한다. 전기적 커넥터들은 전기적 콘택 영역들 내의 수직 비아들을 통과할 수 있다. 랜딩 패드들은 계단형 단차 정렬로 정렬될 수 있다. 적층 멀티칩 모듈은 2n-1이 W보다 작고 2N은 W보다 크거나 동일한 N개의 식각 마스크들의 세트를 이용하여 제조될 수 있으며, 각 마스크를 위한 2n-1(n=1,2, ,N)개의 랜딩 패드들을 교대로 덮고 노출시키는 식각 마스크들을 사용하여 형성될 수 있다.

기술 분야

본 발명은 3차원 적층 멀티칩 모듈, 3차원 적층 멀티 웨이퍼 모듈 및 3차원 적층 멀티칩 모듈 형성 방법에 관한 것이다.

배경기술

3차원(3D) 적층 집적 회로(IC)의 하나의 형태는 수직적으로 적층되고 연결되는 많은 반도체 다이(die)를 사용하여 제조되고, 결합되어 개별적인 3차원 집적 회로들을 형성한다. 외측 연결 패드들로부터 상기 3차원 집적 회로들의 전기적 도전체들까지 및 상기 3차원 집적 회로들의 상이한 층들의 전기적 도전체들 사이의 전기적 연결들은 다양한 방법들을 이용하여 형성될 수 있다. 예를 들어, 인접한 칩들의 가장 자리들의 배선 연결 방법은 계단형 단차 방식으로 엇갈릴 수 있다. 이는 외측 연결 배선들을 칩 상의 패드들과 기판 상의 패드들 사이에 연결되도록 한다.

적층 칩들 사이에 전기적 연결들을 형성하기 위한 실리콘 관통 비아(through-silicon via, TSV)라 일컬어지는 다른 방법은 상당히 관심을 받고 있다. 실리콘 관통 비아(TSV)에 의해 적층된 칩들을 상호 연결하는 점은 종래의 외측 배선 연결 기술들에 비해 몇 가지 이점들을 가진다. 실리콘 관통 비아(TSV)의 적층 칩은 넓은 밴드갭을 가질 수 있고, 이에 따라 외측 배선 연결 기술들로 비아에 연결되는 적층 칩들과 비교해 볼 때, 큰 입력/출력을 가진다. 실리콘 관통 비아(TSV)로서 속도를 향상시키고 및 낮은 전력을 소모하는 보다 짧은 연결 경로가 가능하다.

실리콘 관통 비아는 분리되어 정렬된 다이 또는 다이싱된 후의 웨이퍼 스케일 적층을 사용하여 수행될 수 있다. 이는 저비용, 고생산성을 제공하지만, 칩들의 스택 내의 하나의 칩의 실패는 낮은 수율을 도출하지 못하는 스택을 야기하므로, 수율 문제들이 있다. 또한, 가늘게 만든 웨이퍼들을 취급하는 것은 손상되거나 파괴된 제품을 야기할 수 있는 제조 공정의 문제이다. 실리콘 관통 비아는 또한 다이 스케일 적층을 사용하여 수행될 수 있다. 이는 높은 비용에서도 상대적으로 취급하기 쉽다는 이점을 갖는다.

종래의 실리콘 관통 비아의 다른 단점은 통상적인 실리콘 관통 비아 공정은 각 다이 또는 웨이퍼에 대해 11개의 단계(실리콘 관통 비아 포토레지스트 증착, 실리콘 관통 비아 식각, 실리콘 이산화물 증착, 장벽 시드(barrier seed) 증착, 포토레지스트 패터닝, 구리(Cu)/텅스텐(W) 증착. 포토레지스트 제거, 구리(Cu)/텅스텐(W) 화학적 기계적 연마, 지지/핸들링 다이 연결, 다이 박막화(thinning) 및 연결)를 필요로 한다. 상술한 모든 단계들에 요구되는 시간 및 비용뿐만 아니라 각 다이를 위해 요구되는 핸들링 및 처리는 보다 낮은 수율을 야기한다.

발명의 내용

과제의 해결 수단

3차원 적층 멀티칩 모듈의 실시예는 W개의 집적 회로 다이의 스택을 포함한다. 상기 스택 내의 각 다이는 기판 상의 패터닝된 도전층을 구비한다. 상기 패터닝된 도전층은 전기적 콘택 영역을 포함하고, 상기 전기적 콘택 영역은 전기적 도전체들을 포함한다. 상기 전기적 도전체들의 적어도 하나는 랜딩 패드를 포함한다. 상기 다이의 스택은 상기 스택의 일측 단부에 제1 다이와 상기 스택의 다측 단부에 제2 다이를 포함하고, 상기 제1 다이의 기판은 상기 제2 단부의 상기 패터닝된 도전층에 대향된다. 각 다이 상의 상기 랜딩 패드들은 상기 스택 내의 다른 다이 상의 랜딩 패드들에 정렬된다. 전기적 커넥터들은 상기 다이의 스택으로부터 연장되고, 상기 다이의 스택 내에서 상기 랜딩 패드들에 전기적으로 접촉하여, W개의 다이 레벨들을 갖는 3차원 적층 멀티칩 모듈을 형성한다. 또한 다른 실시예들은 하나 또는 그 이상의 다음과 같은 기재 사항들을 포함할 수 있다. 상기 전기적 커넥터들은 상기 랜딩 패드들에 직접적으로 접촉한다. 상기 다이의 적어도 일부는 상기 전기적 콘택 영역으로부터 이격되는 장치 회로 위치에서 장치 회로를 포함한다. 물질층은 상기 제1 다이의 패터닝된 도전층 상에 위치한다. 상기 전기적 커넥터들은 상기 전기적 콘택 영역들에서 수직 비아들을 통과한다. 각 전기적 커넥터는 하나의 다이 레벨의 하나의 랜딩 패드에 전기적으로 접속된다. 상기 전기적 커넥터들에 의해서 전기적으로 접촉되는 상기 랜딩 패드들은 계단형 단차 정렬로 정렬된다.

3차원 적층 멀티 웨이퍼 모듈의 실시예는 적층 회로 웨이퍼들의 스택을 포함하며, 각 집적 회로 웨이퍼는 다이 영역들의 격자를 포함한다. 각 집적 회로 웨이퍼를 위한 상기 다이 영역들의 적어도 일부는 집적 회로 웨이퍼들의 상기 스택의 상기 다른 집적 회로 웨이퍼들의 다이 영역들에 정렬된다. 각 다이 영역은 전술한 바와 같은 3차원 적층 멀티칩 모듈을 포함한다.

3차원 적층 멀티칩 모듈을 형성하기 위한 제1 방법의 실시예는 다음과 같이 수행될 수 있다. W개의 집적 회로 다이의 세트가 제공된다. 상기 세트 내의 각 다이는 패터닝된 도전층을 포함한다. 상기 패터닝된 도전층은 랜딩 패드들을 갖는 전기적 콘택 영역을 포함한다. 핸들링 다이는 상기 세트 내의 선택된 다이에 실장된다. 각 반복 과정에서 향상된 핸들링 다이를 사용하여 상기 실장 및 제거 단계들이 반복된다. 이러한 반복 수행에 따라, 각 다이 상의 상기 랜딩 패드들은 상기 세트 내의 모든 다이들이 실장될 때까지 각 다이 상의 랜딩 패드들은 상기 세트 내의 다른 다이 상의 랜딩 패드들에 정렬된다. 커넥터들은 상기 3차원 적층 다이를 통해서 상기 모듈의 표면으로부터 형성되어, 상기 세트 내의 각 다이에서 정렬된 랜딩 패드들에 접촉한다. 이에 따라 W개의 다이 레벨들을 구비하는 3차원 적층 멀티칩 모듈이 형성된다.

제1 방법의 실시예들은 또한 하나 또는 그 이상의 다음의 기재 사항들을 포함할 수 있다. 상기 커넥터들을 형성하는 단계는 상기 전기적 콘택 영역으로부터 이격되는 장치 회로 위치에서 장치 회로를 포함하는 상기 다이의 적어도 일부와 함께 수행된다. 상기 핸들링 다이를 실장하는 단계는 핸들링 다이와 상기 다이 사이에 유전층, 접착-강화층을 증착하는 단계를 더 포함한다. 상기 다이는 상기 패터닝된 도전층이 위치하는 제1 측부, 상기 제1 측부에 대향하는 제2 측부, 상기 기판의 상기 제2측부로부터 제거되는 노출된 층을 구비하는 기판을 포함하도록 선택된다. 상기 핸들링 다이의 적어도 일부는 3차원 적층 멀티칩 모듈로부터 제거되어 노출된 표면을 형성한다. 각 다이 레벨을 위한 상기 전기적 도전체의 랜딩 패드 상부에 위치하는 상기 콘택 개구들은 표면 내에 형성되고, N개의 식각 마스트들의 세트는 2N-1은 W보다 작고, 2N은 W보다 크거나 작게 선택되며, 상기 N개의 마스크들을 사용하여 상기 W개의 다이 레벨들까지 콘택 개구들을 식각하고, 상기 N개의 마스크들을 이용하는 단계는 각 마스크를 위한 상기 콘택 개구들의 실질적인 절반을 위하여 2n-1(n=1, 2, …, N)개의 다이 레벨들을 식각하는 단계를 포함하고, 이에 따라 상기 전기적 도전체들은 상기 각 다이 레벨들에서 전기적 도전체 요소들에 전기적으로 접촉하도록 상기 콘택 개구들 내에 형성될 수 있다. 상기 표면은 핸들링 다이 제거 단계 이후에 유전 물질에 의해서 덮이고, 상기 콘택 개구들을 형성하는 단계는 각 마스크를 위한 2n-1(n=1, 2, …, N)개의 랜딩 패드들을 교대로 덮고 노출시키는 단계를 더 포함한다.

복수의 3차원 적층 멀티칩 모듈들을 생성하기 위한 제2 방법은 다음과 같이 수행될 수 있다. W개의 집적 회로 웨이퍼들의 세트가 제공된다. 상기 세트 내의 각 웨이퍼는 다이 영역들의 격자를 포함한다. 각 다이 영역은 패터닝된 도전층을 포함하는 집적 회로 다이를 구비하고, 상기 패터닝된 도전층은 전기적 콘택 영역을 포함한다.

상기 전기적 콘택 영역을 랜딩 패드들을 구비한다. 핸들링 웨이퍼는 상기 패터닝 도전층들 상에 상기 세트 내의 선택된 웨이퍼에 실장된다. 상기 선택된 웨이퍼의 노출된 층은 제거되어, 향상된 핸들링 웨이퍼를 형성한다. 상의 상기 랜딩 패드들은 상기 세트 내의 모든 웨이퍼들이 실장될 때까지, 각 반복 과정에서 향상된 핸들링 웨이퍼를 사용하여 상기 실장 및 제거 단계들이 반복되어, 각 다이의 랜딩 패드들이 상기 집적 회로 웨이퍼들의 세트 내의 상기 다른 다이 상의 랜딩 패드들에 정렬된다. 이에 따라 3차원 적층 다이의 격자를 포함하는 3차원 적층 웨이퍼가 형성된다. 정렬된 랜딩 패드들에 접촉하는 3차원 적층 웨이퍼의 표면으로부터의 커넥터들은 형성되어 3차원 적층 멀티칩 모듈들의 격자를 형성한다. 상기 3차원 적층 멀티칩 모듈들의 격자를 개별적인 3차원 적층 멀티칩 모듈들로 물리적으로 분리시킨다.

제2 방법의 실시예들은 또한 다음과 같이 수행되는 커넥터들의 수행 단계와 함께 수행될 수 있다. 상기 복수의 3차원 적층 멀티칩 모듈들의 각 다이 레벨을 위한 상기 전기적 도전체들의 랜딩 패드들의 상부에 위치하는 상기 콘택 개구들은 상기 3차원 적층 웨이퍼의 상기 표면을 통해서 생성된다. N개의 식각 마스크들의 세트는 2N-1은 W보다 작고, 2N은 W보다 크거나 동일하게 선택된다. 상기 N개의 마스크들을 사용하여 각 마스크를 위한 상기 콘택 개구들의 실질적인 절반을 위하여 2n-1(n=1, 2, …, N)개의 다이 레벨들을 식각하여, W개의 다이 레벨들까지 상기 콘택 개구들을 식각한다. 상기 전기적인 도전체들은 상기 각 다이 레벨들에서 랜딩 패드들에 전기적으로 접촉하도록 상기 콘택 개구들 내에 형성될 수 있다. 제2 방법의 실시예들은 또한, N개의 식각 마스크들을 사용하는 단계가 각 마스크를 위한 대한 2n-1(n=1, 2, …, N)개의 랜딩 패드들을 교대로 덮고 노출시키는 단계를 더 포함하도록 수행될 수 있다.

본 발명의 다른 특징들, 측면들 및 이점들은 첨부된 도면들, 발명의 상세한 설명 및 청구 범위를 참조하여 보다 명확하게 이해될 수 있을 것이다.

발명의 효과

본 발명에 따른 3차원 집적 회로를 구현하기 위한 기술은 종래 기술과 비교하여 웨이퍼 내의 집적 회로와 외측 패드들을 연결하는 연결 경로를 크게 감소시킨다. 따라서 각 다이는 보다 많은 전기적 콘택 영역들을 구비할 수 있으므로, 종래 기술과 비교하여 보다 높은 메모리 밀도와 보다 낮은 비트당 가격의 구현이 가능하다.

발명을 실시하기 위한 구체적인 내용

다음 설명은 특정한 실시예들 및 방법들을 참조하는 통상적인 것이다. 구체적으로 개시된 실시예들과 방법들은 본 발명을 제한하려는 의도가 아니며 본 발명은 다른 특징들, 요소들, 방법들 및 실시예들을 이용하여 구현될 수 있음을 이해할 수 있을 것이다. 본 발명을 예시적으로 설명하기 위하여 기재되는 바람직한 실시예들은 청구 범위들에 의해 한정되는 본 발명의 범위를 제한하는 것은 아니다. 해당 기술 분야에서 통상의 지식을 가진 자라면 후술하는 기재 사항들부터 균등하고 다양한 변경들을 이해할 수 있을 것이다. 다양한 실시예들에 있어서 동일한 요소들은 공통적으로 동일한 참조 부호들로 언급된다.

본 발명은 웨이퍼 스케일 적층(wafer scale stacking) 또는 다이 스케일 적층(die scale stacking)을 사용하여 수행될 수 있다. 그림들을 통해서 본 발명은 일반적으로 다이 스케일 적층의 용어로 설명될 것이다.

웨이퍼 스케일 적층을 사용하여 수행되는 발명으로부터 축적된 추가적인 이점들은 그림들을 참조하여 본 발명에 대한 설명에서 기재된다. 동일한 참조 부호들은 다이들 및 웨이퍼들의 동일한 요소들을 언급할 때, 통상적으로 사용될 것이다.

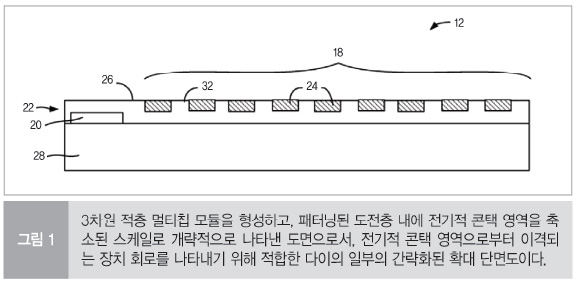

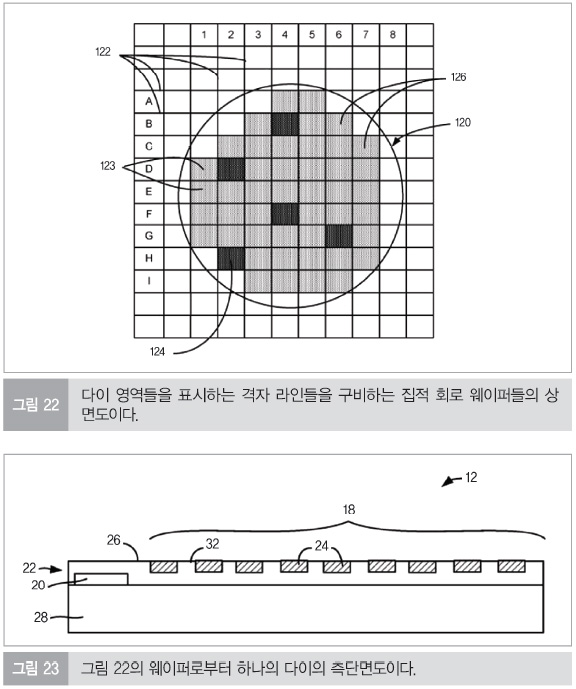

그림 1은 다음에서 기술하는 바와 같이, 3차원 적층 멀티칩 모듈을 생성하기 위하여 적합한 집적 회로 다이(12)의 간략화된 확대 단면도이다. 그림 1의 다이(12)는 패터닝된 도전층(22) 내에 전기적 콘택 영역(18) 및 다이(12)를 위한 도식적으로 나타낸 활성 장치 회로(20)를 나타낸다. 패터닝된 도전층(22)은 상부에 위치하고, 다이(12)의 기판(28)에 의해서 지지되는 유전층(26)을 포함한다. 기판(28)은 통상적으로 실리콘이다. 전기적 콘택 영역(18)은 통상적으로 구리 또는 텅스텐과 같은 적합한 금속으로 형성되는 전기적 도전체들(24)의 수를 포함한다. 유전층(26)은 통상적으로 실리콘 이산화물과 같은 산화물이다. 이러한 실시예에 있어서, 전기적 도전체들(24) 및 장치 회로(20)는 유전층(26) 내에서 형성되고, 유전층(26)의 물질에 의해서 서로로부터 이격된다. 다이의 미션(mission) 기능을 위한 회로들을 포함하는 활성 장치 회로(20)는, 바람직하게는 전기적 콘택 영역(18)으로부터 이격되고, 따라서 전기적 콘택 영역(18)의 하부에 위치하지 않는다. 활성 장치 회로(20)는 플래시 메모리 회로, 다른 형태의 메모리 회로, 전용 회로, 범용 프로세서, 프로그램 가능한 논리 회로 장치, 칩 장치의 시스템의 경우와 같은 회로 형태들의 조합들 및 회로들의 상기 내용 및 회로들의 다른 형태들의 조합들을 포함할 수 있다.

그림 1에 있어서, 활성 장치 회로(20)는 도면의 목적을 위해 상대적으로 작은 요소로서 나타낸다. 콘택 영역(18)과 비교해볼 때, 상대적인 크기는 특정한 실시 형태에 따라 달라진다.

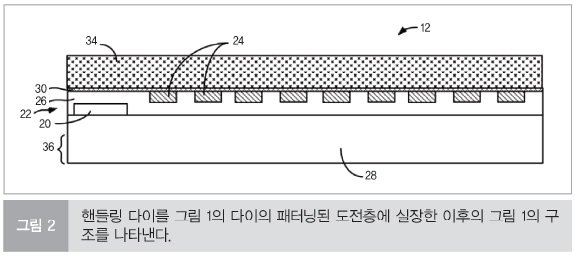

그림 2는 하드 마스크층(30)이 그림 1의 패터닝된 도전층(22)의 상부 표면(32) 상에 증착된 이후의 그림 1의 다이(12)를 나타낸다. 하드 마스크층(30)은 분리와 향상된 접착을 위해 사용되는 선택적인 유전층이다. 핸들링 다이(34)는 다이(12)의 하드 마스크층(30)에 실장된다. 핸들링 다이(34)는, 바람직하게 충분히 두껍고 강하여, 이후의 공정 단계들 동안 하부에 위치하는 다이(12) 및 이후에 추가되는 다이(12)에 손상을 막는데 도움이 된다. 핸들링 다이(34)는 통상적으로 베어 실리콘 다이(bare Si die)이다. 웨이퍼 스케일 다이가 사용될 때, 핸들링 웨이퍼는 통상적으로 웨이퍼(12.1)에 적용되는 하드 마스크층(30)에 대응하는 하드 마스크층 의 웨이퍼(12.1)에 실장된다. 상기 핸들링 웨이퍼는 바람직하게는 충분히 두껍고 강하여, 차후의 공정 단계들 동안 하부에 위치하는 웨이퍼(12.1) 및 차후에 추가되는 웨이퍼(12.1)에 손상을 막는데 도움이 된다. 상기 핸들링 웨이퍼는 통상적으로 베어 실리콘 웨이퍼(bare Si wafer)이다.

그림 3은 그림 2에 나타낸 바와 같이 그림 2의 다이(12)의 기판(28)의 하부 일부(36)는 제거되어 잔존하는 기판(remaining substrate) 상에 하부 연결 표면(40)을 구비하는 향상된 핸들링 다이(38)를 생성한 이후의 그림 2의 구조를 나타낸다. 상기 다이를 박화하는 단계는 핸들링 다이(34)에 의해서 하부에 위치하는 다이(12)에 제공되는 힘으로 인하여 수행된다. 웨이퍼 스케일 구동들 동안, 상기 구동들은 향상된 핸들링 다이(38)에 대응하는 향상된 핸들링 웨이퍼의 생성을 야기한다.

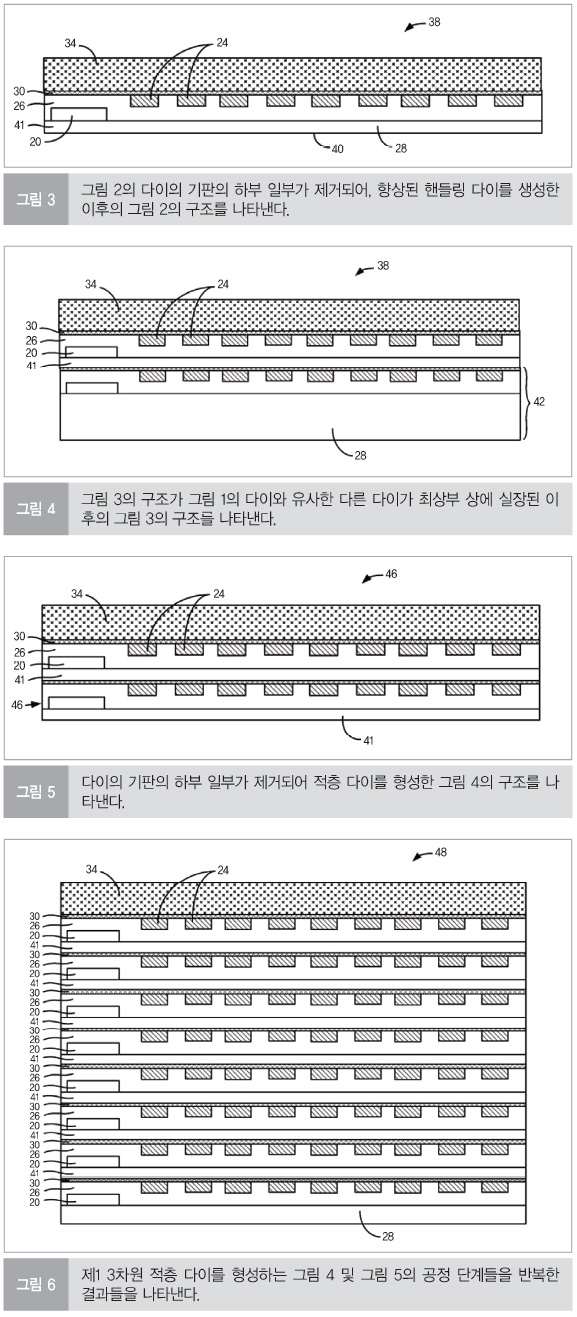

그림 4는 다른 다이(42)의 최상부에 실장된 그림 3의 향상된 핸들링 다이(38)를 나타낸다. 다른 다이(42)는 그림 1의 다이(12)와 유사하지만, 바람직하게는 패터닝된 도전층(22)의 상부 표면(32) 상에 형성된 하드 마스크층(30)을 포함한다. 향상된 핸들링 다이(38)의 하부 표면(40)은 다른 다이(42)의 하드 마스크층(30)에 실장된다. 이와 유사하게, 웨이퍼 스케일 구동들 동안, 향상된 핸들링 웨이퍼의 하부 표면은 다른 웨이퍼의 하드마스크 층에 실장된다.

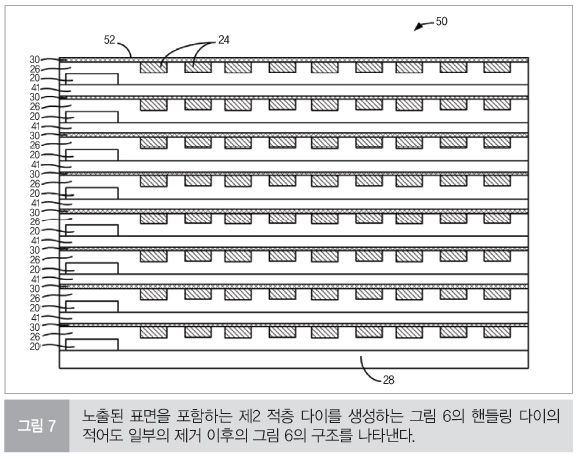

그림 5는 그림 4에 나타낸 바와 같이 각 다이(12)의 기판(41)의 하부 일부(36)가 제거되어, 적층 다이(16)를 생성한 이후의 그림 4의 구조를 나타낸다. 그림 6은 추가적인 다른 다이(42)를 사용한 그림 4 및 그림 5의 공정 단계들을 반복하여 제1 3차원 적층 다이(48)를 형성한 결과들을 나타낸다. 적층 다이(46)의 두께를 감소시킴으로부터 도출되는 하나의 이점은 반드시 식각되고 충진된 비아의 깊이가 감소되는 것이다. 비아의 깊이는 증가시키는 것은 종종 비아의 직경을 증가시키는 것을 요구하므로 이는 제조 공정을 간략화시킨다. 실시예들에 있어서, 상기 비아는 폭이 점점 가늘어질 수 있고, 비아들을 충진하는 기술은 큰 종횡비들(비아의 폭에 의해서 분리되는 깊이)에 제한된다. 웨이퍼 스케일 구동들 동안, 적층 웨이퍼는 제1 3차원 적층 웨이퍼의 생성을 수반하는 유사한 방식으로 형성된다.

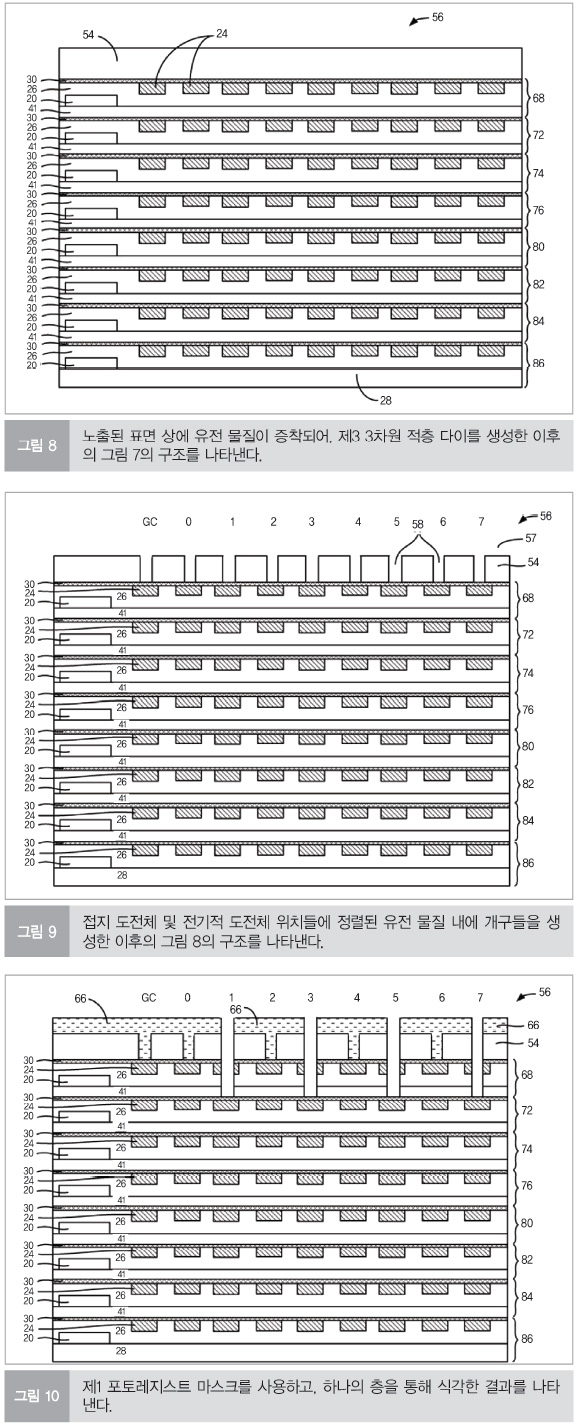

그림 7은 노출된 표면(52)을 구비하는 제2 3차원 적층 다이(50)를 형성하는 그림 6의 핸들링 다이(34)의 적어도 일부를 제거한 이후의 그림 6의 제1 3차원 적층 다이(48)를 나타낸다. 그림 8은 유전 물질(54)이 노출된 표면(52) 상에 증착되어, 제2 3차원 적층 다이(56)를 형성한 이후의 그림 7의 구조를 나타낸다. 마찬가지로, 웨이퍼 스케일 구동들 동안, 3차원 적층 웨이퍼 및 제3 3차원 적층 웨이퍼(56.1)가 형성된다. 그림 9는 적층 멀티칩 모듈(61)의 일부로 나타내고, 전기적 도전체들(24)과 접촉하는 전기적 커넥터들(60)을 생성하는 단계들의 공정을 나타낸다. 전기적 커넥터들(60)은 상이한 레벨들에서 전기적 도전체들(24)의 랜딩 패드들(98)을 콘택 패드들(62)에 연결한다. 상이한 전기적 커넥터들은 전기적 커넥터들(60.0 내지 60.7)로서 식별된다. 전기적 도전체들(24)에 대응하는 콘택에 대한 전기적 커넥터들(60)에 대한 위치들은 도면들에서 0 내지 7로 나타낸다. GC로 나타낸 위치는 통상적으로 각 레벨에서 전기적 도전체들(24)에 전기적으로 접촉하는 접지 커넥터(64)의 위치를 식별한다. 반면에 오직 하나의 전기적 커넥터(60)가 도시되어, 각 레벨에서 전기적 도전체(24)에 접촉하고, 실시예들에 있어서, 많은 다른 전기적 커넥터들(60)이 사용되어, 동일한 레벨에서 전기적 커넥터들(24)에 접촉한다. 웨이퍼 스케일 구동들 동안, 동일한 기본 공정 단계들은 제3 3차원 적층 웨이퍼(56.1) 상에 사용되어, 적층 멀티칩 모듈들(61)의 어레이를 생성한다.

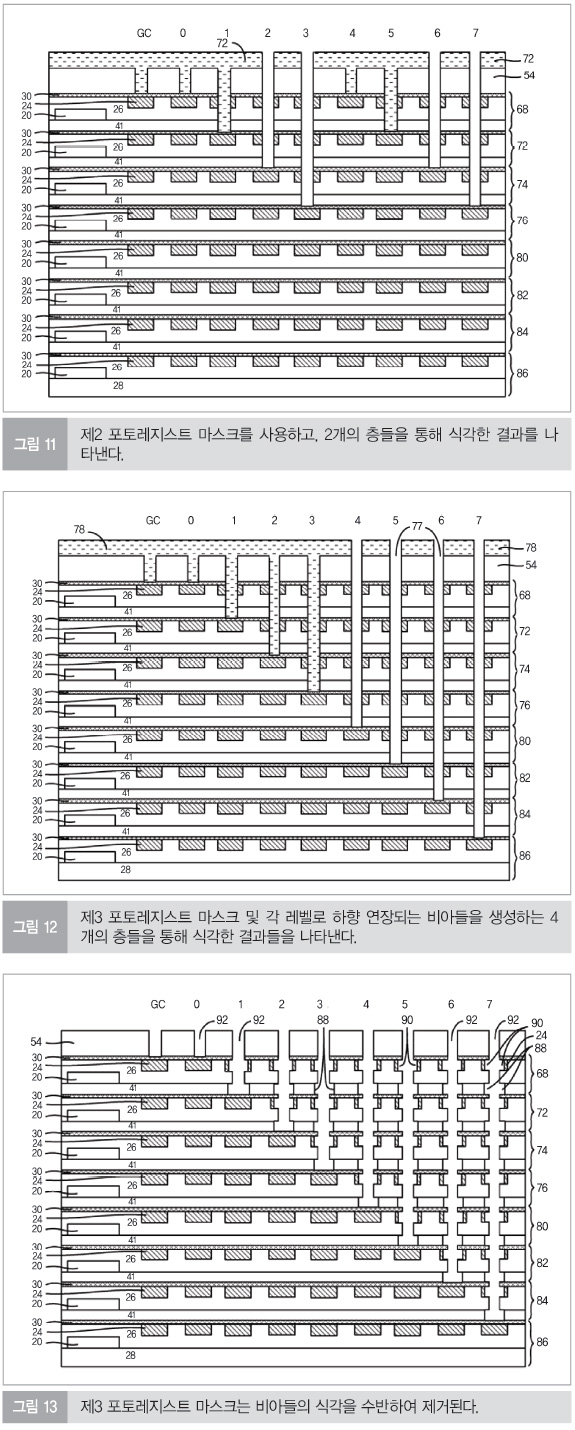

그림 9는 유전 물질(54)을 하드 마스크층(30)까지 하향 식각을 수반하는 유전 물질 상의 초기-공정 포토레지스트 마스크(57)를 형성한 이후의 그림 8의 구조를 나타낸다. 이는 접지 도전체 위치(GC) 및 전기적 도전체 위치들(0 내지 7)에 정렬된 개구들(58)을 생성한다. 그림 10에 나타낸 제1 포토레지스트 마스크(66)는 전기적 도전체 위치들(1, 3, 5 및 7)에서 개구들(58)을 제외한 그림 9의 구조 상에서 형성된다. 전기적 도전체(24)에 정렬된 이들 개구들은 하드 마스크층(30), 제1에서 전기적 도전체들(24), 최상부 레벨들(68), 유전층(26) 및 제2 레벨(70)에서 전기적 도전체들(24)의 상부에 식각 정지층인 실리콘 기판(41)을 통해서 하나의 레벨을 식각한다.

도면들에서 전기적 커넥터들(60)이 일렬로 정렬되게 도시되었지만, 다른 레이아웃들도 가능하다. 예를 들어, 전기적 커넥터들(60)은 평행하거나 가로로 연장되는 많은 행들로 정렬될 수 있다. 예를 들어, 그림 1의 전기적 콘택 영역(18)은 2개 또는 그 이상의 전기적 커넥터들(60)의 행들을 포함할 수 있다.

다음으로, 그림 11에 나타낸 바와 같이, 제1 포토레지스트 마스크(66)는 제거되고, 그 다음에 제2 포토레지스트 마스크(72)가 그림 10의 결과 구조(resulting structure) 상에 형성되어, 접지 도전체 위치들(GC), 전기적 도전체 위치들(0, 1, 4, 5) 및 후속하는 위치(7)를 커버한다. 2개의 레벨들의 식각은 다음과 같이 진행된다. 위치들(2, 6) 하부에 위치하는 결과 구조의 일부들은 이들 레벨들에서 제1 및 제2 레벨들(68, 70)을 통해 2개의 레벨들은 전기적 도전체들(24)까지 하향 식각된다. 위치들(3, 7) 하부에 위치하는 결과 구조의 일부들은 이들 레벨들에서 제1 및 제2 레벨들(70, 74)을 통해 2개의 레벨들이 전기적 도전체들(24)까지 하향 식각된다. 상기 단계들은 그림 11에 나타낸 구조를 형성한다.

다음으로, 제2 포토레지스트 마스크(72)는 제거되고, 제3 포토레지스트 마스크(78)는 형성되어, 접지 도전체 위치(GC), 전기적 도전체 위치들(0, 1, 2, 3) 및 후속하는 위치(7)를 커버한다. 위치들(4, 5, 6, 7) 상부에 위치하는 구조의 노출된 일부들은 4개의 레벨들, 즉, 위치들(4, 5, 6, 7)에서 각기 제5 레벨(80), 제6 레벨(82), 제7 레벨(84) 및 제8 레벨(86)을 하향 식각하여 그림 12의 구조에서 비아들(77)을 생성한다.

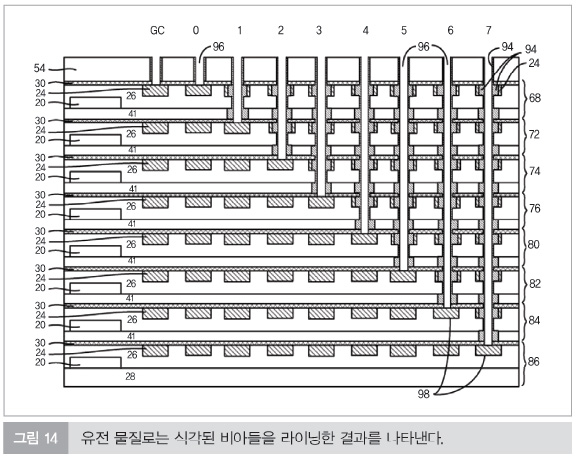

제3 포토레지스트 마스크(78)는 비아들(77)에서 기판들의 노출된 일부들의 등방성 식각에 의해 후속하여 제거되어, 리세스된 영역들(88)을 생성한다. 그림 13에 나타낸 바와 같이, 비아들(77)에서 전기적 도전체들(24)의 등방성 식각은 그 다음 수행되어, 비아들(77)을 따라 도전체 리세스된 영역들(90)을 생성한다. 이들 식각 단계들은 변형된 비아들(92)을 형성한다.

그림 14는 산화물(94)과 같은 유전 물질(94)을 구비하는 변형된 비아들(92)의 정렬에 따라 산화질(94)을 리세스된 영역들(88, 90)에 충진한 결과들을 나타낸다. 산화물(94)은 예를 들어 실리콘 질화물(SiN)일 수 있다. 결과 비아들(resulting vias)(96)은 연장되어 랜딩 패드들(98)로 기능하는 하부에 위치하는 전기적 도전체들(24)의 일부들을 개방시킨다.

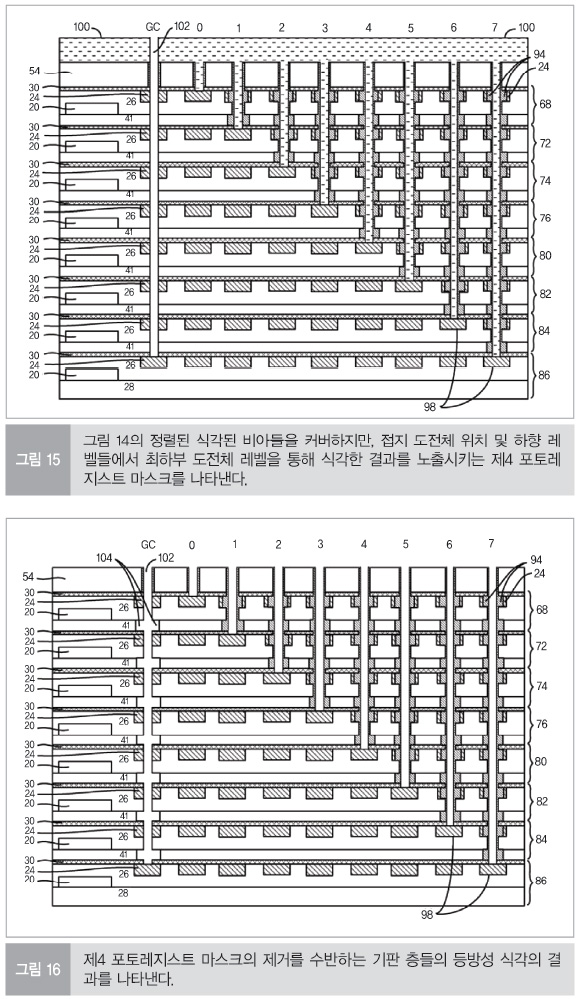

그림 15는 전기적 도전체들(60) 및 접지 도전체(64)를 형성하도록 이용되는 공정 단계들을 나타낸다. 그림 15에 있어서, 제4 포토레지스트 마스크(100)는 접지 도전체 위치(GC)를 제외한 모든 부분을 덮는 것으로 나타낸다. 그림 15는 또한 접지 도전체 비아(102)를 생성하는 제8 레벨(86)에서 제1 내지 제7 레벨들(68, 70, 74, 76, 80, 82, 84)을 통해 전기적 도전체(24)까지 하향 식각의 결과를 나타낸다. 그림 16은 리세스된 영역들(104) 및 접지 도전체 비아(102)에 개구를 생성하도록 접지 도전체 비아(102)에서 기판(41)의 등방성 식각의 결과를 나타낸다. 이는 제4 포토레지스트 마스크(100)의 제거를 수반한다.

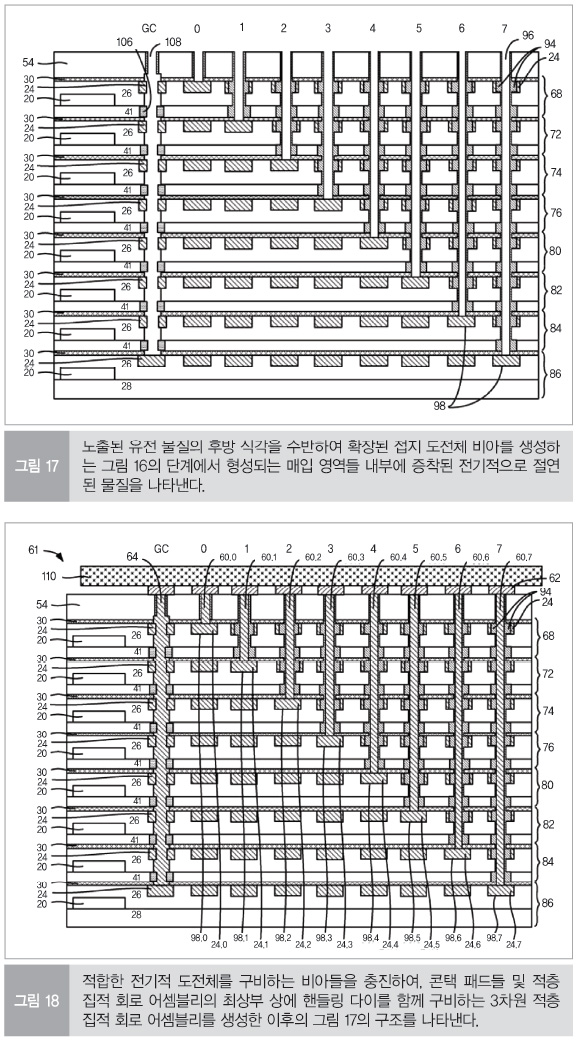

그림 17은 예를 들어, 폴리머와 같은 유기 물질과 같은 전기적으로 절연된 물질을 리세스된 영역들(104) 내에 증착한 결과를 나타낸다. 또한, 층들(26)에서 노출된 유전 물질은 하향 식각되어, 확장된 접지 도전체 비아(108)를 생성한다. 이는 확장된 접지 도전체 비아(108)를 통과하는 전기적 도전체들(24)의 노출된 측벽 콘택 표면들 내의 증가를 야기한다.

그림 18은 결과 비아들(96) 및 금속 또는 다른 적합한 전기적 도전체를 포함하는 확장된 접지 도전체 비아(108)를 충진하여, 접지 커넥터(64) 및 전기적 커넥터들(60.0 내지 60.7)을 생성한 이후의 그림 17의 구조를 나타낸다. 이는 또한 3차원 적층 멀티칩 모듈(61)을 생성한다. 멀티칩 모듈(61)은 멀티칩 모듈(61)과 구조(110) 사이에 위치한 콘택 패드들(62)과 함께 도시된다. 구조(110)는 기술에 의해서 제공되는 유연성 때문에 예를 들어, 메모리 요소들 또는 논리 회로들 또는 메모리 요소들 및 논리 회로들의 조합과 같은 활성 요소들을 구비하는 핸들링 다이 또는 다이일 수 있다. 구조(110)가 활성 요소들을 포함할 때, 구조(110)는 전기적 연결들을 통해 적층 멀티 칩 모듈(61)에 상호 연결될 수 있어, 패드들(62) 및 전기적 커넥터들(60)에 접촉한다. 접지 도전체(64) 및 전기적 도전체들(60)은 실질적으로 균일한 전기적으로 도전성인 물질의 길이들이다. 실질적으로 균일하기 때문에, 여기서 도전체들(60)은 레벨들 사이에 물리적 경계들이 결핍됨을 의미한다. 비록 랜딩 패드들을 형성하도록 사용되는 도전성 물질은 제조 공정의 결과로서 각 레벨에서 상대적인 농도가 다를 수 있는 비아들에서 증착된 상이한 물질들의 멀티 층들을 포함하는 경우에도 여기서 사용되는 도전체들(60)은 실질적으로 균일하다. 이는 흔히 대향되는 전극 전도체들을 연결하는 분리된 도전성 물질을 구비하는 심들(seams)을 형성하는 칩들 및 웨이퍼들이 적층되고, 서로 연결될 때에 각 층의 개별적인 비아 내에 전기적 커넥터들은 각기 형성되고 서로 연결되는 종래의 TSV 공정들에 의해서 형성되는 전기적 커넥터들에 대한 것이다.

그림 6의 제1 3차원 적층 다이(48)를 형성하도록 사용되는 다이(12)는 다른 위치들에서 전기적 도전체들(24), 개별적인 다이 상의 패턴들일 수 있고, 상기 각 다이(12)를 위한 전기적 도전체들에 대한 위치들 및 패턴들은 동일하여 제조 공정들을 가능하게 하는 것이 바람직하다. 특히, 각 레벨에서 랜딩 패드들(98)이 정렬되는 점이 통상적으로 요구된다. 전기적 커넥터들(60)을 형성하기 위해서 상술한 공정은 식각 단계의 20…2n-1에 기반을 둔 이진 공정(binary process)으로서 언급된다. 즉, 그림 10에 나타낸 제1 포토레지스트 마스크(66)는 20개의 랜딩 패드들(98)을 교류하게 덮고, 20개의 랜딩 패드들(98)을 노출시키며, 그림 11에 나타낸 제2 포토레지스트 마스크(72)는 21개의 랜딩 패드들(98)을 교대로 덮고, 21개의 랜딩 패드들(98)을 노출시키며, 그림 12에 나타낸 제3 포토레지스트 마스크(78) 등은 22개의 랜딩 패드들(98)을 교대로 덮고, 22개의 랜딩 패드들(98)을 노출시킨다. 이러한 공정을 이용하여 n개의 마스크들이 사용될 수 있고, 2n개의 레벨들에서 2n개의 전기적 도전체들(24)에 대한 2n개의 랜딩 패드들(98)에 접근을 제공한다. 따라서 3개의 마스크들을 사용하여 8개의 레벨들에서 2n개의 전기적 도전체들(24)에 대한 8개의 랜딩 패드들(98)에 접근을 제공한다. 5개의 마스크들을 사용하여 32개의 전기적 도전체들(24)에 대한 32개의 랜딩 패드들(98)에 접근을 제공할 수 있다. 식각의 순서가 n-1=0, 1, 2, … 일 필요는 없다. 예를 들어, 제1 식각 단계는 n-1=2 일 수 있고, 제2 식각 단계는 n-1=0 일 수 있으며, 제3 식각 단계는 n-1=1 일 수 있다. 이러한 결과는 그림 12에 도시된 구조와 동일할 수 있다. 통상적인 구동들 동안, 절반의 콘택 개구들이 각 식각 단계 동안 식각된다. 식각될 수 있는 레벨들의 수는 5개의 포토레지스트 마스크들이 사용되어 29개의 상이한 랜딩 패드들(98)에 도달하도록 29개의 콘택 개구들을 식각할 때 식각되는 레벨들의 수보다 동일하거나 크고, 상기 마스크들은 콘택 개구들의 절반을 식각하는데 사용되지 않고, 콘택 개구들의 실질적인 절반으로서 언급되는 것을 식각하는데 사용될 것이다.

전기적 도전체들(24)의 랜딩 패드들(98)에 전기적 커넥터들(60)을 연결하기 위한 기술들 및 방법들에 대한 추가적인 정보는 동시 계류 중인 2011년 5월 16일 자의 미국 특허 출원 제13/049,303호(발명의 명칭: REDUCED NUMBER OF MASK FOR IC DEVICE WITH STACKED CONTACT LEVELS)에 개시되어 있고, 2011년 5월 24일 자 미국 특허 출원 제13/114,931호(발명의 명칭: MULTILAYER CONNECTION STRUCTURE AND MAKING METHOD)에 참조로서 기재되어 있다.

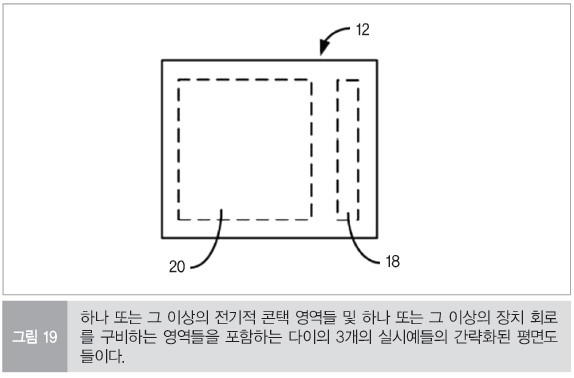

그림 19는 하나 또는 그 이상의 전기적 콘택 영역(18) 및 하나 또는 그 이상의 활성 장치 회로(20)를 구비하는 각각의 다이(12)의 3개의 실시예들의 간략화된 평면도들이다. 다이(12)는 모두 동일하거나 상이할 수 있다. 예를 들어, 중앙 처리 장치(CPU) 또는 컨트롤러들과 같은 논리 다이는 메모리 다이로 사용될 수 있다. 그림 18의 실시예들에 있어서, 다이(12)의 주요 일부를 구성하는 반면, 전기적 콘택 영역(18)은 다이(12)의 하나의 가장자리를 따라 위치된다. 그림 19의 실시예들에 있어서, 전기적 콘택 영역(18)은 활성 장치 회로(20)의 3개의 상이한 측부들을 따라 3개의 상이한 위치들에서 형성된다. 그림 20에 있어서, 이러한 실시예에 따르면, 단일 전기적 콘택 영역(18)에 의해서 분리된 활성 장치 회로(20)의 2개의 영역들이 있다. 적층된 공정의 이점들 중 하나는, 예를 들어 외측 연결 패드들 및 배선들을 연결하는데 적층된 칩들을 사용하는 것 보다 연결 경로가 더 짧기 때문에 각 다이(12)는 영역(18)과 같은 많은 전기적 콘택 영역들을 구비할 것으로 예상된다. 2 마이크로미터와 같은 최소 길이는 하나 또는 그 이상의 전기적 콘택 영역들(18)과 활성 장치 회로(20) 사이에서 유지된다. 상기 최소 거리는 공정에 의해서 유도된 응력들(stresses) 때문에 요구될 수 있다. 따라서 다른 실시예들에 있어서, 하나 또는 그 이상의 레벨들 내의 상기 장치들은 상기 레벨들 사이에 100개 또는 그 이상의 많은 커넥터들을 포함하는 넓은 입력/출력(I/O) 구조들을 포함할 수 있다. 다른 실시예들에 있어서, 레벨들 사이에 약간의 커넥터들이 사용된다.

본 발명에 따르면, 상술한 이점이 적용될 수 있으므로, 종래의 TSV 적층 반도체 장치들을 형성하는 데 요구되는 단계들과 관련되는 시간 및 비용을 크게 감소시킨 3차원 적층 메모리 장치들을 포함하는 3차원 적층 멀티칩 모듈을 형성한다. 또한, 본 발명은 수율들의 향상을 이끌 수 있는 종래의 TSV 단계들과 비교해 보았을 때, 각 다이의 요구되는 핸들링 및 공정을 감소시킨다. 휴대전화들과 같은 장치들에 중요한 더 얇은 장치를 제공할 뿐만 아니라, 하부 부분들(36)의 제거에 의해서 다이(12)의 결과 스택(resulting stack)의 두께의 감소는 몇 가지 이점들을 포함한다. 상술한 이점들은 전기적 커넥터들(24)을 다른 커넥터들 및 랜딩 패드들(98)에 연결하는 전기적 커넥터들(24)의 길이를 감소시키는 것을 포함하여, 저항 및 열 손실을 감소시키고, 속도를 증가시킨다.

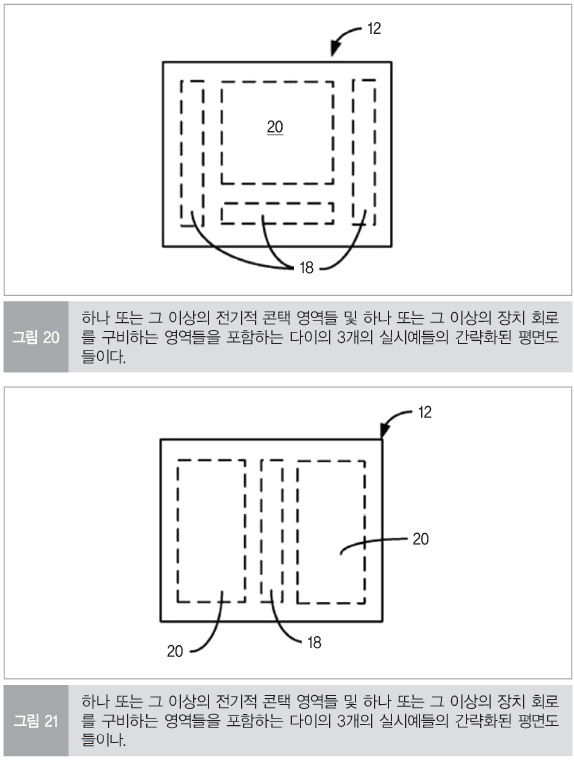

본 발명은 상술한 바와 같이 다이 스케일 적층 단계들을 사용하여 수행될 수 있으며, 또한 다음에서 설명하는 추가적인 이점들을 도출하는 웨이퍼 스케일 적층 단계들을 사용하여 수행될 수 있다. 그림 22는 개별적인 다이(12)가 웨이퍼(120)로부터 생성될 수 있는 다이 영역들(123)을 표시하는 격자 라인들(122)을 구비하는 집적 회로 웨이퍼(120)를 나타내는 상면도이다. 그림 23은 웨이퍼(120) 상의 위치(C 내지 7)로부터 그림 1의 다이(12)와 실질적으로 동일한 통상적인 다이(12)의 간략화된 단면도이다. 이러한 실시예에 있어서, 웨이퍼(120)로부터 생성되는 총 50개의 다이(12)가 있다. 도면의 목적들을 위해서, 5개의 다이(12)는 그림 22에서 5개의 결함이 있는 다이(12) 및 크로스해치됨(crosshatched)에 의해서 표시되는 불량 다이(124)로 가정된다. 이러한 경우에 있어서, 웨이퍼(120) 상의 다이의 90%는 우수한 다이(125)일 수 있지만, 다이(120)의 10%는 불량 다이(124)일 수 있다.

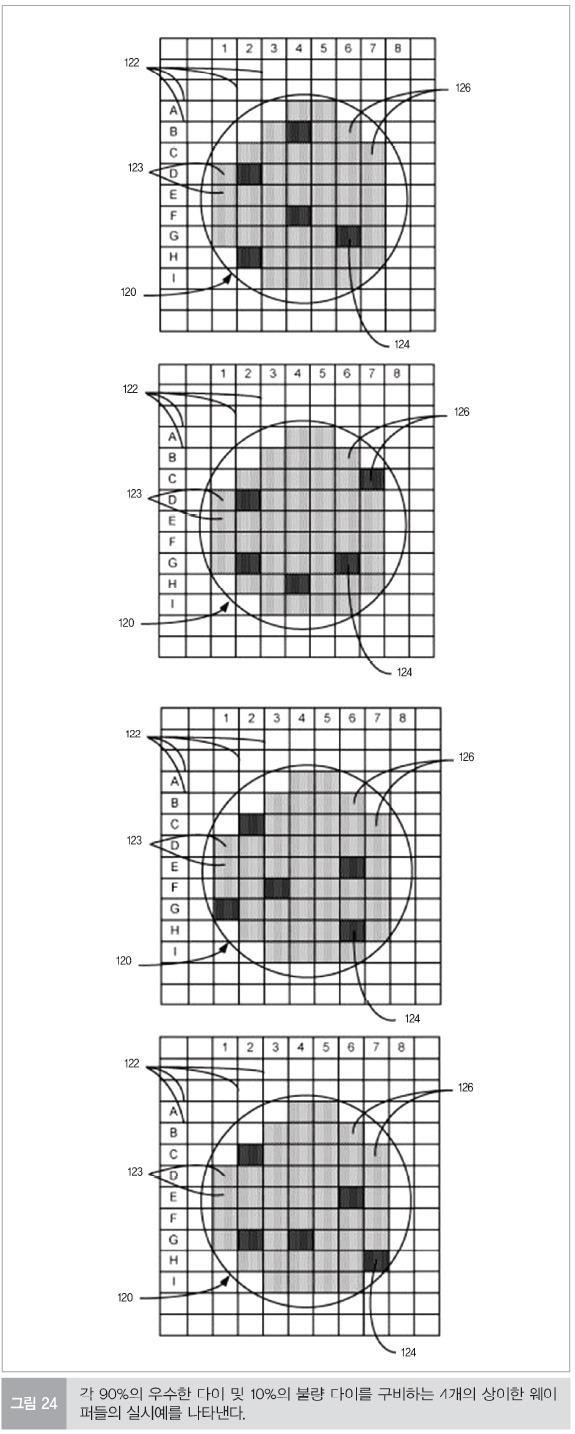

그림 24는 4개의 상이한 집적 회로 웨이퍼들(120)은 각각 불량 다이 영역들(123)의 10%를 갖는 50개의 다이 영역들(123)을 구비하는 실시예를 나타낸다. 집적 회로 웨이퍼들(120)이 개별적으로 다이싱(diced) 된다면, 우수한 다이가 선택될 수 있고, 적층 멀티칩 모듈들(61)에 대한 90%의 수율을 도출하는 다이 스케일 적층 기술을 사용하여 적층될 수 있다. 그러나 다이 스케일 적층 기술들을 사용하는 각 멀티칩 모듈(61)의 개별적인 공정에 대한 필요성은 50개의 적층된 멀티 칩 모듈들(61)이 일제히 처리되는 웨이퍼 스케일 상의 공정보다 훨씬 높은 비용의 공정을 형성한다.

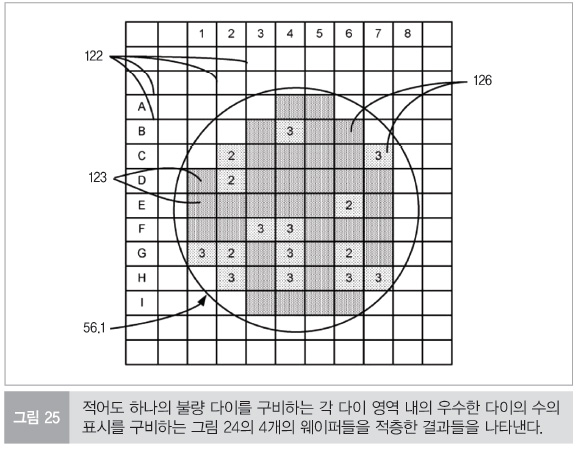

그림 24의 집적 회로 웨이퍼들(120)이 적층되어 그림 25의 제3 3차원 적층 웨이퍼(56.1)가 제공된다. 적층 웨이퍼(56.1)는 A-2 위치로 표시된 15개의 다이 영역들(123)을 구비하고, 4개의 적층 다이 중에서 2개 또는 3개는 우수한 다이로 표시하고, 4개의 적층 다이 중에서 3개는 우수한 다이로 표시한다. 표시하지 않은 것은 모든 레벨은 우수한 다이임을 표시한다. 배선 연결 기술 또는 TSV 와 같은 종래의 방식으로 4개의 상이한 집적 회로 웨이퍼들(120)이 적층되고, 서로 연결되며, 다이싱되어 공정된다면, 하나의 불량 다이를 구비하는 각 적층 멀티칩 모듈은 모든 다이가 우수한 적층 멀티칩 모듈에 대해 우수한 모든 다이의 필요성 때문에 결함으로서 거절되는 적층 멀티칩 모듈을 유발할 수 있다. 이러한 실시예에 있어서, 수율은 70%만이 우수한 적층 멀티칩 모듈들일 수 있다. 즉, 50개 중에서 35개이다. 그러나 상기 기술은 다이 스케일 적층 및 바로 위 단락에서 설명한 공정 기술들과 관련한 공정 비용들을 필요로 하지 않는다.

본 발명의 부분적으로 결함이 있는 적층 멀티-다이 모듈들(61)은 불완전한 다이로서 구분될 수 있다. 예를 들어, 각 다이(12)가 CPU의 하나의 코어(core)라면, 2개의 우수한 다이(12) 또는 3개의 코어 모듈(61)이 있거나, 3개의 우수한 다이(12)가 있을 경우, 불완전한 모듈(61)은 2개의 코어 모듈(61)로서 식별될 수 있다. 이와 유사하게, 각 다이가 1GB 메모리 다이일 경우, 케이스에 따라 불완전한 모듈들(61)은 3GB 메모리 모듈들 또는 2GB 메모리 모듈들로서 표시될 수 있다. 이러한 실시예에 있어서, 35개의 우수한 적층 멀티칩 모듈(61)이 있을 수 있으며 그러나 또한, 2개의 우수한 다이(12)를 구비하는 5개의 불완전한 모듈들(61) 및 3개의 우수한 다이(12)를 구비하는 10개의 불완전한 모듈들(61)이 존재할 수 있다. 여기서 설명하는 상호 연결 기술은 스택의 하나의 레벨 상의 단일 랜딩 패드에 도달하는 개별적인 커넥터들 때문에 스택 내의 결함이 있는 다이의 분리를 가능하게 한다. 다이를 적층하고 커넥터들을 형성하는 제조 공정 동안, 결함이 있는 다이는 구동 가능한 다이로부터 분리될 수 있고, 하나의 접근에 있어서, 커넥터들의 형성을 위한 마스크들을 사용하는 것은 각 스택 내의 결함이 있는 다이의 개수 및 위치들에 따라서 선택된다. 불완전 모듈(61) 구조를 가능하게 하는 것은 종래의 웨이퍼 스케일 공정 기술들에 비해 비용을 감소시키는데 도움이 된다.