| 최첨단 반도체 패키징 기술 C2W(Chip to Wafer), 하이브리드 본딩 기술 동향 |

|

|

|

| 2025-01 자료제공 : 인하대 제조혁신전문대학원 반도체 패키징 연구실 주승환 교수 |

|

|

고성능 소자 수요 증대, HBM5 이상 하이브리드 본딩 적용 확산 전망

신개념의 장비 개발, 구리 산화 및 표면 세척 등 난제 해결해야, 정부 지원 및 산학연 협력 시급

글로벌적인 인공지능(AI) 산업의 확장으로 HBM(high-bandwidth memory)의 수요가 급증하고 있다. HBM은 여러 개의 메모리를 수직으로 쌓아 올리는 3D 적층 구조를 채택하고 있으며, TSV(Through-Silicon Via) 기술을 통해 칩 간 연결하고 있다. 더 많이 쌓아 올리고, 더 빠른 칩간 연결을 위해 하이브리드 본딩 기술에 관한 관심이 매우 높아졌다. 글로벌 시장에서 우위를 선점하기 위해서는 50nm @ 3σ 미만, nm 급의 초정밀 설비 시스템과 Align 시스템 그리고 최상위 수준의 크린 룸 청정도와 진동 방지 시스템의 통합화에 대한 노력이 수반되어야 한다. 본고에서는 현재 하이브리드 본딩 기술에 대한 동향을 알아본다.

서론

인공지능(AI)의 발전으로 고집적, 고성능 칩에 대한 필요가 늘어나고 있는 시대이다. 현재 엔비디아의 최신 ‘블랙웰(Blackwell)’ 칩은 2025년까지 주문이 밀려있는 상황이다. 여기에 들어가는 고속 메모리칩인 HBM(고대역폭 메모리) 칩을 우리나라 SK하이닉스, 삼성전자가 마이크론과 더불어 선도하고 있다. HBM4E 12단 칩이 현재 양산이 되어 지난해 말 출시 예정인 블랙웰 칩에 장착이 되고 있고, 16단 HBM 칩의 개발이 끝나, 차기 엔비디아 칩에 퀄(장착 테스트)을 진행하고 있다는 이야기가 들리고 있다.

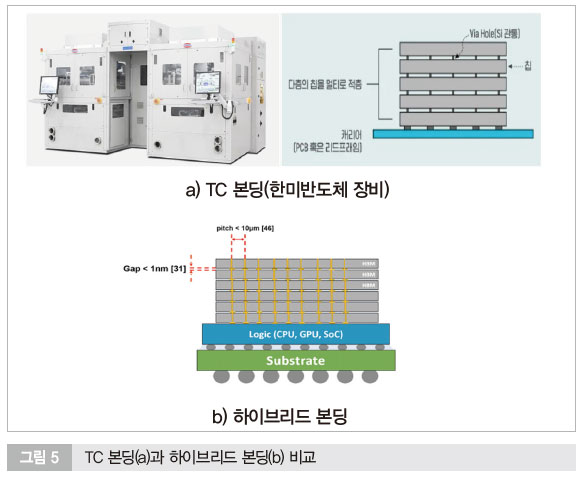

D램을 잘 쌓아 올려야 하는 HBM에서 칩간 접합을 위해 활용되고 있는 기술이 TC(Thermo-Compression, 열압축) 본딩 기술이고, 향후 HBM5 이상에서 사용될 미래 기술로 ‘하이브리드 본딩’ 기술이 주목받고 있다. 용량이 커지고 집적도가 높아지면서 칩의 본딩 간격이 줄어들고 있다. 기존 공정 방식으로 D램을 쌓는 데는 물리적 한계가 있다. 이것을 해결할 수 있는 솔루션이 하이브리드 본딩 기술이다. 고단의 HBM 공정에서 TC 본딩 사용이 불가능한 이유는 CTE(열팽창 계수) 불일치에 의한 휨 변형 때문이다. 이론적으로 변형과 응력의 열응력이 발생하여 피치가 약 7μm 이하에서는 사용이 불가능하다.

현재, HBM4 제조 기술은 SK하이닉스와 한미반도체의 TC 본더 장비가 앞서 나가고 있지만, 집적도가 높은 HBM5 이상에서는 TC 본딩 기술이 아닌 새로운 하이브리드 본딩 기술이 사용될 것이다. 이는 제조의 방식이 마이크로 범프를 사용하던 TC 본더에서 범프가 없는 완전히 다른 제조 방식으로 바뀌게 된다는 것을 의미한다. 이렇게 되면, 현재의 1등이 어떻게 될 지 예측이 안되는 상황이 될 것이다. 따라서, 이런 기술적 추이를 살펴보는 것도 앞으로 미래를 예측하는 좋은 방법이 될 수 있다.

반도체 패키징은 웨이퍼에서 제조된 칩과 부품을 패키징 기판에 수평 실장하는 FOWLP(Fan-Out Wafer Level package), FOPLP(Fan-Out Panel Level package) 기술이 등장하였고, SiP(System-in-Package), MCP(Multi-Chip Package) 등의 개념이 상용화되었다. 그럼으로써 현재 반도체 산업계에서는 반도체를 구성하는 웨이퍼, 칩, 메모리 등의 다양한 구성 요소들을 한정된 공간에 실장하고 있고, 이로 인한 많은 물리적인 제약과 문제가 발생하기 시작하였다.

이후 등장한 3차원(3D) 패키징 기술은 칩간의 간격을 최소 거리로 하고, 공간도 적게 차지하게 되어 새로운 해결 방식으로 여겨지고 있다. 3D 패키징은 수평적으로 칩을 연결하던 방식에서 진화하여 칩을 수직으로 적층하여 연결하는 기술로, HBM 메모리 소자와 같은 칩을 수직으로 적층하는 차세대 패키징 기술이다.

3D 패키징의 필요성이 높아지고 있는 것은 더 작은 고성능 전자 디바이스(HPC, AI, HBM)에 대한 수요 증가가 주된 요인이다. 또한 인공지능이 적용되는 다른 분야에서 혁신적인 응용 프로그램을 용이하게 한다. 고성능 소자에 대한 수요가 증가함에 따라 반도체 분야의 기업들은 이종집적 기술인 2.5D 및 3D 패키징, MR-MUF, 하이브리드 본딩 등 첨단 패키징 기술을 시도하고 있다.

이러한 기술은 더 높은 칩 집적도를 달성하는 데 필수적이지만 대량 생산 및 미세 피치 범프 연결의 문제는 여전히 남아 있다. 첨단 접합 기술은 반도체 산업을 발전시키기 위해 중요하다. 본고에서는 메스 리플로우(mass reflow), TC 본딩, 하이브리드 본딩을 포함한 칩 통합을 위한 3D 패키징 기술에 대해 설명한다.

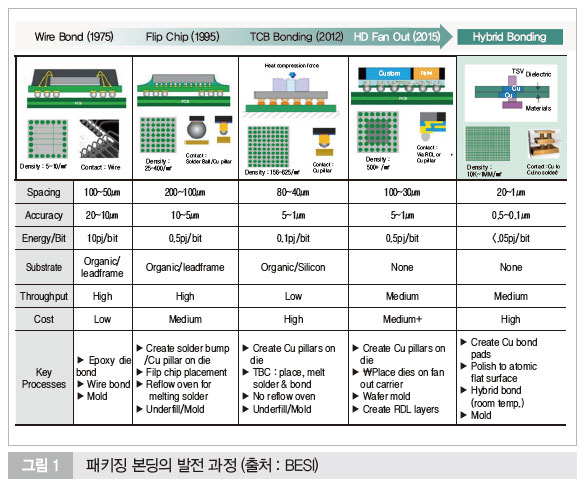

그림 1은 대표적인 본딩 전문 회사인 BESI社의 로드맵이다. TC 본딩은 Fluxless까지 갈 것으로 보이고, 한동안 TCB C2W(Chip to Wafer)와 하이브리드 본딩이 공존을 할 것으로 여겨진다. HBM4 16단이 TCB 본딩으로 개발이 되었다는 이야기가 있는 것으로 보아 그렇게 진행이 되어질 것으로 보이고, HBM 메모리 단은 16단으로 올리고 TCB 본딩을 적용하고, 로직 단의 연결은 하이브리드 본딩을 사용하는 하이브리드 형태로도 나올 가능성도 있다.

플립칩 본딩은 반도체 칩의 액티브한 부분이 있는 부문을 거꾸로 엎어서(Flip) 전극 부분에 범프(bump)를 연결하여 패키징 기판에 접합을 하여 연결하는 방식이다. 범프란 반도체 칩이나 통합 회로(IC)의 표면에 있는 작고 돌출된 솔더이다. 솔더를 기판의 전도성 전극 패드에 정렬시킨다. 정렬된 다수의 솔더는 리플로우(reflow) 오븐을 통해 칩과 칩을 접합시켜 전기적 및 기계적 연결을 용이하게 한다. 오븐에 투입하여 칩과 기판 사이의 다수의 범프를 접합할 수 있어 ‘대량 리플로우’ 혹은 ‘매스 리플로우’라고 말한다.

현재 반도체 패키징 산업계에서는 40~130μm 이하 피치의 범프를 사용하고 있다. 이외에도 40μm 이하 급 구리 돌기 범프(Cu pillar bump)를 사용하여 고밀도를 구현한다. 더 작아질 범프의 사이즈에 맞춰 새로운 범프 접합 공정 개발이 요구되고 있다.

반도체가 고집적화되고, 미세화되면서 피치가 보다 협소해졌고, 여기에 50μm 미만의 피치의 TSV(Through Si Via, 실리콘 관통 전극) 3D 칩 적층을 위한 Cu Pillar bump를 접합하기엔 기존의 리플로우 방식은 불가능하다. 거기에 대량 리플로우의 단점인 휨 현상(warpage)은 마이크로 범프에 적합하지 않을 수 있기 때문에 TC 본딩으로 대체되었다.

TC 본딩은 범프 피치의 감소 추세와 얇아진 다이로 인한 휨 현상 등의 문제를 가진 리플로우 공정의 대안 기술이다. TC 본딩은 부품을 열과 압력을 이용하여 서로 연결하는 장비로서, 반도체 공정에서 가공을 마친 웨이퍼에 개별 칩을 적층하는데 사용되는 장비이다. TC 본딩은 일반적으로 350~400℃의 높은 열과 100g/Bump의 압력이 사용된다.

최근에는 TSV 3D 집적 기술이 적용된 TSV TC 본더가 첨단 패키지 공정에서 적용되고 있다. TSV TC 본더는 AI 구동을 위한 차세대 반도체인 HBM 칩 생산의 핵심 장비로 HBM 수요 확대에 따라 그 수요가 증대되고 있다. 우리나라 대표적인 업체로는 한미반도체가 있고, HBM 본딩에서는 독보적이다. 이외에도 BESI, ASMPT 등이 있다.

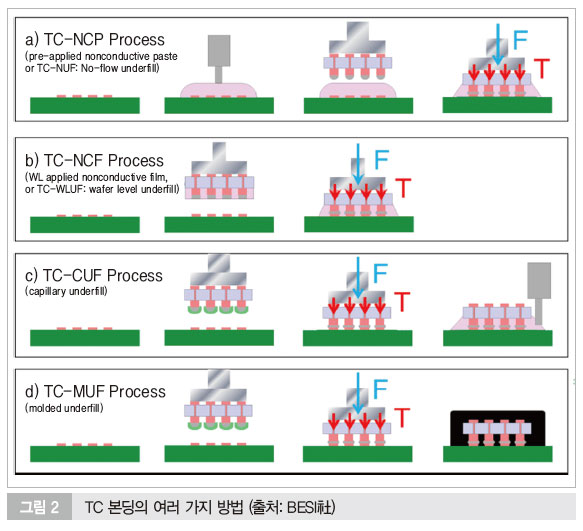

TC 본딩에는 보통 비(非) 도전성 페이스트(Non-Conduction Paste, NCP)나 필름(non-conductive Film, NCF)이 사용된다. NCP와 NCF는 칩과 다이 간의 접합시 접합보조제 역할을 하며, 기판과 다이 간의 열팽창계수(coefficient of thermal expansion) 차이로 인한 칩 휨 현상을 방지한다. 그러나 NCP는 페이스트 형태로 디스펜서를 통해 접합부에 도포되는데, 페이스트 두께 조절이 어렵다는 단점이 있다. 이에 반해 NCF는 기존의 페이스트 형태를 대체한 얇은 필름을 사용하여 두께 조절이 용이하고, 접합 불량률을 낮추는 장점이 있다.

현재 국내 글로벌 기업에서는 에폭시와 아크릴 소재의 NCF를 사용하여 열압착 접합을 진행하고 있으며, 특성을 더 개선 한 새로운 NCF를 HBM3에 적용 중이다. 이 방식은 Micro-bump interconnection이 요구되는 첨단 플립 칩 패키지 및 PoP(Package-on-Package) 유형의 패키징 구조에 적용할 수 있다. 그러나 열압착 접합의 가장 큰 단점인 낮은 생산속도 및 생산성과 높은 적층 수에 따른 칩 휨 현상이 해결해야 하는 과제로 남아 있다.

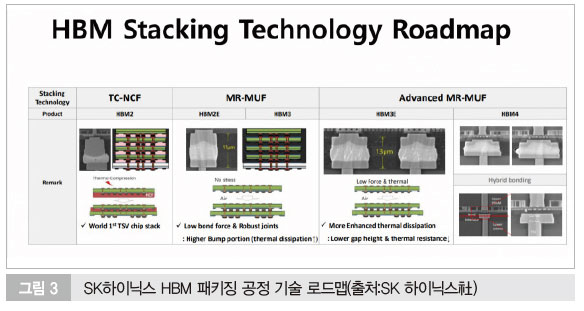

최근에는 SK하이닉스를 중심으로 이 문제점을 해결한 그림 2의 TC-MUF 방식의 MR-MUF(그림 3)라는 방식이 개발됐는데 삼성전자에 비해서 빨리 출시되어 시장의 각광을 받고 있다. 그림 2에서는 TC-MUF에 해당이 되나, 소재 및 여러 가지 공정 기술이 추가가 되었다. 양산에 성공한 ‘HBM3E’는 TSV와 구리 돌기 범프를 가진 12개의 DRAM을 13~15㎛ 간격으로 적층 및 접합하였으며, 새로운 접합 방식인 대량 리플로우-몰디드 언더필(Mass Reflow-Molded UnderFill, MR-MUF) 방식을 적용한 대표적인 사례이다.

기존의 대량 리플로우 방식과 TC 본딩 방식은 1024개 및 그 이상의 미세하고, 조밀한 범프를 연결하는 데 어려움이 있었으며, 긴 공정 시간, 낮은 생산성 등 여러 문제점을 안고 있다. 이에 반해 MR-MUF는 수많은 미세 범프에 균일하게 열을 전달 후, 이를 접합하여 범프-범프 간의 접합 신뢰성 향상 및 다수의 칩 적층 가능함을 보여주었다. 또한, 대량 리플로우 방식을 접목하여 생산성도 증대시킬 수 있는 방식이라는 점에서 반도체 장비 생산 산업계에서 많은 관심을 받고 있다.

최신 패키징 방식을 통한 이종집적 통합 고급 패키징 기술은 전자 디바이스의 지속적인 진화와 소형화를 실현하는 중요한 동인으로 부상했다. 성능, 전력, 면적 비용 및 시장 출시 시간(PPACt: performance, power, area-cost, and time-to-market) 영역에서는 3DIC(3D 집적 회로) 기술로 초점이 옮겨져 상당한 관심을 끌고 있다.

3D는 백엔드 패키지 프로세스의 한계를 넘어 silicon chip 통합 내에서도 이종집적 통합을 의미한다. 여기에서는 3DIC 제조를 위한 하이브리드 본딩 상호 연결 기술의 범위에 중점을 두고 첨단 패키지 상호 연결 기술 기술에 대한 포괄적인 설명을 한다.

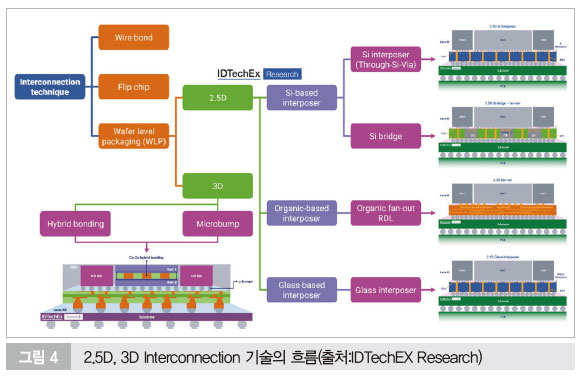

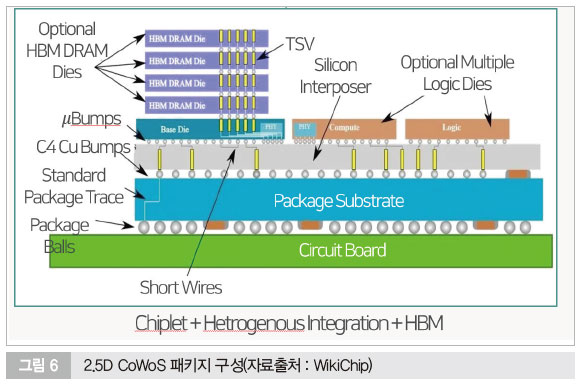

3D 패키징은 반도체 분야에서 다수의 통합 회로 또는 메모리와 같은 소자를 수직으로 적층하는 기술이다. 2D 패키징과 3D 패키징을 융합한 2.5D 패키징이 인터포저(interposer)를 사용하여 여러 소자 간에 고밀도 인터커넥션을 하였다면, 3D 패키징은 인터포저를 사용하지 않고, 로직과 메모리를 TSV를 통하여 직접 수직 적층한다. 이는 전력 소비 감소, 공간 효율성 증대에 따른 전체적인 성능 증가로 이어진다. 고성능 컴퓨팅이 기하급수적으로 증가함에 따라 이종집적은 각 영역에서 더 많은 로직, 메모리 및 특수 칩렛을 결합하여 컴퓨팅을 가속화하는 솔루션이 되었다. 하이브리드 본딩 상호 연결(HBI, 하이브리드 인터페이스)는 금속-금속 및 유전체-유전체 이산화규소(SiO2) 결합으로 정의되는 이종집적 통합 패키징에 대한 가장 중요한 기술 중 하나이다. 이를 통해 실리콘 칩에서 다른 칩으로 직접 금속 패드 대 패드 연결을 통해 연결할 수 있다. 이 기술은 접점 밀도를 높이고 구성 요소 간의 상호 연결 거리를 단축한다.

하이브리드 본딩의 주요 메커니즘은 표면 활성화, 표면 접촉, 압력 및 온도 조절, 확산 및 인터페이스 반응, Cu-Si 결합이다. 이렇게 형성된 결합은 우수한 열 전도성과 전기적, 기계적 강도, 다수의 I/O를 생성할 수 있다. 이는 같은 데이터 양을 전보다 더 빠르게 처리할 수 있게 된다는 것을 의미한다. 그러나 하이브리드 본딩의 신뢰성을 향상시키기 위해서 고려해야 할 여러 요소가 있다. 금속 대 금속 및 유전체 대 유전체의 접촉 계면의 특성과 더 넓은 반도체 패키징 응용 분야 요구 사항을 위해 저비용, 유기 유전체 기반, 낮은 공정 온도의 하이브리드 본딩 상호 연결을 수행하는 방법을 알아본다.

하이브리드 본딩 공정 시에 고려해야 할 점들로는 깨끗한 Cu(구리) 표면을 형성하기 위한 디싱(dishing)이나 Cu의 자연 산화 현상 및 접합부 간의 정밀한 정렬 문제 등이 있다. 매우 미세한 피치 마이크로 범프(18~25μm 피치)는 제품 소비를 위한 비용 효율적인 방법으로 실리콘 칩 간 상호 연결에 적용할 수 있다. 그러나 패키지 간 연결에서는 최첨단 패키지 기술 개발이 계속 진행 중이다.

최근에는 실리콘 칩 통합의 적용이 상당한 주목을 받고 있어 다양한 기능성 실리콘 구성 요소가 칩렛 통합으로 알려진 통합 실리콘 어셈블리로 결합될 수 있다. ‘칩렛’이라는 용어는 특정 기능을 가진 더 작은 크기의 집적 회로(IC)를 나타낸다. 고급 상호 연결 기술로 여러 칩렛을 조립할 수 있다. 이 경우 하이브리드 본딩 상호 연결이라는 고유한 기술 논리는 기존의 구리 마이크로 범프에 비해 더 미세한 피치와 더 낮은 대기 시간의 요구 사항을 위해 개발되었다. 하이브리드 본딩 상호 연결을 통해 직접 금속 패드 대 패드 연결로 실리콘 칩에서 다른 칩으로 연결을 가능하게 한다. 여기서 ‘하이브리드’는 본딩 인터페이스에 금속-금속 및 유전체-유전체가 포함됨을 의미한다. 연결 패드 피치는 마이크로 범프에 의해 만들어진 것보다 더 줄일 수 있다.

하이브리드 본딩 상호 연결 방법은 칩렛 간의 데이터 처리량을 증가시킬 수 있다. 모놀리식 칩과 달리 칩렛은 특정 기능에 따라 칩을 조립한다. 이 개념은 기본적으로 SoC(System on Chip)의 기능적 분할을 기반으로 한다. 고유한 I/O 프로토콜을 특징으로 하는 실리콘 칩은 프론트엔드 패키징 프로세스를 사용하여 상호 연결할 수 있다.

예상되는 개발은 모놀리식 칩 내의 수준에서 파티셔닝을 가능하게 하는 것을 가리키며, 이는 3D 시스템 온 칩(3D-SoC) 파티셔닝으로 나타난다. 그림 6은 2.5D(로컬 고대역폭 메모리와 광 트랜시버 모듈을 연결하는 인터포저) 및 3D(적층 메모리 및 적층 성능 다이) 통합이 있는 고성능 컴퓨팅 시스템과 주요 상호 연결 구조를 보여준다. 이 접근 방식은 여러 별개의 기능 칩의 생성을 용이하게 하며, 별도의 인터포저라는 웨이퍼에 제조된다.

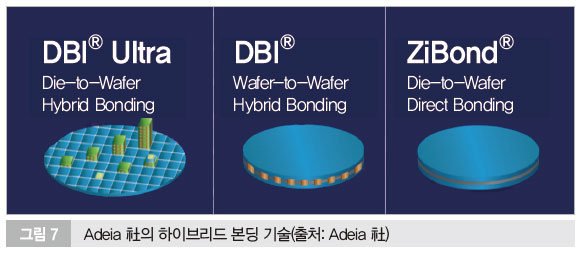

하이브리드 본딩의 개념을 특허로 가지고 있는 Adeia社의 내용을 보면 크게 3가지로 나눌 수 있다. TC본딩의 경우는 Cu-Cu 범프없이 직접 연결하는 본딩으로 300℃ 이상의 고온에서 작업을 하므로, 칩이 손상이 될 수 있다. 반면 HB본딩은 낮은 힘과 실온 가공이 가능한 기술이다. 그림 7은 DBI Ultra 기술로, W2W(Wafer to Wafer) 하이브리드 본딩 방식이다. 이것은 Sony社의 이미지 센서에서 대량생산(HVM)이 되었고, 성숙된 기술이다.

현재 미성숙이 되어 있고, 현재 HBM 등에 적용하려는 기술이 D2W(Die to Wafer)=C2W(Chip to Wafer), D2D(Die to Die)=C2C(Chip to Chip) 이다. 현재는 아직 시장에 적용을 하려는 기술이고, 현재 대량 생산에 들어가지는 않았다.

현재의 기술 현황은 iMEC 연구소에서 발표한 자료를 보면 알 수 있다. 솔더 범프는 5um, D2W HB는 2um, W2W HB는 500nm까지 연결한 연구 결과가 있다.

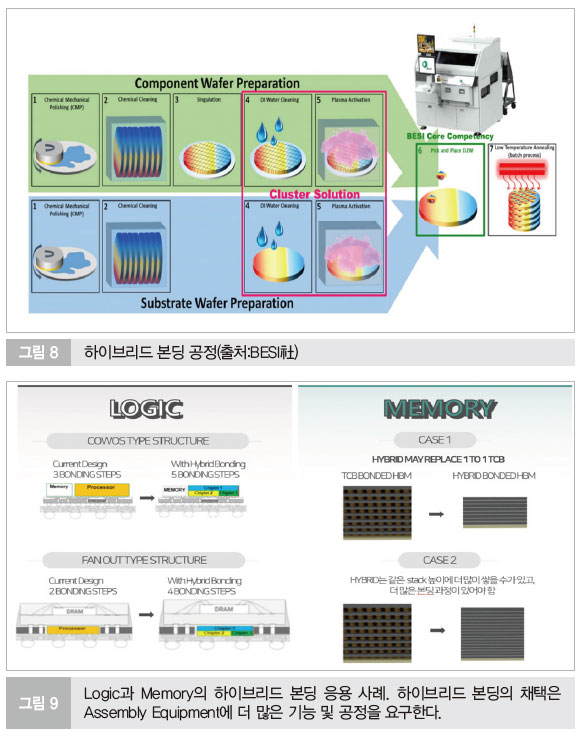

하이브리드 본딩 공정은 여러 공정이 혼합된 공정이고, 크게 웨이퍼를 준비하는 공정과 D2W 본딩과 어닐링 공정으로 나누어진다.

표 1에서는 대표적인 하이브리드 본딩 장비 업체를 소개하고 있다. 장비 업체는 W2W 본딩을 주로 하는 EVG社와 SUSS社가 있고, D2W 장비를 개발하는 회사는 크게 3군데가 있다. BESI(AMAT), ASMPT(EVG), SET(SUSS) 社가 있다. 괄호안에 있는 업체는 전처리 공정, CMP, 세정 공정을 공동으로 개발하는 업체이다.

일반적으로 하이브리드 본딩 장비의 정보는 구하기가 어려운데, SET社는 구매가 가능하고, 자료도 비교적 공개적으로 많이 제공을 한다. SET社는 본더 전문 업체로 SUSS社의 전처리 장비와 결합하여 공정 전체적인 솔루션을 제공한다. 국내에 공급이 가능하고, ‘NeoHB’ 라는 모델로 판매하고 있다. 이 제품에 대한 세미나를 2024년 11월 20일 인하대에서 진행하였다. 하이브리드 본딩 세미나는 5회에 걸쳐서 인하대에서 진행이 되었다.

장비 기술 개발에서 현재 가장 큰 난제는 200nm 미만의 전례 없는 배치 정확도와 같은 심각한 기술적 문제가 있다. 최종 목표는 50nm이다. um 단위도 아닌 nm 단위에서 구현해야 한다. 특히, 용어도 생소한 50nm @ 3σ의 조건을 충족해야 한다. 이점은 전체 시스템에 대한 완전히 다른 새로운 변화를 의미한다. 현재 국내 하이브리드 본딩 장비 업체의 교육 및 새로운 시스템에 대한 연구가 절실한 실정이다. 인하대는 하이브리드 본딩 시스템 개발을 시작하여 보급할 계획이다.

또 다른 난제로는 최첨단 고신뢰성의 고정밀 시스템 확보가 제한적이다. 기존 기술을 사용하는 최고의 기술인 1um xy 시스템이 필요하다. 최고 수준의 모터 제어시스템 기술과 새로운 nm의 정밀 기술이 필요하다. 또한, Align 시스템도 nm 단위로 새롭게 개발이 되어야 하며, 진동 및 cleanness도 Class 1 급으로 되어야 하는 점이 기술적인 난제이다. 현재의 업체 단독으로 해결하기가 벅찬 내용이다.

설비 기술이 해결이 되면 통합성, 생산속도, UPH가 높아야 하는데, 현재는 BESI社가 2,000UPH로 가장 빠른 것으로 알려져 있다.

최근에는 공정에서 새로운 연구가 많이 진행되고 있는데, 친수성 물질들의 특성인 자기정렬(self alignment) 효과를 이용해 Cu-Cu와 Cu-wafer의 접합 메커니즘을 제시하는 연구가 발표되기도 했다. 이를 통해 접합 온도를 200℃까지 낮추었으며, 결과적으로 3D 패키징에서 요구되는 최소 접합 계면 에너지인 5 J/m2보다 2배 높은 10.69 J/m2의 접합 계면 에너지를 얻었다. 그러나 하이브리드 본딩을 하기 위해서 구리 표면의 빠른 산화 문제, 깨끗한 구리 표면을 만들기 위한 세척 문제, 결합 강도 및 저온 접합과 접합부의 정렬 문제 등이 해결이 되어야 한다.

3D 칩 적층을 위한 하이브리드 본딩 패키징에 대하여 최근 동향을 조사한 결과 2020년 Xperi(현재 Adeia)社는 SK하이닉스와 2.5D 및 3D 패키징 등 차세대 메모리 반도체 개발을 위한 ‘DBI(Direct Bond Interface) Ultra’ 계약을 체결한 사례가 있다. 현재는 공정 분야의 연구가 많이 되고 있는데, 장비 개발에 대한 연구도 진행하여야 할 것으로 여겨진다.

HBM 제조용 TC 본딩 공정에서 C2C 분야의 경쟁력을 가진 한국의 업체가 등장해 SK하이닉스뿐만 아니라, 마이크론이라는 해외 반도체 회사에도 판매를 해야 한다. 이 기술을 기반으로 하이브리드 본딩 장비 국산화에 성공해 글로벌 시장에 중심이 되어야 한다. 이 목표를 달성하기 위해서는 용어도 생소하고 어려운 50nm @ 3σ 불확실성 미만에 해당하는 정밀도를 맞추어야 하는데, 이는 기존의 인력이나 기술로는 불가능하고, 앞에서 언급한 새로운 nm 급 정밀 기계 시스템에 대한 교육과 장비 시스템 부품 개발 및 Align, 최고 사양의 크린 룸 청정도와 진동 방지 시스템의 통합화에 대한 노력이 수반되어야 한다. 이를 위해 정부와 학계의 지원이 절실한 실정이다. 새로운 정밀 장비 시대에 맞추어 세계 최고의 장비 기술을 근간으로 둔 글로벌 장비 회사의 탄생이 가능하다.

인하대 제조혁신전문대학원 주승환 교수 연구실에서는 현재, 하이브리드 장비 개발을 위한 기초 연구와 장비 설계가 진행 중이다, 소·부·장 기업과 학교, 연구소 간 유기적인 협력 체계를 구축해 세계적인 장비 회사의 탄생에 일익을 담당하도록 노력하겠다. 기업체와 공동 개발을 추진하고 있으니 협력 가능한 업체는 많은 연락을 바란다. |

| [저작권자(c)SG미디어. 무단전재-재배포금지] |

|

|

|

|