사용 재료의 인장응력 특성을 먼저 알아야

솔더 조인트의 피로수명 감소와 밀접한 관계가 있어

열악한 사용자 환경에서의 보호를 목적으로 전자기기 어셈블리 공정에서는 서로 다른 기계적 및 열적 특성을 가진 다양한 고분자 재료를 사용하고 있다. 그러나 열팽창(CTE, coefficient of thermal expansion) 계수 및 탄성 계수와 같은 기계적 성질의 차이가 전자기기의 신뢰성에 장기적으로 불확실성을 가미하기 때문에 재료 선정 공정에 영향을 끼친다. 일반적으로 주요 신뢰성 문제는 전자 부품의 많은 고장을 유발하는 솔더 조인트 피로(solder joint fatigue)이다. 따라서 신뢰성을 예측할 때 솔더 조인트에 대한 폴리머 캡슐화(코팅, 포팅(potting) 및 언더필)가 미치는 영향을 이해하는 것이 필요하다.

열악한 사용자 환경에서의 보호를 목적으로 전자기기 어셈블리 공정에서는 서로 다른 기계적 및 열적 특성을 가진 다양한 고분자 재료를 사용하고 있다. 그러나 열팽창(CTE, coefficient of thermal expansion) 계수 및 탄성 계수와 같은 기계적 성질의 차이가 전자기기의 신뢰성에 장기적으로 불확실성을 가미하기 때문에 재료 선정 공정에 영향을 끼친다. 일반적으로 주요 신뢰성 문제는 전자 부품의 많은 고장을 유발하는 솔더 조인트 피로(solder joint fatigue)이다. 따라서 신뢰성을 예측할 때 솔더 조인트에 대한 폴리머 캡슐화(코팅, 포팅(potting) 및 언더필)가 미치는 영향을 이해하는 것이 필요하다. 폴리머 캡슐화의 열팽창으로 인해 솔더 내에 인장응력이 존재할 때 피로 수명이 크게 줄어드는 것으로 나타났다. 인장응력을 지니고 있다는 것은 솔더 조인트를 반복적인 다축응력상태(multi-axial stress state)에 놓이게 한다는 의미이고, 이는 종래의 반복 전단 하중보다 더 피해를 준다고 밝혀졌다. 마이크로 전자 솔더 조인트의 피로 수명 감소에 미치는 영향을 이해하려면 인장응력 성분특성을 구분해야 할 필요가 있다. 따라서 무연 솔더 조인트에 변동하는 인장응력 조건을 다루기 위해 특별한 시편을 제작하였다. 본고에서는 열역학적 인장 피로 시편의 구성 및 검증을 제시한다. 솔더링 조인트에 가해지는 인장응력의 크기를 변화시키기 위해 열 사이클링 범위를 포팅의 팽창 특성과 일치시켰다. 솔더 조인트 형상은 단순 응력 상태를 유지하면서 BGA 및 QFN 솔더 조인트와 관련이 있는 척도 인자로 설계하였다. 다양한 포팅 재료 특성에 있어서 열팽창 동안 솔더 조인트의 응력-변형 거동을 관찰하기 위해 FEA 모델링을 수행하였다. 솔더 조인트에서 축방향 응력의 크기는 열 사이클의 피크 온도와 함께 열팽창 계수와 탄성 계수 모두에 의존하는 것으로 나타났다. 시편의 열 사이클링 결과는 다양한 팽창 특성을 지닌 포팅 재료의 열팽창으로 인해 솔더 조인트에서 발생하는 인장응력의 크기를 연관시키는데 도움이 되고, 캡슐화된 전자 패키지에서 솔더 조인트의 낮은 사이클 피로 수명에 대한 새로운 통찰을 제공할 것이다.

소개

다수의 전자 부품 고장은 솔더 조인트 피로 고장에서 기인하는 경우가 많다. 우주 항공, 자동차, 산업 및 일반 소비재 애플리케이션에서 많은 전자 부품은 솔더 조인트에 열역학적 피로(TMF) 조건의 대상이 되는 변덕스러운 온도에서 동작한다. 전자 어셈블리의 솔더 피로는 부품과 PBC 사이의 온도 변화와 열팽창 계수(CTE) 불일치의 정점에 있다. 온도가 변화하는 동안, PCB와 부품 간의 CTE 차이는 전단 하중 하에서 솔더 조인트를 차례대로 누르는 차등 재료 팽창(differential material expansion)을 유발한다. CSP의 솔더 조인트에 가해지는 전단 변형을 줄이기 위해 다양한 언더필 재료가 솔더 조인트의 변형을 제한하기 위해 사용되고 있다. 플립칩 패키지와 같은 다이 레벨 솔더 인터커넥트는 특히 열팽창 응력을 재분배하여 솔더 범프에 가해지는 변형을 제한함으로써 언더필의 이점을 얻는다.

전단 변형을 제한하는 것 외에도 언더필 팽창으로 BGA 솔더 조인트에서 큰 일반 변형이 발생하는 것으로 나타났다. Kwak 등은 열 사이클링을 거친 솔더 조인트의 변형률을 측정하기 위해 광학 현미경을 이용한 2D DIC 기술을 사용하였다.[1] 그들은 CTE가 30ppm/℃이고 유리전이온도(Tg)가 80℃인 언더필이 100℃ 온도에서 6000με의 평균 정상 변형을 생성할 수 있음을 발견했다. 이러한 높은 일반 변형률은 전단 변형이 BGA 패키지 내에서 일어나는 것처럼 중립점까지의 거리에 동일하게 의존하지 않았다. 일반 변형의 크기는 CTE, 탄성 계수(E), 패키지 크기 및 온도에 따라 달라지는 복합적인 의존성을 갖고 있다. 일반 변형의 추가는 전단과 축 변형의 조합 하에서 솔더 조인트를 누르고, 이로 인해 온도 변화 중에 솔더 조인트가 불-비례 반복 하중(cyclic loading)을 차례대로 받게 된다.

대형 축 변형을 제한하려면, 국부적인 불일치를 줄이기 위해 low-CTE 언더필이 선택되어야만 한다. 이전의 연구에 따르면, 언더필 CTE와 솔더의 CTE가 거의 일치하면 언더필되지 않은 부품에 비해 패키지 신뢰성이 2배까지 늘어난다,[2] 현재 수치적 연구에서는 특정 언더필 재료를 추가하면 BGA 솔더 조인트의 수명이 실험에서 입증된 것보다 훨씬 더 연장될 수 있음을 예상했다. 실험 데이터에서의 편차 이유는 피로 수명 모델에 존재하는 데미지 파라미터 기여도에 대한 응력 및 변형 상태를 잘못 해석했기 때문이다. 언더필 팽창 동안, 평균 인장 또는 압축 응력이 기존 전단 변형에 추가될 수 있다. 대부분의 무연 솔더에 대한 반복적인 실험에서 포지티브한 인장응력을 추가하면 피로 수명이 크게 단축되는 것으로 나타났다.

Liang 등은 SAC305 솔더에서 일정한 축방향 응력을 가함에 따른 뒤틀림 피로 실험을 수행한 결과, 반복 전단 하중에 6MPa의 일정한 축방향 응력을 추가하면 0.34% 전단 변형률 범주에서 14배, 0.36% 전단 변형률 범주의 경우 4배로 피로 수명이 감소함을 발견했다.[3] 상온에서 SAC305의 피로 수명은 래칫 변형률(ratcheting strain rate)과 관계가 있는 것으로 나타났으며, 낮은 축 응력 또는 변형을 포괄하면 고장 시간을 크게 줄일 수 있는 높은 래칫 변형을 유발할 수 있다.[4] 고온에서, 래칫 파괴 현상이 발생하여 솔더의 반복적인 크리프 거동으로 인해 더 이상 래칭 변형이 누적되지 않는다. 솔더 합금에서 래칫 파괴가 발생하는 정확한 온도는 조사되지 않았으며 TMF 수명에 미치는 영향은 알려지지 않았다.

무연 솔더에서 래칫 변형률에 대한 온도 영향의 불확실성 외에도, 벌크 및 매크로 스케일 솔더 조인트의 크기 의존적 미세 구조의 차이로 인해 피로 특성이 달라질 수 있다. Andersson 등은 벌크 및 마크로 스케일 솔더 조인트에서 등온 피로 실험을 수행했으며 낮은 변형률 범위와 높은 변형률 범위에서 역 피로 수명 성능을 관찰했다.[5] 연구 결과를 조종할 수 있는 중요한 요인은 반복적인 실험에 사용된 변형 유형이었다. 벌크 솔더는 반복 인장/압축으로 테스트하였고, 솔더 조인트는 반복 전단 하중 하에서 테스트하였다. 솔더 합금의 피로 균열 전파 속도는 형상, 금속 간 레이어 두께 및 하중 모드에 의존하는 것으로 알려져 있다.[6]

솔더의 신뢰성에 대한 축방향 응력의 기여도를 평가하기 위해 온전한 축방향 하중 모드에서 솔더 조인트의 피로 수명을 조사해야 할 필요가 있었다. 온전한 축방향 하중의 TMF 조건 하에서 매크로 스케일 솔더 조인트를 실험적으로 처리하기 위해 새로운 테스트 쿠폰을 고안하였다. 테스트 쿠폰은 잠재적인 전단 변형을 피하고, 열팽창 동안 축 변위가 용이하도록 포팅 재료를 사용하여 두 PCB 사이의 솔더 조인트 그리드를 누르는 구조로 구성하였다. 두 PCB 사이의 공간은 CSP의 공간보다 훨씬 더 큰 간격으로 설계하였기에 갭 충진에 사용되는 충진재는 언더필 재료에만 국한을 두지 않았다.

본 고에서는 열 사이클링 동안 재료 팽창으로 인한 CTE 불일치 구동 인장 하중을 재현하기 위해 설계된 시편의 개발 과정을 제시한다. 시편은 재료의 CTE 불일치에 의해 일어나는 축방향 하중을 유도하기 위해 제작했다. 시편의 단계별 시공 절차는 의도된 기능을 향상하기 위해 제작된 설계 반복과 관련하여 함께 제시하였다. 응력 및 변형 솔더 조인트 발생의 양과의 연관성을 보여주기 위해 분석용 변위 호환성 방정식을 사용하여 각 포팅 재료에 적절한 열 사이클링 범위를 선택했다. 다양한 유리전이온도(Tg)를 지닌 포팅 재료를 선정하여 열적으로 안정적으로 거동하는 포팅 재료와 비교해 그 범위에 걸쳐 열 사이클링 할 때 솔더에서의 응력을 평가했다. 유한요소법(Finite element model, FEM)을 사용하여 솔더 조인트의 변형을 포착하였고 응력-변형 상태를 다양한 온도에서의 포팅 재료 특성과 연관시켰다. 실험 결과는 캡슐화된 어셈블리에서 솔더 조인트의 TMF 수명에 관한 축방향 하중이 미치는 영향을 이해하는데 사용될 수 있다.

재료 선택

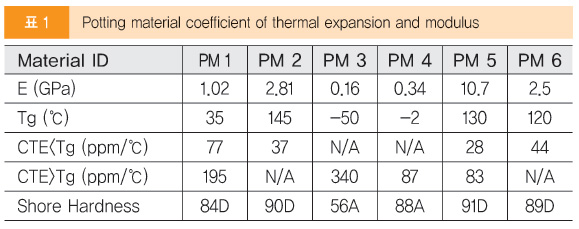

온도 변화에 따라 응력 레벨을 변이시키기 위해서는 재료의 CTE와 E 모두를 제어하는 것이 바람직하다. 선정된 재료는 전자 제품에서 포팅, 언더필, 컨포멀 코팅 및 일반 캡슐화에 가용 되는 상업용 열경화성 에폭시, 아크릴 및 폴리우레탄이다. 표 1에 나타낸 바와 같이 다양한 특성을 갖는 6개의 재료를 초기에 선택하였다. Tg의 범위와 경도 값을 갖는 물질을 CTE와 E의 상이한 조합과 함께 선택하였다.

에폭시계 포팅 재료는 유리전이온도(Tg) 이상의 온도에서 높은 CTE를 나타냈다. 낮은 CTE 에폭시를 Tg 초과한 온도로 가열할 때, 큰 팽창이 나타나고, 솔더 조인트에 과도한 굽힘과 일반 응력을 가하여 부품 고장을 가속화할 수 있다.[7] 이는 재료가 계수의 감소에 상응하지 않는 자체 Tg에 근접함에 따라 CTE가 빠르게 증가하는 게 원인이다. 이 지연현상은 중합체의 CTE가 자유 부피(free volume)의 변화에 의해 발생하는 반면, 계수의 변화는 중합체 사슬의 병진 및 회전 운동(translational and rotational movements)의 증가에 의해 나타난다.

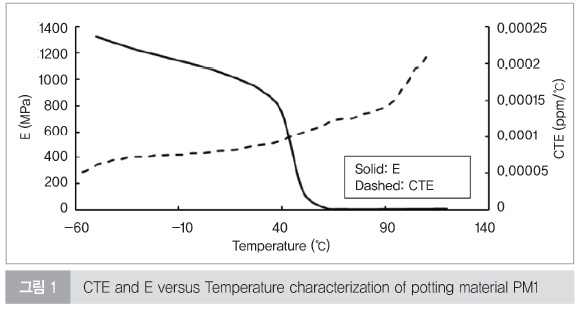

포팅 재료 PM 1에 관한 동역학측정장치(DMA) 및 열역학측정장치(TMA) 분석을 수행하여 Tg, 탄성 계수(E) 및 CTE 값을 획득하였다. 그림 1에서는 Tg 근처에서 재료의 E 값과 CTE가 급격하게 변화하는 것을 보여주고 있다. 데이터에 따르면 실제 재료의 CTE는 표준 테스트 온도 프로파일 내내 400% 정도 차이날 수 있다. 언급해야 할 중요한 점은 제조업체가 제공한 E 및 CTE 값이 전체 온도 범주에서 평균으로 간주했다는 것이다. 자체 유리전이온도와 의도된 동작 온도를 고려하지 않고 포팅 재료를 선정하면, 솔더 조인트의 응력이 늘어날 수 있고, 부품 신뢰성이 20% 이상 줄어들 수 있다.[8] High-Tg의 포팅 재료의 경우, 경도계를 사용하여 Tg 미만의 온도 범주에서 재료 경도를 측정했다. 원하는 시험 온도에서 일정한 경도 값이 발견되었으며 Tg 미만에서 재료 특성의 열 안정성을 입증하였다.

쿠폰 디자인

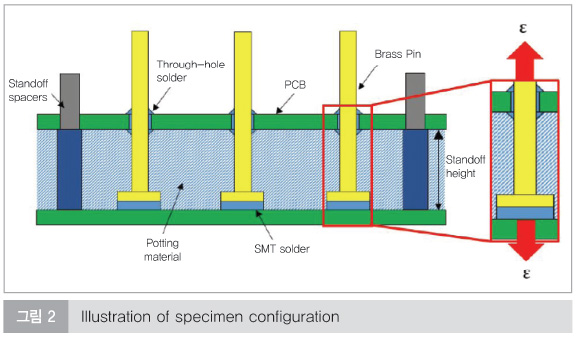

시편 제작의 목적은 CTE 불일치 구동 TMF의 고유 특성에서 비롯되었다. 다양한 언더필 재료의 특성을 가지고 서로 다른 크기의 부품을 테스트할 경우 몇 가지 테스트 파라미터만 변경하면 되지만, 솔더 조인트의 피로 수명에 영향을 미치는 외부 요인을 실제로 제어할 수는 없다. 전단 변형은 항상 테스트 항목에 들어가 있기 때문에 솔더 조인트 주위의 상단과 하단 표면에 PCB를 배치하여 PCB와 부품의 전체 CTE 불일치를 제거하는데 중점을 둔 대체 테스트 방법을 제안하였다. 언더필을 사용한 칩 스케일 테스트에서 응력 레벨에 영향을 미치는 가장 중요한 두 가지 파라미터는 리플로우 된 솔더 구의 스탠드오프 높이와 부품 크기이다. 응력 또는 변형 레벨을 제어하기 위해 시편에서는 그림 2와 같이 조절 가능한 스탠드오프 높이로 설계하였다. 스탠드오프 높이는 표면실장된 솔더 조인트를 이용하여 하부 PCB에 연결된 상태에서 상부 PCB에 부착된 비아 쓰루홀 솔더 조인트를 제어하였다. PCB와 솔더 조인트 사이의 인터포저로써 황동 단자 핀을 선택하였다. 포팅 재료는 두 회로 보드 사이 그리고 솔더 조인트 및 핀 주위의 틈에 채워 넣었다.

PCB 설계는 NSMD(non-solder mask defined) 패드와 OSP 표면처리된 양면 2레이어 보드를 활용하였다. 보드 두께는 1.6mm이다. 표면 실장 패드 사이의 간격은 6.35mm이다. 시편의 전체 길이와 너비는 각각 89mm와 25mm였다. 트레이스는 각 쓰루홀 조인트로 라우팅하였고, 모든 표면실장 패드는 공통 접지로 라우팅하였다. PCB는 제조 비용과 복잡성을 낮추기 위해 시편의 양면에 싱글 보드 디자인을 사용할 수 있도록 설계하였다. 표면실장 패드와 도금 된 쓰루홀은 각 row에 11개의 핀 중 3개의 row에서 상호 교체 가능하게 배치하였다. 스탠드오프 커넥터를 고정하기 위해 각 모서리에 4.3mm 직경의 구멍 4개를 뚫었다. 스탠드오프 높이는 두 보드 사이의 공간에 채워지는 포팅 양을 규정하는 데 사용된다. 표면실장 솔더 조인트는 5mil 두께의 프레임 스텐실을 사용하여 SAC305 솔더페이스트로 인쇄하였다. 쓰루홀 조인트는 SN96 솔더 와이어를 사용하여 수납땜하였다.

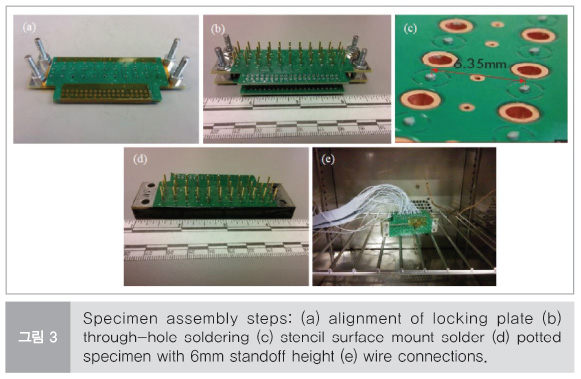

SMT 솔더 조인트를 쓰루홀 연결부에 연결하고 포팅 팽창 도중 견고한 인터페이스를 제공하기 위해 네일 헤드(Nail head) 타입의 황동 터미널 핀을 사용하였다. 황동 핀의 전체 길이는 16.87mm이며 테두리 직경은 1.50mm이다. 리플로우 동안 금 도금된 테두리의 측면 사이에서 발생하는 솔더페이스트의 습윤을 방지하기 위해 사포(400 grit sandpaper)를 사용하여 접합면에 직각으로 된 금 마감 층을 제거한다. 테두리 측면을 샌딩하여 리플로우 동안에 바닥면의 금 마감재를 유지하면서 언더코트(undercoat)된 니켈 레이어를 노출하는 금 표면마감재를 제거하였다. 시편의 어셈블리 절차는 그림 3과 같이 오류를 최소화하고 일관성과 재현성을 유지하기 위해 몇 단계로 진행하였다. 첫 번째 단계는 핀 테두리에 맞춰 잠금 플레이트(locking plate)을 정렬하는 것으로 구성되었다. 잠금 플레이트는 핀 테두리의 직경과 일치하도록 표면실장 패드가 뚫린 유사한 PCB로 만들었다.

그런 다음 폴리이미드 테이프의 레이어를 픽쳐 패드 밑면에서 위쪽을 향하게 놓았다. 이 형태는 픽쳐 내부로 테두리의 바닥을 고정하고, 핀의 이동을 제한하는데 도움이 되었다. 핀을 잠금 플레이트에 고정한 후, 쓰루홀 조인트의 솔더링 동안에 이동하는 것을 예방하기 위해 상부 PCB를 제자리에 삽입하여 고정시켰다. 각 쓰루홀은 솔더 와이어를 사용하여 수납땜하였다.

세 번째 단계에서 SAC305 솔더페이스트를 5mil 두께의 스텐실을 이용하여 하단 보드의 구리 패드에 인쇄하였다. 패드와 핀 테두리 사이에서 솔더페이스트가 리플로우되도록 충분한 간격을 만들기 위해 5mil 두께의 정밀 와셔(precision washer)를 스탠드오프 스페이서와 함께 배치했다. 핀과 패드 사이의 최종 간격은 스텐실 솔더페이스트 높이보다 약 2mil 더 크게 했다. 쓰루홀 솔더 조인트가 2차 리플로우 프로세스를 겪기 때문에 더 커진 간격은 리플로우 동안에 솔더페이스트로 내려갈 수 있도록 핀에 충분한 공간을 제공한다.

리플로우 작업 후, 과도한 보이드 현상과 습윤 이슈를 검출하기 위해 X-선 이미징을 사용하여 시편을 검사하였다. 검사 이후, 경화 중 포팅 재료를 안전하게 잡기 위해 폴리이미드 테이프로 시편의 3면을 감쌌다. 솔더 내 잔사 크리프 변형의 축적을 방지하고, 에폭시 경화 중 발열 온도를 회피하기 위해서 선정된 각각의 포팅 재료들을 권장된 최저 온도에서 경화시켰다. 4mm, 6mm 및 12mm 3개의 스탠드오프 높이를 처음에 선택하였다. 스탠드오프 높이는 포팅의 열팽창 동안 변위 범위를 규정하고 쓰루홀과 표면실장 조인트 양쪽에 변위 제어 하중 조건을 매길 수 있는 포팅 높이 제어를 가능하게 한다. 리플로우된 표면실장 솔더 패드는 황동 테두리의 접촉면과 일치하는 120㎛의 평균 높이와 1.5mm의 직경을 가지고 있었다. 솔더 패드의 높이는 기록된 평균 값에서 ±40㎛로 다양했다. 해당 PCB를 통해 열 사이클링 동안 각 핀의 저항을 측정하였고, 각 시편에서 33개의 개별 솔더 조인트에 대한 사이클 횟수를 파악하였다.

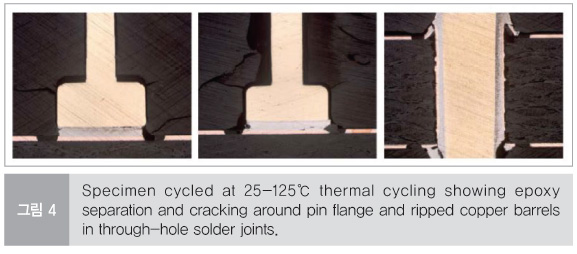

온도 범위를 선택하면 열 사이클링 동안 솔더 조인트의 응력 변형 상태를 제어할 수 있다. 평균적인 반복 온도를 실온 초과 혹은 미만의 범위로 조정하면, 인장 또는 압축 평균 변형률이 켜졌다. PM1 포팅 재료가 사용된 시편을 우발적인 고장과 비슷한 고장이 가속화되는 100℃의 온도 범위에서 12mm 스탠드오프 높이로 테스트하였다. 그림 4에 표시된 시편의 종단면은 솔더 표면실장 패드 내의 균열과 함께 쓰루홀 구리 배럴 내에서 구리 레이어의 오류를 나타냅니다. 광범위한 에폭시 균열이 시편의 중앙에서 관찰되었고, 솔더 조인트와 황동 핀에서 에폭시의 큰 분리가 관찰되었다.

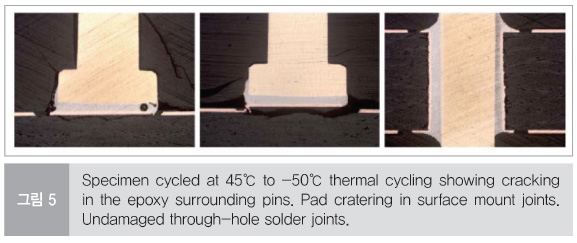

선정한 열 사이클은 PM 1의 Tg를 가로질러 FR4 라미네이트 재료에서부터 동박 도금을 분리하기에 충분히 큰 변형을 초래했다. 그런 다음 솔더 조인트의 변형률 범위를 줄임으로써 에폭시의 크랙을 방지하기 위해서 시편의 스탠드오프 높이를 6mm와 4mm로 줄였다. 구리 배럴의 유사한 불량이 관찰되었으나, 장기간의 사이클을 가지고 있다. 마이너스의 평균 반복 온도로 열 사이클링하는 동안에 솔더 조인트의 불량은 패드 분화구(pad cratering)의 원인이 되었다. 쓰루홀 조인트는 특정 손상 누적을 보이지 않았지만, 그림 5에서 포팅 재료의 압축 응력 생성 동안 시편의 큰 굽힘으로 인해 많은 비중의 솔더 패드가 거의 동시에 나빠졌다. 압축 평균 변형 반복 하중 동안에 솔더 패드에 어떠한 크랙도 눈에 띄지 않았다.

다양한 포팅 재료로 열 사이클링하고 횡단면 절단한 불량 모드를 통해서, 쓰루홀 조인트는 거의 항상 표면실장 조인트보다 더 많은 손상을 촉진하고 저항 측정을 사용하여 솔더 패드 내의 손상을 추적하기 어렵게 한다는 점을 알 수 있었다. 표면실장 솔더에 향하는 축방향 하중을 제한하기 위해, 재료의 Tg를 가로지르는 열 사이클링에서 대량의 에폭시 포팅 재료와 함께 쓰루홀 솔더 조인트를 사용해서는 안 된다.

열 사이클링 프로파일

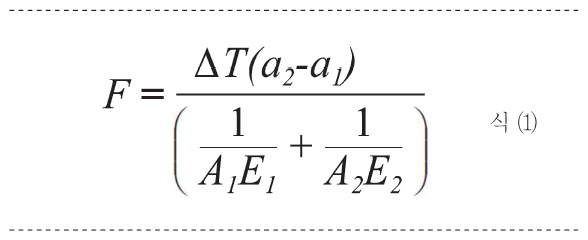

솔더 조인트 내의 응력 상태에 대한 기본적인 이해를 돕기 위해 간단한 호환성 변위 방정식을 사용하였다. 수학식 (1)은 솔더와 포팅 물질의 열팽창 계수 불일치 및 탄성 계수로 인한 솔더 조인트의 세기를 나타내고 있다. 이 관계는 솔더와 포팅 팽창 사이의 순수한 선형 탄성 상호 작용을 가정하고 포팅 재료와 열 프로파일을 일치시키기는 예비 기준으로 사용하였다.

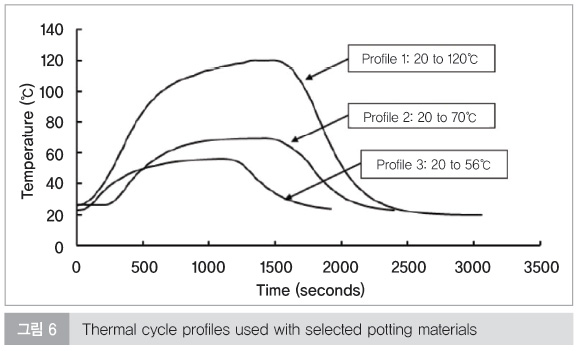

본 연구를 위해 3개의 열 사이클이 선택하였으며, 그림 6에 표시하였다. 열 사이클은 시편 중앙에서 기록된 온도를 나타낸다. 포팅 재료의 많은 체적으로 인해, 시편의 큰 열 질량은 챔버 공기에서 솔더 조인트로의 온도 전달을 느리게 하였다. 3가지 온도 프로파일 모두 평균 10분의 dwell time과 15℃/분의 램프 속도를 사용하였다.

프로파일 3의 저온 범위에서 주기 비율은 시간당 약 2 사이클이었으며, 이는 –40~125℃의 열 사이클링 범주 하에서 솔더에 더 많은 손상을 주는 것으로 알려져 있다.[9] Dwell time이 길면 솔더 조인트에서 더 많은 변형이 발생하는 것으로 알려져 있다. 무연 솔더의 피로 수명은 피크 온도가 125℃인 열 프로파일의 경우에 dwell time을 15분에서 30분 이상으로 늘림으로써 현저히 감소했다.[10] 그래서 저온 및 고온 dwell 단계 양쪽에서 일관된 dwell time이 유지하였다.

수정된 시편 설계

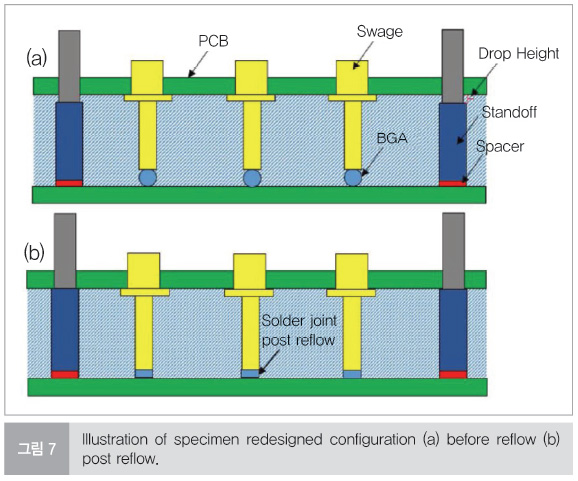

표본의 두 번째 반복은 패드 분화구 현상을 완화하기 위해 솔더 마스크 규정 패드와 유사한 보드 레이아웃을 사용하였다. 더 큰 스웨이지 핀(swage pin)에 맞도록 쓰루홀을 넓혔고, 표면실장 패드 개구부를 핀 직경 760㎛에 맞게 조정하였다. 재설계된 보드의 길이와 너비 치수는 변경하지 않았고 핀 수도 유지하였다. 스웨이지 핀을 수용하고 솔더 패드를 강화하기 위해 몇 가지를 변경하였다. 쓰루홀 트레이스는 각각 2층과 3층으로 라우팅하였다. 새로운 스웨이지 핀 연결로 수정된 시편 구성이 그림 7에 나와 있다.

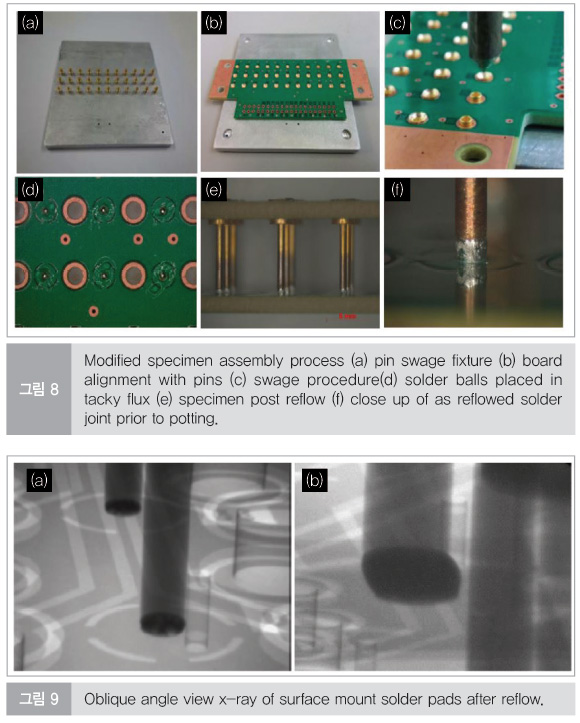

쓰루홀을 솔더 조인트를 대체하기 위해 스웨이지를 선택하면, 상부 보드와 더 강력한 접촉을 제공하나 스탠드오프 높이를 제어하고 포팅 재료 체적을 변경할 수 있는 조정성이 없어진다. 따라서 이러한 설계 결정은 이전 시편 설계에 비해 표면실장 솔더 조인트의 응력 및 변형을 변경하는데 필요한 파라미터의 수를 제한한다. 새로운 스웨이지 핀의 작은 구멍으로 인해 솔더 페이스트와 솔더 구체의 두 가지 솔더 조인트 유형이 사용되었다. 그림 7에서는 수정된 시편의 시편 어셈블리 과정들을 보여주고 있다. 스웨이지용 신규 핀 지지를 위해 알루미늄 픽쳐를 가공하였다. 스웨이지 작업 이후, 납볼을 점착성 플럭스를 사용하여 구리 패드에 놓고 정렬하였다. 얇은 심 스페이서는 리플로우 동안 낙하 높이를 조정하고 솔더 조인트의 최종 높이를 제어하는데 사용하였다. 낙하 높이는 원하는 솔더 조인트 높이에 따라 조정된다.

760㎛ 직경의 SAC305 납볼이 500㎛의 평균 최종 솔더 높이를 구현하기 위해 각 가장자리에 14mil 스페이서와 함께 사용되었다.

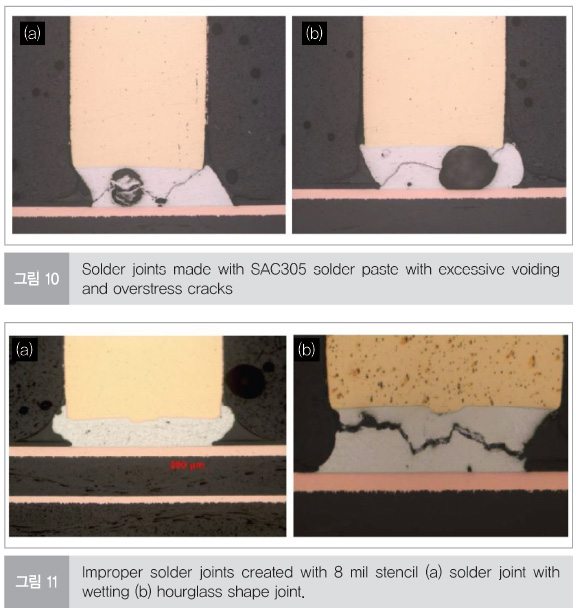

솔더 높이는 더 작은 직경과 심 스페이서(shim spacer)를 지닌 납볼을 선택함으로써 조정할 수 있었다. 본 실험에서 단일 납볼 크기는 솔더 조인트의 응력 수준에 영향을 미치는 변수를 제한하는데 사용하였다. 초기에, 솔더 조인트는 0.8mm의 개구 및 구리 패드 레이아웃과 유사한 피치 크기를 지닌 8mil 스텐실로 SAC305 솔더페이스트를 사용하여 만들어졌다. 이전 디자인과 비교해 대량의 솔더페이스트 체적이 사용되었기 때문에, 구리 패드 상에 오버프린팅된 솔더페이스트는 리플로우 동안 솔더페이스트의 체적 무너짐을 보상한다. 리플로우 이후 보이드와 정렬에 대한 조인트 품질 검사를 위해 X-선 이미징 검사를 수행하였다. 그림 9는 구리 패드 및 황동 핀에 보이드 및 오정렬이 있는 솔더 조인트의 X-선 이미지를 보여주고 있다. 솔더 조인트의 오정렬은 스텐실된 페이스트를 지닌 스웨이지 보드의 장착 및 정렬의 공차로 인해 발생하지만 솔더 조인트의 하부면과 상부면 사이의 동심원 오프셋 거리가 80㎛를 초과하지 않았다.

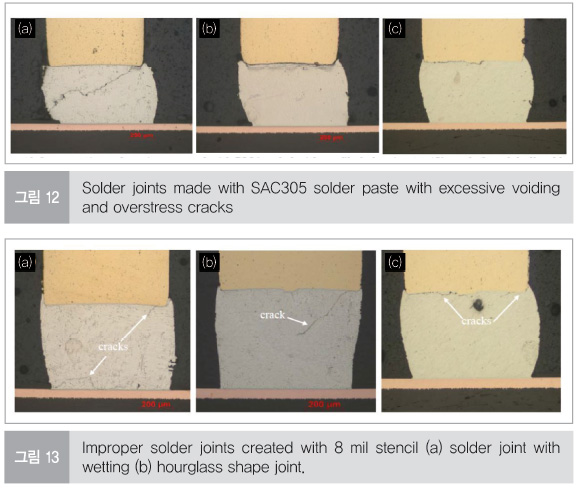

솔더페이스트와 다양한 포팅 재료를 가지고 어셈블리된 시편을 그림 10과 같이 횡단면으로 절단하였다. 큰 보이드와 함께 대부분의 솔더 조인트를 관통한 피로 크랙 성장을 확실하게 볼 수 있었다. 과도한 보이드는 피로 크랙의 브리징(bridging)을 촉진하고 솔더의 유효 피로 저항을 잠재적으로 감소시키는 것으로 알려져 있다. 솔더 조인트의 오정렬도 나타나 있으며, 축 방향 하중에 매우 중요하다. 솔더 조인트는 열팽창 동안 인장력이 가해지므로 벌크 솔더에서의 응력 상태는 조인트 길이 전체에 걸쳐 일관된 횡단면적에 달려 있다. 비스듬한 솔더 조인트가 장력으로 하중을 받을 때, 재료 내의 응력 상태는 혼합된 인장 및 전단 하중으로 변환된다. BGA 조인트는 기하학 구조에서의 원형 형상으로 인해 다축 응력 상태를 나타낸다. 리플로우된 솔더 조인트의 목표는 형상 첨도(shape convexity)를 줄이고, 축 방향 하중 하에서 응력 상태를 단순화하는 것이었다.

비스듬한 솔더 조인트 이외에도 테스트 동안에 불일치한 솔더 조인트가 발생하는 또 다른 문제가 그림 11에 나와 있다. 핀 측면에 습윤이 발생한 조인트는 저항의 변화를 포착할 수 없게 한다. 크랙이 줄어든 응력 영역을 통해 완전히 전파되지 못하고 하고, 전기적 불연속을 감지하지 못하게 하는 일정한 전기적 접촉을 유지하기 때문이다.

모래 시계 모양의 솔더 조인트에서 발생하는 또 다른 문제는 스탠드오프 높이가 더 커서 모래 시계 모양을 형성하는 리플로우 동안 솔더페이스트가 굶주리는 결과를 낳았다. 모래 시계 모양의 조인트가 있는 시편은 모래 시계 모양으로 유발된 다른 응력 농도로 인해 간헐적인 고장률을 나타냈다. SAC305 솔더 합금의 솔더 구체는 시편 어셈블리와 리플로우 절차의 빈번한 불일치로 인해 솔더페이스트로 만든 솔더 조인트로 대체했다. 호환성 변위 방정식을 통해, 온도 프로파일 3을 사용하여 PM 6을 선택했다. PM 1의 선택된 온도 그리고 PM 1의 CTE 및 E 특성, 시편 내의 솔더 조인트 오류는 1 ~ 232의 열 사이클에 따라 다르다. 온도 프로파일 3의 저온에서 반복 하중은 낮은 피크 온도로 인해 등온 조건 하에서의 피로 하중의 그것과 대부분 유사하였다.

시편의 횡단면 절단 후, 스탠드오프 스페이서 근처의 시편 모서리에서부터 시편의 중심까지 솔더 조인트 높이의 경미한 변화가 명백하게 보였다. 스탠드오프 스페이서에 더 가까운 솔더 조인트는 중앙의 조인트보다 약간 짧은 높이를 갖는 것으로 나타났다. 이 변형의 이유는 조인트 높이 변동의 한 원인이 되는 PCB 자체의 곡률로 밝혀졌다. 더 짧은 조인트는 솔더 조인트와 포팅 재료 높이의 상대적인 차이로 인해 더 큰 응력과 변형을 나타내는 것으로 알려져 있다. 솔더 조인트 높이의 차이와 시편 구성은 파괴 모드에 영향을 미쳤다. 그림 12와 그림 13은 열 사이클링 후 시편 내 다양한 위치에서의 솔더 조인트를 보여주고 있다. 온도 프로파일 3을 이용하여 포팅 재료 PM 6으로 테스트 한 시편의 동일한 row 상의 다양한 솔더 조인트의 횡단면을 비교하였다. 시편 모서리의 솔더 조인트에서는 대부분의 솔더에서 45°의 크랙 성장을 보인 반면, 중앙의 조인트에서는 금속간 레이어 주위의 솔더 매트릭스에서 크랙이 존재했다. 고장 사이클 변동의 한 가지 이유는 솔더 조인트 높이의 변동성 때문이었다. BGA 패키지의 솔더 볼 높이는 신뢰성에 영향을 미치는 가장 중요한 파라미터 중 하나이다. 더 길어진 솔더 조인트를 사용하면, 더 짧은 솔더 조인트와 비교했을 때 낮아진 조인트 변형률이 나타나기 때문에 피로 수명이 많이 증가할 수 있다.[11] 솔더 조인트 높이의 차이는 응력과 변형의 분포에도 영향을 미치고, 특정 방향 하에서 불량을 쉽게 발생하게 한다. 솔더 조인트에서 관찰되는 불량 유형에 대한 특정 테스트 조건 정보들을 수집하기 위해서 더 많은 테스트가 필요하다.

REFERENCES

[1] Kwak, Jae B., et al. "Deformation and strain measurement of flip-chip solder bump under in-situ thermal loading." ASME 2009 International Mechanical Engineering Congress and Exposition. American Society of Mechanical Engineers, 2009.

[2] Ghaffarian, Reza. BOK─ Underfill Optimization for FPGA Package/Assembly. Pasadena, CA: Jet Propulsion Laboratory, National Aeronautics and Space Administration, 2011.

[3] Liang, Ting, et al. "Torsional fatigue with axial constant stress for Sn.3Ag.0.5 Cu lead-free solder." International Journal of Fatigue 67 (2014): 203-211.

[4] Gao, Hong, and Xu Chen. "Effect of axial ratcheting deformation on torsional low cycle fatigue life of lead-free solder Sn.3.5 Ag." International Journal of Fatigue 31.2 (2009): 276-283.

[5] Andersson, Cristina, et al. "Comparison of isothermal mechanical fatigue properties of lead-free solder joints and bulk solders." Materials Science and Engineering: A 394.1 (2005): 20-27.

[6] Nadimpalli, Siva PV, and Jan K. Spelt. "R-curve behavior of Cu.Sn3. 0Ag0. 5Cu solder joints: effect of mode ratio and microstructure." Materials Science and Engineering: A 527.3 (2010): 724-734.

[7] Lee, Joon-Yeob, et al. "Study on the board level reliability test of package on package (PoP) with 2nd level underfill." 2007 Proceedings 57th Electronic Components and Technology Conference. IEEE, 2007.

[8] Wilcoxon, Ross, Dave Hillman, Doug Pauls, and Dan White. "The Impact of Improper Conformal Coating Processes on BGA Solder Joint Integrity." SMTA International Conference Proceedings (2015): 870-882

[9] Chow, Seng Guan, et al. "Board level solder joint reliability modeling of embedded wafer level BGA (eWLB) packages under temperature cycling test conditions." Electronics Packaging Technology Conference (EPTC), 2011 IEEE 13th. IEEE, 2011.

[10] Fan, Xuejun, G. Rasier, and Vasu S. Vasudevan. "Effects of dwell time and ramp rate on lead-free solder joints in FCBGA packages." Proceedings Electronic Components and Technology, 2005. ECTC`05.. IEEE, 2005.

[11] Redustion of woid formation by applying sinusoidal linear/logarithic sweep movements using piezoelectric actuator with a small amplitude.