프로세스 제어에 따라 절연체 재료의 성능 비교 가능

PCB 어셈블리 및 수명에서 패드 분화구에 의한 반품 줄여

인장강도시험을 통해 PCB 작업장은 자체적인 프로세스 제어에 따라 패드 분화구를 견뎌내는 절연체 재료의 성능을 비교할 수 있으며, PCB 어셈블리와 서비스 수명에서 패드 분화구에 의한 반품을 줄일 수 있다. 서로 다른 작업장에서의 프로세스 편차 때문에 서로 다른 PCB 작업장의 데이터 비교는 여전히 추천한지 않는다. 이 테스트 방법은 신중하게 실행했을 때 재현 가능한 것으로 입증되었으며 이례적인 결과가 없었으며, 이는 우수한 실제적인 테스트라는 것을 암시한다. 특정 인장강도를 지닌 재료는 제품의 운송 및 서비스 수명 동안 실제 PCB 패드 분화구를 견딜 수는 있지만, 하나의 제조업체에서 재료들 간의 차이점들을 제공하기 때문에 최종 사용자는 동일 PCB 작업장에서의 최고의 후보 재료들 선정이 가능하다.

인장강도시험(CBP; Cold Ball Pull test)은 서로 다른 초저손실 절연체 재료(Dk = 3 ~ 4.2, Df <= 0.005 @ 1GHz)에 있어서 PCB 패드 분화구(pad cratering)의 저항을 검증하는데 사용된다. 인장을 위해 16mil 공칭 패드 크기가 생성된 쿠폰을 활용하는 일반적인 테스트 보드 디자인을 이용하였고, 여러 PCB 작업장에서 재료를 제조하였다. 제작 후, 인장을 위해 20mil SAC305 볼을 16mil 공칭 패드에 SMT 프로세스를 통해 어테치하였다. 통계 분석에 필요한 150개의 데이터 포인트를 생성하기 위해 각 재료들로 제작된 3개의 쿠폰에 각각 50개의 인장 위치를 표시하였다. 이를 통해 재료 구조의 최대 인장력 차이를 비교하여 결과를 차별화할 수 있었다. 결과적으로 PCB 패드 분화구를 견딜 수 있는 다양한 초저손실 절연체 재료의 성능을 인장강도시험을 이용해 종합적으로 비교할 수 있었다.

4G/LTE 클라우드 컴퓨팅 그리고 5G가 구축됨에 따라, 급증하는 인프라 성능 요구를 맞추기 위해 고성능의 서버, 네트워크 및 통신제품들이 필요해지고 있다. 결론적으로, PCB 설계 및 성능 요건은 이들 애플리케이션의 요구조건을 만족시킬 수 있는 재료(더 낮은 유전율(Dk)과 유전정접(Df), 고주파 및 고속(낮은 신호 손실 요구사항을 위해), 더 높은 결합 강도(소형 직경 패드를 지닌 파인 피치 BGA 디바이스를 위해), 더 높은 유리전이온도(high Tg, 무연 어셈블리 준수를 위해) 등)라는 도전과제를 부여하고 있다. 필수적인 전기와 열성능 이외에도 이들 인프라 최종 제품군의 장수명을 보장하기 위해 보다 엄격한 신뢰성 요구도 또한 고려되어야만 한다.

이러한 인프라 유형 제품군의 설계에는 일반적으로 더 두껍고 더 큰 보드가 사용된다. 고려되어야 하는 다른 요인들은 다음과 같다. ▶ 수분 흡수 및 CTE를 감소시키기 위한 더 높은 충전제 함량, ▶ E-glass 대비 비닐 실란 표면처리(vinyl silane surface treatment)된 낮은 Dk glass, 낮은 프로파일 Cu 포일과 구리 본딩 처리되어 접착할 수 있는 수지 화학제, ▶ RoHS 그린 준수를 위해 할로겐-프리 난연제. 과거에 사용된 SnPb 솔더와 기존의 다이시아노다이아미드(dicy)가 경화된 비충진 FR-4 재질과 비교했을 때 앞의 요인들을 결합해 보면, 증가된 열적 및 성능 요건을 지원하는데 필요한 신규 재료들이 높은 PCB 패드 분화구 불량률을 초래할 수 있다는 우려가 제기되고 있다. IC패키지 대형화, 패드 직경 소형화, 스택업 복잡화 등이든지 아니면 잠재적인 CAF 성장 가속화 그리고 PCB 어셈블리 공정의 ICT(in circuit test)와 기타의 취급 단계, 운송 및 사용기간 동안의 다른 기계적 및 열적 기계적 신뢰성 문제와 결부되어 나타나기 때문이다[1].

PCB 패드 분화구 현상에 대해, IPC-9708에서는 표면실장부품의 패드 하부에서 응집성 절연체 크랙 혹은 파열이 형성된 것으로 규정되어 있으며, 그림 1[1]과 같이 기계적 테스트 하에서 BGA 및 BTC 패키지에 가장 일반적으로 발생한다. 기계적 굽힘 및 충격 테스트 도중 PCB 어셈블리에 적용된 변형률 및 변형률 속도가 솔더 조인트 근처에서 다양한 고장 모드를 유발할 수 있다. 이러한 고장 모드의 유병률(prevalence)과 분포는 사용된 솔더 야금, 패키지 유형, 구성, 부품-PCB-패드 크기 비율 그리고 PCB 재료를 포함한 여러 요인에 따라 달라진다. 일반적으로 다중 고장 모드는 서로 다른 변형률과 변형률 속도 레벨에서 동시에 발생한다.

IPC 9708 표준에서는 다음과 같이 다양한 패드 분화구 고장 모드에 대한 일부 가이드를 제공하고 있다[1].

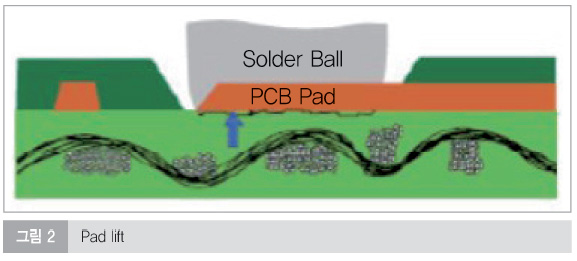

솔더 볼이 있는 솔더 패드의 리프트(그림 2 참조).리프트된 패드는 파열된 베이스 재료를 포함할 수도 있다. 이 고장 모드는 패드 분화구와 반대로 도체(호일)의 접착성 고장이며, 이는 절연체 수지의 응집성 불량이다.

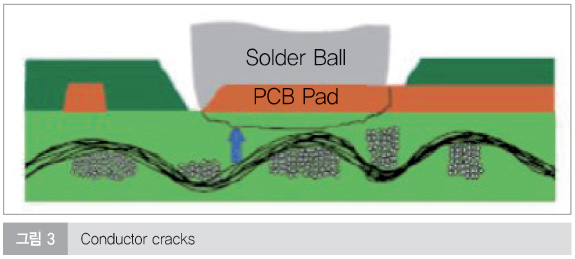

PCB 패드가 리프트되어 있으나 여전히 부분적으로 도체에 부착되어 있다. 이 또한 응집성 불량이다(그림 3 참조).

PCB 패드가 분화되고, 밑에 있는 유리 섬유가 노출되어 유리 섬유 강화재에 2차 접착성 불량을 지닌 절연체 수지의 응집성 결함이 발생했다(그림 4 참조).

PCB 패드가 분화되고, 하부 수지가 노출되었다. 그러나 유리 섬유가 보이지 않았다. 절연체 수지의 응집력 불량이다(그림 5 참조)

패드 분화구의 발생을 완화하기 위해, 기계적 응력에 관한 절연체 재료의 저항을 특성화할 필요가 있다. 따라서 기계적 굽힘(단조 및 구면), AE 감지, 낙하 충격, 인장강도, hot pin pull 등과 같은 절연체 재료의 특성화를 위해 다양한 방법론이 개발되었다[2 ~ 16]. 앞의 2개는 PCBA 레벨 테스트와 관련이 있고 반면, 마지막 2개는 패드 레벨 테스트와 관련이 있다.

PCBA 레벨 테스트에서는 서로 다른 변형률과 변형률 속도 레벨로 여러 개의 실패 모드가 동시에 생성되는 것이 일반적이다. 높아진 힘 가속과 솔더 야금, 패키지 타입, 구성, 부품 대 PCB 패드 사이즈 비율 그리고 PCBA 재료 등과 같은 많은 변수 때문에 개별적으로 실패 모드를 분리하고 어셈블리에서 가장 약한 부분을 식별하기 어렵게 한다. 이는 PCBA 레벨 테스트가 시간과 비용 측면에서 효과적이지 않음을 의미한다. 패드 레벨 테스트를 사용하면, 패드 하부의 절연체 레이어 내 고장 모드를 제어하는 게 더 쉽다. 아울러 패드, 수지 및 유리 섬유 사이의 접착력을 규정하는 것도 훨씬 수월하다[16]. 2개의 패드 레벨 테스트 사이에서, 인장강도시험은 통계적으로 적절한 샘플 크기를 수집하고 테스트를 수행하는데 있어서 요구되는 재료와 시간 때문에 hot pin pull 테스트보다 훨씬 경제적이다.

iNEMI의 초 저손실 프로젝트 작업 그룹은 연구를 위해 10개의 절연체를 선정하였다. 재료는 일련의 파라미터 규정과 재료 공급업체의 참여 의사에 기반을 두고 선정하였다.

재료 영역을 좁히는데 사용된 선정 기준은 다음의 공급업체 라미네이트 데이터를 기반으로 하였다.

전기적 목표 :

▶ Dk : 3~4.2 @ 1GHz

Df : <= 0.005 @ 1GHz

열-기계적 목표 :

▶ Tg : > 160℃

▶ Z-CTE : 50℃ ~ 260℃, <3.0 %

구성 :

▶ 3 mil ~ 10 mil의 다중 절연체 두께

▶ 코어용 VLP 또는 HVLP 구리

▶ UL V-0 등급

프로젝트 작업 그룹에서는 재료 테스트 보드를 설계할 표준 스택업을 결정했다. 스택업 구성에 적용된 기준은 다음과 같다:

▶ 22개의 레이어

▶ 4개(스택업 중앙에 2oz 레이어)

▶ 최소 두께 150mil

▶ 단일 라미네이션

▶ 전기적 구조가 드릴된 백

▶ 신뢰성 테스트 구조를 위한 OSP 표면 마감처리

▶ Spread glass ply(즉, 1086, 1067 등)

▶ 모든 프리프레그에 대한 높은 수지 함량의 중간재

4개의 PCB 작업장(G, T, H, V)에서 모든 스택업 간의 유리 플라이 타입(Glass ply type), 수지 함량 및 레이어 두께를 일치시키는 것이 바람직하지만 모든 재료 공급업체가 동일한 유리 스타일로 원하는 두께에 맞춰 재료를 제공하지는 않았다. 각 재료에 대한 스택업은 작업 그룹에 의해 규정된 공칭 스택업에 최대한 가깝도록 수정하였다.

이번 연구에 활용된 테스트 방법은 IPC 9708의 인장강도 방법론에 따라 다음과 같이 개선하였다.

▶ 측정된 평균 패드 크기 : 16 ±0.5 mils

▶ 어테치된 솔더 볼 크기 : 20 mils

▶ 솔더 볼 조성 : SAC405

▶ 솔더 스텐실 : 스테인리스 스틸 5 mil 두께, 20 mil 개구부

▶ 볼 어테치용 솔더 페이스트 : SAC305 페이스트

▶ 피크 리플로우 온도 : 최소 245℃

▶ 테스트 장비 : Bond Tester

▶ Jaw 사이즈 : 750um

▶ 클램핑 압력 : 21psi

▶ Pull 속도 : 5mm/sec

재료 테스트 패널에 통합시킨 쿠폰 디자인은 각 5개의 고유한 패드 크기(14mil, 15mil, 16mil, 17mil, 18mil 직경 패드)에 5×5 구형 패드 어레이로 구성되었다(그림 6 참조). 그림 7에서 보여주는 바와 같이, 어레이의 패드는 1mm 피치로 이격하였고, 5mm 솔더 마스크 간격의 NSMD로 설계하였다.

각 패드 그룹에서의 실제 패드 크기는 광학 측정값 입력과 디자인된 각 패드 크기의 평균 데이터를 이용하여 3차원 좌표측정기(CMM, coordinate measurement machine)로 측정하였다. 솔더 볼은 앞서 언급된 조건에 따라 각 쿠폰의 패드에 어테치하였다. 그림 8에서 보여주는 바와 같이, 각 샘플들은 우수한 솔더볼 어테치를 보장하는 조인트 부분에서 검사가 이뤄졌다. 구리 패드를 완전히 덮고 있는 패드와 NSMD 윈도우 중앙에 놓인 패드만 허용되는 것으로 간주하였다.

평균 16mils±0.5에 근접하게 측정된 설계 패드 어레이를 표 1에서 보는 바와 같은 테스트를 진행하기 위해 선정하였다. 실제 패드 크기 분포는 재료 및 공정 파라미터와 같은 각 PCB 작업장의 공정 제어능력에 달라졌다. PCB 작업장 V가 생산한 평균 패드 크기는 16mil 공칭 목표 및 다른 PCB 작업장보다 낮았으며, 주목할 부문은 모든 PCB 작업장의 CBP(Cold Ball Pull) 강도를 비교한 결과라는 점이다. 각각의 재료는 각 50번의 당김(pull)을 지닌 3개의 쿠폰(coupon)으로 제작되었고, 150번의 피크 당김을 생성하고 생산 통계 소프트웨어로 분석하였다. 솔더볼이 부착되지 않은 누락된 특정 당김 혹은 사이트는 당김 데이터에서 생략하였다.

테스트 후 발생한 고장 모드는 재료, 프로세스 및 디자인 형상에 따라 달라질 수 있다. 이러한 고장 모드에는 벌크 솔더 파손, 계면 IMC 파손, 고장 혼합 모드 및 PCB 패드 분화구가 포함되어 있다(그림 9 참조).

본 연구의 초점인 PCB 패드 분화구 고장 모드와 관련하여, 고장 위치는 ▶ 패드 리프트, ▶ 도체 크랙, ▶ 유리섬유 노출을 가진 분화구, ▶ 유리섬유 노출이 없는 분화구의 4가지 범주로 분류될 수 있으며, 앞의 그림 2 ~ 그림 5에서 이를 설명하고 있다. 크랙 자체는 변형 완화를 위한 최소 저항 경로의 결과일 것이며, 대량의 수지를 통해 아래쪽으로 전파되는 패드 가장자리에서 시작되거나 아니면 레진과 유리섬유 간의 계면에서 핵이 생성되는 하부 혹은 절연체 레이어 내로 패드 크랙이 확대됨으로써 시작될 수 있다. 분화구 고장은 전기적 오픈을 초래하지 않지만, 크랙 확대 지속성 때문에 일련의 후속 및 수명에서 잠재적으로 전기적 고장을 일으킬 수 있다.

수지 화학제, 경화제, 유리 수지 함량, 충전제 함량 등과 같은 유전 재료 설계 변수에 기초하여, 고장 완화를 위해 내 파손 성을 개선시키는 데 가장 큰 영향을 미치는 것을 식별하는 것이 쉽지 않았다. 파괴 역학의 관점에서, 매트릭스 내 상이(相異)한 성분들 사이의 접착력은 이 시험 방법으로 정량화하기 어렵다. 크랙이 시작될 때 벌크 수지 재료 자체는 파괴 에너지의 대부분을 흡수할 수 있으며 파괴 깊이에 의한 고장 모드의 분포는 다소 불규칙적으로 나타난다. 따라서 이 테스트에 근거하여, 벌크 수지 자체의 파괴인성(fracture toughness)을 높이는 것이 성능 향상을 향한 방향이라고 결론 내릴 수 있다. 불행히도 IPC TM650에서 이러한 재료에 대한 파괴인성을 테스트하는 표준화 방법이나 시행지침이 존재하지 않아서, 굴곡 탄성률, 굴곡 강도 및 박리 강도와 같은 일반적인 기계적 특성만 상관관계에 사용하였다. 파괴인성 측정을 위한 ASTM 시험 방법이 앞으로의 연구에 참고할 수 있다.

CBP(Cold ball pull) 테스트는 패드 위의 솔더 조인트에서 솔더 조인트를 수직으로 잡아 당겨 Cu 패드와 기본 절연체 사이의 파괴 강도를 보여주도록 설계되었다. 크랙 경로에서 크랙 개시 및 전파를 개별적으로 식별하기에 충분하지 않았지만 전체 파쇄 공정의 총 에너지를 정량화할 수 있었다. 그림 11은 4개의 서로 다른 PCB 작업장에서 테스트 한 10가지 재료의 CBP 비교를 보여주고 있다. 4개의 PCB 작업장 간의 공정 제어는 알려져 있지 않다.

동일한 라미네이트 재료와 스택업으로 제작된 PCB는 여전히 PCB 작업장의 공정 엔지니어링 매개 파라미터의 차이에 영향을 받는다. 동일한 PCB 레이아웃과 재료가 사용 되더라도 PCB 패드의 평균 직경은 로트 간 및 PCB 작업장 간 편차가 존재한다. 실제 패드 크기는 표 1에 표시되어 있으며, 설계 패드 크기의 결과는 그림 6과 같이 16~18mil이었다.

PCB 크기가 16mil에 가장 가까운 절연체 재료에 대한 PCB 패드의 접착 강도를 비교하기 위해 4개 PCB 작업장의 쿠폰에 대해 인장강도시험을 수행하였다. 테스트 조건에 따른 모든 고장 모드는 그림 4 및 그림 10에서와 같이 유리섬유가 노출된 경우의 응집 고장이었다. 그래서 데이터는 비교 가능하였고, 강도 등급은 하부와 같이 PCB 작업장별로 그룹화하였다.

1. G 작업장 : G3> GL> GE> GY

2. H 작업장 : H1> HW> H3> H5> HL> HY

3. V 작업장 : VR> VY> VE

4. T 작업장 : TY> TR> T8> TE> T2

그림 11은 적용된 각 재료의 피크 인장력 값에 대한 평균 및 표준 편차 통계를 보여주고 있다. 이 데이터는 각기 다른 제조 공장에서 동일한 자재를 사용했을 경우의 성능 차이와 동일한 작업장에서 서로 다른 자재를 적용했을 경우의 차이를 나타내고 있다. 예를 들어, 자재 Y의 성능은 G 작업장에서 보다 T 작업장에서 통계적으로 더 우수하다고 나왔다. 또한 자재 3은 G 작업장에서 자재 Y보다 통계적으로 우수했다.

작업장 사이의 제어되지 않은 프로세스 차이와 함께 V 작업장에 적용된 패드 사이즈 차이가 PCB 작업장 간의 차이를 나타내는 원인이었다. 다양한 재료가 적용된 작업장 내에서의 순위는 해당 작업장 제품의 라미네이트 강도를 나타내는 좋은 지표이다.

인장강도시험을 통해 PCB 작업장은 자체적인 프로세스 제어에 따라 패드 분화구를 견뎌내는 절연체 재료의 성능을 비교할 수 있으며, PCB 어셈블리와 서비스 수명에서 패드 분화구에 의한 반품을 줄일 수 있다. 서로 다른 작업장에서의 프로세스 편차 때문에 서로 다른 PCB 작업장의 데이터 비교는 여전히 추천한지 않는다.

이 테스트 방법은 신중하게 실행했을 때 재현 가능한 것으로 입증되었으며 이례적인 결과가 없었으며, 이는 우수한 실제적인 테스트라는 것을 암시한다. 특정 인장강도를 지닌 재료는 제품의 운송 및 서비스 수명 동안 실제 PCB 패드 분화구를 견딜 수는 있지만, 하나의 제조업체에서 재료들 간의 차이점들을 제공하기 때문에 최종 사용자는 동일 PCB 작업장에서의 최고의 후보 재료들 선정이 가능하다.

다음 단계는 재료가 실제 서비스에 사용될 때 패드 분화구가 발생하는 최대 인장력 임계 값을 결정하는 것이다. 이 작업을 충격 시험, 구면 굽힘 시험, DMA 등과 같은 다른 방법의 결과와 관련시켜 해당 작업을 수행하는 것이 좋다. 제품 설계 및 제작자 프로세스 제어에 따라 임계 값이 달라질 것으로 예상된다.

REFERENCES

[1] IPC-9708, Test Methods for Characterization of Printed Board Assembly Pad Cratering,2010.

[2] Mukadam, M., Long, G., Butler, P., Vasudevan, V., “Impact of Cracking Beneath Solder Pads in Printed Circuit Boards on the Reliability of Ball Grid Array Packages”, Proc SMTAI, 2005, pp. 324-329.

[3] Roggeman, B., Borgesen, P., Li, J., Godbole, G., Tumne, P.,Srihari, K.., Levo, T., Pitarresi, J., “Assessment of PCB Pad Cratering Resistance by Joint Level Testing”, Proc 58th Electronics Components and Technology Conference, May 2008, pp. 884-892K.

[4] Ahmad, M., David, S., Burlingame, J., “Methodology To Characterize Pad Cratering Under BGA Pads In Printed Circuit Boards”, Proc. SMTA PanPacific Microelectronics Symposium, Kauai, HI, 2008.

[5] Ahmad, M., Burlingame, J., Guirguis, C., “Comprehensive Methodology To Characterize And Mitigate BGA Pad Cratering In Printed Circuit Boards”, SMTA Journal, Vol. 22, No. 1, 2009, pp. 21-28.

[6] Ahmad, M., Burlingame, J., Guirguis, C., “Validated Test Method to Characterize and Quantify Pad Cratering Under BGA Pads on Printed Circuit Boards”, Proc APEX Expo, Las Vegas, NV, March 2009.

[7] Roggeman, B.,, Venkatesh Raghavan, Peter Borgesen, “Joint Level Test Methods for Solder Pad Cratering Investigations”, Accepted for publication Journal of Electronics Packaging, March 2011.

[8] Godbole, G., Roggeman, B., Borgesen, P., and Srihari, K.,“On the Nature of Pad Cratering”, Proc 59th Electronics Components and Technology Conference, May 2009, pp. 100-108.

[9] McMahon, J., Gray, B., “Mechanical Failures in Pb-Free Processing: Evaluating the Effect of Pad Crater Defects on Process Strain Limits for BGA Devices”, Proc.SMTA PanPacific Microelectronics Symposium, 2010.

[10] Gray, B., McMahon, J., “Mechanical Failures in Pb-Free Processing: Selected Mitigation Techniques for Pad Crater Defects”, Proc SMTAI, 2010, pp. 530-534.

[11] Raghavan, V., Roggeman, B., Meilunas, M., Borgesen, P., “Effects of Pre-Stressing on Solder Joint Failure by Pad Cratering”, Proc 60th Electronics Components and Technology Conference, May 2010, pp. 456-463.

[12] IPC/JEDEC-9702, “Monotonic Bend Characterization of Board Level Interconnects”

[13] Brian Roggeman and David Rae,S,”Reliability Impact of Partial Pad Crater”,SMTA International Conference Proceedings,2012.

[14] Anurag Bansal, Cherif Guirguis and Kuo-Chuan Liu, “Investigation of Pad Cratering in Large Flip-Chip BGA using Acoustic Emission”,IPC/APEX 2012.

[15] M. Ahmad et al, “Validated Test Method To Characterize And Quantify Pad Cratering Under BGA Pads On Printed Circuit Boards”, IPC/APEX 2009 Conference, Las Vegas, NV, April, (2009)

[16] Jeffrey Chang-Bing Lee et al, “Dielectric Material Characterization for

PCB Pad Cratering Resistance”, ECWC, Nuremberg, Germany,May (2014)