전해주조된 3mil 스텐실 적용이 유리

6mil 이상의 패드 간격, 솔더링 불량 낮아

0201 부품들은 광범위한 프로세스 최적화 작업을 거친 이후 휴대전화, 블루투스 모듈 그리고 무선 LAN 등과 같이 매우 높은 밀집도의 애플리케이션에 사용되고 있다. 많은 보고서에서 0201 부품의 무연 어셈블리를 평가해 왔다. 레지스터 및 커패시터들은 극소형 01005 사이즈(0.4mm × 0.2mm)로 현재 생산되고 있다. 그러나 매우 얇은 부품을 사용한다는 것은 SMT 어셈블리에 새로운 도전과제들을 잉태하게 한다. 어셈블리 수율 상 PCB 디자인의 영향력을 조사하기 위해서, 01005 테스트 시편은 서로 다른 패드 사이즈, 레지스터 간격, 외형 그리고 방향을 감안하여 디자인되었다. 실험은 솔더 페이스트 프린팅, 부품 실장 및 리플로우 프로세스 최적화와 특성화를 위해 실시했다.

포터블 전자기기의 소형화, 경량화, 다기능화에 대한 지속적인 요구가 소형 부품의 적용을 부추기고 있다. 이러한 요구를 충족시키기 위해 01005 칩 부품들이 현재 상업적으로 이용 가능하다. 그러나 새로운 최종 제품에 매우 작은 부품들을 구현한다는 것은 일부 설계와 어셈블리 프로세스에 있어서 도전과제가 나타나는 것을 의미한다. 본고에서는, 테스트 시료는 어셈블리 수율 상 PCB 패드 디자인의 영향을 조사하기 위해 디자인하였다. 01005 테스트 보드 제조의 프로세스 캐파빌리티를 평가하였다. DOE(Design of Experiments)는 3D 솔더 페이스트 검사기를 기반으로 솔더 페이스트 프린팅을 최적화하기 위해 사용하였다. 무연 솔더가 모든 어셈블리 테스트에 적용하였다. 실장 정도 및 리플로우 불량 상 프로세스 파라미터의 영향을 도출해 내기 위해 여러 번의 테스트를 수행했다. 실험 결과의 분석과 어셈블리 결함을 위한 리플로우 앞단 검사를 통해서, PCB 디자인과 어셈블리 프로세스에 관한 권고사항들을 만들었다.

서문

전자기기의 경박단소화 제작 열망, 특히 캠코더, 카메라, 휴대전화 및 랩톱과 같은 휴대용 전자기기에서 요구가 강하게 나오고 있기 때문에 부품 간격 협소화가 전자산업계의 일반적인 추세가 되었다. 사실, 부품 소형화를 이끄는 또 다른 흐름은 특징들과 기능들의 복잡성 증대이다. 수동소자는 PCB 상의 중요한 에어리어를 차지하고 있다. 특히 아날로그와 전형적인 디지털 시스템과 비교해 대량의 수동소자가 사용되는 혼합 신호(mix-signal) 애플리케이션에서 더욱 그러하다.[1] 수동소자의 사이즈와 이들 간격이 줄어든다는 것은 결국 패키징 집적도 향상을 의미하고, 이는 많은 전자기기 소형화를 이루는 효율적인 방법임을 뜻한다.

전자산업계에 크게 영향을 끼치는 두 번째 트렌드는 RoHS 및 유럽의 WEEE 법안, 일본의 리사이클링 법과 중국 및 캘리포니아에서 발효 중인 친환경 법안에 대응하는 무연 솔더로의 전환이다. 무연 솔더의 젖음성은 공용 SnPb와 다르고[2], [3], [4], 더 높은 리플로우 온도가 요구된다.

최근, 0201 부품들은 광범위한 프로세스 최적화 작업을 거친 이후 휴대전화, 블루투스 모듈 그리고 무선 LAN 등과 같이 매우 높은 밀집도의 애플리케이션에 사용되고 있다.[5], [6], [7], [8], [9], [10], [11], [12] 많은 보고서에서 0201 부품의 무연 어셈블리를 평가해 왔다.[13], [14] 레지스터 및 커패시터들은 극소형 01005 사이즈(0.4mm × 0.2mm)로 현재 생산되고 있다. 그러나 매우 얇은 부품을 사용한다는 것은 SMT 어셈블리에 새로운 도전과제들을 잉태하게 한다. 01005 어셈블리 프로세스에 영향을 주는 주된 요인들은 하부의 카테고리로 나눌 수 있다(PCB 디자인, 부품들, 스텐실, 솔더 페이스트, PCB 취급, 프린팅, 픽앤플레이스먼트, 리플로우 및 검사).[15], [16] 어셈블리 수율 상 PCB 디자인의 영향력을 조사하기 위해서, 01005 테스트 시편은 서로 다른 패드 사이즈, 레지스터 간격, 외형 그리고 방향을 감안하여 디자인되었다. 실험은 솔더 페이스트 프린팅, 부품 실장 및 리플로우 프로세스 최적화와 특성화를 위해 실시했다.

테스트 시료 디자인

01005 부품에 맞는 패드 디자인을 최적화하고 어셈블리 프로세스를 평가하기 위해서 테스트 시료가 디자인되었다. 패드 치수는 표 1에 나타냈다. 패드 사이즈 Type 1은 ‘nominal’이 고려되었다. 패드 형태는 NSMD(non-solder mask defined)로 했다. PCB 디자인에 다른 변수를 포함하였다: 2개 패드 중 하나는 레이저 드릴로 형성한 비아; 2개의 패드 모두를 레이저 드릴로 형성한 비아; 어떠한 비아도 없는 패드; 서로 다른 레지스터 방향(0°, 45° 및 90°); 레지스터 간격 그리고 의도적인 솔더 마스크 불일치. Via-in-pad 디자인은 고밀도 보드 레이아웃에 점점 더 일반화되고 있다.

그림 1에서 보는 바와 같이 테스트 시료는 하나의 면에 레지스터 9600개, CSP 8개 그리고 BGA 1개가 장착된 high-Tg(Tg>170℃) 양면 기판이다. 패드는 immersion silver 마감처리되었고, 모두 NSMD 형태로 하였다. 테스트 보드는 8.0" × 6.0" × 0.042" 두께이고, 2 × 2 array를 기본 테스트 패턴으로 하였다. 보드의 각 사분면에 자리 잡은 총 20개의 디자인 그룹이 존재했다. 90° 방향의 7번 그룹: 0° 방향의 7번 그룹; 45° 방향의 1 그룹; 0° 및 90° 방향의 1 그룹 그리고 하나 패드 내 하나의 비아; 0° 및 90° 방향의 1 그룹과 양쪽 패드 내 비아들; 그리고 0° 및 90° 방향의 1그룹, 레지스터의 너비 사이에서 솔더 마스크는 의도적으로 2mil 이동시켰다. 라운드 글로벌 및 로컬 피디셜 또한 이 디자인에 포함되었다.

보드 제조의 프로세스 캐파빌리티 평가

보드 자체 품질은 신뢰할만하고 일관성 있는 SMT 어셈블리에 있어서 중요하다. 보드 제조가 가능하지를 그리고 보드가 스펙사항들을 충족하는지를 결정하기 위해 공정분석에는 새로 들어온 보드로 수행되었다. 5개의 사각형 패드 사이즈 디자인과 5개의 서로 다른 간격의 디자인을 이번 측정을 위해 선택했다. 보드 당 50개 샘플들을 2개의 보드에서 측정했다. 디자인 스펙에 기반을 두어 패드 폭과 간격의 허용오차는 ±0.5mil로 하였다. 일반 분포 샘플들을 위한 공정능력분석은 Minitab 13.0 버전을 이용하여 실시되었다. 이 분석에서 프로세스 다양성은 6개의 표준편차(각 면의 평균에서 ±3σ)에 의해 평가되었다. 패드 치수의 경우, 공정능력통계는 표 2에 요약되어 있다. 개별 분석에 상응하는 캐파빌리티 히스토그램의 하나는 프로세스 평가에 기반을 둔 일반적인 곡선과 겹쳤다. 그리고 표준편차는 그림 2에서 보여주고 있다. 유사한 패드 간격의 경우, 공정능력분석은 표 3에 요약되었으며, 개별 분석에 상응하는 캐파빌리티 히스토그램은 그림 3에서 나타내고 있다.

표 2와 그림 2의 분석 결과에 따르면, 패드 사이즈에 대한 공정은 목표에서 중앙점이 형성되지 않았고, 대부분의 패드는 목표보다 적었으며, 표준정규분포는 LSL(Lower Specification Limit)로 이동되어 형성된 것을 확실히 할 수 알 수 있었다. 패드들은 설계 값보다 적은 ~0.5mil이었다. 표 4와 그림 3에서 보여준 분석결과에 따르면, 간격에 대한 공정은 목표에서 중앙점이 형성되지 않았다. 대부분의 간격은 목표보다 컸고, 표준정규분포는 USL(Upper Specification Limit)로 이동되어 형성된 것을 볼 수 있었다. 패드 사이즈와 간격 양쪽의 경우, Cpk<<1인 공정능력지수가 원하는 공정 규격으로 충족되지 못했다. 보정 요인은 보드 제조업체에 의한 프로세싱 요인들을 지정하기 위해서 아트웍 이미징을 그리는 데 사용되고 있다. 그러나 테스트 시편에서 디자인된 작은 공간(최소 4mi) 때문에 적용될 수 있는 보정의 양은 제한적이다. 어셈블리 프로세스 최적화 논의 이후, 패드 및 공간의 디자인 값(실제 값이 아닌)은 패드와 간격을 설명하는데 사용될 것이다.

다이렉트 레이저로 이미지를 형성하는 것은 솔더마스크 define에 사용된다. 그림 4에서 보는 바와 같이, 솔더마스크는 ±2mil 솔더마스크 정렬 허용오차 사양 내에서 4mil와 5mil의 간격을 지닌 패드 사이에서 디자인되지 않을 수 있다. 솔더마스크 기재가 매우 우수하다.

프린팅 최적화

솔더페이스트 프린팅은 SMT 공정 내에서 중요한 단계이다. 대다수의 SMT 어셈블리 불량이 이 공정 단계와 연관이 있기 때문이다. 본 프로젝트에서, 4개의 주요 요인들을 조사하였다: 스텐실 두께, 스퀴지 압력, 스퀴지 속도 그리고 스텐실-보드 분리 속도. 요인들과 레벨은 표 4에 나타내고 있다. 표 5에서 보여준 바와 같은 Taguchi’s L8 OA에 상응하게 하였다. 각 DOE 실행의 경우, 3개의 보드는 메탈 스퀴지 블레이드가 장착된 전자동 스크린 프린터로 인쇄되었다. 그런 후에 3D SPI를 이용해 검사했다. 패드 사이즈 Type 5(13%)용 20개 reference designator의 솔더페이스트 높이와 체적 데이터들이 분석을 위해 수집되었다.

본 테스트에 사용된 솔더페이스트는 88.5%의 메탈 함유 및 Mesh 400의 SAC305(96.5%Sn/3%Ag/0.5%Cu) 무연 솔더페이스트 제품이었다. 3mil과 4mil 두께의 2개의 전해주조된 스텐실이 이번 실험에 테스트되었다. 개구 외형은 패드 외형과 동일하게 했고, 패드 사이즈에 대한 개구비율은 100%이었다. 개구의 벽 면적에 대한 개구의 오픈 면적의 비율로 정의된 AR(area ratio)은 축적했고 표 1에 기재했다.

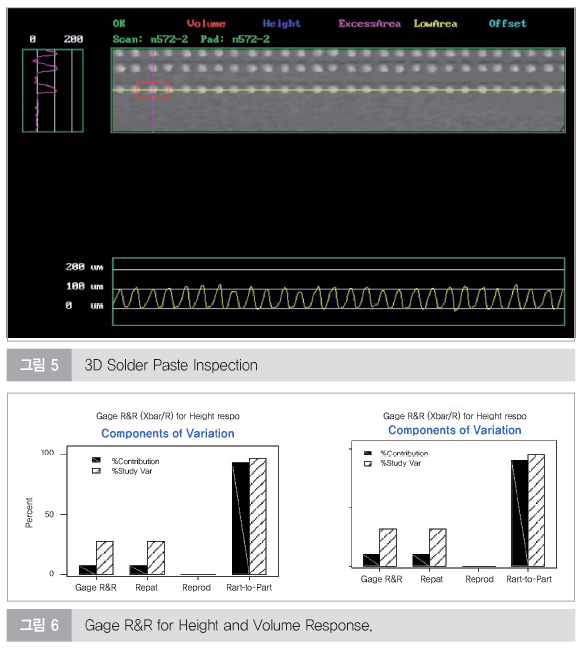

테스트 실행 전에, 3D SPI를 조정했다. 조정된 이후의 3D SPI 결과는 그림 5에서 보여주고 있다. Gage R&R(Gage Repeatability & Reproducibility) 조사가 수행되었다. 재현성의 변동은 하나 이상의 게이지/작업자 조합 간의 차이에 기인한다. 반복성의 변동은 싱글 게이지/작업자 조합에 의한 연속적인 판독 값의 차이에 기인한다. 솔더페이스트 높이 및 체적 응답에 기반을 둔 Gage R&R 결과는 그림 6에서 나타내고 있다. 하나의 게이지/작업자 조합만이 존재할 때, 재현성의 변동은 ‘0’이다. 대부분의 변동이 부품 간의 차이에 기인한다는 것을 볼 수 있을 것이다. 높이 응답에 기반을 둔 Gage R&R 결과는 7.5%이고, 체적 응답에 기반을 둔 Gage R&R 결과는 9.83%이었다. 게이지의 양쪽 측정 오차는 이 검사 설비가 3D 솔더페이스트 검사에 적절하고 가용할 수 있다고 나타내고 있는 제품 특성의 측정에서 10% 미만이었다.

그림 7과 그림 8은 Taguchi DOE 분석 결과를 보여주고 있다. 그림 7은 솔더페이스트 체적 이송효율에 기반을 둔 방법의 주된 효과 그림이다. 체적이송효율은 스텐실 두께에 기인한 솔더페이스트 체적 내의 차이를 정상화하기 위해 사용되었다. 그림 6을 통해서, 스텐실 두께만이 체적이송효율에 확실한 영향을 미치고 있음을 알 수 있다. AR이 이송효율과 솔더페이스트 침전의 반복성에 가장 큰 영향을 갖고 있기 때문에 AR과 관련하여 3mil 두께의 스텐실(95% 이상)은 4mil 두께의 스텐실(72%)에 비해 더 좋은 이송효율을 보이고 있다. 패드 사이즈 Type 5의 3mil 스텐실(0.903)은 4mil 스텐실(0.677)에 비해 더 높은 AR을 가지고 있다. 통상적으로 ≥0.6의 AR이 산업계에서 수용 가능한 수준이라고 여겨지고 있다.[17] 분리 속도는 약간 영향을 미친다; 더 빠른 분리는 더 높은 이송효율에 이바지한다. 프린팅 속도 또한 미치는 영향이 적다. 반면 스퀴지 압력은 이송효율에 미미하게 영향을 끼친다.

게다가 S/N 비율의 변수 분석에 의한 DOE의 실험 결과는 그림 8에서 보여주고 있다. 여기서 실험은 ‘nominal is the best’ 품질 특징으로 진행되었다. 더 높은 S/N 비율이 더 좋다. 높은 S/N 값은 시그널이 제어할 수 없는 노이즈 요인들보다 매우 더 높다는 것을 함축하고 있기 때문이다. 최적화된 프린트 파라미터들은 S/N 비율 도표에 기초하여 식별될 수 있다. 최적화된 프린팅 파라미터들은 ▶ 스텐실 두께 : 3mil, ▶ 프린팅 속도 : 2 in/sec, ▶ 스퀴지 압력 : 14lb, 분리속도 : 0.01 in/sec이었다. 그림 9는 최적화된 프린팅 파라미터 설정을 이용한 프린팅 성능을 보여주고 있다.

그림 10에서는 최적화된 프린팅 설정에 기반을 둔 2개의 스텐실에 서로 다른 패드 사이즈 타입에 대한 공정생산지수(CP) 비교를 보여주고 있다. 3mil 스텐실은 앞서 DOE 결과를 확인하는 4mil 스텐실에 비해 더욱 공정에 적합하고, 굳건하게 한다. 유사하게도, 더 높은 AR을 지닌 더 거대해진 패드 사이즈 타입들은 커진 공정능력지수를 가지고 있다. 3mil 두께 스텐실은 모든 다음의 어셈블리 실험에 사용되었다.

실장 정도 평가

01005 레지스터의 전형적인 사이즈는 termination 폭 0.08mm의 0.38mm × 0.18mm이다. 01005 부품들은 포켓 간 2mm 피치 간격의 일반적인 8mm 테이프&릴로 제공된다. 그림 11에서 보는 바와 같이, 수급 받은 테이프&릴 내에는 2개의 일반적인 방향성 불량이 존재했다; edge-standing과 뒤집힘(upside-down) 부품이 그것이다. 때때로 edge-standing 부품은 부품의 픽앤플레이스 동안 노즐 팁에 피해를 입힌다. Edge-standing 부품은 이들 작은 부품의 너비와 두께가 비슷하기 때문에 픽앤플레이스 비전 시스템에 의해 그 차이가 감지되지 않은 채로 놓일 수도 있다. 뒤집힘 부품은 적절한 길이와 너비 치수를 가지고 있어서 픽앤플레이스 비전 시스템에 의해 일반적으로 불량처리가 되지 않을 것이다.

01005 부품들은 고속기 설비를 통해 실장했다. 새로운 노즐 바디와 팁은 01005 부품에 맞춰 특별히 제작했다. 노즐 팁의 직경은 0.38mm이었고, 팁의 구경은 0.14mm이었다. 아주 작고 정밀한 팁의 유지보수는 매우 중요하다. 팁이 닳아졌거나 혹은 충분하게 평평하지 않는다면, 실장 성능에 분명하게 영향을 미칠 것이다. 피더 정밀은 일관적인 픽 성능에 민감하다.

플레이스먼트 테스트의 목적은 2개 혹은 3개, 로컬 혹은 글로벌 피디셜을 사용했을 때 패드 정도에 대한 실장을 비교하는 것이다. 4개의 테스트는 ▶ 2개 라운드 글로벌 피디셜, ▶ 3개 라운드 글로벌 피디셜, ▶ 2개 라운드 로컬 피디셜, ▶ 3개 라운드 로컬 피디셜에 기초를 두고 실행되었다. 그림 12에서 보는 바와 같이 X1, Y1, X2 및 Y2 거리가 자체 관련 패드와 관련 있는 부품의 중앙 오프셋과 로테이션을 계산하기 위해 분석되었다. 중앙 오프셋은 다음과 같이 계산한다.

측정된 오프셋은 PCB 정도와 플레이스먼트 머신 정도의 결합이다. 2개의 보드가 각 테스트에 실행되었고, 25개의 부품이 측정을 위해 무작위로 선택했다. 계산된 오프셋과 로테이션 데이터는 통계 소프트웨어 Minitab 13.0을 활용하여 분석했다. 표 6에서는 모든 조합의 평균과 Cpk를 나열하고 있다. Cpk 값은 중앙 USL과 ±2mil의 LSL와 회전 USL 및 ±5°의 LSL으로 계산되었다. 이 데이터를 통해서 3로컬 피디셜이 패드 정도에 최상의 실장 결과를 초래한다는 것을 활용하였음을 알 수 있다. 로컬 피디셜은 프로세싱 동안에 PCB 스트레치 및 오버/언더 에치와 같은 PCB 제조공정 중 원인이 되는 PCB 내부의 영역 변수에 더 많이 조절되었다. 모든 그 이후 어셈블리는 실장을 위해 3개의 로컬 피디셜을 사용했다.

리플로우

그림 13과 그림 14에서와 같이 quick-ramp와 a soak profile 2개의 리플로우 프로파일이 무연 솔더링에 적용되었다. 초기에 하나의 보드는 air 상태에서 리플로우 되었다. 그런데 젖음 상태가 만족스럽지 못했다. 각 솔더 영역들은 마이크로스코프를 통해서 볼 수 있었다.

01005 솔더 페이스트 침전은 대부분의 솔더 합금이 대기 환경 내에서 표면산화를 유발할 수 있는 리플로우 분위기 중에 노출되기에는 매우 적다. 그 이후, 질소가 리플로우에 적용되었고, 우수한 젖음상태를 얻었다. 그림 15에서는 air와 질소 리플로우 분위기 간의 젖음성 비교를 보여주고 있다. 질소는 모든 이후 어셈블리에 적용되었다. 2개의 리플로우 프로파일을 이용해 리플로우 된 솔더 접합을 X-선 투과하였다. 그림 16에서는 일반적인 X-선 이미지를 보여주고 있다. 2가지 모든 프로파일에서는 레지스터 터미널 하부에서도 약간의 보이드, 초기 단계의 필렛 현상을 볼 수 있었다.

리플로우 전단 검사

리플로우 이후, 모든 보드가 검사되었고, 많은 불량들이 검출되었다. 리플로우 이후 브릿지, 튬스톤, edge-standing 부품, 부품 유실 및 부품 뒤집힘이 포함된 불량들이 관측되었다. 솔더 볼이 불량 분석에 포함되지 않은 반면, 어셈블리된 테스트 보드의 주의 깊은 실험에서는 매우 적은 솔더 볼이 드러났다. 검사된 이들 솔더 볼은 이들이 플럭스 잔사 내에 갇혀 있고, 최소 전기 간격 요구를 어기지 않는 IPC-A-610D에 수용할 수 있는 수준이다. 28920개의 레지스터 장착 중에서 총 2296개의 불량이 나타났는데, 즉 7.94%의 불량률을 보였다. 이 수치는 패드, 간격, 리플로우 프로파일, 방향 그리고 비아-인-패드의 모든 결합을 포함하고 있다. 표 7에서는 모든 샘플의 불량 분포도를 나열하고 있다. 그림 17에서는 모든 불량에 대한 불량 분포도를 보여주고 있다. 브릿징 및 튬스톤은 초기 불량이 68%이었다. 그림 18에서는 일반적인 불량을 도시화하고 있다.

브릿징

Space 1(4mils pad-to-pad) 그룹 내에서는 브릿지의 90.3%이 판명되었고, Space 2(5mils pad-to-pad) 그룹 내에서는 브릿지의 9.7%이 나타났다. 앞서 언급한 그림 4에서 같이, 이들 촘촘한 공간에서 패드 간의 NSD 방식의 패턴이 존재해 있다. 6mil 혹은 그 이상의 패드-투-패드 간격에서는 어떠한 브릿지가 나타나지 않았다.

그림 19에서는 서로 다른 패드 사이즈 타입별 브릿지 불량 비율을 보여주고 있다. 불량 비율 퍼센트는 카테고리별 어셈블리된 부품의 카테고리/총 수량에 100%을 곱하여 불량의 수량을 계산했다. 더 큰 패드 사이즈는 직사각형 패드의 경우 보다 더 많은 브릿지 결과가 나오고, 홈베이스형 디자인은 직사각형 패드에 비해 솔더 브릿지 경향이 더욱 많았다는 것을 볼 수 있었다. 병렬구조 레지스터에 있어서 6mil 패드-투-패드 간격의 최소화는 01005 칩 레지스터용으로 권고되고 있다.

튬스톤

그림 20은 패드 사이즈 Type 1(100%) 패드의 경우, 튬스톤에 대한 패드-인-비아 디자인의 영향을 보여주고 있다. 예상대로, 비아-인-패드 디자인은 크게 악화되는 2개의 레지스터 패드 중 하나에서만 비아를 지닌 튬스톤 공산이 극적으로 늘어났다.

그림 21은 튬스톤 불량률에 있어서 리플로우 프로파일의 영향을 도표로 보여주고 있다. 데이터에는 모든 패드 사이즈 타입과 레지스터 방향을 포함하고 있다. 직선 램프-투-피크 프로파일은 소크 프로파일보다 상당히 우수했다.

그림 22는 Type 1 사이즈 패드(100%)에 있어서 레지스터 방향성의 작용에 대한 튬스톤 불량률을 도표로 보여주고 있다. 양쪽 리플로우 프로파일 데이터를 포함하고 있다. 레지스터 방향성은 튬스톤에 적은 영향을 미쳤다.

그림 23은 튬스톤 불량률에 있어서 패드 사이즈 타입의 영향을 도표로 보여주고 있다. 데이터에는 0°와 90° 정방향 그리고 양쪽 리플로우 프로파일이 포함되었다. 늘어나는 패드 사이즈 및 솔더의 체적은 튬스톤 불량률에 큰 영향을 끼친다. Ramp 프로파일을 이용해, 0° 및 90° 방향과 패드 사이즈 Type 2(90%)을 ramp 프로파일로 이용해 튬스톤 불량률은 실장된 1200개의 레지스터에서 0%이었다.

그림 24에서는 패드 사이즈 Type 1에 있어서 레지스터 길이 방향으로 2mil 의도적인 솔더 마스트 이동을 통해 어떠한 비아 패드가 없는 튬스톤 불량률을 비교하고 있다. ±2mil는 솔더 마스크 디자인 허용오차였다. 솔더 마스크를 이동하는 것은 솔더 가능한 동박 영역과 맞지 않았다: 패드는 하나의 가장자리에서만 패드가 존재하고, 패드는 다른 곳에서 4mil의 트레이스 길이가 더해졌다. 솔더 마스크 불일치는 튬스톤 불량률을 높이는 역할을 했다.

부품 유실

노즐 팁 개구 및 부품의 소형 사이즈 때문에 진공 센스는 부품 픽업을 확인하는데 사용되지 않을 수 있다. 노즐이 닳아지기 시작한 이후, 팁의 표면은 반짝거리기 시작하고, 비전 시스템은 가끔 소형 01005 부품으로써 반짝거리는 팁을 인식할 것이다. Tip wear는 부품 유실을 피하기 위해 적당한 모니터링이 될 필요가 있다.

Edge-standing 및 뒤집힘 부품

플레이스먼트 섹션에서 언급한 바와 같이, 뒤집힘 및 Edge-standing 불량은 수급된 테이프 내 부품 정방성에 기인한다. 부품의 대칭을 감안할 때, 비전 시스템은 꾸준하게 edge-standing 부품과 뒤집힘 부품을 검출하지 못할 수 있다. 벌크 피딩이 커다란 칩 부품을 위해 주로 사용되기 때문에 뒤집힘 부품은 이슈가 되지 않을 수도 있다. 이 경우, 업 혹은 다운 방향성은 큰 의미가 없다. Edge-standing 부품들은 테이핑 시스템 내에서 설명될 것이다.

신뢰성

패드 사이즈 Type 2에서 80개의 레지스터들은 -55℃~+125℃ 조건으로 열사이클이 진행되었다. 레지스터들은 열 사이클 동안 원래 자리에서 모니터되었다. 어떠한 레지스터 불량이 1000 열 사이클 이후 없었다.

결론

01005 칩 레지스터 플레이스먼트는 이미 연구되어졌다. 보드 제조업체가 ±0.5mil의 설계 허용오차를 유지하지 않으면 않을수록 패드는 거의 0.5mil 이하의 설계 치수가 된다. 전해주조된 3mil 스텐실은 4mil 스텐실과 비교해 견고한 페이스트 프린팅 프로세스와 더 높은 Cp 수치를 나타냈다. 솔더 침전의 높은 표면 체적비율 때문에 질소 리플로우가 우수한 솔더 젖음을 이루기 위해서 필요하다. 브릿지 불량과 관련해서, 병렬 레지스터의 패드 간격이 6mil 혹은 그 이상인 경우 어떠한 불량도 관측되지 않았다. 비아-인-패드가 없으며, 90%의 아주 적은 패드 사이즈(패드 사이즈 타입 2)로 설계된 직사각형 패드는 0° 혹은 90° 레지스터 방향성과 무관하게 램프 프로파일로 1200개 실장에서 어떠한 튬스톤이 나타나지 않았다. 이 조합의 경우 더 커진 샘플 사이즈는 ppm 불량률을 결정하기 위해 실행되어야만 한다. 실제 보드 상에서 보통보다 작은 패드를 감안할 때, 90% 패드의 평균 폭은 6.7mil(7.2mil 설계 값 대비)이었고, 01005 칩 레지스터의 측정된 폭은 7.1mil이었다. 그래서 패드는 칩 레지스터보다 폭이 약간 더 작았다. 이 패드 사이즈에서 솔더 접합의 초창기 열 사이클 신뢰성은 1000 열사이클 이후 어떠한 불량도 나타나지 않았다.

REFERENCES

1. R. K. Ulrich and L. W. Schaper, “Integrated Passive Components Technology”, 2003 IEEE, ISBN 0-471-24431-7, pp. 1-2.

2. S. V. Sattiraju, B. Dang, R. W. Johnson, Y. Li, J. S. Smith and M. J. Bozack, “Wetting Characteristics of Pb-free Solder Alloys and PWB Finishes,” IEEE Transactions on Electronics Packaging Manufacturing, Vol. 25, No. 3, July 2002, pp. 168-184.

3. Suk Chae Kang, Chunho Kim, J. Muncy, M.Schmidt, and D. Baldwin, “Experimental Wetting Dynamics Study Of Eutectic And Lead-Free Solders Varying Flux, Temperature and Surface Finish Metallization,” Proceedings of the IEEE/CPMT/SEMI 29th International Electronics Manufacturing Technology Symposium, July 14-16, 2004, pp. 56~63.

4. B. Huang, A.Dasgupta, and N.-C. Lee, “Effect of SAC Composition on Soldering Performance,” Proceedings of the IEEE/CPMT/SEMI 29th International Electronics Manufacturing Technology Symposium, July 14-16, 2004, pp. 45~55.

5. D. Shangguan, “0201 Assembly Capability for Miniaturization: From Design to Volume Manufacturing. Proceedings of 2003 International Printed Circuit & Electronics Assembly Fair Technical Conference and Exhibition, December 10-12, 2003 Guangzhou, China.

6. M. Wang, D. Shangguan, M.T. Ong, F. Mattsson, D. Geiger, and S. Yi, Assembly Process Qualification on 0201 Packages for Volume Manufacturing. Proceedings of SMTA International Conference, Sept. 2002, Chicago, IL, pp. 53~58.

7. M. Wang, D. Shangguan, D. Geiger, F. Mattsson, and S. Yi, “PCB Design Optimization of 0201 Packages for Assembly Processes”. Proceedings of the Telecomm Hardware Solutions Conference & Exhibition, SMTA/IMAPS, May 2002, Legacy Park, TX, pp. 103~108.

8. M. Wang, D. Shangguan, D. Geiger, K. Nakajima, C.C. Ho, and S. Yi , “Board Design and Assembly Process Evaluation for 0201 Components on PCBs”. Proceedings of APEX 2002, San Diego, CA, January 19-24, 2002, pp. S30?1-1 to S30?1-8.

9. M. Wang, D. Geiger, K. Nakajima, D. Shangguan, C. C. Ho, and S. Yi, Investigation of Printing Issues and Stencil Design for 0201 Package. Proceedings of SMTA Conference, October 2001, Chicago, IL.

10. J. Medernach and K. Suzuki, “0201 Process Development and Application Challenges”, Proceedings of the IPC SMEMA Council APEX 2001, San Diego, CA, January 14-18, 2001, pp. MP5-1-1 to MP5-1-5.

11. R. Brooks, M. Guilford and Doug Hendricks etc, “0201 Component Issues: Supply Chain, Design and Manufacturing Process”, Proceedings of the IPC SMEMA Council APEX 2001, San Diego, CA, January 14-18, 2001, pp. MP5-2-1 to MP5-1-7

12. P. N. Houston, B. J. Lewis, B. A. Smith, “High Speed 0201 Processing and Characterization” IPC SMEMA Council APEX 2001, San Diego, CA, January 14-18, 2001, pp. MP5-3-1 to MP5-3-8.

13. Reza Ghaffarian, S. Manian Ramkumar, and Arun Varanasi, “Lead Free 0201 Assembly and Thermal Cycle/Aging Reliability,” Proceedings of the IPC Expo/APEX Conference, Anaheim, CA, February 5-10, 2006, pp. S01-01-1 to S01-01-20.

14. Jason Fullerton, “0201 Process and Yield Improvement During Launch to Production,” Proceedings of the IPC Expo/APEX Conference, Anaheim, CA, February 5-10, 2006, pp. S01-03-1 to S01-03-10.

15. F. Mattsson, D. Geiger and D. Shangguan, “PCB Design and Assembly Process Study of 01005 Size Passive Components Using Lead-free Solder”, SMTA 2004

16. R. Jarvina, S. Greiner and R. Warren, “01005 SMT component Assembly for Wireless SIP Modules”, Proceedings of the 2005 IEEE Electronic Components and Technology Conference, May 31-June 3, 2005, Lake Buena Vista, FL, pp. 1502~1505

17. Chrys Shea, Bruce Moloznik, and David Hemmelgarn, “Printing and Profiling Fine Feature Devices,” Proceedings of the IPC Expo/APEX Conference, Anaheim, CA, March 31 ?April 2, 2003, pp. S02-3-1 to S02-3-12.