품질 및 성능 관련 객관적인 데이터 월등

빔균일도 우수한 맞춤형 BSOM 모듈이 핵심

LCD 디스플레이 업계에서는 OLED급의 화면품질을 구현하기 위해 로컬디밍(Local Dimming) 용도로 미니엘이디 백라이팅 기술을 적극적으로 채용하고 있다. 이러한 미니엘이디 적용에 있어서 매우 얇은 플렉시블PCB 위에서 고품질 솔더링과 고생산성 솔더링 기술을 구현해야 한다는 2가지 기술적 이슈가 있다. 이러한 요구를 충족시키기 위해서 첨단기술로서 선택적 레이저 리플로우(LSR; Laser Selective Reflow) 접합기술이 개발되었다. 본 논문에서는 LCD디스플레이용 미니엘이디 백라이팅 제조를 위한 고품질·고속 레이저 솔더링 기술과 불량품 미니엘이디를 제거하고 신규 양품 미니엘이디를 부착하기 위한 완전 자동 레이저 리페어 기술을 2회에 걸쳐 소개한다. 이번호는 2회차로 레이저 솔더링 기술을 활용한 리웍 공정 및 품질 결과를 알아본다.

미니엘이디 패널용 레이저 리웍 공정(Laser Rework Process for Mini-LED Panel)

그림 1에서 미니엘이디 패널용 레이저 리웍 공정에 대한 실험 셋업을 보여 준다.

레이저 리웍에 대한 핵심 요소들은 레이저 출력 전송용 광섬유와 SMA 커넥터를 포함하는 중출력과 저출력 DDL 레이저, 상대적으로 중형과 소형 빔크기 발생용 플랫탑 옵틱 모듈(BSOM; Beam Shaping Optic Module), 온도 검사용 적외선 카메라(IR Camera), 비전 모듈(Vision Module), 미니엘이디를 포함한 플렉시블 박형 PCB(Thin and Flexible PCB with Mini-LED), XYZ 구동 스테이지(Moving Stage), 접합 프로세스 GUI(Graphic User Interface)와 컨트롤 GUI를 포함하는 토털 컨트롤 시스템(Total Control System) 등이 있다.

그림 2에서는 미니엘이디 PCB 셋업부터 플로잉 접합 공정, 접합 품질 검사, 접합 공정 후의 전체 점등 검사(Global ON/OFF Test)와 휘도검사(Luminance Test)를 포함하는 미니엘이디 패널용 레이저 리웍 공정 흐름도를 보여 주고 있다.

그림 3의 (a) 상단 그림은 다음과 같은 핵심 레이저 리웍 공정을 보여 주고 있다. (1) 불량 접합 미니엘이디 칩 위치 검사(Defective Mini-LED Chip Location Check), (2) 불량접합 미니엘이디 칩의 제거(Removal of the defective Mini-LED Chip), (3) 레이저빔 출사 전의 리웍 위치에 솔더 닷팅 및 신규 양품 미니엘이디 칩의 부착(Solder Dotting at Rework Location and Attachment of New Mini-LED Chip without laser emission), (4) 레이저빔 조사를 통한 미니엘이디 칩의 레이저 접합(Mini-LED Chip laser bonding with laser emission). 그림 3의 (a) 하단 그림은 미니엘이디 칩 제거 전의 불량접합 미니엘이디 칩 위치 사진과 칩 제거 후의 위치 사진을 보여 준다. 다음 그림 3의 (b) 그림은 레이저 리웍 접합 온도에 대한 측정 및 제어 방법을 보여 주고 있으며, 온도 제어는 레이저 출력, 플로잉 속도, 빔크기를 잘 셋업하고 피드백 제어를 통하여 수행하게 된다.

플렉시블 PCB에 미니엘이디 칩을 레이저 접합한 후의 휘도 검사 모듈(Luminance Inspection Module)

플렉시블 PCB에 미니엘이디 칩을 레이저 접합한 후의 동작상태 검사는 점등검사를 통하여 이루어진다. 점등검사를 통하여 온/오프 상태(ON/OFF Status)와 휘도 레벨(Luminance Level)을 정량화하여 파악함으로써 미니엘이디 칩의 접합 품질이 양호 또는 불량 여부를 판단하게 된다.

첫째, 온/오프 검사에서 불량은 (1) 접합 공정 동안에 칩 위치 정렬불량(Misalignment)에 의한 전극 접합 에러(Electrode Bonding Error), (2) 양호한 전극 접합임에도 LED 구동회로 에러(LED Driving Circuitry Error)와 같이 2가지 에러 요인에 의해 발생할 수 있다. 이러한 불량들은 생산 수율을 낮게 만드는 큰 이슈를 발생시킴으로써 심각한 경제적 손실로 연결될 수도 있다.

둘째, 전극 접합 및 연결이 양호함에도 불구하고 미니엘이디 칩 자체의 불량 현상인 휘도 불량(Luminance failure)이 발생할 수 있다. 이 경우에 미니엘이디 칩은 정상 레벨보다 지나치게 어둡거나 밝은 휘도 레벨을 나타낼 수 있으며, 전체적으로 균일한 명도(Overall Uniform Brightness)가 보장되지 않아서 제품 불량으로 연결될 수 있으며 온/오프 검사 불량과 마찬가지로 경제적인 손실로 연결될 수 있다. 두 가지 모두의 불량을 해결하기 위하여 불량인 미니엘이디 칩 위치를 신속하게 인지하고 성공적으로 리웍 공정을 수행해야만 한다.

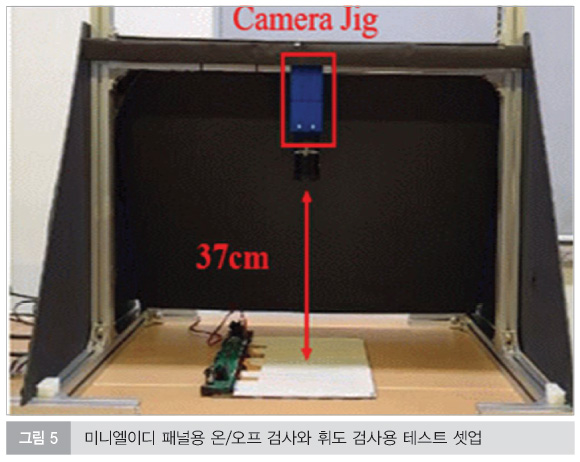

그림 5에서 미니엘이디 패널용 온/오프 검사와 휘도 검사용 테스트 셋업을 보여 준다. 휘도 불량 검사(Luminance Failure Inspection)를 수행하기 위하여 CMOS 카메라를 사용하였으며 미니엘이디 칩을 식별하고 전용 검사 알고리즘을 사용하여 합격/불합격 휘도 레벨을 확인함으로써 불량 칩의 위치 데이터(Location Data)를 검출하였다. CMOS 카메라는 5000만화소(50MP)의 센서와 픽셀 해상도 50um인 VC-50MC 모델이었고 카메라 렌즈는 FV3526L-F를 사용하였다. 카메라와 PCB를 암상자(Dark Box) 내부에 배치하여 배경 잡광(Background Noise Light)을 제거하였고, 상부에 카메라를 배치하고 하부에 미니엘이디가 장착된 PCB를 배치하였으며 카메라-PCB 간격을 370mm의 최적 거리로 설정하여 PCB 전체를 1장의 이미지로 획득하였다. 이때 최적 거리는 개별 미니엘이디 칩을 확실하게 독립적으로 식별 가능하면서도 PCB 표면 전체를 1장의 이미지로 촬영할 수 있도록 결정하였다.

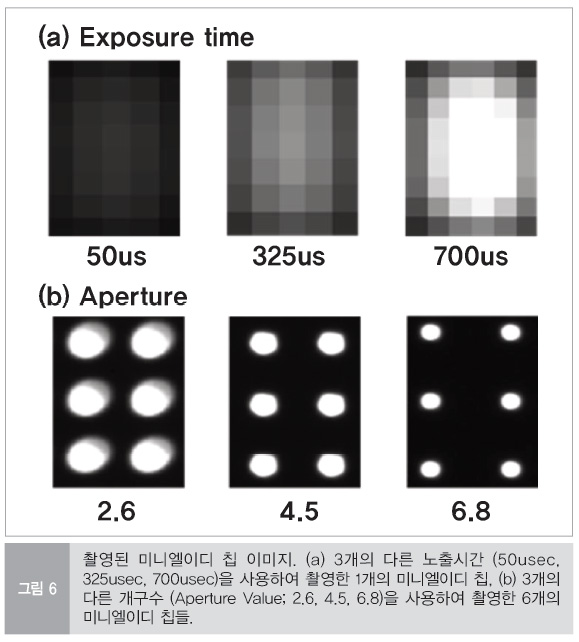

그림 6에서는 3가지 카메라 노출 시간과 3가지 카메라 조리개 개구수(Aperture Value)들에 따른 미니엘이디 칩 이미지를 보여 주고 있다. 카메라 노출 시간은 카메라를 사용하여 이미지를 획득하기 위하여 조리개를 개방한 시간(Aperture Opening Time)으로써, 이 노출 시간이 작을수록 어두운 이미지를 획득하게 되며 클수록 밝은 이미지를 획득하게 된다. 따라서 개별 미니엘이디 칩을 명확하게 독립적으로 식별할 수 있도록 최적의 노출시간을 찾아서 적용해야만 한다. 개구수는 카메라 조리개(Camera Aperture or Iris)의 광통과용 구멍을 얼마나 크게 개방하는가에 대한 수치로서 “개구수(F#) = 초점거리 / 조리개직경”로 정의된다. 개구수가 작을수록 조리개가 크게 개방되어 카메라 센서로 광량이 많이 입사되어 밝아지는 것이며, 개구수가 클수록 조리개가 작게 개방되어 카메라 센서로 광량이 적게 입사되어 어두워지는 것이다. 광량이 너무 많아져서 밝아지면 밝은 부분의 주변 화소에 광이 새어 나가서 밝은 긴 줄이나 뿌옇게 보이는 이미지를 발생시키기도 하는데 이를 광누출 또는 빛샘 효과(smear effect)라고 부른다. 또한 광량이 너무 많아지면 카메라 획득 이미지에 산란 현상이 발생하기도 한다. 이미지를 획득한 후에 밝기 수준은 8비트 또는 256단계로 구분하여 수치로 저장한다. 그림 6의 ‘(a) Exposure time’에서는 각각 50, 325, 700마이크로초(μsec)의 노출시간으로 촬영된 1개의 미니엘이디 칩에 대한 이미지를 보여 준다. 50μsec 노출시간에 대한 이미지는 개별 칩을 식별하기에 너무 어두우며, 700μsec 노출시간에 대한 이미지는 휘도 레벨을 계산하기에 너무 밝다는 문제점이 있어서 개별 칩 식별에 적당하고 가장 많은 휘도 레벨들을 구분할 수 있어서 휘도 레벨 계산에 최적인 325μsec를 최적 노출시간으로 결정하였다. 그림 6의 ‘(b) Aperture’에서는 3가지 조리개 개구수(F/2.6, F/4.5, F/6.8)를 사용하여 6개의 미니엘이디 칩을 동시에 획득할 때 개별 칩을 명확하게 식별할 수 있는데 최적인 조리개 개구수를 찾기 위한 테스트 결과를 보여 주고 있다. F/2.6과 F/4.5는 너무 많은 입사광량 때문에 광누출이 심하여 개별 칩을 명확하게 식별하기 어려움을 알 수 있다. F/6.8은 광누출 없이 명확한 이미지를 획득할 수 있어서 개별 미니엘이디 칩을 식별하기에 최적임을 알 수 있다.

그림 7에선 미니엘이디 PCB에 대한 휘도 불량 검사로 획득한 이미지를 보여 준다. 미니엘이디 칩을 식별하고 휘도 레벨을 계산한 후에 100% 기준 휘도 레벨과 비교하여 정상(합격; Good), 휘도 불량(불합격; Bad), 온/오프 불량(불합격; Bad)을 결정하였다. 개별 칩 화소에 대하여 중첩시켜 나타낸 녹색 박스는 정상 칩을 의미하며 80%~100% 휘도 레벨을 가지는 경우이며, 황색 박스는 휘도 불량 칩을 의미하며 20%~79%의 휘도 레벨을 가지는 경우이다. 적색 박스는 온/오프 점등 불량 칩을 의미하며 0%~19%의 휘도 레벨을 가지는 경우이다.

표 1에서는 최적화 후에 컴퓨터로 휘도 불량 검사를 5회 실시하여 획득된 데이터를 보여 주고 있다. 미니엘이디 칩을 정확하게 식별하여 카운트하였는지를 이해하기 위하여 정상 칩, 휘도 불량 칩, 점등 불량 칩을 카운트한 결과를 보여 주고 있다. 검사성공비율(Success Inspection Ratio) 또는 검출능력(Detection Power)은 정상 미니엘이디 칩의 식별에 대해서 검출 수량과 실제 수량의 비율인데, 정상 검출수량과 정상 실제 수량이 각각 16,700개와 16,725개로서 16700/16725*100 = 99.9%가 되어 매우 양호한 결과를 보여 주었다. 휘도 불량 칩과 점등 불량 칩에 대한 카운트에 있어서 측정된 수량과 실제 수량의 비율의 척도인 초과 계수 비율(Over-Censorship Ratio)은 (3407 + 53)/(3395 + 40) = 3460/3435 = 1.0073이므로 0.73%로 확인되었으며 이는 매우 작은 미니엘이디 칩의 휘도 검사에 있어서 매우 우수한 검사 결과로 판단되고 있다.

요약(Summary)

본 논문에서는 미니엘이디 백라이팅 LCD 디스플레이에 사용되는 미니엘이디 백라이팅 패널용 fLSR 레이저 접합 및 레이저 리웍 기술을 소개하였다. fLSR 접합 기술은 고속 생산 시간, 높은 생산수율, 매스 리플로우 대비 40% 향상된 접합 강도, 표면 색조 광택의 불변성, 표면 반사율의 불변성 등의 우수한 공정 성능 특성들을 나타내고 있어서 미니엘이디 제조 기술의 핵심 미래 기술이라고 정의할 수 있다. 이러한 우수한 공정 성능을 확보하기 위하여 400mm 길이를 가진 우수한 빔균일도를 가진 협폭 면적 빔을 생성할 수 있는 플랫탑 옵틱 모듈(BSOM 모듈)을 맞춤형으로 개발하여 적용하였다. 또한 최적의 공정 제어 소프트웨어와 장비 제어 특성들을 구현하였다. 또한 불량 접합 미니엘이디 칩을 제거하고 양품 미니엘이디 칩을 전자동으로 접합할 수 있는 미니엘이디 패널 레이저 리웍 장비를 개발하여 우수한 성능을 검증하였다.

* 감사의 말 (Acknowledgement)

본 연구는 재정적으로 산업통상자원부의 지원 (과제번호 20011140)을 받아서 수행되었다.

* 참고 문헌 (References)

[1] E. C. Charter, et al. (2004), CIE 130-1998 Technical Report: Colorimetry, 3rd edition, p. 18, CIE (International Commission on Illumination), Vienna, Austria.

[2] J. Krochmann, et al. (1998), CIE 15:2004 Technical Report: Practical Methods for the Measurement of Reflectance and Transmittance, CIE (International Commission on Illumination), Vienna, Austria.

[3] IEC 60749-19:2003/AMD1:2010 (2010), Semiconductor Devices –Mechanical and Climate Test Methods – Part 19: Die Shear Strength, 2010-11 Edition, IEC (International Electrotechnical Commission), Geneva, Switzerland,