다양한 프로세스 및 디자인 파라미터 중심의 연구

페이스트 타입, 예열 슬로프, 표면 마감재가 주요 요인

제조 관점에서 볼 때, 초소형 부품의 크기는 제조 장비의 성능과 다양한 공정 파라미터 제어에 심각한 문제를 제기한다. Plexus Electronic Assembly는 이러한 문제 중 일부, 특히 0402/0201 디바이스 및 튬스톤 결함을 형성하는 성향과 관련된 문제를 조사했다. 실험 결과 페이스트 Type, 예열 슬로프 및 표면 마감재 조건이 튬스톤과 관련된 중요한 파라미터임을 나타냈다. 프로세스 파라미터를 올바르게 모니터링하고 제어할 경우, 초소형 수동부품 실장 및 솔더링 프로세스는 매우 강력해질 수 있다. 실험에서 얻은 정보를 기반으로 0402 및 0201과 같은 초소형 수동소자를 사용할 때 튬스톤 결함을 예방하기 위해 여러 사항을 감안해야 한다.

전자산업계의 오랜 추세 중 하나는 전자 부품의 소형화이다. OEM(Original Equipment Manufacturer) 및 EMS(Electronic Manufacturing Service) 제공업체가 인쇄회로기판의 ‘차지 면적’을 줄이기 위한 노력을 지속함에 따라 이러한 움직임은 멈추지 않고 있다. 일반적으로 부품의 소형화는 통합 또는 크기 축소를 통해 이뤄질 수 있다. 크기 축소는 통합보다 비용 효율적이고 유연한 것으로 여겨지고 있다. 전류 제한, 전송선로 종단 및 디커플링 스위칭 노이즈에 사용되는 수동 부품은 다양한 용도로 인해 크기 감소가 주요 초점이 되었다.[4]

제조 관점에서 볼 때, 초소형 부품의 크기는 제조 장비의 성능과 다양한 공정 파라미터 제어에 심각한 문제를 제기한다. Plexus Electronic Assembly는 이러한 문제 중 일부, 특히 0402/0201 디바이스 및 튬스톤 결함을 형성하는 성향과 관련된 문제를 조사했다.

본고의 목적은 1) 튬스톤 메커니즘 및 설계 고려 사항, 2) 튬스톤에 영향을 미치는 잠재적 프로세스 파라미터, 3) Plexus 설계 테스트 기판을 사용하여 수행된 실험 설계(DoE) 결과를 논의하는 것이다.

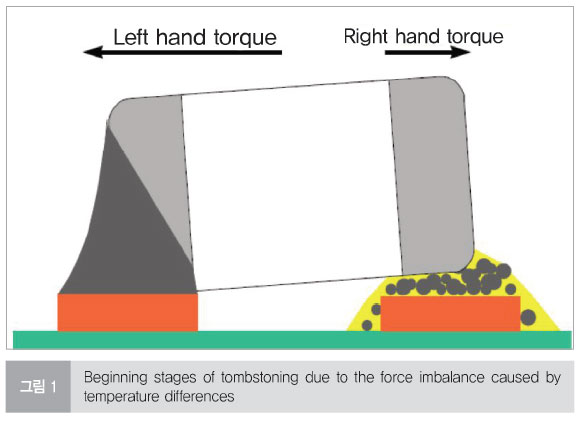

모든 솔더링 결함 중에서 튬스톤(맨해튼 현상, 드로우브리징 또는 스톤헨징이라고도 함)은 소형 수동 소자를 솔더링할 때 가장 일반적으로 나타나는 현상이다. 튬스톤은 솔더 페이스트에서 리드리스(leadless) 부품의 한쪽 끝을 들어 올리거나 세우는 현상으로 정의할 수 있다. 이 현상은 리플로우 솔더링 중 젖음력의 불균형으로 인해 발생한다. 중심에서 벗어난 부품을 정렬하는 데 도움이 되는 솔더의 셀프센터링(selfcentering) 력(力)은 튬스톤 효과에 기여하는 힘과 동일하다. 0402 및 0201 디바이스와 같은 소형 부품의 경우 용융 솔더의 표면 장력과 기판 및 부품 사이에 미묘한 밸런스가 존재한다. 이 밸런스는, 관련된 모든 요소의 솔더링 가능성이 약간 변경되고 부품 각 끝단의 솔더링이 리플로우되기 시작하는 정확한 순간의 차이로 인해 쉽게 깨질 수 있다. 그림 1은 소형 표면 실장 패키지의 튬스톤 시작 단계를 보여주고 있다.

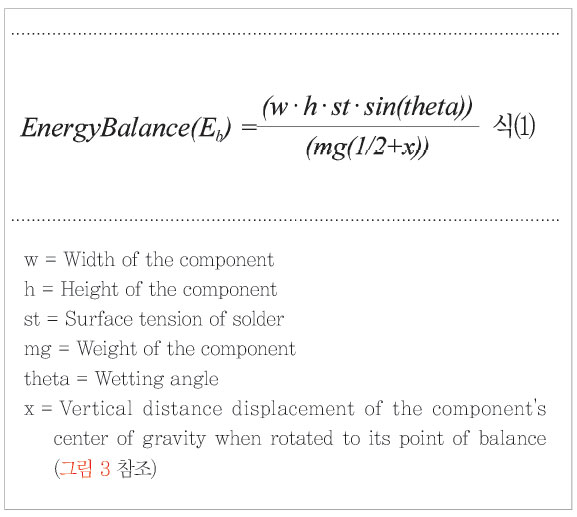

그림 1에서 알 수 있듯이 ‘우측 토크’는 부품을 움직이지 않게 유지하는 중력의 효과를 의미하는 반면, ‘좌측 토크’는 부품을 위쪽으로 당기는 표면 장력의 힘을 나타낸다. 에너지 균형 모델은 식(1)과 같이 표현될 수 있다.

쉬운 이해를 위해 오픈된 면의 솔더 페이스트는 부품에 아무런 영향을 미치지 않는다고 가정하였다. 그림 2와 그림 3은 에너지 균형 방정식에 사용된 다양한 용어의 세부 사항을 보여준다.

방정식의 사용을 이해하는 핵심은 ‘좌측’ 토크 힘이 1보다 큰 경우(EB>1), 가장 높은 위치 에너지 지점(그림 3의 왼쪽 참조)을 통과해서 부품을 들어 올릴 수 있는 충분한 표면 장력 위치 에너지가 존재하고, 그래서 튬스톤이 생성된다.

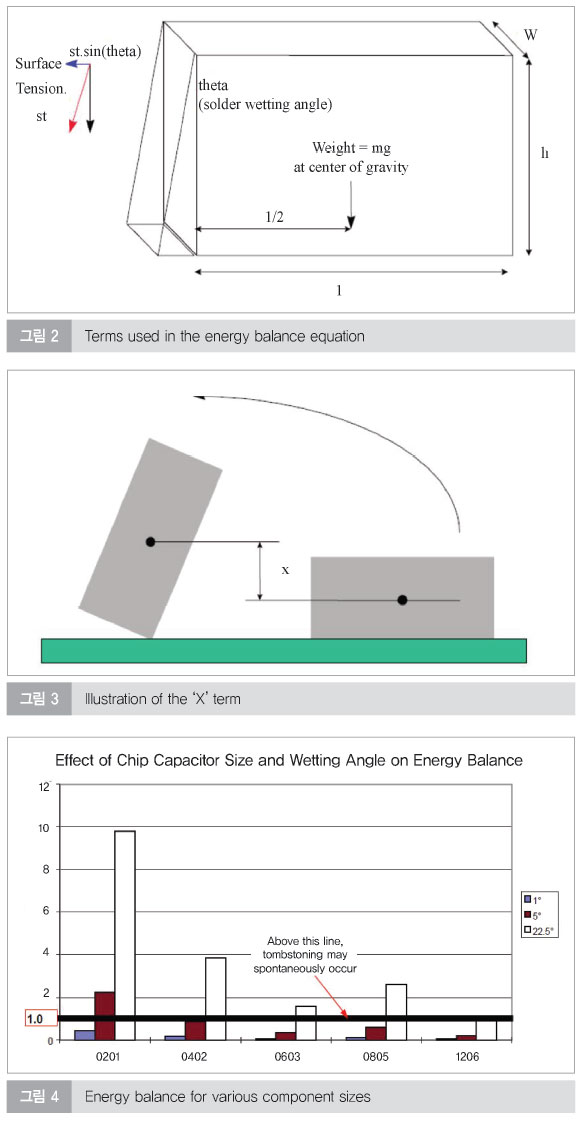

에너지 모델은 매우 조잡하지만, 부품의 크기가 줄어들수록 표면 장력의 힘이 매우 중요해져서 튬스톤 가능성이 커진다는 점을 분명하게 보여주고 있다. 0402에서 0201 부품으로 크기가 줄어든다는 것은 약 1/8의 부피와 약 1/5의 질량이 감소한다는 것을 뜻한다. 부품의 크기 외에도 솔더의 습윤 각도도 영향을 미치는 변수이다. 각도는 특히 습윤, 솔더의 양, 패드 형상과 관련된 물리적인 요인에 영향을 받는다. 그림 4는 크기와 습윤 각도가 에너지 균형에 미치는 영향을 보여주고 있다. 표시된 대로 Eb >1일 때 튬스톤 발생 비율이 늘어났다.

패드 디자인

열악한 풋프린트 디자인이 튬스톤 발생에 직접적으로 기여할 수 있다는 것이 입증되었다. 표면 장력 불균형으로 인한 좌측 토크의 밸런스를 맞추기 위해 SMT 풋프린트 확장을 줄여 솔더 접촉각을 줄일 수 있다.[5]

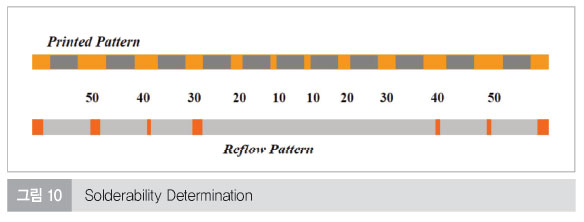

홈 플레이트 모양의 애퍼처 스텐실 디자인은 과도한 솔더 페이스트 증착 가능성을 낮추는 것으로 나타났다. 일반적으로 패드의 과도한 페이스트 증착으로 인해 리플로우 도중에 솔더 볼이나 솔더 비드가 형성된다는 것은 잘 알려져 있다. 연구에 따르면 홈 플레이트 디자인을 사용하면 일반 수동 부품에서 솔더 볼 형성을 제어하는 데 상당히 효율적인 것으로 입증되었다. 따라서 각 패드에 들어가는 페이스트의 양에 대한 더 우수한 제어를 얻기 위해, 이와 동일한 디자인을 초소형 수동 부품에 활용하는 것이 가능할 수도 있고, 그로 인해 결함을 줄일 수 있다.

솔더링 성

모든 솔더링 공정에서 부품과 기판의 솔더링 성은 가장 중요한 문제이다. 리플로우 중에 솔더가 완전히 젖을 수 있도록 모든 표면은 쉽게 납땜이 될 수 있는 조건이 되어 있어야만 한다. 특히, 대부분 보드 표면 처리 유형이 중요한 요소로 여겨진다. HASL(열풍 납땜 레벨링)은 효과적인 납땜 가능한 보드 표면 처리재로 수년 동안 사용되어 왔다. 그러나 HASL 처리와 관련된 균일하지 않은 표면으로 인해 단자의 소형화 추세 시 결함 레벨을 유지하거나 낮추기가 매우 어려울 수 있다. 결과적으로, 보다 균일한 평면의 구리 표면 코팅 마감이 필요해졌다. 최근 몇 년 동안 유기 납땜성 보호(OSP) 코팅 회로 기판이 Au/Ni와 같이 오랫동안 선호된 금속 도금과 은, 팔라듐, 주석과 같은 최신 기술과 함께 다양한 금속 도금이 주류가 되었다.

솔더 페이스트 증착

공융 솔더는 녹는점이 낮고 물리적 특성이 뛰어나기 때문에 전자기기 제조에 가장 많이 사용되었다. 그러나 소형 부품의 튬스톤 현상을 방지하기 위해 일부 업계에서는 은과 안티몬이 포함된 페이스트를 사용하는 것을 제안하였다. 이 두 금속의 조합은 솔더 페이스트의 리플로우 특성을 변경하여 궁극적으로 튬스톤 결함을 감소시킬 수 있는 것으로 추측된다.

다른 연구에 따르면 리플로우 속도는 솔더 페이스트 파우더 크기에 의해 영향을 받을 수 있다. 일반적으로 Type Ⅲ(325~500 메쉬)는 리플로우 솔더 작업에 사용되었다. 하지만, Type Ⅳ는 솔더/플럭스 입자의 직경 감소로 인해 고유한 장점을 가질 수 있다.[3]

리플로우 조건

리플로우 공정의 주요 관심사는 프로파일과 솔더링 분위기이다. 리플로우 프로파일의 예열 슬로프 또는 램프 속도가 너무 빠르면 플럭스의 휘발성 물질이 빠르게 증발하여 실장된 부품이 이동할 수 있다.[5] 이러한 위치 변화로 인해 튬스톤 가능성이 커질 수 있다. 이동 외에도 부품 길이에 따른 온도 차이 또는 열적 변화도 튬스톤 발생에 영향을 미친다. IR 구조의 솔더링 머신보다 대류 리플로우 오븐을 사용하는 장점 중 하나는 부품과 PCB 전반에 걸친 온도 균일성이 가능하다는 것이다. 그러나 대류 리플로우를 사용하더라도 불규칙한 리플로우의 가능성은 여전히 존재한다.

질소를 사용하여 리플로우 오븐을 불활성화하는 방식이 일반화되었다. 솔더링 중 질소의 효과는 유익한 것으로 입증되었다. 주요 장점은 용융 솔더의 젖음성이 향상되고 솔더링할 금속 표면의 산화물 형성이 감소한다는 것이다.[7] 그러나 오븐 내부에 존재하는 허용 가능한 산소 농도 수준은 지난 몇 년 동안 세밀하게 조사되었다.

과거에는 튬스톤 현상의 본질을 포착하기 위해 동적 수학적 모델을 개발하려는 전문가들의 노력이 이루어져 왔다. 컴퓨터 모델링의 사용을 포함한 일부 최근 개발에서는 튬스톤 표시의 필수적인 물리적, 기계적 원인을 상당히 효과적으로 예측하고 있다. 이러한 발전에도 불구하고 ‘실제’ 제조 시뮬레이션을 통해 얻은 프로세스 및 설계 파라미터의 영향은 최소화되어 있다. 이에 이러한 정보를 제공하기 위해 본 실험을 진행하게 되었다.

테스트 기판 설계

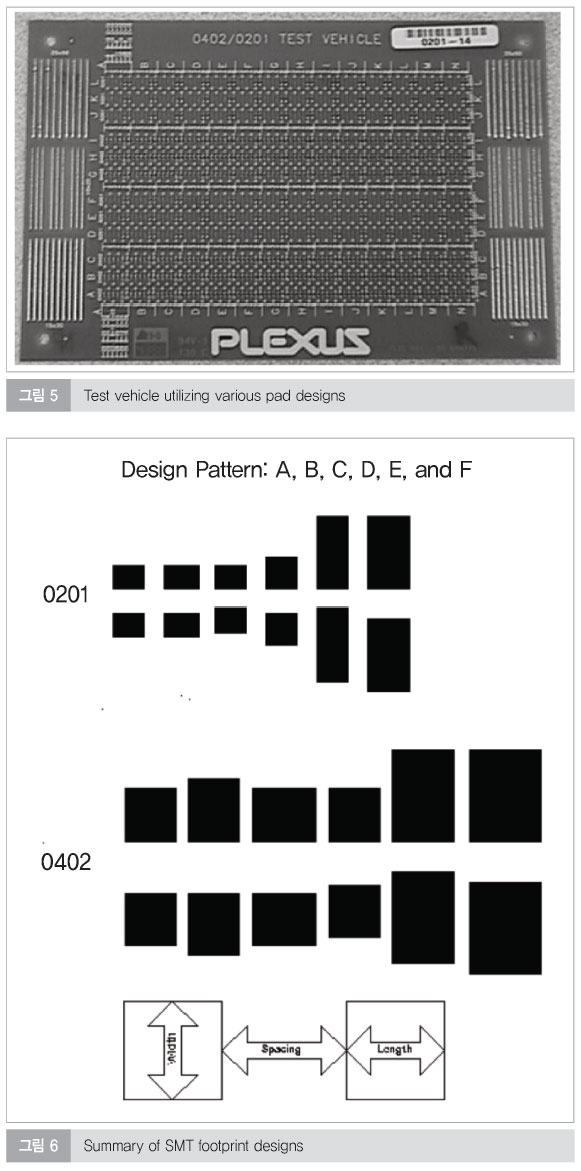

초소형 부품의 튬스톤 결함을 줄이기 위한 최적의 풋프린트 설계를 추가로 조사하기 위해 Plexus Technology Group에서 테스트 보드를 개발했다. 그림 5는 본 연구를 위해 개발된 테스트 보드이다.

테스트 보드는 소형 수동 소자용 잠재적인 패드 설계를 나타내기 위해 설계하였다. 서로 다른 12개의 SMT 풋프린트 디자인 조합을 통합하여 튬스톤 현상에 패드 디자인이 미치는 효과를 정량화했다. 패드의 길이, 너비 및 간격은 Plexus의 PCB 설계 지침에 따라 수정되었다. 그림 6에서는 연구에 사용된 SMT 풋프린트 디자인이 요약되어 있다.

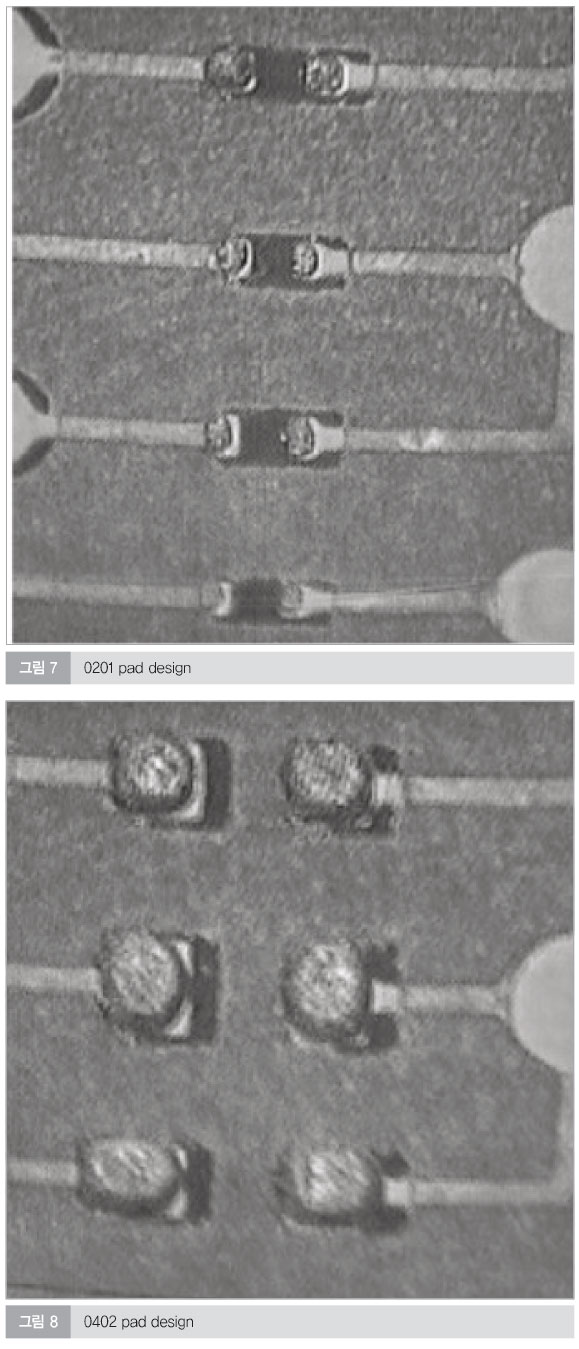

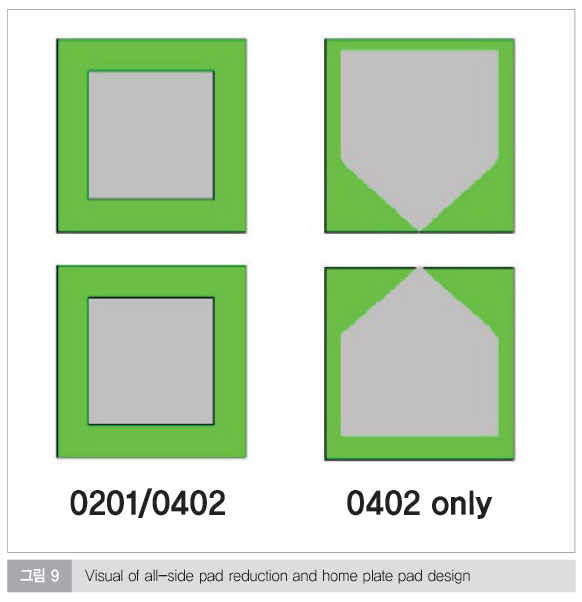

그림 7과 그림 8에서는 각각 0201 및 0402 부품에 대한 솔더 페이스트 증착과 함께 다양한 패드 설계를 보여주고 있다.

스텐실 디자인의 종횡비(aspect ratio) 요구 사항으로 인해 모든 0201 패드에 표준 전면 축소가 사용되었다. 본 연구에 사용된 전면 축소 및 홈 플레이트 패드 설계의 다이어그램은 그림 9에서 볼 수 있다.

솔더링 성(solderability) 시험

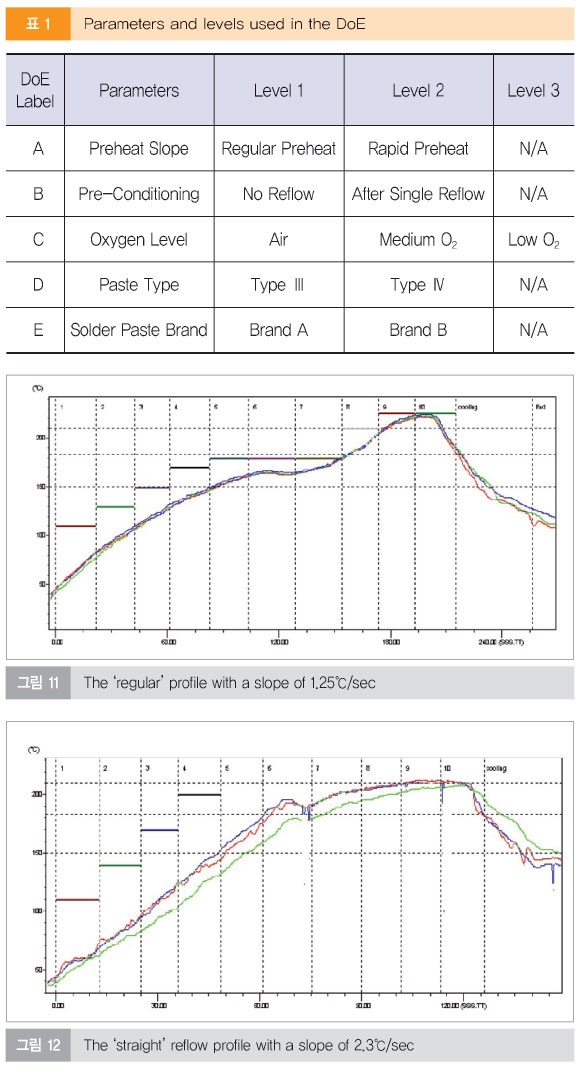

테스트 보드의 솔더링 성을 결정하기 위해 보다 ‘실제적인’ 솔더링 성 시험 접근 방식이 개발되었다. 이 테스트는 OSP 표면처리 된 일련의 긴 구리 라미네이트 영역에 페이스트를 정밀하게 증착하는 방식을 기반으로 하였다. 5mil 두께의 증착물이 각각 25mil × 50mil, 15mil × 30mil, 10mil × 20mil에 5mil 두께의 증착물을 올렸고, 행(row)은 10mil~50mil 거리를 다양하게 하여 분리하였다.

25mil × 50mil 및 15mil × 30mil 개구의 경우, 솔더링 성 데이터는 각 데이터 세트별 브릿지된 가장 큰 갭을 기록함으로써 정량화할 수 있다. 그림 10은 솔더링 성 테스트 기판의 왼쪽/오른쪽에 대해 30mil/20mil의 결과가 어떻게 얻어졌는지 보여준다. 가장 작은 개구 세트인 20mil × 10mil 데이터에서는 관찰된 브릿지되지 않은 갭의 수를 계산한 다음 이를 총 갭의 수로 나누었다.

Design of Experiment (DOE, 실험계획법)

앞서 언급한 영역의 영향을 탐색하기 위해 튬스톤 현상과 직접적으로 관련이 있는 것으로 간주되는 파라미터와 해당 레벨을 사용하여 전체 요인 설계 배열을 작성하였다. 표 1에서는 해당 DoE에 사용된 파라미터를 요약하였다.

파라미터에는 예열 속도, 보드의 프리-컨디셔닝(Preconditioning), 산소 농도 레벨, 솔더 페이스트 유형 및 솔더 페이스트가 포함되어 있다. DoE에 사용된 모든 파라미터는 제조 공정에서 가장 중요하고 가장 쉽게 변경되는 것으로 간주되었다. 설계에서 산소 농도 수준을 제외한 모든 파라미터는 두 가지 레벨로 구분하였다. 표 1에서 알 수 있듯이 산소 농도는 세 가지 레벨로 두었다. 각 파라미터의 다양한 레벨은 공급업체(질소 또는 페이스트 공급업체) 또는 ‘실제’ 생산 경험을 통해 결정되었다.

DoE에서는 예열 램프에 있어서 두 가지 레벨로 선정하였다. 낮은 레벨과 높은 레벨은 각각 약 1.25℃/초(‘regular’) 및 2.3℃/초(‘straight’)로 결정하였다. 그림 11과 그림 12는 실험에 사용된 프로파일을 보여주고 있다.

다음으로 설정한 파라미터는 프리-컨디셔닝(pre-conditioning)이다. 보드의 프리-컨디셔닝은 SMT 프로세스 이전에 열 사이클에 노출되었는지 여부를 나타낸다. 낮은 레벨은 보드를 리플로우에 노출시키지 않는 것으로 구성되었으며, 높은 레벨에서 처리된 보드는 질소가 풍부한 환경에서 한 번의 리플로우 사이클에 노출되었다. 이 ‘프리-컨디셔닝’ 단계는 양면 리플로우 기술을 사용하여 보드의 실제 상황을 가장 잘 시뮬레이션하는 것이다.

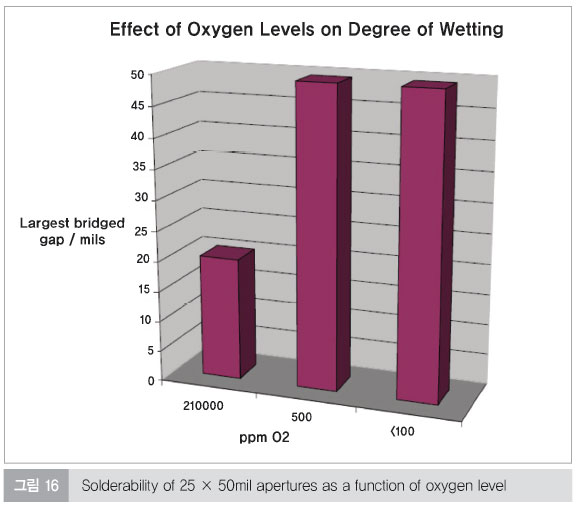

산소 농도는 솔더링에 영향을 미치는 중요한 요소이므로 2단계가 아닌 3단계의 파라미터로 포함하였다. 공급업체의 권장 사항에 따라 산소 농도를 210,000ppm O2, 500ppm O2 그리고 <100ppm O2의 세 가지 레벨로 하였다.

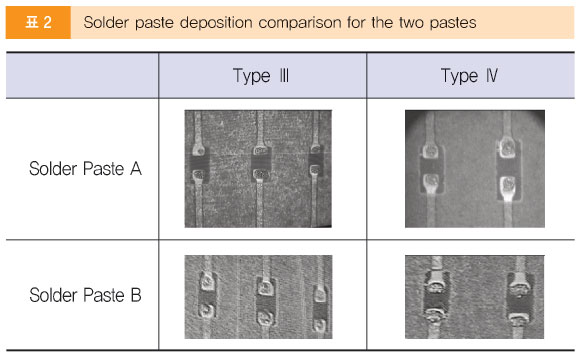

마지막으로 금속 조성과 입자 크기가 다른 두 가지 페이스트를 사용하여 튬스톤에 미치는 영향을 확인했다. 페이스트 브랜드 A는 일반적인 공융 솔더인 반면, 페이스트 브랜드 B에는 일정 비율의 은(Ag)과 안티몬(Sb)이 포함되어 있다. 또한, 서로 다른 솔더 입자 크기 간의 페이스트 증착 특성을 조사하기 위해 각 브랜드의 Type Ⅲ 및 Type Ⅳ 페이스트를 모두 사용했다.

이 다중 레벨 설계에서, 튬스톤 형성에 영향을 미치는 중대한 파라미터 및 관련 레벨을 조사했다. 설계 배열은 주요 요인이 상호 작용과 혼동되는 것을 방지하기 위해 완전 요인(48개 테스트 조합)으로 설정되었다.[2] 실험 오류의 척도를 얻기 위해 각 테스트 조합에 대해 두 개의 동일한 샘플 세트를 처리했다. 이전에 논의된 테스트 기판은 모든 실행에 대한 테스트 수단으로 사용되었다.

배열에 나열된 테스트는 무작위로 수행되었다. 이러한 무작위화는 실험에 포함되지 않은 특정 요인을 제어할 수 없을 때 실험 오류를 줄이거나 최소화한다. 모든 테스트 조합이 완료되면 솔더링된 부품의 육안 검사를 수행하였다. 부품 튬스톤에 대한 육안 검사가 응답 변수로 사용되었다.

실험 동안 총 48개의 서로 다른 테스트 조합이 검사되었다. 약 50,000개의 부품이 솔더링되었다. 본 실험에서 수집된 데이터는 분석을 위해 통계 소프트웨어에 입력되었다. 결과는 기판 설계, 납땜성 테스트 및 DoE 분석 간에 개별적으로 분석되고 요약되었다.

기판 디자인의 효과

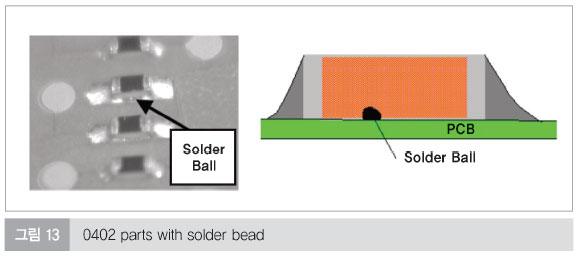

홈 플레이트형 스텐실 설계가 수동 소자의 공정 수율을 향상시키는 것으로 추측되었지만, 데이터에서는 공정 수율이 크게 향상되지 않은 것으로 나타났다. 예상한 대로, 홈 플레이트형 설계가 없는 일부 0402 부품 근처에서 최대 직경 2mil의 솔더 볼이나 비드가 발견된 것으로 나타났다. 그림 13은 관찰된 솔더 비드를 보여주고 있다.

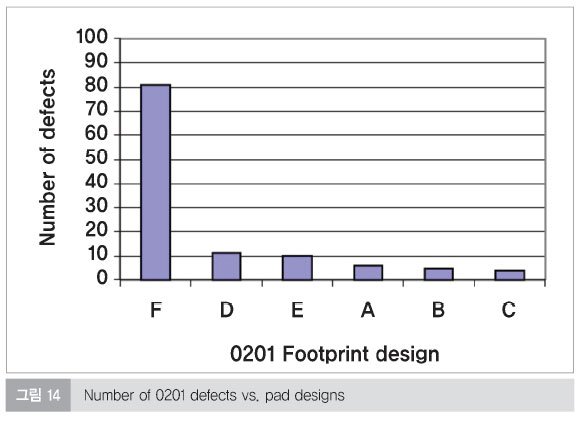

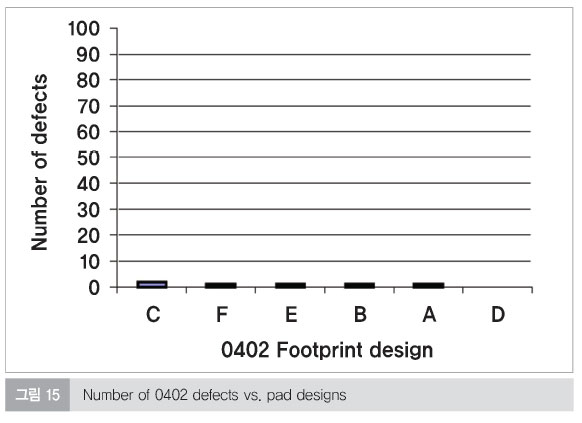

0201 부품의 경우, 엄청나게 큰 패드가 튬스톤의 주요 요인인 것으로 밝혀졌다. 에너지 방정식과 일치하며 그림 14에서 알 수 있듯이 길이가 길어진 0201 풋프린트는 튬스톤에 더 취약한 디자인으로 여겨진다. 놀랍게도 0402 부품의 결함률은 제시된 패드 설계 변화에 민감하지 않은 것으로 보인다(그림 15 참조).

솔더링 시험 결과

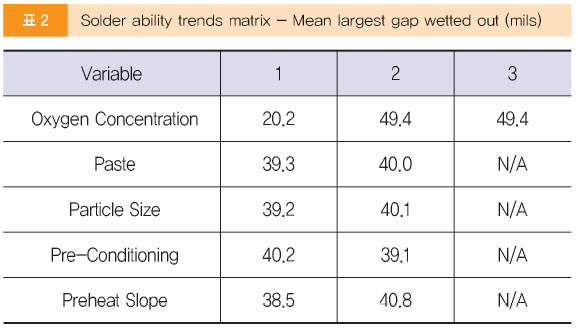

세 가지 다른 유형의 개구/간격에서 관찰된 경향은 매우 유사했다. 간결함을 위해 25 × 50 mil 개구에서 얻은 결과만 논의한다. 그러나 다른 두 유형의 솔더링 테스트 데이터에 따르면, 매우 유사한 거동을 보였다. OSP 마감처리 표면의 솔더링 성을 분석한 결과, 지금까지 가장 중요한 제어 변수는 리플로우 대기 상의 산소 함량임을 알 수 있었다. 세 가지 산소 농도 조건으로 수행된 모든 실험의 평균 결과를 비교하면 대기 상태와 산소 농도 약 500ppm에서의 솔더링 성은 매우 큰 차이를 보였다. 그러나 500ppm 산소에서는 솔더링 성 테스트 방법의 상한 한계에 도달하여 산소 농도가 100ppm 이하로 줄어듦으로써 OSP 마감에 대한 솔더링 성이 더 좋아졌는지 여부를 구별할 수 없게 만들었다. 전처리(preconditioning), 프로파일 유형, 입자 크기 및 페이스트 제조업체/플럭스의 효과는 약간의 경향을 보였지만 산소 함량의 효과가 단연 가장 컸다. 표 2와 그림 16에 OSP-솔더링 성의 경향을 요약하여 나타내었다.

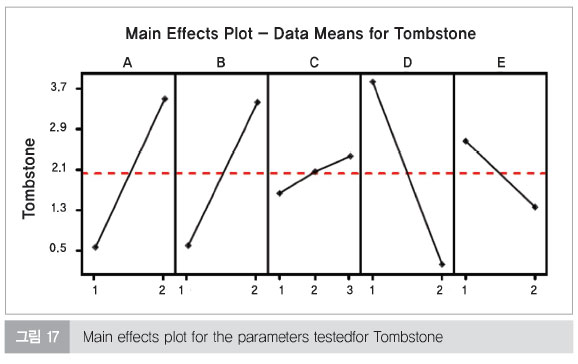

48번의 테스트 실행에서 수집된 DOE 데이터는 분석을 위해 통계 소프트웨어에 입력되었다. 정규성 가정(assumption of normality)을 확인하기 위해, 각각 관찰된 데이터 세트의 잔사 값에 대해 정규확률그림(normal probability plot)이 개발되었다. 하나의 특정 잔사는 나머지 데이터 포인트보다 훨씬 높았다는 점에 유의해야 한다. 신중한 조사 후, 실험 오류 때문에 외곽 응답(outlying response)이 폐기되었다. 분산 분석(ANOVA, An analysis of variance)이 중요한 요인을 결정하기 위해 수행되었다. ANOVA에서는 A, B 및 D(A = 예열 슬로프, B = 프리-컨디셔닝, D = 페이스트 타입)가 실험에서 튬스톤에 영향을 미치는 중요한 요인임을 밝혀 냈다.

그림 17에 표시된 주요 효과 모형은 예열 슬로프가 증가함에 따라 튬스톤의 빈도가 증가하고 OSP 마감이 프리-컨디셔닝 되었을 때 증가함을 시사한다. 또한 그림에서는 솔더 페이스트 타입 Ⅳ가 튬스톤 결함을 줄이는 데, 가장 중요한 영향을 미치는 것으로 명확하게 정의한다.

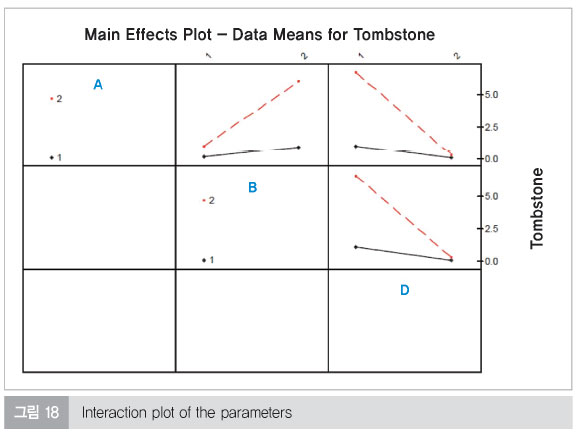

요소 간의 관계를 더 설명하기 위해 교호작용 플롯(interaction plot)이 개발되었다. 그림 18에서 이를 볼 수 있다.

ANOVA 표를 통해, 다음 파라미터의 조합이 튬스톤 결함의 수를 감소시킨다는 것을 알아냈다.

▶ 낮은 예열과 Type Ⅳ 솔더 페이스트

▶ 우수한 솔더성 마감재와 낮은 예열

▶ 우수한 솔더성 마감재와 Type Ⅳ 솔더 페이스트

교호작용 효과 분석에서 기재된 모든 해당 파라미터도 중요한 요인이라는 점에 유의해야 한다. 따라서 주요 효과는 튬스톤 현상에 큰 영향을 미치는 것으로 보인다.

리플로우 프로파일

예상한 바와 같이, 예열 슬로프의 증가는 이 DOE에서 중요한 요소인 것으로 보인다. 이는 튬스톤의 주요 원인이 다른 시간에 고체에서 액체로 위상 변화하는 솔더에 기인한다는 업계의 인식을 뒷받침한다.

수집된 데이터에서는 2.3℃/min의 예열 슬로프가 튬스톤 형성에 중추적인 역할을 한다는 것을 보여주었다. 슬로프가 늘어남에 따라, 솔더가 다른 시간에 녹는 점에 도달할 가능성도 커졌다.

프리-컨디셔닝

OSP 마감은 다중 리플로우 사이클에 맞춰 설계되었지만, 표면 마감재의 솔더링 가능성은 리플로우 조건에 노출됨에 따라 줄어들었다. 튬스톤에서 중요한 요소로 프리-컨디셔닝의 결과는 전혀 예상치 못한 일이었다. 이는 양면 리플로우 테크놀로지 어셈블리 상의 부품이 튬스톤이 될 확률이 높아지는 것을 의미한다.

Type Ⅲ 대 Type Ⅳ 입자 크기

모든 테스트 조합이 완료되기 전에도 Type Ⅳ 페이스트의 프린팅 품질이 Type Ⅲ 페이스트의 프린팅 품질보다 훨씬 우수하다는 것이 분명하였다. 표 3에서는 0201 패드의 일부 프린팅 패턴을 보여주고 있다. Type Ⅲ 페이스트의 솔더 증착 패턴은 상당히 불규칙했다.

솔더 페이스트 브랜드

통계적으로, Ag와 Sb을 함유한 솔더 페이스트 브랜드는 본 실험에서 중요한 요소가 아닌 것으로 나타났다. 따라서, 이들 금속이 느리게 용융됨으로써 튬스톤을 감소시킨다는 결론은 제공된 증거에 의해 입증될 수 없었다.

다른 관찰 사항

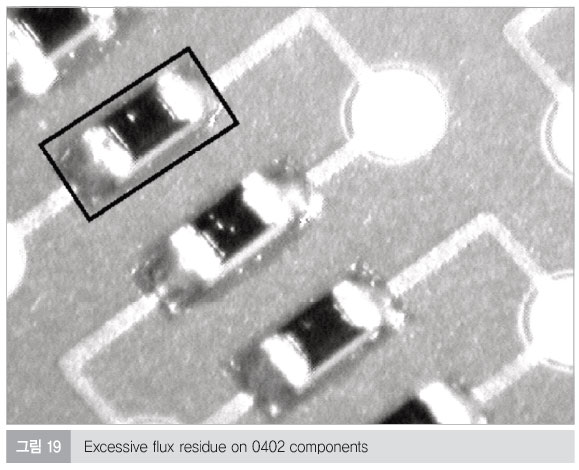

일부 테스트 보드에서 튬스톤 결함이 존재하는 것 이외에도, 일부 0402 부품 주변에 과도한 no-clean 플럭스 잔사를 발견할 수 있었다(그림 19 참조).

검출된 잔사량은 대기 상의 리플로우 처리된 보드에서 더 심각한 것으로 밝혀졌다. 이 발견은 과도한 플럭스 잔사가 주로 로진 및 산소의 존재와 관련이 있음을 의미한다.

DOE의 결과는 페이스트 Type, 예열 슬로프 및 표면 마감재 조건이 튬스톤과 관련된 중요한 파라미터임을 나타냈다. 프로세스 파라미터를 올바르게 모니터링하고 제어할 경우, 초소형 수동부품 실장 및 솔더링 프로세스는 매우 강력해질 수 있다. 실험에서 얻은 정보를 기반으로 0402 및 0201과 같은 초소형 수동소자를 사용할 때 튬스톤 결함을 예방하기 위해 다음과 같은 사항을 권장한다.

1. 일관된 솔더링 성을 제공하는 부품 및 PCB를 선택해야 한다.

2. 미세한 솔더 입자의 솔더 페이스트를 사용하여 솔더 점착성을 높이고, 프린팅 정의를 향상시킨다.

3. 열 프로파일을 최적화하여 단자 간의 잠재적인 온도 차이를 줄인다.

질소는 본 연구에서 튬스톤 결함에 영향을 미치는 중요한 인자로 밝혀지지 않았지만, 젖음성 증가 및 납땜 잔사 감소의 증거는 불활성 리플로우 환경에서 관찰되었다. 이 관찰은 업계 전문가가 수행한 여러 연구와 일치했다.

본 연구의 결과는 초소형 수동부품을 포함하는 PCA의 어셈블리 과정에서 제조 공정에서 Plexus에 의해 활용될 것이다. 또한, 모든 공정과 마찬가지로, 장비 및 파라미터의 지속적인 개선 및 최적화는 품질 결함이 없는 어셈블리를 생성하고 기술의 최첨단에 기여할 것이다.

REFERENCES

1. Anonymous, “Solder Paste Wettability Test”, Heraeus Technical Service Bulletin, February 1998.

2. Box G., Hunter W., Hunter J.S., Statistics for Experimenters, John Wiley & Sons, 1978.

3. Hwang J., Solder Paste in Electronic Packaging, Van Nostrand Reinhold, New York, 1995.

4. Klaiber R., Lasky R., Lassen C. and Thome J., “Critical Issues in Electronic Packaging Assembly”, Circuits Assembly, Dec 1995.

5. Prasad R., Surface Mount Technology Principles and Practices, Chapman and Hall, 1997.

6. Verbockhaven C., “OSP Coatings: Influence of Nitrogen Atmosphere”, Proc. NEPCON West 1996.

7. Wassink R., Seegers M. and Verguld M., "Use of Nitrogen in Reflow Soldering", Proc. NEPCON West 1993.

8. Wassink R., Soldering in Electronics, Electrochemical Publications Limited, 1989.

9. Yoshinobu A., “Reinventing the Manhattan Effect”, Electronic Packaging and Production, Feb 1991.

10.Yoshinobu A., “Surface Tension Effects on the Solder Joint”, International Conference on Electronic Assembly Material and Process Challenges, May 1996. |