많은 칩 애플리케이션의 경우, 시스템 복잡성 및 제조 프로세스 통합 등의 요구사항 때문에 하나의 칩 솔루션을 허용하지 않았지만, 반면에 이종 반도체 테크놀로지에서는 점차 요구되고 있다. 고밀도 I/O 배선이 필요한 분야에서는 이러한 이종 반도체 테크놀로지 배선을 필요로 하고 있다. 최소화가 요구되는 애플리케이션의 경우, 세라믹 혹은 유기물 칩 캐리어와 같은 전통적인 패키징 테크놀로지는 원하는 수준의 I/O 배선을 지원하지 못할 수도 있다.

실리콘 캐리어(silicon carriers) 적용 SoP(System-on-Package) 테크놀로지는 모듈 디자인의 유연성과 이종(異種) 칩의 고성능 통합을 제공하는 잠재력을 가지고 있다. 그리고 또한 2D 및 3D 칩 애플리케이션이라는 넓은 범위에서 고-수율/저-생산비용이 가능한 확실한 칩 제조능력도 제공한다. 핵심 기술에는 실리콘 관통전극(silicon through-via) 기술, 고집적 와이어링(high-density wiring), 칩의 많은 I/O 배선, 테스트 지원 및 어셈블리 기술 등을 포함하고 있다. 실리콘 관통전극은 효과적인 area array 신호, 전력 및 이들 박막 실리콘 패키지를 관통한 실리콘 배선을 허용케 하는 것이 핵심이다.

고집적 와이어링과 고밀도 칩 I/O 배선은, 실리콘 패키지 이용 ‘가상 칩’이 내재된 시스템-온-칩(system-on-chip)의 성능에 근접한 이종 칩들의 긴밀한 통합을 가능하게 할 수 있다. 실리콘 캐리어 제조는 제조 능력과 mid-UV 리소그래피(후속 CMOS 후공정 디자인 규칙에서 고밀도 패키지 와이어링을 제공하기 위한)에 영향을 미친다. 게다가, 실리콘 캐리어 패키지의 열팽창은 고밀도 칩 마이크로 범프 배선 크기와 비슷한 사이즈에서도 신뢰성 유지에 도움을 주는 칩에 영향을 끼친다. 추가적으로, 이종 칩 통합인 SOP 칩은 우수한 칩들인 수동부품 통합, 능동소자 및 전자광학 구조 또한 기능검사 성능 등을 필요시 마다 유지하면서 시스템 수준의 성능을 향상시킬 수도 있다. 본고에서는 기술적인 문제와 실리콘 캐리어 테크놀로지의 새로운 애플리케이션을 향한 최근 발달 동향에 대해 알아본다.

서문

지난 30년 동안, IBM은 1970년대에 멀티칩 모듈(MCM), 1980년대 및 1990년대 열전도 모듈(TCM) 그리고 1990년대 및 2000년대 최첨단 유기 마이크로-비아 빌드업 레이어 기술들을 소개해 왔다. 실리콘 기반 패키징(SBP)은 가까운 시일 내에 패키징 테크놀러지에 잠재적으로 영향을 줄 것이다.

차세대 칩들은 실리콘 관통전극, 고밀도 와이어링 및 파인-피치 배선이 가능한 실리콘 캐리어를 이용할 것이다; 이들 디바이스는 첨단 냉각 테크놀로지와 새로운 테스트 능력에 영향을 끼칠 수 있고, 2D 및 3D 구조를 지원할 수 있다. 첨단 반도체 회로 디자인은 106~108㎝-2 범위의 배선 밀도를 지녀 1억 회로 이상을 포함할 수 있다. 결과론적으로, 가장 낮은 비용, 가장 적은 사이즈 및 최상의 성능을 지닌 칩들은 SOC 칩 솔루션을 자주 이용해왔다. 시스템 기능은 호환 가능한 반도체 프로세스를 이용해 싱글 웨이퍼 위에서 제조될 수 있다.

많은 칩 애플리케이션의 경우, 시스템 복잡성 및 제조 프로세스 통합 등의 요구사항 때문에 하나의 칩 솔루션을 허용하지 않았지만, 반면에 이종 반도체 테크놀로지에서는 점차 요구되고 있다. 고밀도 I/O 배선이 필요한 분야에서는 이러한 이종 반도체 테크놀로지 배선을 필요로 하고 있다. 최소화가 요구되는 애플리케이션의 경우, 세라믹 혹은 유기물 칩 캐리어와 같은 전통적인 패키징 테크놀로지는 원하는 수준의 I/O 배선을 지원하지 못할 수도 있다. 실리콘 관통전극의 칩 적층 및 패키지와 같은 새로운 패키징 방법은 보완할 수도 있거나, 혹은 첨단 와이어-본드 칩 적층 패키지 및 세라믹 혹은 유기물 칩 캐리어와 같은 전통적인 배선과 패키징을 대체할 수도 있다. 실리콘 관통전극 및 고밀도 와이어링이 가능한 실리콘 캐리어는 타이트한 이종 칩 테크놀로지의 통합과 새로운 ‘가상 칩’ 혹은 SOP 솔루션을 지닌 SOC 성능을 달성한다는 의미를 가지고 있다.

실리콘 캐리어 테크놀로지 기반 SOP 테크놀로지의 목적은 1) 모듈러 칩 디자인의 유연성 제공 2) 싱글칩 통합과 동등하거나 초과하는 성능의 이종 칩 테크놀로지들의 통합 3) 높은 칩 제조 수율 지원 4) 낮은 칩 생산비용 지원이다. 실리콘 캐리어를 가지고서, 각각의 칩은 시스템 성능 및 제조 수율을 위해 개별적으로 최적화될 수 있다. 실리콘 관통전극 기반 패키징은 전기 광학 테크놀로지를 가진 새로운 SOP 칩의 토대를 제공할 수 있다. 그리고 실리콘 기반 소형 멀티칩 모듈(MMCM, mini-multichip module)은 일반 상업용과 특수용 칩 애플리케이션에서 모두 매력적이다.

패키지 배선과 와이어링을 위한 실리콘 기반 패키징 솔루션은 1972년에 제안된 실리콘 패키지를 시작으로 지난 30년 동안 제안되어 왔다. 그러나 이 같은 방법들이 칩 혹은 실리콘 패키지를 위해 경계선 접합에 이용되어 왔으며, 경계선 접합은 전력 분산 및 I/O 신호 제한이라는 점 때문에 자주 부적합하다고 여겨져 왔다. 실리콘 기반 패키징은 후공정(back-end-of-line, BEOL) 프로세스를 활용해 고밀도 와이어링을 제공할 수 있다. BEOL 와이어링 접지 규칙은 고수율 및 저생산비용이 가능한 이전 실리콘 세대의 것이 된다.

실리콘 캐리어의 열팽창은 높아지는 칩-패키지 인터페이스 신뢰성의 캐리어에 실장된 실리콘 디바이스와 동일하다. 또한 정합(整合)된 열팽창은 솔더 마이크로범프(μ-C4) 혹은 칩과 실리콘 캐리어 간의 동박 배선과 같은 진일보된 배선의 이용을 가능케 한다. 게다가 이 기술은 캐시 메모리용 DRAM, 위상동기회로(phase-locked loop) 혹은 I/O 드라이버와 같은 캐리어 자체에 수동소자의 임베디드를 가능하게 한다. 관통전극(through-via)이 가능한 실리콘 캐리어는 혼합 반도체 테크놀로지들을 지원할 수 있으며, 능동 혹은 수동 회로와 전기광학 테크놀로지의 고밀도 I/O 와이어링 배선을 제공할 수 있고, 3차원 회로집적을 지원할 수 있다. SOP 실리콘 캐리어 테크놀로지는 반도체 리소그래피 내에서 진일보된 확장성으로 고-성능 및 저-비용 패키징 솔루션을 모두 제공할 수 있다.

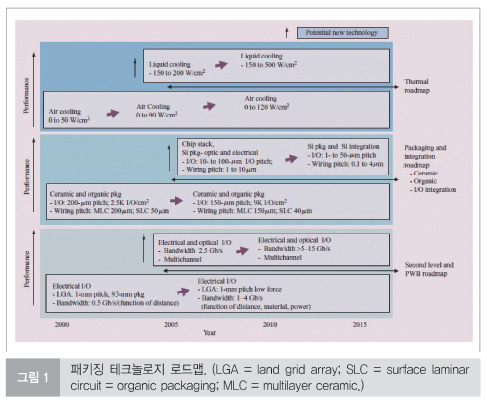

그림 1에서는 패키징 테크놀로지 내에서 1) 열 냉각, 2) first-level 배선 및 패키징, 3) second-level 배선 및 PCB 3가지 영역으로 나눠 발전되고 있는 추세를 보여주고 있다. 진일보된 열 냉각용 인터페이스 재료는 50W/㎝-2~90~120W/㎝-2까지 직열 전도(direct heat conduction) 용량을 향상시킬 것이다.

또한, 냉각은 마이크로-채널 수냉(liquid cooling)의 수용제 혹은 수용제의 충돌제트(jet impingement)로 이뤄질 것이고, 그래서 칩 동작 온도를 내릴 것이다. 동작 온도 하악으로 칩 성능이 증가하기 때문에, 수냉은 성능 밸런스와 용량 냉각을 위한 칩 설계 디자인의 최적화를 제공한다. 플립칩 기술과 같은 First-level 배선 테크놀로지는 파인 I/O 피치 및 와이어링(유기물 및 세라믹 패키징 솔루션 본연에 기반 된)을 향한 진일보를 거듭하고 있다. 칩 적층(chip stacking) 및 패키징용 실리콘 적용과 같은 이머징 솔루션(emerging solution)은 더 높은 레벨의 집적에서도 적용될 수 있다. 더 높은 칩 집적은 3D 칩 와이어링을 통해 이뤄질 수 있지만, 이 같이 늘어난 집적 성능으로부터의 이점을 위해서는 효율적인 비용의 어셈블리 및 테스트를 지닌 정밀 정렬(precision alignment)이라는 핵심 애플리케이션이 적당한 신뢰성을 가져야만 한다.

Second-level 배선의 발전 및 향상된 PCB는 전기 및 광학 배선을 혼합함으로써 더 많은 통신 주파수를 지원하기 위해서 요구되고 있다. 광학 집적은 전기 와이어링보다 더 낮은 전력과 더 긴 거리에서 늘어난 통신 대역폭을 제공할 수 있다. 그렇지만 짧은 거리의 경우, 광학 집적이 낮은 비용으로도 사용 가능하거나 혹은 공간 한계로 인한 실용화가 이뤄질 때까지, 전기집적이 비용 효율적인 방법으로 더 높은 주파수를 사용될 수 있도록 지속적으로 연구되리라 기대된다.

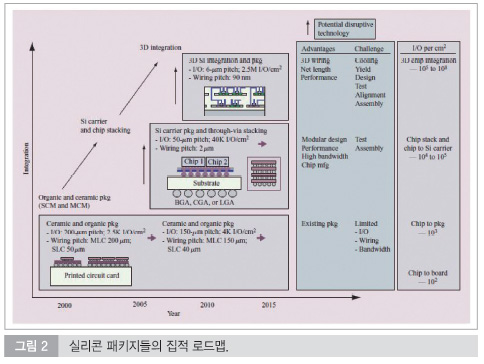

그림 2에서는 향후의 2D/3D 패키지와 집적 레벨을 향상시키는 칩 집적 방법의 일부 프로젝트를 보여주고 있다. 실리콘 칩 적층, 실리콘 캐리어 혹은 3D 칩 회로를 이용한 방법들은 모듈러 디자인, 향상된 성능 및 낮은 제조비용과 같은 이점을 제공한다. 특정 새로운 패키징 테크놀로지, 어셈블리, 테스트 및 신뢰성의 경우에는 늘어난 집적 용량 및 성능의 이점을 주기 위해서 비용-효율적이 되어야만 한다. 와이어-본드 칩 적층 테크놀로지와 비교해 실리콘 관통전극은 또한 회로(더 높은 주파수 동작을 지원하는 낮은 전기적 기생손실(electrical parasitic losses)을 지닌) 간의 배선 거리가 더 짧다. 실리콘 캐리어 MMCM은 전기/광학 부품의 집적을 위한 높은 유연성을 제공한다. 게다가 전도성 관통전극 와이어링인 실리콘 캐리어는 집적 수동소자, MEMS 및 광학부품의 자기정합 어셈블리용 미세가공 홈(micromachined recesses)을 포함할 수 있다.

추가적으로, 실리콘 캐리어 상면의 파인피치 μ-C4 접합 패드는 플립칩 실장 부품 사이에서 고밀도 배선을 가능케 한다. 칩투칩 공간, 칩 사이 와이어링, I/O 밀도는 고성능 이종 테크놀로지의 집적을 지원하는 현재 패키징 용량과 비교해 10X~100X 만큼 향상될 수 있다. 실리콘 캐리어는 실리콘 칩의 그것과 동일한 팽창의 열 계수를 가지고 있기 때문에, 솔더 배선을 위해 배선 피치들이 수십 미크론 혹은 더 작게 측정될 수 있을 것이며, 동박 배선을 위해 훨씬 더 작게 될 수 있을 것으로 기대된다. 적층-웨이퍼 구조를 이용한 3D 회로 집적의 경우, 지속적으로 진일보된 웨이퍼-레벨 프로세스/집적이 3D에 유리한 와이어링을 제공하기에 심지어 더 짧은 망 길이를 제공할 수도 있다.

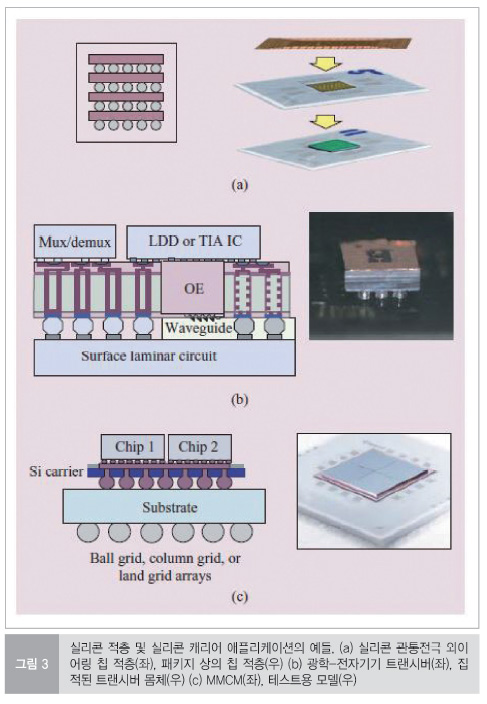

그림 3은 실리콘 기반 패키징 애플리케이션의 대표적인 그림이다. 그림 3의 a)는 집적된 칩 적층/인터포져, b)는 광학 전기 트랜시버 c)는 MMCM의 종단면 모식도를 보여주고 있다. 본고에서는 최근 실리콘 관통전극 패키지, 최적의 칩 적층, 실리콘 기반 전기-광학 패키징 및 MMCM 패키지 집적을 적용한 SBP 테크놀로지의 발전동향을 설명하고 있다. 생산현장 산업계의 진일보, 디자인 고려사항, 이론 및 경험적 결과에 대해 논의하고, 실리콘 관통전극 컨덕터의 제조를 위한 기계적인 문제들을 핵심적으로 설명한다.

칩 적층 및 통합을 위한 산업계 진일보

1972년 수동 혹은 능동 실리콘 캐리어에 연결된 μ-C4에 의해 제안된 실리콘-온-실리콘 구조가 D. J. Bodendorf 등에 의해 보고되었다. 제안된 캐리어의 한 가지 이점은 칩간 열팽창의 동일한 계수이고, 배선의 열사이클 피로 문제를 해결한다는 것이다. 그래서 칩-온-칩 적층을 적용하는 산업계에서는 와이어 본딩 및 VLSI(very-large-scale-integration) 반도체 칩의 시스템 통합에서의 이용과 같은 다양한 방면으로 사용하고 있다. 통합의 확산은 특히, 1990년부터 현재까지 신중하게 진행되어 왔다. 1990년대 초반 칩 적층 테크놀로지를 예로 들자면, 접착제를 가지고 두 개의 칩을 붙이고, 칩 주변에 와이어-본드하면서 시작되었다.

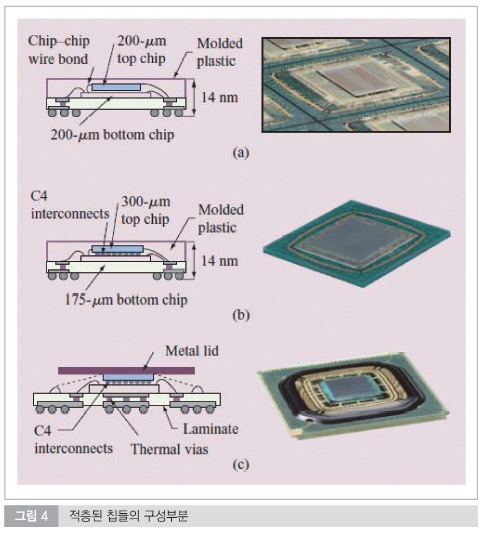

1990년대 중반, 칩 적층의 예를 들자면, 단지 두 개 칩을 이용해 메모리와 마이크로프로세서 배선을 위해 자주 이용되었다. 시간이 흐른 뒤, 칩 적층 테크놀로지는 단지 와이어 본딩만으로 혹은 칩과 칩의 배선(어레이 솔더 접합, 패키지에 배선을 제공하는 커다란 다이에 소형 칩(다이)이 표면실장으로 결합된)과 같은 다양한 적층 형태로 발전했다. 더욱 복잡해진 칩 적층 테크놀로지의 제품들이 8개 혹은 그 이상의 칩을 위해 2개의 적층되었고, 경계 와이어-본드 배선, 유연한 패키징 겹침 혹은 플립칩 배선의 조합 및 와이어-본드 배선을 이용해 등장했다. 그림 4에서는 이들 제품들을 보여주고 있다. 그림 4(a)에서는 1.4㎜ PBGA(plastic ball grid array) 패키지 및 1.5W 전력손실(거의 100개 사이의 다이 접합 및 3㎜ 미만의 와이어본드 길이로 산업계에서 사용이 가능한 100㎛의 와이어본드 다이 피치를 지원한다)보다 적은 와이어-본드 칩 적층을 보여주고 있다. 그림 4(b)는 플립칩 적층과 1.4㎜의 많이 와이어-본드된 PBGA 패키지(2W 전력손실, 16개의 배선/㎟ 플립칩 접합 및 300㎛ 패키지가 다이 상부 경계선에 와이어 본드된 배선)를 나타내고 있다. 그림 4(c)에서는 열적으로 향상된 플립칩 적층(8W 전력손실의 리드를 이용한 3.7㎜의 많은 BGA 패키지)을 보여주고 있다. 좀 더 최근에는, 산학연(독일의 Fraunhofer Institute, the University of Alabama, 일본의 the Association of Super-Advanced Electronic Technologies(ASET), the Interuniversity MicroElectronics Center (IMEC))이 새로운 차세대 칩 적층 테크놀로지와 SiP 혹은 SOP 제품들을 보고하고 있다. 칩 적층 테크놀로지 연구소의 보고서에서는 실리콘 관통전극 제품의 장점과 현존하는 와이어-본드 테크놀로지 제품과 비교한 예를 담고 있다. SiP 및 SoP 보고서에서는 전통적인 패키징, 전형적인 세라믹, 유기물 및 수동부품 집적 및 2D/3D 와이어링 집적을 이용한 박막-필름 테크놀로지의 확산을 예로 들었다.

칩 적층 및 첨단 SoP 패키지 배선 솔루션을 이용해 적용될 수 있었던 시스템 통합의 더욱 향상된 수준을 향한 연구는 1990년대 후반에서부터 지금까지 진행되어 왔다. SoP 테크놀로지는 고밀도 I/O 칩 적층, 칩에서 패키지로의 고밀도 I/O 배선 혹은 광학전자기기에서 필요로 하는 수준의 통합에 이용할 수 있다. 이러한 구조는 통합된 수동소자 및 3D 설계 구성에 있어서 통합 회로에 이점을 준다. 3D 설계는 일상품 및 복잡한 가전제품들 자체를 최소화시킬 수 있다. 1990년~2000년대 동안 IBM의 첨단 집적기술은 반도체 BEOL 와이어링 접지 규칙에 영향을 미쳤다. BEOL 와이어링 규칙은 일반적인 패키징 와이어링 규칙보다 10~100배 더욱 미세하고, 이미 구성된 제조 프로세스 및 장비들을 이용해 고-수율을 낼 수도 있다. 산학연 연구에서 IBM은 실리콘 관통전극 테크놀로지를 연구 담당했다. 이 테크놀로지는 새로운 종류의 가전기기에서 요구하는 높은 I/O 밀도, 고성능 및 저-생산비용을 충족시킬 수 있다.

시스템 디자인을 위한 애플리케이션 및 고려사항

SoP 테크놀로지의 근본적인 이점은 자체적으로 높은 집적 모듈러 시스템 혹은 최적화된 비용, 사이즈 및 성능을 가진 하부 시스템을 지원할 수 있다는 것이다. 그리고 타임투마킷을 실현할 수 있고 칩 디자인 블록(구분)의 재사용이 가능하다. 따라서 중요한 것은 패키지 테크놀로지, 어셈블리, 테스트 및 신뢰성의 일반적인 사항들뿐만 아니라 전체 시스템 기능요구 및 제조 프로세스와 관련한 디자인 측면이 반드시 고려되어야만 한다. SoP 테크놀로지는 다층 첨단 패키징 기술에 각각의 최종 애플리케이션 커스터마이즈 솔루션이 가능하도록 조합할 수 있다.

SoP가 사용될 수 있는 시장으로는 이미지 센서, 고밀도 메모리 플래시카드뿐만 아니라 RF 및 무선 디바이스(초창기 휴대전화, WLAN, 블루투스 솔루션) 및 파워서플라이, 자동차 전장 등이 있다. 최근에 SoP 애플리케이션은 일반적으로 모듈, 적층-다이 패키지, 적층된 패키지 이 3가지의 범주 중 하나에 포함된다. 비록 플립칩/와이어-본드 조합이 점차적으로 증가하고 있음에도 불구하고 와이어 본드된 다이 적층과 결합된 박리 기판이 시장에서 우세를 보이고 있다. 적층-다이 CSP가 선도적으로 이용되고 있는 상업 분야로는 핸드셋 시장이 대표적이다. 이는 메모리 기능의 확대(메시지, 컬러 디스플레이, 쌍방향 게임 및 또 다른 기능들)와 동시에 사이즈 감소를 향한 디자인 압박 때문이다.