TSV 활용 가능성 높이는 기술 제안

불량 없는 높은 수율 달성이 중요

차세대 3D 패키징은 3차원 적층 반도체 칩 구조를 생성하는 TSV(through silicon via)의 사용이다. 3차원 이기종 집적 반도체 구조는 전력감소, 성능향상 및 소형화 등과 같은 많은 이점을 제공한다. 이들 TSV 생성을 위한 반도체 기술의 실행 가능성은 이미 도달하였다. 그러나 3차원 반도체 구조 패키지의 다음 단계는 대량 생산에 대한 비용 효율적인 기술로 만들기 위해서 어디에 중점을 둘 필요가 있느냐이다. 논의 또 다른 주요 주제는 누가 3D IC 어셈블리를 담당할 것인가이다. 과거 반도체 제조사는 다이를 설계 및 제조했고 그런 후에 어셈블리와 테스트를 위해 패키징 업체에 전달했다. 본고에서는 4개의 다른 어셈블리 플로우를 언급할 것이고, 이들이 Foundry 중심 프로세스 플로우 혹은 OSAT 중심의 프로세스 플로우 둘 중 하나와 어떻게 부합하는지를 논의할 것이다.

3D IC 어셈블리에 있어서의 도전과제는 어떻게 휨을 관리하고, 얇은 웨이퍼를 핸들링하느냐이다. 이는 높은 어셈블리 수율을 이루고, 최종 구조물이 지정된 신뢰성 요구를 통과할 수 있게 보장하기 위해서이다. 테스트 시료는 60㎛~30㎛ 범위 내의 피치들로 된 마이크로-범프된 다이를 가지고 있다. 패드 밀도가 더 높아지고, 다이 사이즈가 더 커졌기 때문에, 모든 마이크로-범프 상호접합물들이 얇은 Si-인터포저에 어테치되도록 보증하기가 매우 어렵게 되었다. 게다가 다이와 인터포저 사이의 낮은 스탠드오프는 언더필을 어렵게 만들고 있다. 이 방법은 우선 인터포저에 다이를 어테치하는 것이고, 그 다음 서브스트레이트에 다이/인터포저 sub-어셈블리한다. 이 시나리오의 경우, 다이/인터포저 서브-어셈블리는 서브스트레이트에 플립칩이 어테치될 수 있는 모놀리식 실리콘 다이와 유사하다. 본고에서는 다양한 어셈블리 옵션과 각각의 도전과제들을 논의할 것이다. 조사를 통해서, OSAT(Outsourced Assembly and Test) 설비에서 2.5D 어셈블리를 하는 최상의 방법을 제안할 것이다.

서문

차세대 3D 패키징은 3차원 적층 반도체 칩 구조를 생성하는 TSV(through silicon via)의 사용이다. 3차원 이기종 집적 반도체 구조는 전력감소, 성능향상 및 소형화 등과 같은 많은 이점을 제공한다. 이들 TSV 생성을 위한 반도체 기술의 실행 가능성은 이미 도달하였다. 그러나 3차원 반도체 구조 패키지의 다음 단계는 대량 생산에 대한 비용 효율적인 기술로 만들기 위해서 어디에 중점을 둘 필요가 있느냐이다.

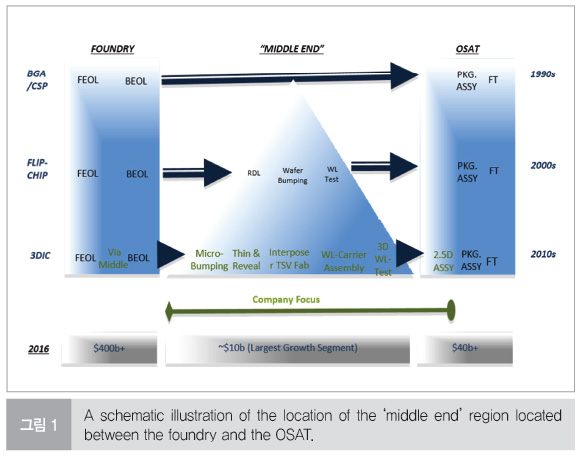

논의 또 다른 주요 주제는 누가 3D IC 어셈블리를 담당할 것인가이다. 과거 반도체 제조사는 다이를 설계 및 제조했고 그런 후에 어셈블리와 테스트를 위해 패키징 업체에 전달했다. 플립칩 테크놀로지의 발전에 따라, RDL, 웨이퍼 범핑 및 테스트가 가능한 소위 ‘middle end’라고 불리는 새로운 섹터가 발달해 왔다. Middle 영역에서는 게다가 마이크로-범핑, 웨이퍼 thinning 및 후면 노출, 인터포저 제작, 웨이퍼 레벨 어셈블리 그리고 3D 웨이퍼 레벨 테스트를 포함하여 성장해 오고 있다. 그림 1에서는 시간의 경과에 따라 middle 영역이 어떻게 성장했는지를 보여주고 있다. 이 영역은 가장 거대한 규모를 형성하고 있다. 3D IC 테크놀로지의 발전에 따라, Foundry를 위한 패키징 솔루션이 OSAT에서 진행했던 공정과 다르게 될 가능성이 있다는 점을 인지하였다. 본고에서는 4개의 다른 어셈블리 플로우를 언급할 것이고, 이들이 Foundry 중심의 프로세스 플로우 혹은 OSAT 중심 프로세스 플로우 둘 중 하나와 어떻게 부합하는지를 논의할 것이다.

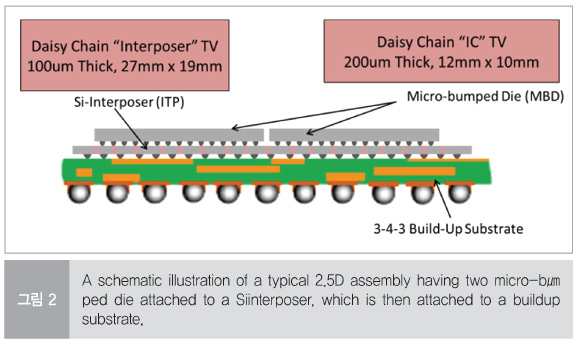

본고에서는, 그림 2와 같이 2.5D 테스트 시료의 표준 유형에 대한 다른 어셈블리 플로우를 거친 실험을 통해서 설명할 것이다.

가전업종으로 확대 꾀하는 이형삽입실장기

그림 2의 경우, 2개의 마이크로 범프된 다이(MBD)가 Si 인터포저(ITP)에 어테치되었다. 그런 다음 빌드업 된 서브스트레이트에 어테치되었다.

패키지 솔루션이 발달함에 있어서도, 확실한 하나는 해당 패키지가 온도 사이클링, 고온 저장, 온/습도 테스트, 균일한 HAST(high accelerated stress test) 그리고 PCT(pressure cooker test)가 진행되는 Board Level Reliability 테스트와 JEDEC standard module를 통과할 수 있도록 제작되어야만 한다. 신뢰할만한 패키지 발전 경험을 통해서, 응력과 전체 어셈블리 프로세스의 영향을 이해하는 것이 어셈블리된 패키지의 최종 warpage에 극적인 효과를 미치고 있음을 알고 있었다. 많은 보고서에서는 유기 플립칩 패키지와 서브스트레이트의 신뢰성에 대한 warpage의 영향을 연구해 왔다. 그리고 이 연구는 현 3D IC 패키징 설계에 적용될 수 있다. Warpage는 패키지의 최종 신뢰성에 영향을 미칠 것이다. ITP 및 서브스트레이트 warpage 최소화를 위해서 패키지 & 어셈블리 프로세스를 적절하게 구상해야 하는 매우 중요한 이유이다.

테스트 시료 설계

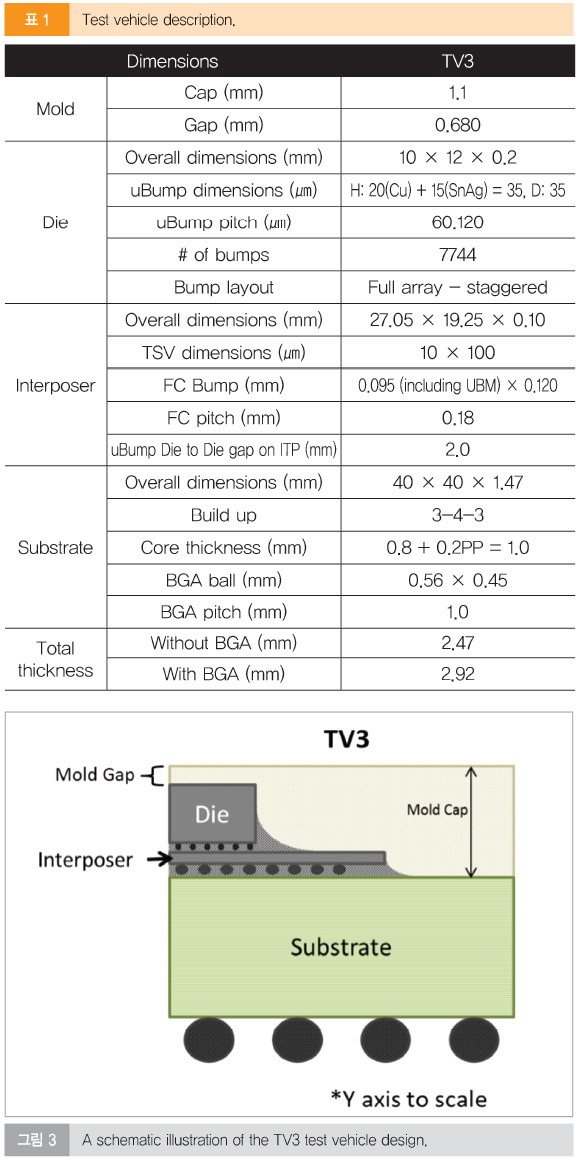

그림 3은 분석에 사용된 오버몰드된 TV3 테스트 시료의 모식도이다. ITP 및 서브스트레이트와 관련한 다이 두께의 자세하게 보여주고 있다. 이 테스트 시료의 세부사항은 표 1에서 나타내고 있다. 서브스트레이트의 경우, 19.25mm × 27.05mm 치수와 0.100mm 두께로 된 ITP가 1.47mm의 총 두께인 3-4-3 빌드업 서브스트레이트에 어테치되었다. ITP의 표면에는 10mm × 12mm의 치수인 2개의 MBD이다. 두께를 X로 표시하였고, 몰드 갭 두께는 Y로 하였다. 양쪽 MBD는 2mm 간격으로 떨어뜨려 놓았다. 솔더 캡핑된 필러(solder capped pillar)는 35㎛ 스탠드오프의 ITP와 내부 어레이 120㎛ 피치로 된 60㎛ perimeter 피치에 MBD를 어테치하기 위해 사용되었다. MBD와 ITP 양쪽 모두 상업용으로 가용한 capillary 언더필용 재료들을 이용하였다. 그 이후의 언더필 경화에서, 전체 스트립은 적절한 HVM 금형 재료들을 사용한 트랜스퍼 금형 프로세스(transfer mold process)를 통해 금형되었다.

Si-인터포저(ITP)와 마이크로 범프 다이(MBD) 제작

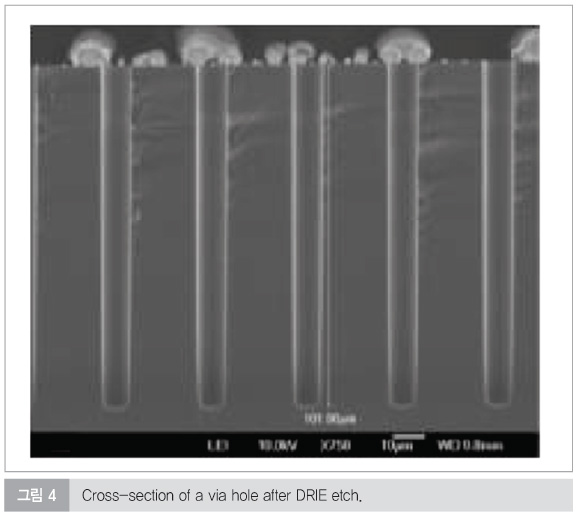

ITP는 Via First 프로세스를 이용한 300mm 웨이퍼로 만들어진다. TSV는 10㎛ 직경을 가지고 있으며, 100㎛ deep이다. 스탠더드 DRIE 건식에칭 프로세스가 웨이퍼 내 비아홀 형성에 이용되었다. 그림 4에서는 drilled via 홀의 SEM 이미지를 보여주고 있다.

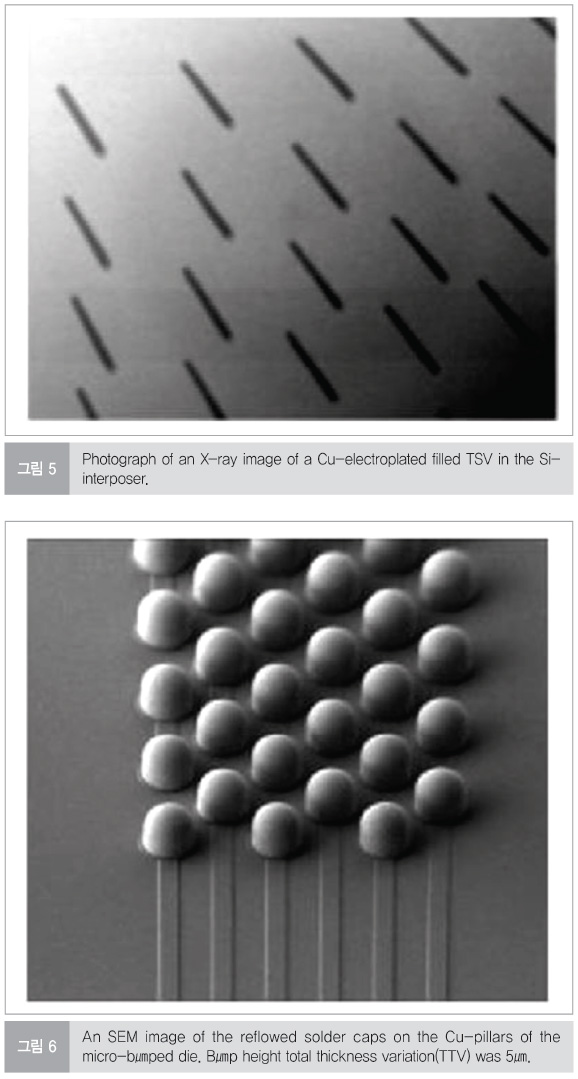

스탠더드 PECVD TEOS 프로세스는 SiO2 분리막을 deposit하는데 사용되었다. Ti-Cu 배리어/시드 층이 증착되었고, 비아는 Cu 전해도금 프로세스를 이용해 충진되었다. 그림 5에서는 도금 이후 Cu 충진된 TSV의 X-Ray 이미지를 보여주고 있다. 완벽한 홀 충진을 보였으며, 어떠한 보이드도 나타나지 않음을 볼 수 있다. 스탠더드 oxide BEOL 프로세스가 상부 표면 금속층 생성을 위해 사용되었다. 이 디자인에서, 단지 하나의 금속 레이어만 사용되었다. 그 후 숨겨진 두꺼운 웨이퍼가 임시 캐리어 웨이퍼(temporary carrier wafer)에 어테치되었는데, 이는 웨이퍼의 후면에 TSV을 얇게 하고 노출하기 위해서이다. 그런 후 RDL과 후면 솔더 범핑이 실시되었다. 다음으로, 캐리어 웨이퍼가 제거되었고, 이후 어셈블리에서 사용될 수도 있는 단일 ITP 생성을 위해 웨이퍼가 다이싱되었다.

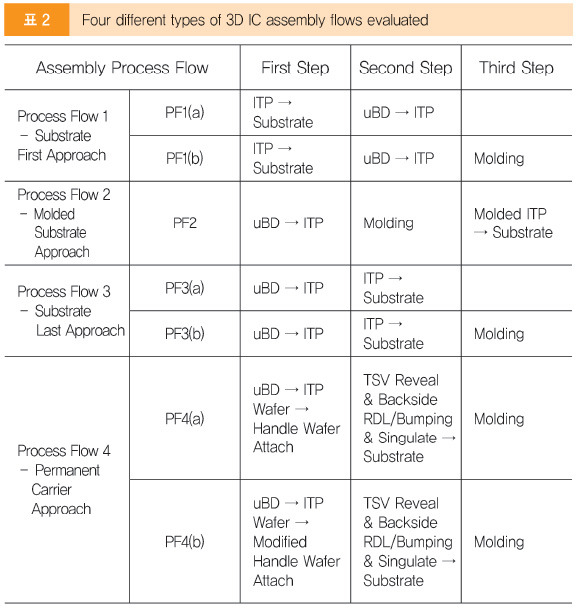

MBD는 300mm 웨이퍼로 만들어졌다. 신뢰성 테스트용 적합한 데이지체인 구조를 제작하기 위해서 최초 스탠더드 금속화는 웨이퍼 상에서 생성되었다. 그 후에 표면 산화가 전체 웨이퍼에 걸쳐 deposit되었고 Cu 필러가 도금될 부분에서 제거되었다. 그런 후 35㎛ 직경의 Cu 필러가 서로 각각의 면에 도금되었고, Pb-Free 솔더 도금이 진행된 후 리플로우되었다. 그림 6에서는 MBD 상에 솔더 캡핑된 Cu 필러의 SEM 이미지를 보여주고 있다. 홀의 SEM 이미지를 보여주고 있다.

어셈블리 프로세스 플로우

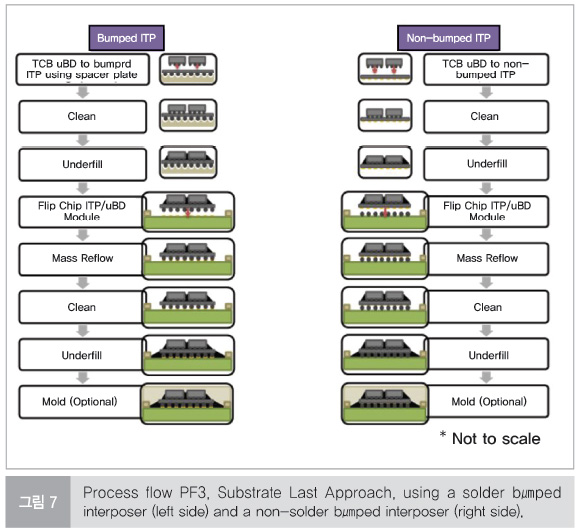

4개의 서로 다른 타입의 어셈블리 플로우를 평가하였다. 각 플로우는 표 2에서 보는 바와 같은 3단계로 구분할 수 있다. 각 프로세스의 자세한 사항들은 다음과 같이 하였다.

▶ Process Flow 1(PF1) - Substrate First Approach : 플 로우 PF1(a) 프로세스에서, ITP가 서브스트레이트에 먼저 어 테치된 후 MBD가 단일 ITP의 상면에 어테치된다. PF1(b)에 서, 어셈블리에서는 최종 2.5D 구조의 전체 신뢰성을 향상시 킬 패키지 warpage를 더욱 개선시키기 위해 오버몰드한다.

▶ Process Flow 2 (PF2) – 2번째 프로세스 플로우는 진공척(vacu㎛ chuck)이 2×4 ITP 블록을 잡고, MBD가 ITP 블록에 최초로 어테치되는 지 점인 프로세스 플로우 PF1의 변곡점이다. 그런 후 상면이 오 버몰드되고, 후면은 솔더 범프된다. 그 다음에 이 몰드 어셈 블리는 기존 대량 리플로우 솔더 어테치 방법을 활용하여 서 브스트레이트에 어테치된다.

▶ Process Flow 3 (PF3) – PF3(a)에서는, 후면 솔더 범프가 있든 없든 단일 ITP는 진 공 구조물의 해당 위치에 놓인다. 두 번째 MBD가 ITP에 어 테치되고 어셈블리된 ITP는 서브스트레이트에 어테치된다. PF3(b) 어셈블리 플로우 경우, MBD/ITP/서브스트레이트 어 셈블리는 전체 warpage 감소를 위해 몰드되었다.

▶ Process Flow 4 (PF4) – PF4(a) 플로우에서는, MBD가 두꺼운 ITP 웨이퍼에 어테치 된다. 취급된 웨이퍼는 상부 다이에 어테치되고 그 후 웨이퍼 가 얇아지고, TSV가 노출된다. 웨이퍼는 단일화되고 그 후 MBD/ITP 어셈블리는 서브스트레이트에 어테치된다. 플 로우 PF4(b) 프로세스에서는 수정된 handle 웨이퍼 디자인 이 최종 패키지 warpage 감소를 위해 사용되었다.

본고에서는 Process Flow 3 - Substrate Last Approach Process(PF3)와 관련된 프로세스 어셈블리 향상에 초점을 두고 있다. 이 작업에서 프로세스 조건의 효과의 경우, 신뢰성 있는 요구를 충족하는 패키지 설계를 위해서 재료 선택과 패키지 치수를 논의할 것이다.

그림 7에서 이 프로세스 플로우의 자세한 사항을 보여주고 있다. 이 프로세스에는 2개의 서로 다른 어셈블리 플로우가 존재한다. 첫 번째의 경우, PF3(a) 솔더 범프된 ITP는 fixture에 의해 제 위치에 놓인다. 여기서 정밀 fixture는 MBD 어테치 동안 진공을 이용하여 솔더 범프된 ITP를 제 위치에 잡아둔다. 두 번째 플로우에서, PF3(b), 범프되지 않은 ITP는 진공을 사용하여 확실하게 제 위치에 놓는다. 두 번째 MBD는 그런 후에 ITP에 어테치되었다. 이 플로우에서 솔더 볼은 서브스트레이트 위에 놓이고, 서브스트레이트는 리플로우를 이용해 ITP에 어테치된다.

본고에서는 범프되지 않은 인터포저를 이용한 PF3 어셈블리 방법 중 MBD에 대한 ITP 어테치 단계에 초점을 두고 있다(그림 7의 프로세스 플로우의 우측 면).

어셈블리 프로세스 발전

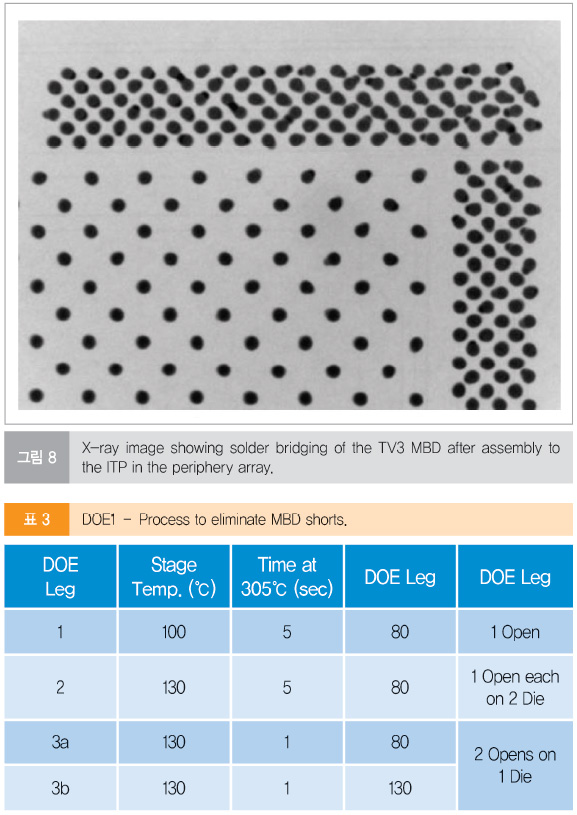

본고에서는 DOE(design of experiment)가 Si ITP에 대한 높은 수율의 MBD 어테치 달성을 위해 사용되었다. 초기 하드웨어 설정이 이뤄졌을 때, 초기 실패 모드가 ITP에 MBD의 솔더링 브릿지가 결정된다. 그림 8에서는 ITP 어셈블리 이후 TV3 MBD의 60㎛ 피치 주변 어레이 내의 이러한 브릿지 X-Ray 이미지를 보여주고 있다. 최종적으로 수용할만한 프로세스 윈도우를 이루기 위해 3개의 다른 DOE가 수행되었다. 작성된 데이터에 따라, 이들 각각의 실험상 DOE을 좀 더 자세하게 설명할 것이다.

DOE1: PROCESS TO ELIMINATE SHORTS

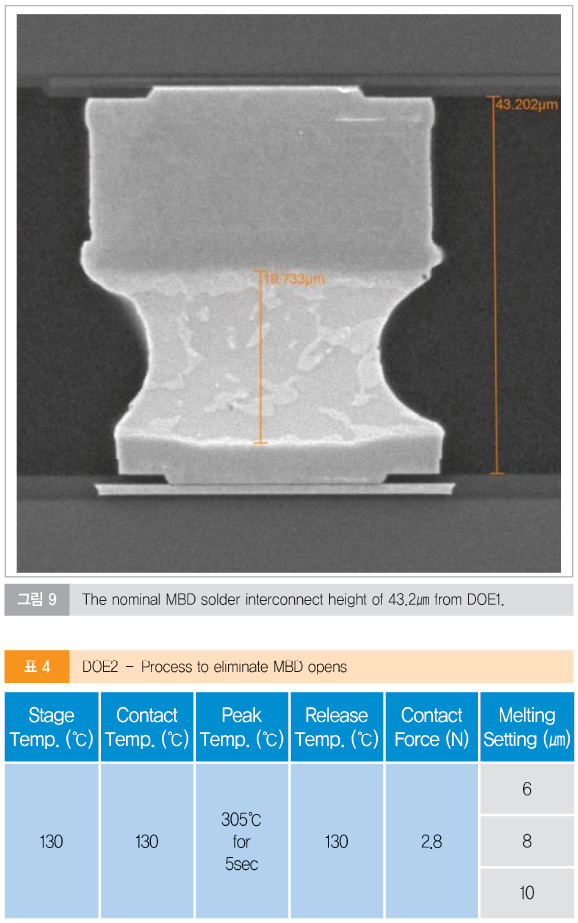

첫 번째 DOE에서 평가를 위한 3가지 변수는 스테이지 온도, thermode의 피크 온도에서의 시간 그리고 냉각 온도이다. Thermode 헤드의 피크 온도는 305℃이다. 이 실험을 통해서, 공칭 MBD 인터커넥트 높이는 43.2㎛이었다. 이루고자 원하는 목표 높이는 유한요소해석(finite element analysis)에 기반을 둔 35㎛이다. 그림 9에서는 이 build에서의 솔더 인터커넥트 결과의 SEM을 보여주고 있다. 이 DOE의 결과는 솔더 오픈의 실패모드로 변경되어 왔다. 모든 4개의 DOE의 경우, 표 3에서 보여주는 바와 같은 솔더 오픈이 존재하였다.

DOE2: PROCESS TO ELIMINATE SOLDER OPENS

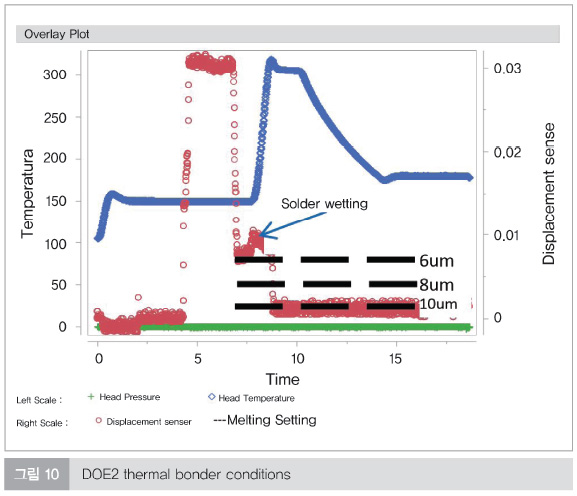

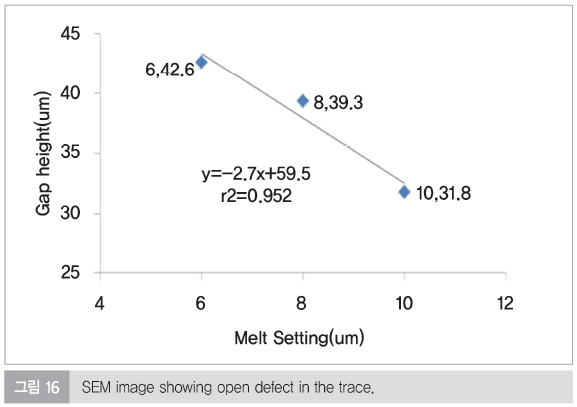

솔더 오픈을 없애기 위한 프로세스 조건들은 표 4에서 나타내고 있다. 본딩 동안 한 가지는 솔더의 융점 때문에 솔더 캠핑된 Cu 필러의 무너짐을 확인해야만 한다. 전체 무너짐을 예방하기 위해, 헤드의 Z-변위 양을 제어할 수 있도록 장비의 Z-변위 조정 기능이 있다. 솔더 리플로우 이후 제어된 Z-변위의 양은 소위 ‘용융 조정(Melt Setting)’이라고 불린다. 주요 변수는 6-10㎛의 용융 조정 높이 범주 내로 제어하는 것이다. 이 작업의 전기적 테스트를 통해 10㎛의 용융 조정 높이를 이용하였을 때 어떠한 솔더 오픈과 쇼트가 없음을 확인하였다. 전기적 테스트와 X-Ray는 또한 쇼트 실패 부문이 없는지를 확인하기 위해서 사용되었다. 이 구조에 사용된 thermal bonder 컨디션은 그림 10에서 보여주고 있다. 6㎛, 8㎛ 그리고 10㎛ 용융 조정 조건의 지점을 나타내고 있다.

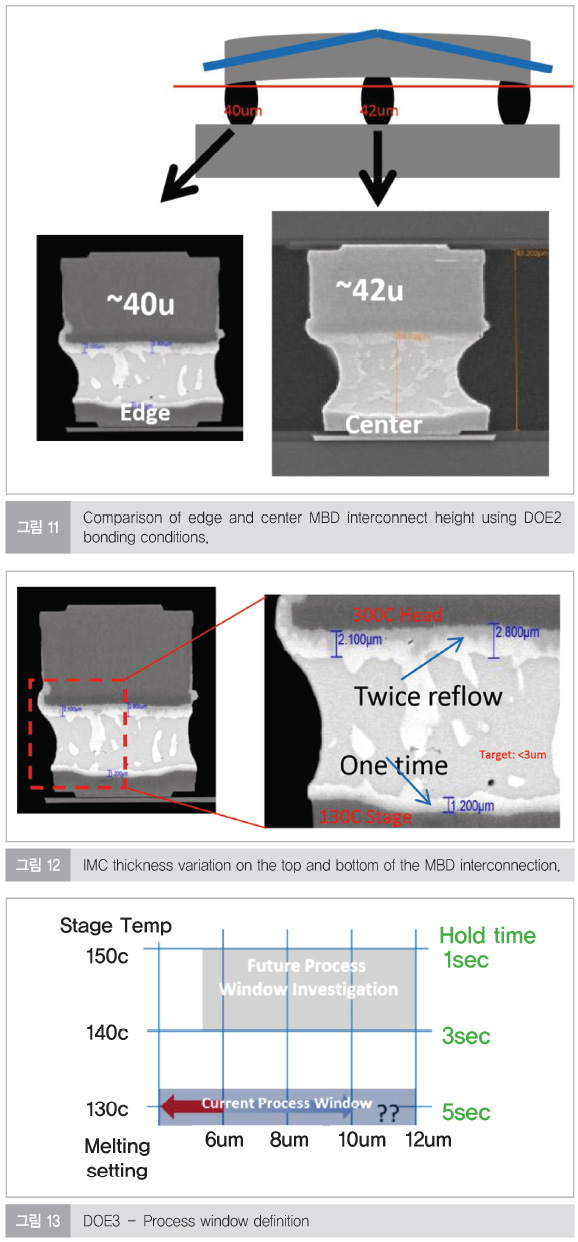

이 빌드에서 MBD 솔더 상호접촉의 횡단면 절단이 이뤄졌는데, 다이의 경미한 휘어짐이 발견되었다. 휘어짐은 MBD 전체를 관통하는 온도 경도 때문이고, 불균등한 갭 높이를 유발한다는 점을 알 수 있었다.

그림 11에서는 40미크론의 높이를 가진 엣지 MBD 솔더 접합과 42미크론의 높이를 지닌 중앙 다이 솔더 접합을 보여주고 있다. 또한 MBD 상호접촉부에서 IMC(intermetallic compound) 두께가 달라지는 것을 발견했다. 그림 12에서는 Cu 필러 인터페이스에서의 2.1~2.8㎛ IMC 두께 범위를 보여주는 반면, ITP 패드 인터페이스에서는 1.2㎛ IMC 두께만 보여주고 있다. 이는 솔더가 2번의 리플로우를 통해 Cu 필러 saw를 덮은 반면, ITP 패드 saw는 단지 한 번의 솔더 리플로우된 사실을 통해 설명될 수 있다. 어셈블리 이전 다이 사이드 상의 IMC 양은 약 1㎛이다.

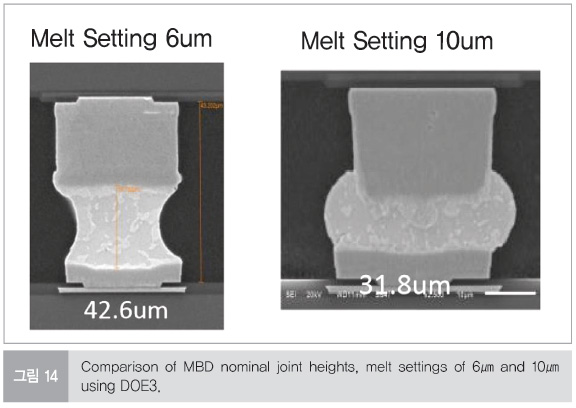

앞서 언급한 바와 같이, 최종 목표는 약 35㎛의 MBD 상호접촉 공칭 높이를 지닌 프로세스와 어떠한 솔더 브릿지 혹은 오픈을 지니지 않은 프로세스를 향상시키는 것이다. 최종 DOE3 단계에서, 최종 프로세스 윈도우에 도달하기 위한 스테이지 온도, 유지 시간 및 용융 조정이 평가되었다. 그림 13에서는 DOE3의 자세한 사항을 보여주고 있다. 이 빌드에서는 6㎛ 및 8㎛의 용융 설정 모두에서 솔더 오픈이 나타났다.

12㎛의 용융 조정에서 솔더 브릿지 현상을 보였다. 10㎛의 용융 조정에서만 어떠한 오픈 혹은 브릿지가 없는 약 32㎛의 공칭 접합 높이를 나타냈다. 그림 14에서는 6㎛과 10㎛의 용융 조정을 적용했을 때, 공칭 MBD 상호접촉의 비교되는 모습을 보여주고 있다. 6㎛ 용융 조정의 경우, 42.6㎛의 공칭 접합 높이를 이뤘고, 10㎛에서는 31.8㎛이었다.

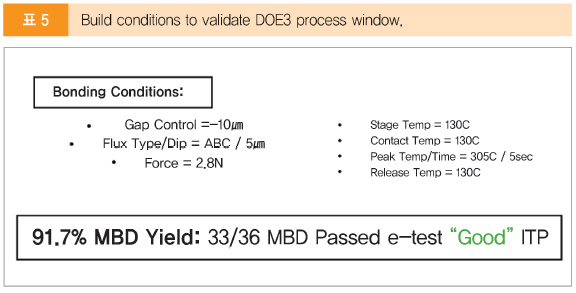

최상의 프로세스 윈도우 조건을 확인하기 위해 표 5에 제시된 프로세스 조건을 사용하여 36개의 인터포저 세트를 어셈블리하였다. 이 빌드에서, 36개 중 33개의 부문에서는 어떠한 솔더 결함도 없이 전기 테스트를 통과했다.

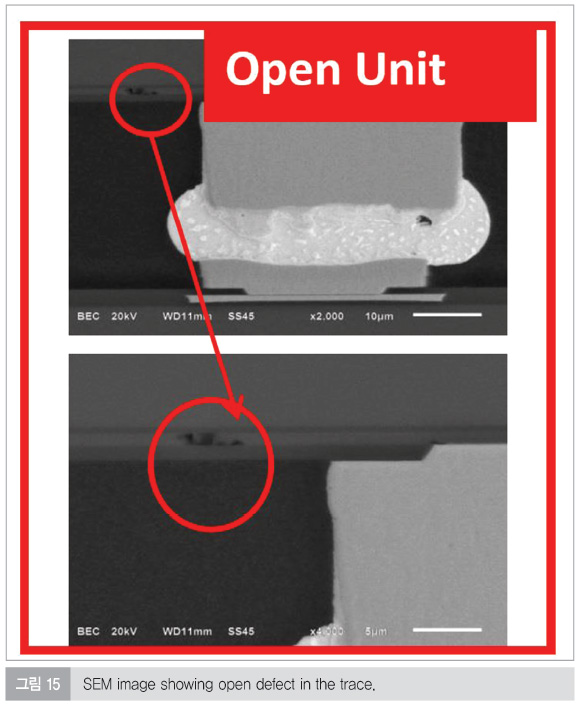

그러나 전기적인 테스트 오픈 실패 모드를 보여주는 3개 부문의 신중한 실패 분석을 통해서, 3개 모두가 봉합된 MBD 하드웨어 위의 트레이스 내의 오픈 때문이라는 것을 알아낼 수 있었다. 그림 15에서는 MBD 면 위의 트레이스 내 오픈과 관련한 SEM 이미지를 보여주고 있다. 이 오픈 결함을 우수한 인터커넥트를 보였을 때와 비교했을 때, 우수한 상호접촉은 경화와 관련한 어떠한 불량도 없었음을 발견했다. 따라서 이들 3개 어셈블리가 불량이 된 이유를 대략적으로 설명할 수 있게 되었다. 현재 빌드들은 이 프로세스를 재확인하는 과정을 거치고 있다.

실험 최종결과

해당 어셈블리 프로세스 향상의 주요 초점은 OSAT 어셈블리 설비와 호환 가능한 어셈블리 프로세스 윈도우를 수립하는 것이다. MBD 상에 솔더 캐핑된 Cu-필러의 Si-to-Si 본딩 접근법은 열압착본딩을 이용하여 non-b㎛ped Si-ITP를 행한다. 도전과제는 어떠한 솔더 브릿지 혹은 오픈 없이 높은 수율을 이룰 수 있는 적합한 프로세스 조건들을 생성하는 것이다.

실험 플로우를 통해서 볼 수 있듯이, 최초 솔더 브릿징 현상을 경험했다. DOE1의 조건들을 활용하여 솔더 브릿지 현상을 없앴을 때, 다음 목표는 DOE2의 주제였던 솔더 오픈을 제거하는 것이다. 그러나 DOE2에서 솔더 오픈이 없어진 곳의 공칭 솔더 상호접촉 높이는 35㎛ 수준의 공칭 목표치보다 높은 대략 43㎛이었다.

DOE2 실험에서, 용융 설정이 다양하게 하였고, 어떠한 솔더 오픈이 생성되지 않은 10㎛의 수치가 결정되었다. 이는 90% 어셈블리 수율을 달성하는 70개 다이 본딩에 기반을 두고 있다. 마이크로 범프된 다이(그림 15 참조) 상에 트레이스가 크랙되었기 때문에 10% 불량이 존재하였다. 또한 이 작업을 통해 용융 설정 대비 높이의 차이를 도표로 그릴 수 있었고, 35㎛의 공칭 상호접촉 높이를 달성하기 위한 이상적인 조건사항을 결정할 수 있었다. 그림 16에서는 이 실제 빌드로부터 용융 설정 대비 높이 차이의 직선형 하향 도표를 보여주고 있다. 마이크로 범프된 다이의 중앙이라는 동일한 위치에서 만들어진 단일 측정 포인트이다.

DOE3의 목표는 이상적인 프로세스 윈도우를 결정하는 것이었다. 여기에서 목표는 불량 없이 약 35㎛의 공칭 상호접속 높이를 달성하는 것이다. 표 5를 통해서 볼 수 있듯이, MBD 경화로 인한 불량 때문에 오픈 현상이 나타난 것은 36개 중 3개의 어셈블리이었다. 본고를 참조한다면, Si-ITP 어셈블리 수율과 관련해 높은 MBD 수율을 생성할 수 있는 프로세스 윈도우를 달성하는 것을 매우 확신한다.

결론

1. 반도체 FAB은 TSV 기술을 통해 견고하고 신뢰할만한 디 바이스를 제작할 수 있다.

2. 프로세스의 PF3 타입은 OSAT 설비와 호환 가능하며, JEDEC 신뢰성 사양의 도전과제를 충족시킬 수 있는 3D IC 패키지를 생성할 수 있다.

3. 이 연구는 Si-ITP 프로세스에 있어서 MBD의 높은 수율 을 달성할 수 있음을 보여주고 있다.

4. 제조 기반 시설은 기존 OSAT 제조 인프라를 활용하여 이 들 패키지 타입의 대량 생산 어셈블리를 위해 존재한다.