Dual Face-Down 구조 방식 제안

퍼포먼스적, 경제적 매우 유리

DRAM 디바이스의 효과적인 3D 적층은 많은 이점을 제공한다; 증가된 퍼포먼스, 늘어난 부품 밀집도 및 더 커진 면적 활용. 그러나 패키지 어셈블리 선정 방법론에서는 프로세스 복잡성, 각 프로세스 관련 비용, 전체 패키지 어셈블리 수율 및 최종 제품의 신뢰성이 고려되어야만 한다. 본고에서는 앞서 언급된 패키지 어셈블리 변화의 긍정적인 부문과 부정적인 부분을 퍼포먼스 속성과 물리적 한계 양쪽을 비교면서 설명할 것이다. 아울러, 매우 혁신적이고 매우 얇은 3D 패키지 디자인 그리고 특히, center-bond 패드 DRAM 다이에서 어셈블리 프로세스 향상을 꾀할 수 있는 기술을 소개할 것이다. 새로운 방법은 특별한 다이 레벨의 프로세스 단계를 요구하지 않고 기존 패키지 어셈블리 구조를 활용하기 때문에 경제적인 측면에서 유리하다.

성능 중심의 전자기기 혁명은 IC 패키징 업계에 꾸준한 도전과제를 부과하고 있다. 차세대 프로세서들이 자체적으로 잠재적인 성능에 도달하도록 많은 제조업체들은 더 큰 메모리 대역폭이 가능한 인터페이스 포맷을 향상시키고 있다. 빨라진 시그널 속도를 지원할 수 있는 메모리 기능들을 보장하기 위해, 패키지 개발자들은 혁신적인 3D 패키지 어셈블리 기술과 공정 미세화에 더욱더 의존하고 있다.

일부 애플리케이션 업체들은 와이어 본드 프로세스를 활용하여 인포터저 서브스트레이트에 다이 소자를 직접적으로 적층하는 방법을 제한적으로 성공했다. 주변에 위치한 본드 패드에 2개 이상의 메모리 다이를 적층하는 것은 상당히 성공적으로 이뤄져왔다. 그러나 다이 소자가 전형적으로 동일한 물리적인 아웃라인을 가지고 있기 때문에 와이어-본드 loop height를 명확하게 하기 위한 레이어 간 공간이 필요하다. 게다가 전체 마감처리된 패키지 높이는 여러 애플리케이션에서 중요 요소가 될 수 있다. 다이 소자가 매우 얇게 제작됨에 따라, 적층 내부의 누적된 소자들은 초과될 수 있다. 고성능 DRAM 다이는 적층시키기가 특히 어렵다. 이는 와이어-본드 사이트에 위치된 center 때문이다. 이 요인은 다이 적층 프로세스를 복잡하게 하고, 지나치게 긴 와이어-본드 인터페이스로 인해 기능성 시그널 속도를 현저하게 강조시킬 수 있다.

DRAM 디바이스의 효과적인 3D 적층은 많은 이점을 제공한다; 증가된 퍼포먼스, 늘어난 부품 밀집도 및 더 커진 면적 활용. 그러나 패키지 어셈블리 선정 방법론에서는 프로세스 복잡성, 각 프로세스 관련 비용, 전체 패키지 어셈블리 수율 및 최종 제품의 신뢰성이 고려되어야만 한다. 본고에서는 앞서 언급된 패키지 어셈블리 변화의 긍정적인 부문과 부정적인 부분을 퍼포먼스 속성과 물리적 한계 양쪽을 비교면서 설명할 것이다. 아울러, 매우 혁신적이고 매우 얇은 3D 패키지 디자인 그리고 특히, center-bond 패드 DRAM 다이에서 어셈블리 프로세스 향상을 꾀할 수 있는 기술을 소개할 것이다. 새로운 방법은 특별한 다이 레벨의 프로세스 단계를 요구하지 않고 기존 패키지 어셈블리 구조를 활용하기 때문에 경제적인 측면에서 유리하다.

배경

반도체 메모리는 컴퓨터와 게임 콘솔에서부터 멀티미디어와 통신제품에 이르기까지 무수히 많은 전자기기의 향상에 필수적인 역할을 담당한다. 보드 서플라이어 베이스를 제공하고 높은 수준의 퍼포먼스를 유지하기 위해서, 메모리 제품군은 엄격하게 표준화되어 부착되어야만 한다. 이들 표준화는 반도체 제조업체들의 긴밀한 협력체인 JEDEC Solid State Technology Association을 통해서 발전되어 왔다. JEDEC JC-42 위원회에서는 성장하고 있는 DDR(double data rate) 메모리 계열 표준화를 포함하여 RAM(random access computer memory)용 디바이스 인터페이스를 위한 광범위하게 사용되는 표준화 작업을 제기해 왔다. 특히 JEDEC DDR3 SDRAM 표준은 이전 세대 메모리 디바이스(DDR1, DDR2)에 비해 향상된 퍼포먼스, 저전력 및 더 많아진 기능성을 제공하여 산업계에서 광범위하게 채택되어지고 있다. 전임 DDR2 SDRAM 보다 우위에 있는 DDR3 SDRAM 기술의 주요 이점은 더 넓어진 대역폭을 활용하여 두 배의 전송 데이터 효율능력을 가지고 있다는 것이다. 예를 들면, 4배의 클록 사이클 당 전송이 2배인 64-비트 와이드 DDR3 모듈은 64배의 메모리 클록 속도까지 전송효율을 이룰 수 있다. 100MHz의 메모리 클록 주파수를 지닌 DDR3 SDRAM은 최대 6400MB/s의 전송효율을 제공하고 JEDEC DDR3 표준은 8기가비트까지의 칩 용량을 정의해 놓고 있다. DDR3 메모리는 전력소모가 또한 30% 정도 감소한다. DDR3는 단지 1.5V의 공전전압만으로도 작동한다. 반면 이전 DDR 디바이스 계열은 1.8V에서 2.5V가 필요하다. JEDEC에 따르면, 특히, 서버 혹은 다른 업무용 중요 디바이스의 메모리 안정성을 고려할 때, 동작에 필요한 절대 최대값은 1.575 V가 고려되어야만 한다.

메모리 기술의 향상

DDR3 계승자인 DDR4는 심지어 낮은 동작 전압에서도 높은 대역폭을 제공해 준다. 그러나 DDR3는 2011년에 8억8백만개의 DDR 모듈 유닛의 89%를 차지할 것으로 예상된다. 이는 전년도 대비 67% 성장한 것이다(출처: IHS iSuppli Research). DDR3 모듈 생산은 2012년을 거쳐 90%까지 지속적인 상승이 예측된다. 그러다가 DDR4 메모리가 최종적으로 대량생산라인에 접어드는 2014년에 사이클 하락이 점쳐진다. 분석가에 따르면, 기본적으로 DDR4 생산이 2012년부터 시작될 것으로 예상되었으나, DDR4의 대량 생산은 포인트-투-포인트 토폴로지, 제조 복잡성, 높은 클록-속도(~4266MHz) 및 여러 다른 이유들로 인해 지연되었다. 그러나 4세대 double-data-rate DRAM의 생산곡선은 빠르게 올라갈 것이다. 현재 전문가들은 DDR4가 즉시 12%를 차지할 것으로 전망하고 있으며, 2015년에 DDR4 모듈의 시장점유율은 56%에 이르고, DDR3는 42%를 점유할 것으로 예상된다(총 DRAM 모듈 선적은 110억 유닛이 예상).

DDR4 JEDEC 스펙이 2011년에 확정되지 않았음에도 불구하고, 많은 제조업체들은 테스트 목적으로 데모용 메모리를 공급하기 시작했다. 예를 들면, 삼성전자는 2010년에 30nm급 공정 기술을 활용한 1.2V 2GB DDR4 NDIMM(non-buffered dual in-line memory)을 발표했었다. 이 DDR4 DRAM 모듈은 1.2V에서 2.133Gbps의 전송효율을 달성한다. 노트북 애플리케이션의 경우, DDR4 모듈은 40%의 전력소모 감소가 기대된다(1.5V DDR3 모듈 대비).

고밀도 메모리의 요구

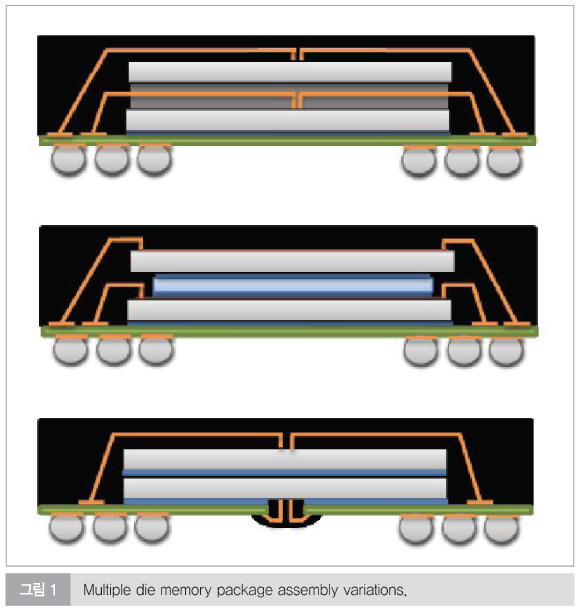

적층 DRAM DDP(dual-die-package)에 대한 산업계의 솔루션은 전통적인 face-up wire-bond 기술을 사용하는 것이다. 그림 1에서는 전통적인 2개의 다이 패키징 솔루션을 활용한 DDR 메모리의 모습을 보여주고 있다. 그러나 DDR 메모리 다이는 상기 다이의 중앙에 위치한 와이어-본드 사이트를 가지고 있다.

Face-up 구조에서 2개의 center-bond 다이를 수직 적층은 이미 실시되고 있으나, wire-bond된 첫 번째 층 사이트 위에 두 번째 층 다이를 실장하기 위한 균일한 표면상태를 유지하는 것이 매우 어렵고 와이어 길이가 거대해진다. wire-bond 길이를 최소화하기 위해서 많은 서플라이어들은, 다이 소자의 center-bond 사이트를 외측 엣지로 변경하기 위해 웨이퍼 표면의 구리 전도체가 제공되는 표면 RDL(redistribution layer) 프로세스를 채택하고 있다. 그림 1의 (b)에서 이를 잘 나타내고 있다. 그림 1의 (a)와 (c)의 구조들은 전형적인 face-up 및 face-down 구조의 다이 실장 모두가 적용되었다. 하부의 다이가 through-window-wire-bond 프로세스를 통해 처음으로 실장되었다. 그런 후에 두 번째 다이는 하부 다이의 뒷면 상에 face-up으로 실장되고 wire-bond된다.

메모리 소자의 수직 적층 혹은 pre-packaged 싱글 다이 메모리 디바이스 적층은 더 큰 메모리 밀집도를 형성하게 한다; 그러나 이들 구조에서는 최적화된 최종 패키지 아웃라인 밀집도, 퍼포먼스 증대 그리고 전력감소 목표를 달성할 수 없다. 이들 패키지 어셈블리 변화가 과거 애플리케이션에서 성공적인 수준으로 진화했음에도 불구하고, 시그널 집적도 유지와 관련한 문제들을 극복하고, 메모리 밀집도 증대에 따라 일반적으로 발생하는 퍼포먼스 감소를 극복하기 위해 새로운 혁신기술이 필요하다.

증대된 DDR 메모리 퍼포먼스

멀티-코어 프로세스가 장착된 서버군에서는 더 큰 메모리 대역폭 요청이 이어질 것이고, 생산제품의 소형화 수요 확대와 더불어 고성능 컴퓨팅 기기에서는 더 높은 밀도 그리고 더 빠른 속도의 메모리 디바이스 및 모듈 수요가 지속될 것이다. 게다가 차세대 스마트폰과 개인용 휴대 미디어 전자기기의 급격한 성장을 대비하기 위해 적은 공간에서도 더 큰 대역폭 메모리를 제공할 수 있는 더욱 혁신적인 솔루션들이 필요해 질 것이다.

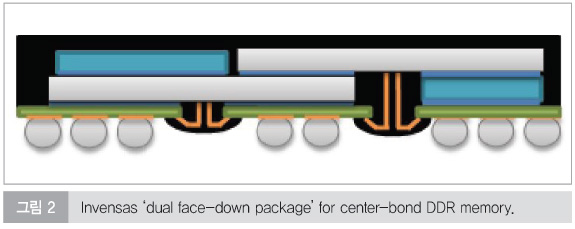

DDR 어셈블리의 핵심 이슈 중의 하나는 전체 트레이스 길이를 최소화하면서 시그널 function 밸런스를 유지하는 것이다. Invensas에 의해 개발된 혁신적인 DFD™(dual face-down) 패키지는 패키지 내부 다이 소자의 이러한 측면들을 양측을 향상시킨다. 그림 2에서 보여주고 있는 이 구조는 기존 DDR 어셈블리와 비교했을 때 향상된 열적 성능뿐만 아니라 전기 퍼포먼스와 수율 증대를 제공한다.

DFD 패키지는 유연한 엑세스를 가능하게 한다. 2개의 다이 소자로부터 분리된 DQ 시그널은 함께 묶어질 수 있거나 혹은 분리(깊이 혹은 폭 확장 가능)해서 사용될 수 있다. 다이 소자 양쪽에 through-window wire bond 프로세스를 사용하는 것은 웨이퍼 상 고가의 RDL 공정 요구를 없애기 위한 조치이다. 다이 본드 사이트와 인터포저 간의 짧은 인터페이스 결과는 더 나은 전기적 퍼포먼스를 위한 최소의 인터커넥트 경로 길이를 제공하고, 골드 와이어 사용을 상당하게 줄여준다.

DFD 패키지 서브스트레이트 디자인

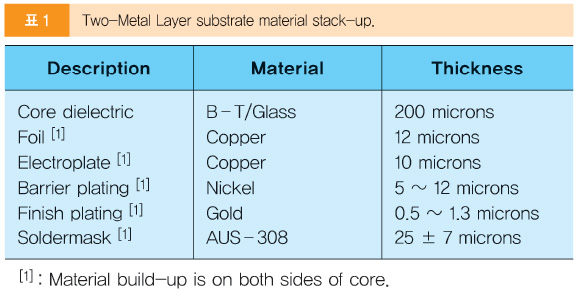

Dual die package 서브스트레이트에 선택한 기본적인 재질은 외부 표면 양쪽에 12마이크로 두께(1/2 oz)의 동박호일로 라미네이트된 200미크론 두께의 유리강화 BT(Bismaleimide-Triazine) 계열이다. 라미네이트는 어레이 배열 반도체 패키지 애플리케이션에서 선호되는 서브스트레이트 재질 중 하나이다. 재질 조성물의 물리적으로 안정적인 특성은 커다란 패널 사이즈 제조에 월등한 최상의 선택이라고 간주되고 있다.

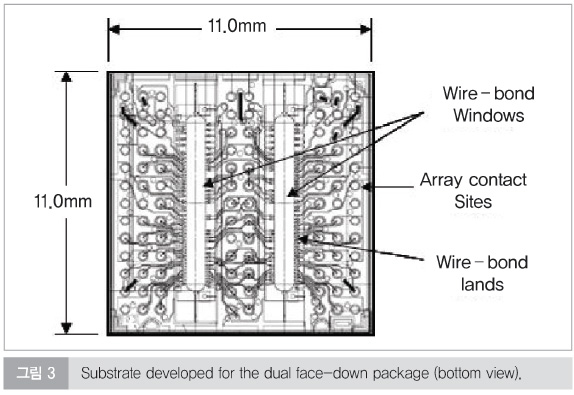

마감된 dual-face-down 패키지 서브스트레이트는 280±50 미크론 두께이고, 사이드 당 11.5mm로 측정되었다. 2개의 좁은 슬롯은 through-window wire-bond 프로세스에 맞도록 wire-bond 랜드 간의 특색을 제공한다.

wire-bond 랜드와 볼 어테치먼트 랜드를 연결하는 도전성 트레이스들은 35미크론의 균일한 너비를 가지고 있으며, 컨덕터들 사이의 간격은 동일했다. 솔더 볼 접촉물들을 부착하기 위해 배치된 랜드 특성들은 450미크론 직경 표면을 제공하는 솔더마스크로 정의된다.

DFD 어셈블리 프로세스

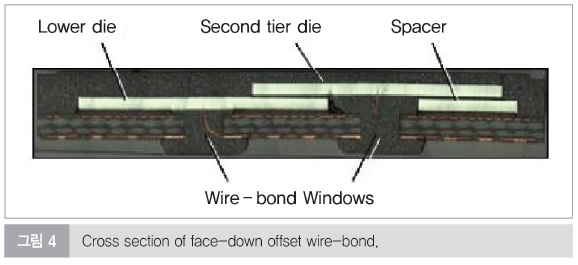

Invensas의 DRAM용 멀티-다이 패키지는 face-down 디바이스 배열만 활용함으로써 증대된 전기적 그리고 열적 퍼포먼스를 제공한다. 그림 4에서 보는 바와 같이 열 임피던스 감소를 위해 적층된 다이 오프셋을 통해 이 방식은 단말까지의 인터커넥트 경로 길이를 최소화한다.

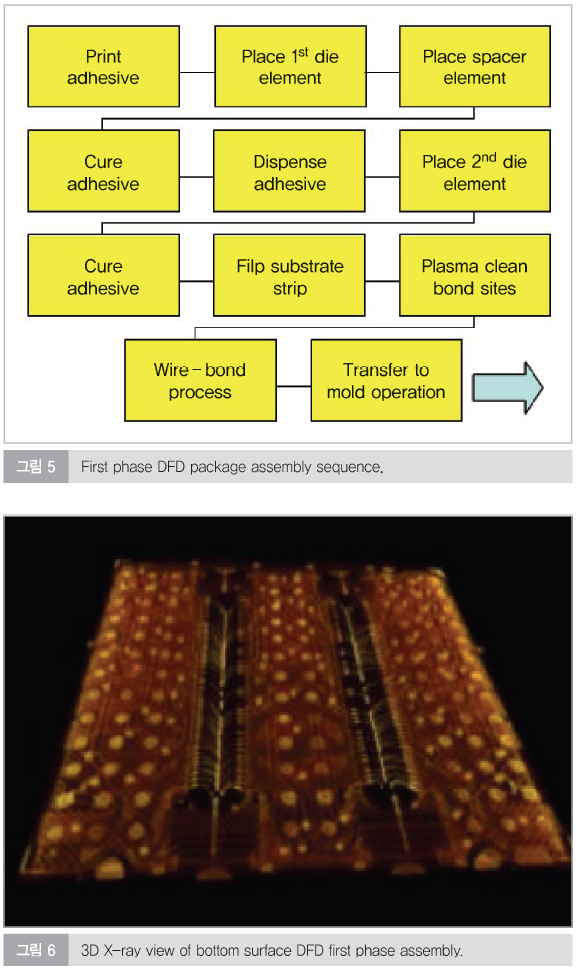

첫 번째 단계의 어셈블리 순서는 스텐실 프린팅 시스템을 통한 어레이된 서브스트레이트 스트립의 이송으로부터 시작한다. 스텐실 프린팅 시스템은 다이 어테치 점착성분이 서브스트레이트 표면 상 프린트되는 장소에 프린트한다. 정밀한 다이 어테치 시스템을 활용하여, 예열된 다이 소자들은 접착-라인이 그어진 서브스트레이트 상에 놓인다. 다이 소자와 동일한 두께의 spacer 소자도 2번째 층 다이 어테치먼트 서포트를 위해 서브스트레이트 상에 놓인다(내부 프로토타입 DFD 부품들은 2개의 Micron 1Gb DDR3 디바이스를 활용해 향상되었다). 모든 다이 소자와 spacer들이 경화될 때, 스트립은 하부 다이의 후면과 spacer에 접착제의 패턴을 침전시키기 위해 디스펜싱 시스템을 통해 이송된다. 2번째 층 다이 어테치와 경화 이후, 스트립 어셈블리는 wire-bond 프로세스를 대비해 다이 본드 패드 에어리어 노출을 위해 뒤집힌다.

주의사항 : ‘Through-window’ wire-bond의 준비로, 스트립은 공격적인 플라즈마 클리닝 프로세스를 거친다. 다이와 서브스트레이트 상의 wire-bond 사이트가 특정 함유물 부재(wire-bond 인터페이스를 절충할 수 있는)를 보장하기 위해서이다. 클리닝 프로세스 이후 스트립은 고속 wire-bond 시스템을 통해 즉시 이송된다.

wire-bond 프로세스는 싱글 다이 face-down 어셈블리에 적용되었던 것과 크게 다르지 않다. ‘Gold wire-bond’ 프로세스의 처음 단계는 소형 볼 특징을 형성하도록 와이어 끝 부분을 녹이기 위해서 개방형 수소화염이거나 혹은 전기 스파크 둘 중 하나를 채용한다. 그 이후에 골드 볼은 정밀한 힘, 시간 그리고 짧은 주기의 초음파 에너지를 이용하여 반도체 다이 본드 사이트에 눌러진다. wire-bond 프로세스의 첫 번째 단계가 완성된다. 그런 후에 골드 와이어는 상향 곡선이 되고, 서브스트레이트 외부 표면의 본드 사이트에 맞춰 고리모양이 된다.

wire-bond 인터페이스의 다음 단계는 ‘wedge-bond’ 프로세스를 이용하는 것이다. 이 프로세스는 Ni/Au 도금 서브스트레이트 랜드에 골드 와이어를 연결하기 위해 정밀한 힘과 초음파 에너지에 의존한다(그림 5 참조).

wire-bond 프로세스 균일성과 퀄리티(그림 6 참조)를 확인하기 위한 시각적인 검사 작업을 거친 뒤, 어셈블리된 스트립은 몰딩 작업을 위해 최종 어셈블리 작업자에 이송되었다.

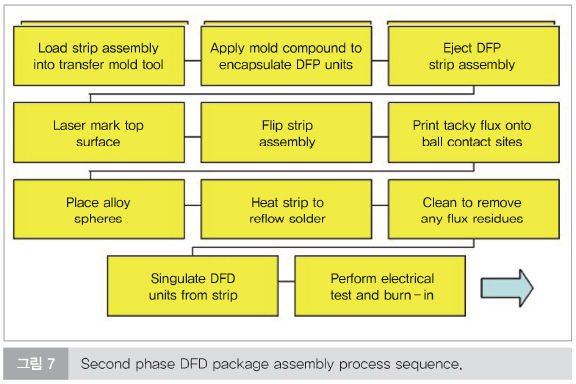

패키지 어셈블리의 최종 단계는 사출성형, 레이저마킹, 볼 어테치, singulation, 전기 테스트 및 burn-in을 포함하고 있다(그림 7 참조).

어셈블리 재료 설명

- 첫 번째 레이어 접착제 : 45미크론 두께의 Henkel ‘Ableflex’ (프린트 프로세스)

- 두 번째 다이 어테치 접착제 : 30미크론 두께의 Henkel ‘Ablebond’ (디스펜스 프로세스)

- wire-bond 인터페이스 : 20미크론 직경의 Au 와이어

- 다이 두께 : 150미크론

- 몰드 콤파운드 : Hitachi 케미컬 (사출성형 및 슬롯 충진)

FBGA 접합 부착

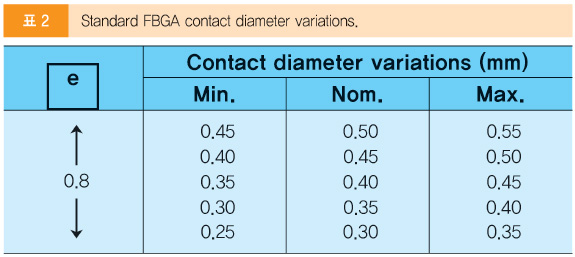

JEDEC 설계 표준에서는 합금 및 심지어 다양한 폴리머 기본 재질의 볼, 범프 혹은 다른 돌출형 단자(핀들 제외)에 대한 FBGA의 접촉 특성을 설명하고 있다. 거리 혹은 특정 두 개의 인접한 row의 센터라인(e) 간의 피치 혹은 볼의 column이 3개의 치수 중 하나가 될 수 있다고 말하고 있다; 0.5mm, 0.65mm 혹은 0.80mm로, 기존 JEDEC DRAM 표준을 준수하고 DIMM 서브스트레이트 상 효율적인 회로의 표면 라우팅에 대응하는 치수이다. Invensas 엔지니어들은 0.8 볼 피치 변화를 선택했다. 0.8mm 접촉 피치는 또한 표 2에서 보여주는 바와 같이 볼 직경 선택에 있어서 폭 넓은 선택을 가용하게 한다.

DFD 패키지 애플리케이션을 위해 선택된 접합물은 450미크론 직경 랜드에 부착되는 450미크론 직경의 SAC105 합금 솔더 볼이다. 솔더 볼 어테치먼트 프로세스는 순차적인 3개 스테이지 동작으로 이루어져 있다. 각 접촉 사이트 상 점착성 플럭스의 프린팅을 시작으로, 플럭스가 준비된 사이트 위에 프리폼된 450미트론 직경의 솔더 sphere을 놓고, 접합 프로세스를 완성하기 위해 mass 리플로우로 솔더링한다. 비록 이 프로세스를 위해 선택된 플럭스 재질이 ‘no-clean’으로 분류되었다고 하더라도, 철저한 반수성(semi-aqueous) 클리닝 프로세스가 솔더 리플로우 이후에 뒤따라야 한다. 특정 잔사 재질 혹은 인터포저의 바닥 표면에서 파티클을 제거하기 위해서 필요하다.

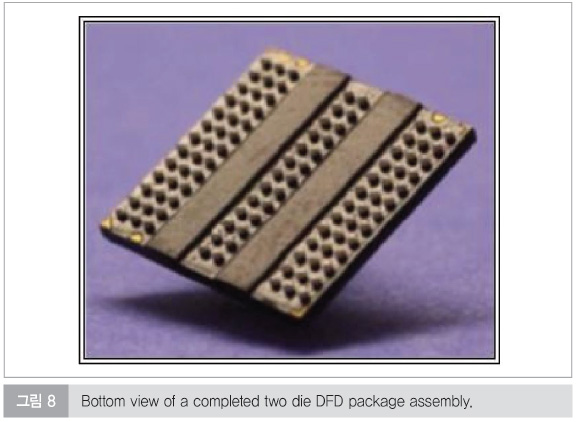

최종 작업은 스트립 배열로부터 개별 DFD 유닛을 분리하는 것이다. 비록 미래의 디자인이 die punch singulation(대량 생산구조에 일반적으로 선호되는)을 수용할 수도 있다고 하더라도, 매우 부드러운 wall 표면을 결과를 보이는 정밀한 saw singulation에 의존하여 이 프로그램이 개발되었다(그림 8 참조).

JEDEC 준수

비록 JEDEC 위원들이 DFD 애플리케이션을 대표하는 기계적인 아웃라인을 아직 개발하지 않았다고 하더라고, Invensas 엔지니어들은 JEDEC 디자인 표준인 FBGA 계열의 ‘JEDEC PUBLICATION 95 DESIGN GUIDE 4.5’의 기존 디자인 가이드라인에 충실하여 시도했다. 표준지침에서는 패키지의 캐리어 바디가 유전체 구조에 적용하는 금속 회로 패턴을 가지고 있다고 간단하게 서술했다. 하나 혹은 그 이상의 반도체 디바이스들은 이 유전체 캐리어의 상부 혹은 하부면 둘 중 하나에 접촉될 수 있다. 유전체 캐리어의 밑면은 금속 볼의 어레이 패턴이 된다. 이 패턴은 PCB와 같이 특색과 일치하는 패키지 바디로부터 기계적 및 전기적 접합을 형성한다.

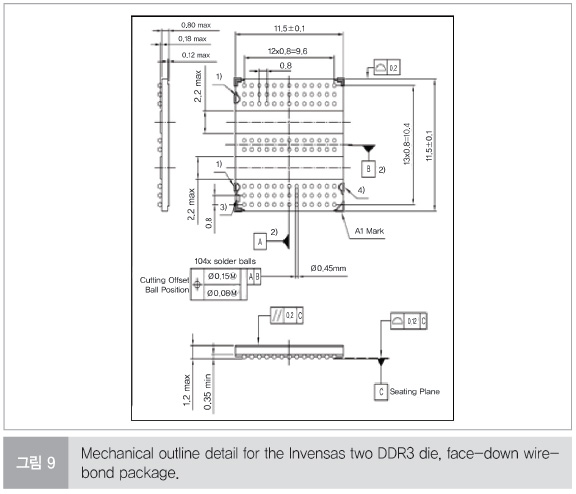

볼 위치 결정과 관련하여, 매트릭스 피치와 중앙 row(들)의 오프셋 혹은 기준점 A 혹은 B로부터 볼의 column(들)은 그림 9에서 자세하게 설명하는 바와 같이 FBGA 패키지 상의 볼 위치를 정의한다.

향후의 JEDEC 표준에서는 다이 소자가 반도체를 보호하기 위해 다양한 기술로 밀봉될 수도 있음을 포함하는 인터포저의 표면을 명시한다. 표준에서는 심볼들, 의미들, 알고리즘들 그리고 정방형 몸체의 ‘flange-type’ FBGA로 참조할 수 있는 것들에 관한 규정된 치수들과 허용오차를 정의한다. ‘Flange’ 항목은 다이 소자의 아웃라인을 넘어선 확대된 패키지의 에어리어를 설명하고 있다. 스펙사항은 JEP95, Section 3, SPP-003 당 미터법 치수기입을 사용하고, ASME Y14.5M-1994에 정의된 기하학 치수공차를 준수한다. 이 표준은 생산되고 있는 모든 FBGA 디자인에 문서화되지 않았다. JEDEC Publication 95(JEP-95) 내에 포함된 향후 FBGA 아웃라인을 위해 뒤따라갈 수도 있는 디자인 요구사항을 단순하게 설정한다. 1.2mm의 총 패키지 높이는 표준 RFIMM 서브스트레이트의 두 면에 잠재적으로 디바이스 실장을 가능하게 하는 프로파일을 제공한다.

RDIMM 서브스트레이트 발전

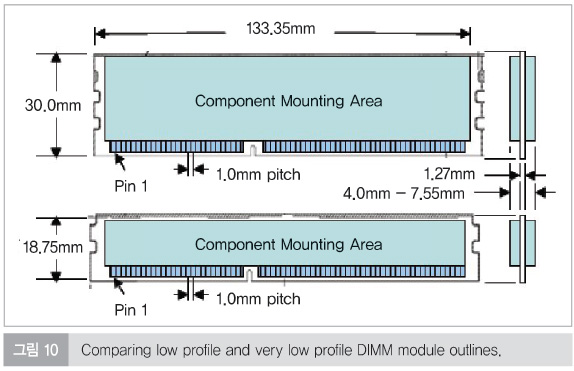

RDIMM(듀얼 in-line 메모리 모듈) 포맷은 높은 퍼포먼스를 위해 발전했다. DDR 애플리케이션은 접촉면에 위치한 바닥 엣지의 row를 통하여 호스트 PCB에 인터페이스되도록 디자인되었다. JEDEC는 DIMM 서브스트레이트를 위한 필요조건들을 컨트롤하고, 1.0mm의 일반 접합 피치를 명시하는 MO-269 생산 아웃라인 문서를 기록했다. 그리고 엣지 접점이 Ni/Au 표면 마감재로 도금되어진 특색도 포함하고 있다. JEDEC Committee JC-11에 의해 마련된 제시된 아웃라인에서는 전자산업계에서 사용이 예상되는 생산제품을 반영하고 있다. 그러나 ‘standard’로서 자동 분류되지 않았고, 사용자들에게는 ‘변화가 발생하기 쉬움’이라는 경고를 주었다. 자체 높이에 대한 물리적으로 동일하게 수용할 수 있는 JEDEC MO-269 문서에 정의된 3개의 RDIMM 프로파일 변화가 있다; 50.0mm 높이가 하나이고, 다른 것은 30.0mm(‘low profile’로 규정된) 그리고 세 번째의 상당히 낮은 높이를 가지는 것은 ‘very-low profile’로 규정되어 있다(그림 10 참조).

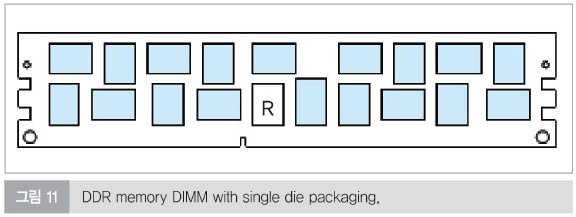

기본적인 아웃라인 치수와 더불어 문서에서는 또한 메모리 패키지 프로파일을 고려하고, 히트 스프레더를 요구하는 변화를 포함하고 있다. 그림 11에서 보여주고 있는 예는 스탠더드 ‘Low Profile’ DIMM 서브스트레이트에 공급된 18개 싱글 다이로 패키지된 DDR 메모리 + 레지스터로 구성된 고성능 메모리 제품군의 현재의 대량 생산품을 나타내고 있다.

일관성 없는 패키지 실장과 이 제품의 정방성 때문에, 회로 인터페이스는 10개의 회로 레이어(8개의 싱글레이어 + 파워 및 그라운드) 만큼 필요로 하는 최적화 요구보다 적다.

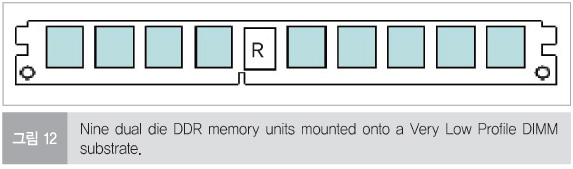

Invensas의 DFD 메모리 패키지 아웃라인은 11.5㎟이다. 이는 싱글 다이 DDR 메모리 패키지 아웃라인보다 단지 약간만 큰 수준이다. DFD 메모리 패키지 유닛이 나란히 일렬로 배열될 수 있기 때문에, 사용자는 ‘Very-Low(18.5mm) Profile’ DIMM 서브스트레이트 변화를 적용할 수 있다(그림 12 참조).

2개의 다이가 face-down한 패키지는 3개의 주요 속성을 가지고 있다; 1) 다이 소자에서부터 패키지 서브스트레이트까지 직접적인 회로 경로를 제공한다. 그리고 다른 2개의 다이 이노베이션과 비교했을 때 인덕턴스를 매우 감소시킨다. 2) 싱글 배열 포맷에서 일반적인 방향성으로 배열되도록 디바이스를 가능하게 하고, 상당히 낮은 프로파일 서브스트레이트 디자인의 사용과 패키지 간의 회로 인터페이스를 더욱 직접적으로 하게 한다. 3) 이 덜 복잡한 라우팅 구조는 또한 DIMM 서브스트레이트로부터 2개의 회로 레이어를 제거함으로써 잠재적으로 제조비용을 줄일 수 있다.

요약 및 결론

제품 소형화 및 고성능 컴퓨팅 요구 증가로 높은 밀집도와 더 빠른 속도의 메모리 디바이스와 모듈 요구가 지속되고 있다. 멀티-코어 프로세스를 채택하고 있는 서버용과 기업용 시장에서는 더 거대한 메모리 밴드폭을 원하고 있다. 모바일 기기 시장은 스마트폰과 태블릿 제품군 역시 상당한 성장이 이어지고 있다. 제조업체들은 줄어든 전력소모를 가능하게 하면서 적은 공간을 차지하는 더 큰 밴드폭 메모리를 기대하고 있다. 메모리 제품군의 디바이스 적층 부문은 늘어나는 고밀도화, 퍼포먼스 및 전력 감소의 요구에 부응해 성장해 가고 있다. 그러나 DDR 메모리용 적층 듀얼-다이-패키지와 관련한 현재 산업계 솔루션으로는 전형적인 face-up wire-bond 프로세스가 이용되고 있다. Center-bond 포맷은 지나친 wire-bond 루프 너비를 초래한다. Face-down 방향으로 하나의 다이를 실장하면 하나의 다이에 있어서 wire-bond 길이를 줄이는데 도움을 주지만, wire-bond 인터페이스는 상당히 길게 남아 있다.

2개의 다이 소자 간의 와이어 길이가 큰 차이를 보일 때, 패키지 퍼포먼스는 손상된다. wire-bond 길이를 줄이고 서브스트레이트 인터페이스에 더욱 균일한 다이를 제공하기 위해, 회사들은 center-bond 랜드에서부터 다이 소자의 외부 엣지까지 동박 전도체를 이어주기 위한 웨이퍼 변경이라는 조치를 취하고 있다. 이 웨이퍼 레벨 RDL(redistribution layer) 프로세스는 상당한 비용이 추가된다. 그리고 wire-bond 사이트가 다이의 외부 엣지에 있다고 하더라도, wire-bond 루프 프로파일의 간격을 유지하기 위해서 하부 다이와 상부 사이에 spacer가 확보되어야만 한다. 회사들은 또한 늘어나는 메모리 밀집도에 대한 대가로 심각한 열 퍼포먼스 제약에 직면해 있음을 발견하고 있다.

Invensas는 본고에서 묘사된 DFD 패키징 혁신이 다층 디바이스에 대한 이점으로 μBGAⓇ face-down 구조를 확장하고, 멀티-메모리 디바이스 패키징 콘셉트의 전형의 하나로 대표될 수 있다고 믿고 있다. 실행 가능한 범주에서 다이 사이즈 다운을 야기하는 실리콘 프로세싱 테크놀로지 진보 때문에 DFD는 부분적으로 가능해져 왔다. 회사들은 높은 퍼포먼스 RDIMM 애플리케이션의 요구에 부응할 수 있는 마감 패키지 아웃라인을 유지하면서 오프셋 다이 적층 프로세스가 효과적으로 완성될 수 있다는 점을 증명해 왔다.

Dual die face-down 패키지는 전기적 그리고 열적 퍼포먼스 모두에서 현존하는 산업계 전반에 분명한 장점을 제공한다. 퍼포먼스와 관련해서도, FEA(finite element analysis) 데이터는 패키지 열 저항이 25% 만큼이나 감소되어 디바이스 프로젝트를 증진시키는 2개의 다이 DFD 메모리를 수집한다. 경제적인 측면에서도, 대안이 되는 2개의 다이 메모리 패키지 변화와 비교했을 때, 전체 패키징 비용이 15~20% 하락한 것으로 평가되었다. 게다가 DFD 어셈블리 프로세스는 기존 BGA 패키지 어셈블리 및 테스트 인프라를 사용하기에, 신규 재질 혹은 특화된 설비가 필요 없다.